Verilog simulation tutorials

Contents

- Getting started with Incisive tools

- Running a Verilog 'Hello world!'

- Simulate a synchronizer

Getting started with Cadence Incisive tools

suite utilizzata: Incisive release 10.2

Documentazione in

/usr/cadence/Incisive_10.20/doc

Eseguibili in

/usr/cadence/Incisive_10.20/tools/bin

Incisive tutorial here

Importante! Cadence stesso fornisce un tutorial!

/usr/cadence/Incisive_10.20/doc/iustutorial

cd ~/cadence/tutorial/incisive cp -r /usr/cadence/Incisive_10.20/doc/iustutorial/examples/files ./src

Stating NCLaunch:

nclaunch [options] &

nclaunch -help

nclaunch -help >> ./doc/nclaunch.help

Running a Verilog 'Hello world!'

Un semplice hello world program da runnare alla command line:

// hello.v Verilog hello world program module hello; initial begin $display("Hello world! \n"); $finish; end endmodule

E lo posso compilare/runnare da command line ad esempio richiamando Verilog-XL:

verilog hello.v

Questo produce un output del tipo

Tool: VERILOG-XL 08.20.001-d Oct 22, 2012 00:31:41

Copyright (c) 1995-2004 Cadence Design Systems, Inc. All Rights Reserved.

Unpublished -- rights reserved under the copyright laws of the United States.

Copyright (c) 1995-2004 UNIX Systems Laboratories, Inc. Reproduced with Permission.

THIS SOFTWARE AND ON-LINE DOCUMENTATION CONTAIN CONFIDENTIAL INFORMATION

AND TRADE SECRETS OF CADENCE DESIGN SYSTEMS, INC. USE, DISCLOSURE, OR

REPRODUCTION IS PROHIBITED WITHOUT THE PRIOR EXPRESS WRITTEN PERMISSION OF

CADENCE DESIGN SYSTEMS, INC.

RESTRICTED RIGHTS LEGEND

Use, duplication, or disclosure by the Government is subject to

restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in

Technical Data and Computer Software clause at DFARS 252.227-7013 or

subparagraphs (c)(1) and (2) of Commercial Computer Software -- Restricted

Rights at 48 CFR 52.227-19, as applicable.

Cadence Design Systems, Inc.

555 River Oaks Parkway

San Jose, California 95134

For technical assistance please contact the Cadence Response Center at

1-877-CDS-4911 or send email to support@cadence.com

For more information on Cadence's Verilog-XL product line send email to

talkv@cadence.com

Compiling source file "hello.v"

Highest level modules:

hello

Hello world!

L8 "hello.v": $finish at simulation time 0

0 simulation events (use +profile or +listcounts option to count)

CPU time: 0.0 secs to compile + 0.0 secs to link + 0.0 secs in simulation

End of Tool: VERILOG-XL 08.20.001-d Oct 22, 2012 00:31:41

A simple inverter Verilog tutorial

Bla bla bla click here

Simulate a synchronizer

Bla bla bla click here

A simple multiplexer

Bla bla bla click here

Create a D Flip-Flop

Bla bla bla click here

RTL simulation using Verilog-XL compiler

Anziche' usare nclaunch posso usare Verilog-XL e visualizzare le forme d'onda con SimVision

L'eseguibile e' sotto Incisive in

$IUS_DIR/tools/bin/verilog

verilog -help

Documentazione (Verilog-XL User Guide) sotto

$IUS_DIR/doc/vloguser

Posso fare tutto senza gui con

verilog main.v test_main.v

Attenzione all'ordine! che conta!

Pay attention when specifying the files names. The files have to be specified in a particular order such that the lower-level modules are compiled before the higher-level modules. The testbench would be the last item to be compiled.

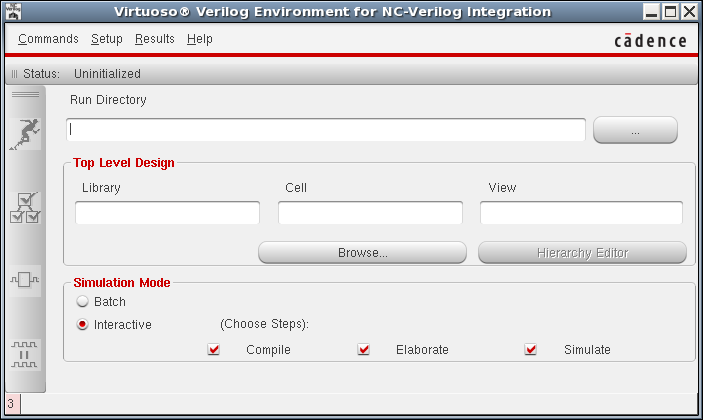

Oppure da Cadence IC posso usare la Verilog Integration offerta da IC:

CIW ⇒ Tools ⇒ NC-Verilog…

or from Schematic Editor L ⇒ Launch ⇒ Simulation ⇒ NC-Verilog

Documentazione in (ncveruser.pdf):

/usr/cadence/IC_6.1.5/doc/ncveruser

web tutorial here

DFF example:

// dff.v Verilog code `timescale 1ns/100ps module DFF(D, clk, Q); input D; input clk; output Q; reg Q; always @ (posedge clk) Q <= #2 D; endmodule

MUX example:

Senza ritardi:

module MUX2(input A, B, select, output W); assign W = (A & ~select) | (B & select); endmodule

Con i ritardi, per vedere i glitches

`timescale 1ns/100ps module MUX2(input A, B, select, output W); assign #6 n = ~select; assign #3 m = A & select; assign #3 p = B & n; assign #2 W = m | p; endmodule

Sincronizzatore:

// synch.v Verilog code `timescale 1ns/100ps module SYNCHRONIZER(input clk, adata, output reg synchdata); always @ (posedge clk) if ( adata == 0) synchdata <= 0; else synchdata <= 1; endmodule