### University of Turin

Faculty of Mathematical, Physics and Natural Sciences

Physics Degree Thesis

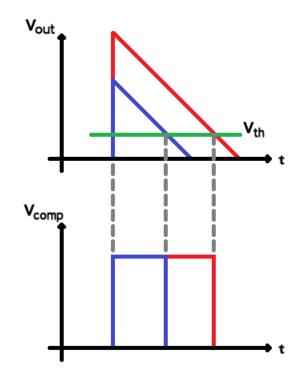

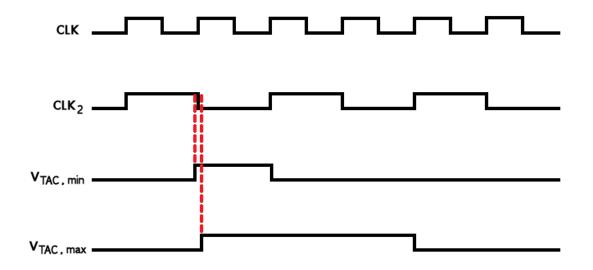

# A Low Power Front-End Amplifier for the Microstrip Sensors of the PANDA Microvertex Detector

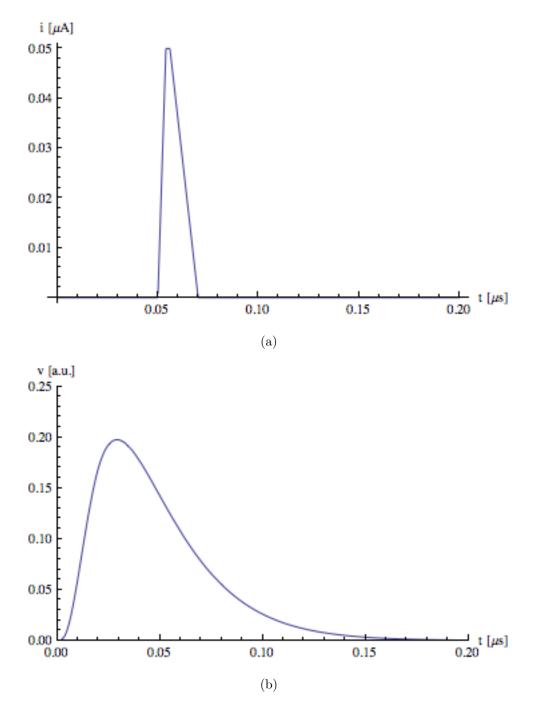

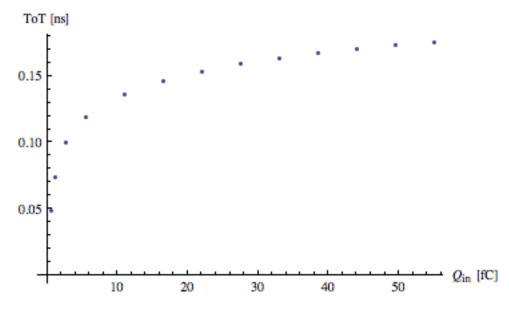

Candidate: Valentino Di Pietro

Supervisor: Dr. Angelo Rivetti

Academic year 2011 / 2012

### Abstract

This thesis is part of the ongoing studies for the PANDA (antiProton ANnihilation at DArmstadt) Microvertex Detector (MVD) microstrip sensors readout electronics. The PANDA experiment is one of the key projects at the future Facility for Antiproton and Ion Research (FAIR), which is currently under construction at GSI, Darmstadt. It will perform precise studies of antiproton-proton annihilations and reactions of antiprotons with nucleons of heavier nuclear targets. The covered centre-of-mass energy between 1 GeV and 5 GeV allows very accurate measurements, especially in the charm quark sector, so it will be possible to explore the nature of the strong interaction and to obtain a significant progress in the understanding of the QCD spectrum and hadron structure [1]. The innermost PANDA detector is the MVD. It is made up by two different sensors: pixels and microstrips. The subject of this thesis is the design of these microstrip sensors readout system based, such as the pixel sensors, on the Time over Threshold (ToT) technique. The principles of this kind of measure will be widely discussed later, at the moment we only need to specify that this involves the design of a time-based ASIC (Application Specific Integrated Circuit). Moreover, considering that one of the main features of the PANDA experiment is that it's triggerless, it is necessary to perform time measures with accurate time resolution. This choice to extract the amplitude, and thus the energy, information through time measures allows to use a TDC (Time to Digital Converter) rather than an ADC (Analog to Digital Converter). TDCs are digital or analog circuits with a low dynamic range, so they are more suitable to be implemented with the well known CMOS technologies working with typical power supplies of  $(1.2 \div 1.5) V$ . The purpose of this thesis is thus to develop a low-power front-end amplifier optimized for time-based measures, in particular to study the feasibility of such a structure identifying the possible relative issues. The thesis has been organized as follows:

#### Chapter 1

This chapter contains a more detailed introduction on the Panda experiment and a brief description of two points of its physics program: hadrons in nuclear matter and parton structure. Then there is an overview on the Panda detector structure involving the Target and the Forward Spectrometers. The core of the chapter is the description of the Microvertex Detector with particular attention payed on the microstrip sensors features and issues. In the end there is a table summarizing the key parameters of the system driving the design of the front-end electronics.

#### Chapter 2

This is a theoretical chapter necessary for a better understanding of the problems encountered in the design of a front-end amplifier. The first part regards the study of the ideal cases where we use an ideal preamplifier and use a  $\delta$ -like pulse as input signal. After that, is reported the discussion on the effects of non-idealities such as the issues due to a real amplifier or to a more realistic model of the signals coming from the detector. In the last part of the chapter is discussed the noise in front-end amplifier. The noise calculations are examined in detail both in simpler and more complicated cases in order to make it possible a comparison with the results obtained with the CAD simulations.

#### Chapter 3

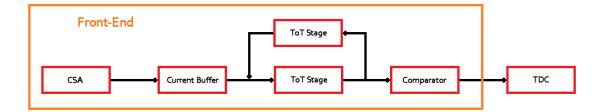

In this chapter, the ToT principle is introduced and the TDC necessary to perform accurate timing measurement is briefly described. The chapter then concentrates on the implemented front-end. The building blocks are described in detail at the schematic level and analyzed with the help of small signal analysis models.

#### Chapter 4

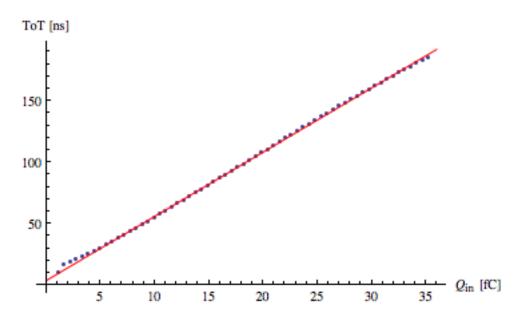

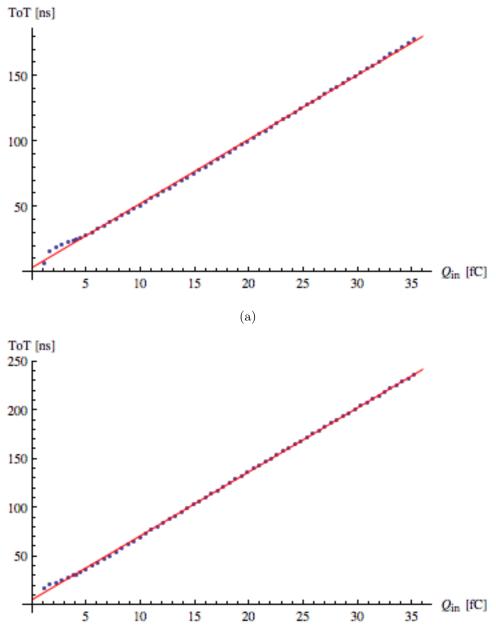

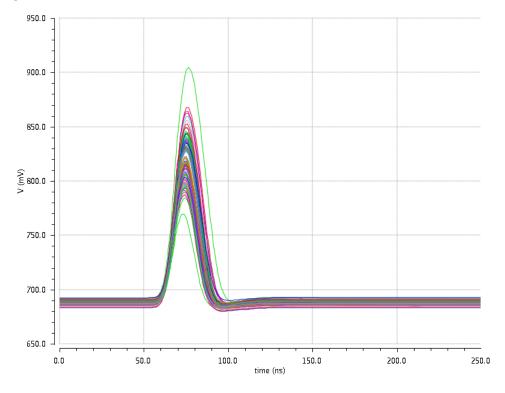

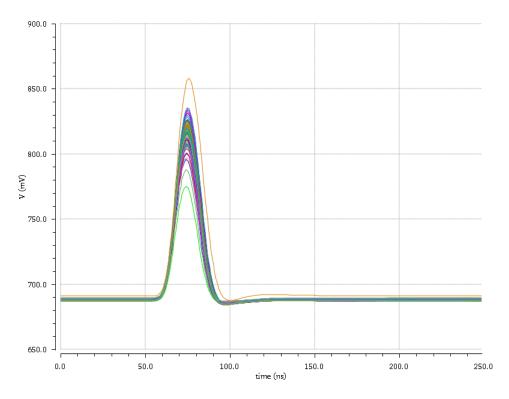

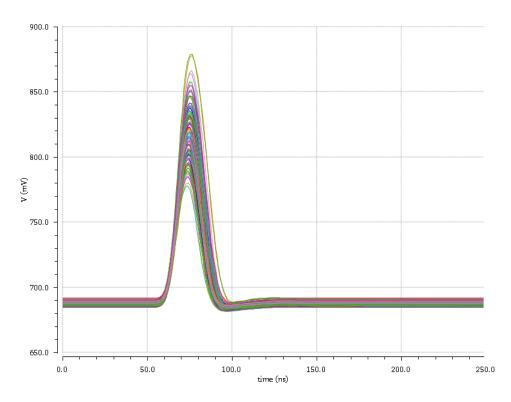

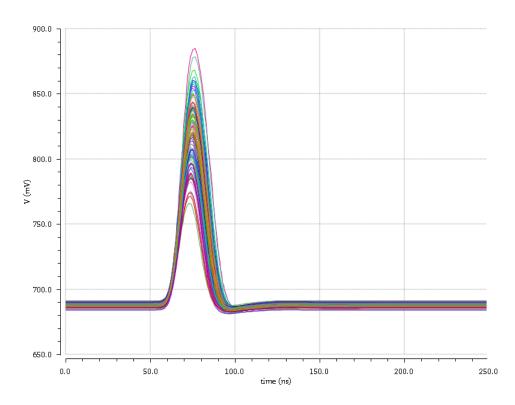

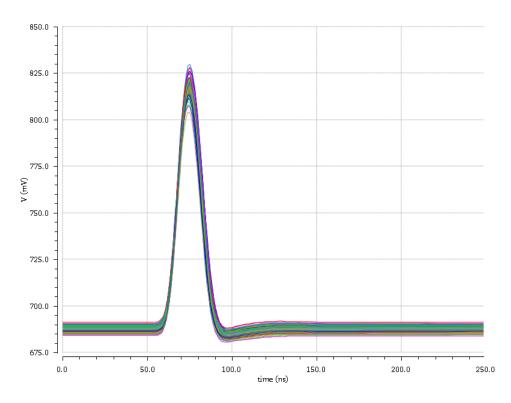

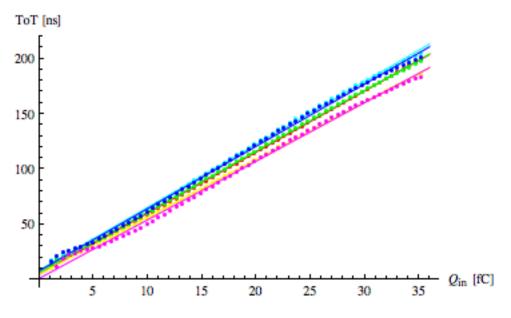

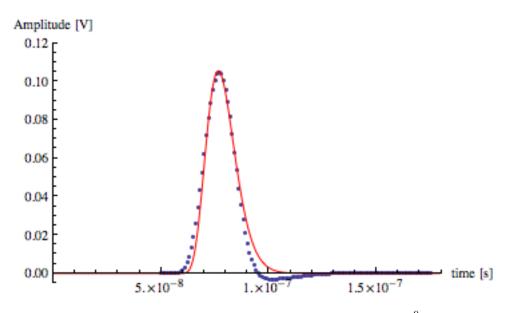

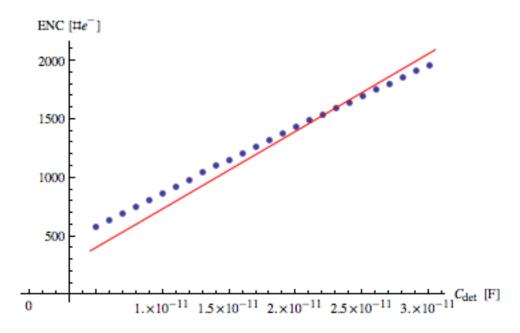

In this chapter, the results of the CAD simulations are reported and the performance are discussed. The results shown focus on the study of the linearity of the ToT measures, the corner process analysis, the different behaviors due to temperature variations, the noise of the chain and the jitter of the comparator.

The main results achieved in this work and the issues that need to be addressed in the future are summarized in the conclusions.

# Contents

| 1        | The  | e PANDA Experiment                                                   | <b>5</b> |

|----------|------|----------------------------------------------------------------------|----------|

|          | 1.1  | Introduction                                                         | 5        |

|          |      | 1.1.1 Hadrons in nuclear matter                                      | 6        |

|          |      | 1.1.2 Parton Structure                                               | 8        |

|          | 1.2  | The PANDA Detector                                                   | 10       |

|          | 1.3  | Micro Vertex Detector (MVD)                                          | 12       |

| <b>2</b> | From | nt-End Amplifier                                                     | 17       |

|          | 2.1  | The preamplifier                                                     | 17       |

|          | 2.2  | The shaper                                                           | 19       |

|          |      | 2.2.1 $\mathbf{CR}$ -( $\mathbf{RC}$ ) <sup><b>n</b></sup> shapers   | 23       |

|          | 2.3  | Non-ideal behavior                                                   | 26       |

|          |      | 2.3.1 Finite feedback resistor effects                               | 26       |

|          |      | 2.3.1.1 Pole-Zero Cancellation                                       | 31       |

|          |      | 2.3.1.2 Baseline Holder                                              | 34       |

|          |      | 2.3.2 Sensor signal variation effects                                | 38       |

|          |      | 2.3.3 Gain and bandwidth limitations in CSAs                         | 42       |

|          |      | 2.3.3.1 Effects of finite gain                                       | 42       |

|          |      | 2.3.3.2 Effects of bandwidth limitation                              | 44       |

|          | 2.4  | Noise calculations                                                   | 47       |

|          |      | 2.4.1 Noise sources in a front-end amplifier                         | 48       |

|          |      | 2.4.2 Noise in a CR-RC shaper                                        | 51       |

|          |      | 2.4.3 Noise in a $\mathbf{CR}$ - $(\mathbf{RC})^{\mathbf{n}}$ shaper | 54       |

|          |      | 2.4.4 Noise indexes                                                  | 57       |

| 3        | Imp  | Dementation                                                          | 58       |

|          | 3.1  |                                                                      | 58       |

|          | 3.2  | Time to Digital Converter                                            | 59       |

|          | 3.3  | 8                                                                    | 63       |

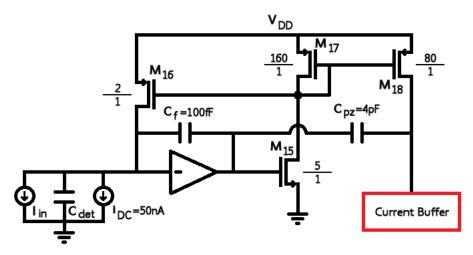

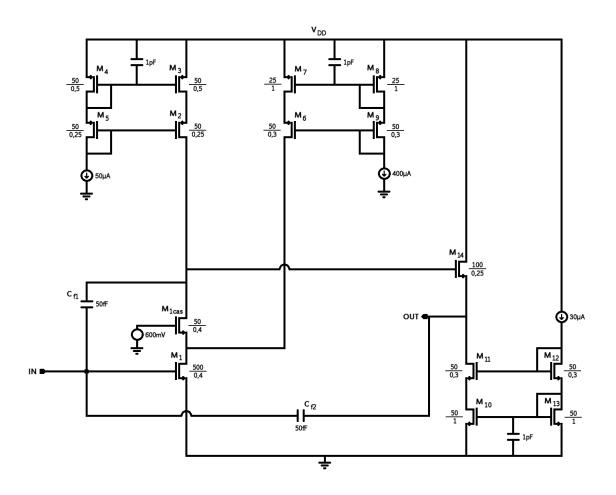

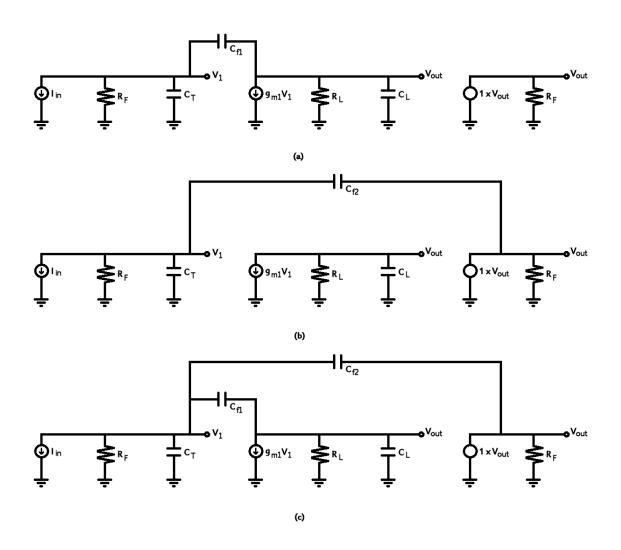

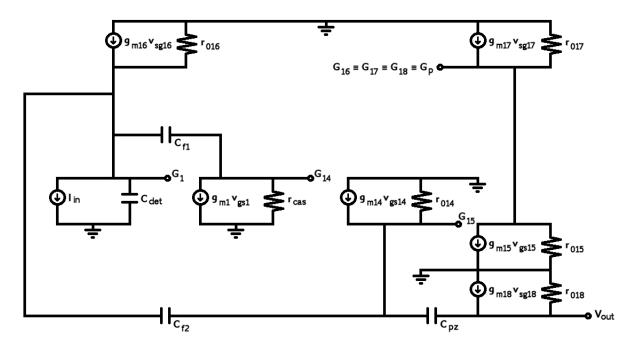

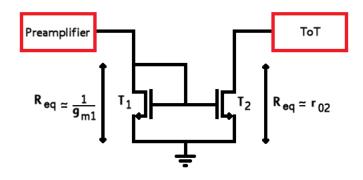

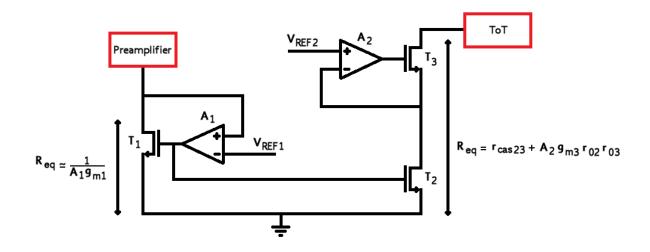

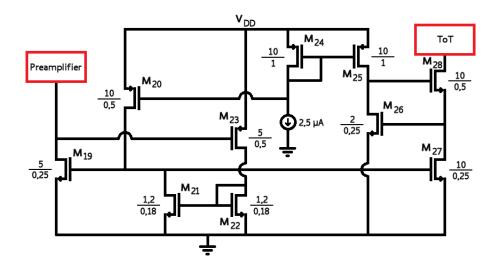

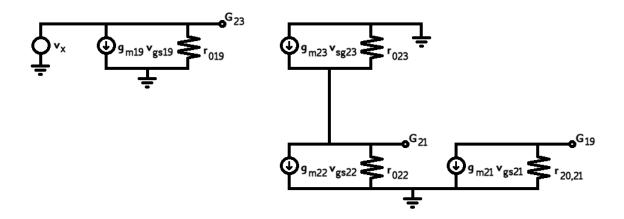

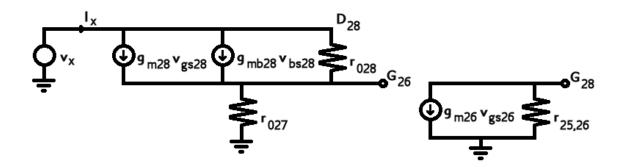

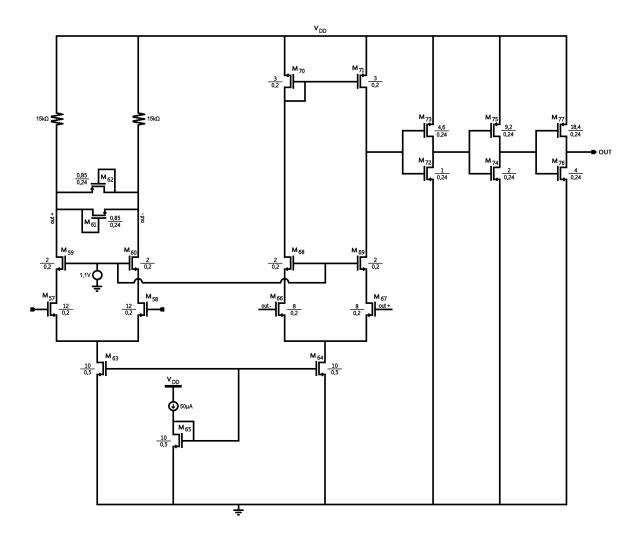

|          |      | -                                                                    | 66       |

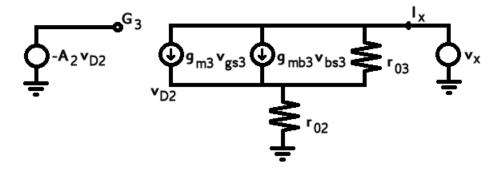

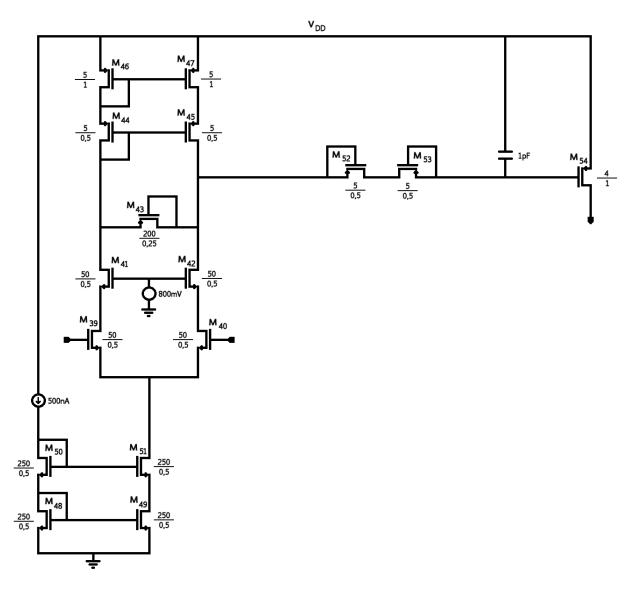

|          |      | 3.3.2 Current Buffer                                                 | 73       |

|          |      | 3.3.3 ToT Stage                                                      | 79       |

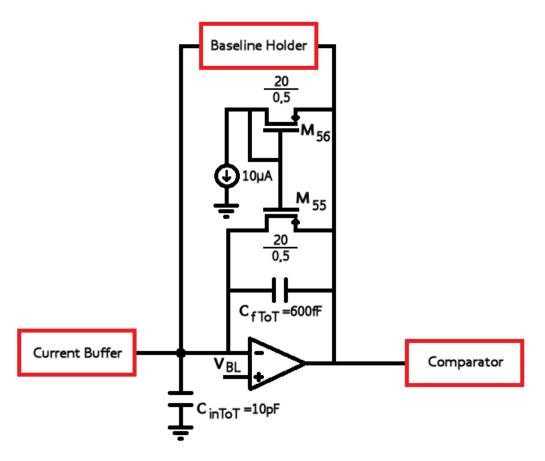

|          |      | 3.3.4 Baseline Holder                                                | 83       |

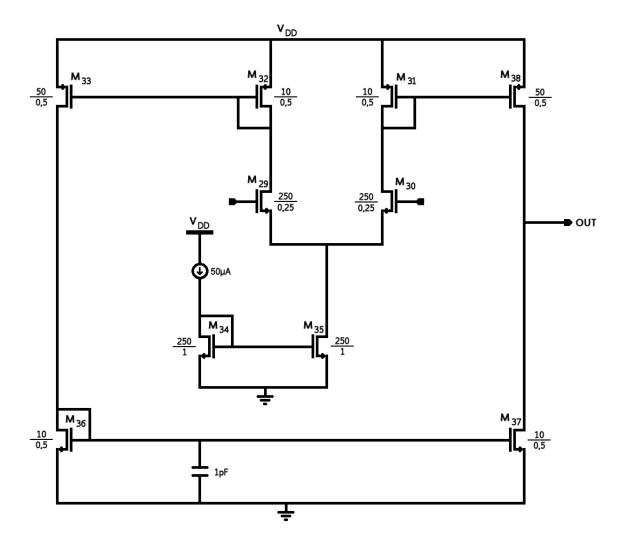

|          |      | 3.3.5 Comparator                                                     | 85       |

| 4 S | mulations 86                  |

|-----|-------------------------------|

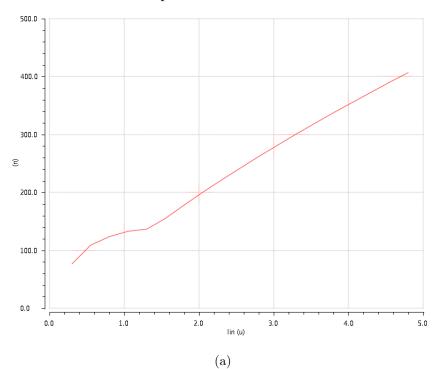

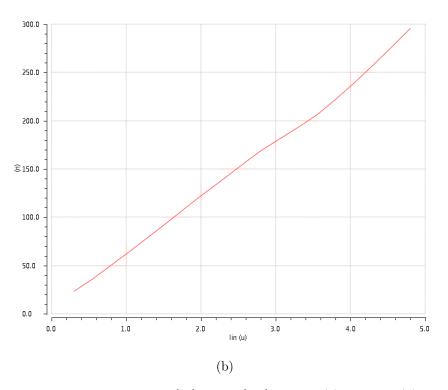

| 4.  | L Linearity                   |

| 4.  | 2 Corner Process Analysis     |

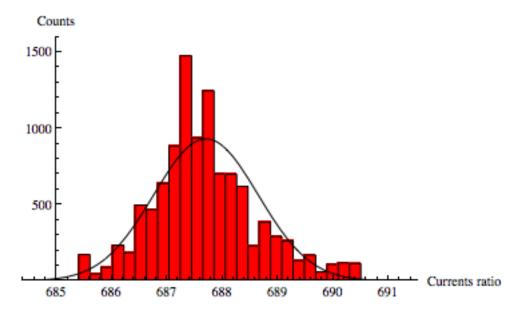

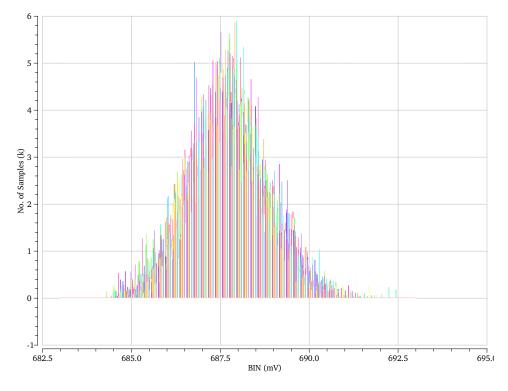

| 4.  | B Monte Carlo Simulation      |

| 4.  | I Temperature variations   95 |

| 4.  | 5 Noise                       |

| 4.  | 6 Comparator jitter           |

|     |                               |

### Chapter 1

# The PANDA Experiment

#### 1.1 Introduction

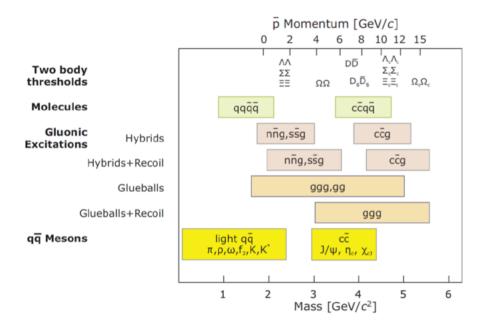

PANDA (antiProton ANnihilation at DArmstadt) is a subnuclear physics experiment involving more than 450 scientists from 17 countries that is planned to start in 2018. The experiment aim at investigating the physics of strong interaction and the hadron structure, acquiring understanding of the mechanism of hadron mass generation, quark confinement and probing the existence of glueballs and hybrids. In order to achieve these goals it will perform several measurements of antiprotons interactions with protons and nuclei in a fixed target setup. The innovation of PANDA, compared to other fixed target experiments, is due to the high luminosity  $(L \lesssim 2 \cdot 10^{32} \frac{1}{cm^2 s})$  and very good collimation of the incident antiproton beam which allow to have a large number of events and a more accurate statistics. An antiproton beam in the momentum range of 1.5 GeV/c - 15 GeV/c, provided by High Energy Storage Ring (HESR), gives access to a center of mass energy range from  $2.2 GeV/c^2$  to  $5.5 GeV/c^2$  in  $\overline{p} - p$  annihilations allowing a precise test of the Quantum Chromodynamics (QCD) between the perturbative and non perturbative regime. Figure 1.1 shows the accessible mass range of hadrons at the PANDA experiment in relation to the antiproton momenta required in the fixed target collisions.

Figure 1.1: Mass range accessible at PANDA  $(2.2GeV/c^2-5.5GeV/c^2)$ . The upper scale indicates the corresponding antiproton momenta required in a fixed target setup.

With the accessible energy region at HESR it is possible to cover a larger range of studies compared with Low Energy Antiproton Ring facility (LEAR) of CERN (beam momentum up to 2.2GeV/c), such as:

- Investigation on the behavior of hadronic particles in nuclear matter for understanding the origin of hadron masses.

- Measurement of Generalized Parton Distributions (GPDs), transverse parton distribution functions, and electro-magnetic form factors in the time-like region in order to study the proton structure.

#### 1.1.1 Hadrons in nuclear matter

PANDA foresees the possibility to study antiproton annihilations on fixed heavy nuclear targets. These reactions are ideally suited to investigate the modification of hadronic mass in nuclear matter and unravel its origin. The QCD vacuum is characterized by quark and gluon condensate, so the chiral symmetry (a symmetry of the QCD Lagrangian under which the left-handed and right-handed parts of Dirac fields transform independently) in QCD is spontaneously broken by the fact that the quarks do have mass linked to the condensate. However the light quark masses are much smaller than the hadronic scales and for this reason the chiral symmetry may be considered an approximate symmetry of the strong interactions.

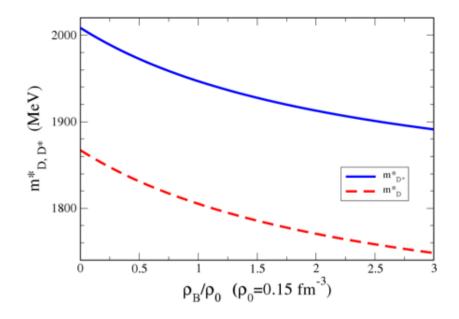

A partial restoration of chiral symmetry is expected in dense nuclear matter and at high temperatures for the light quarks due to a change in the quark condensate leading to a deconfined state, thus to the formation of the Quark-Gluon Plasma. This should therefore lead to the modification of hadrons properties, like mass and width, when they are embedded in the nuclear matter. The high intensity beam, up to 15 GeV/c in PANDA, allows an in-medium extension of these studies towards the heavy-quark sector, especially for mesons containing open or hidden charm. Given the large contribution of the c quarks in the charmonium mass, the in-medium masses states are expected to be affected mainly by the gluon condensate. For this reason it is predictable a small shift of the in-medium mass  $(\sim 10 MeV/c^2)$  for the low lying charmonium states. The D mesons, which are made of a c quark coupled to a light antiquark, represents, together with the B mesons, a possibility to study the in-medium modifications of systems with a single light quark. Figure 1.2 shows the theoretical predictions for the drop of the D and  $D^*$  meson masses in relation to the surrounding nuclear matter density. The D mass dropping lowers the DD threshold in the nuclear matter and consequently increases the production cross section of the D and  $\overline{D}$  mesons in antiproton nucleus reactions.

Figure 1.2: D and  $D^*$  meson effective masses as a function of nuclear matter density.

Another important study for a better understanding of the properties of charmed hadrons in nuclear matter is the measurement of the  $J/\Psi$  dissociation in the nuclear matter. This phenomenon is due to any interaction of  $J/\Psi$ , or its precursor

8

states, with the nuclear medium which could break the bound state of the charm composing it. The available data on the  $J/\Psi$  nucleon cross section are scarce and they are determined by indirect experimental information from the  $J/\Psi$  nucleon interaction in high energy pN (proton-Nucleus) collisions, so the deduced  $J/\Psi$  nucleon dissociation cross section has large uncertainties and its momentum dependence is unknown. In PANDA a reliable  $J/\Psi$  nucleus dissociation cross section will be obtained by the comparison of the production yield of  $J/\Psi$  in  $\bar{p}$  annihilation on p and different nuclear targets. This is important for the understanding of the charmonium suppression in relativistic heavy ion collisions, which is considered one of the most promising signature of the formation of the quark-gluon plasma.

#### 1.1.2 Parton Structure

#### Generalized parton distributions

The binding force between quarks and gluons, which makes possible the formation of hadrons, has to be studied in the non-perturbative QCD regime. At the moment there is not a reliable fully quantitative calculation starting from QCD first principles, so the nucleon structure is described by phenomenological functions like form factors, parton densities and distribution amplitudes. In the infinite momentum approximation, the partons are free non-interacting particles and it is possible to describe the hadrons with the distribution of partons in the longitudinal direction given by the distribution functions, while elastic form factors give information on the charge and magnetization distributions in the transverse plane. The Generalized Parton Distributions (GPDs) unify and extend these concepts, giving a description of partons with functions of more variables and allowing a full three dimensional image of hadrons. The GPDs, introduced in the study of hard exclusive processes in lepton scattering experiments, contain informations on the distribution of partons both in the transverse plane and in the longitudinal direction and the quark and gluon angular momentum contributions to the nucleon spin. PANDA will conduct studies of Hard Exclusive Processes in  $\overline{p}p$  annihilation with various final states in a new kinematic region expecting new insights into the applicability and universality of these novel QCD approaches. Measurement of the Crossed-Channel Compton Scattering  $(\bar{p}p \to \gamma\gamma)$  and Hard exclusive meson production  $(\overline{p}p \to \gamma \pi^0)$  are foreseen.

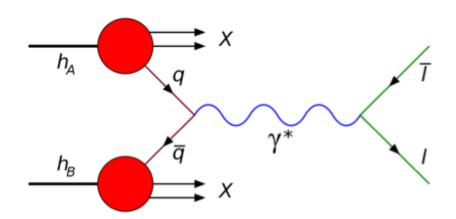

#### The Drell-Yan process

The Drell-Yan process occurs in high energy hadron-hadron scattering, where a quark and antiquark from the interacting hadrons annihilate creating a virtual photon or Z boson, which then decays into a pair of oppositely-charged leptons as shown in Figure 1.3.

Figure 1.3: Drell-Yan process.

The Drell-Yan process is an ideal tool for investigating the transverse parton distribution functions. In PANDA the Drell-Yan process will be studied in semiinclusive lepton production for di-muons in scattering of unpolarized antiproton beam over unpolarized proton target  $\bar{p}p \rightarrow \gamma^* \rightarrow \mu\mu + X$ . From the angular distribution of dileptons it is possible to evaluate the distribution function of a transversely polarized quark inside an unpolarized hadron  $h_1^{\perp}(x, \vec{k}_1^2)$ .

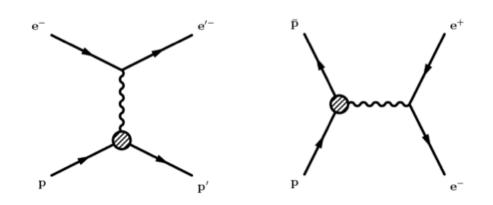

#### Time-like form factor of the proton

The electromagnetic form factor of the proton is of upmost importance for the study of hadronic structure and internal dynamics at low energies as well as the higher energies where perturbative QCD applies. The measurement of the electron scattering on protons allows to determine the proton form factors in the region of space-like momentum transfer  $q^2 < 0$ . While  $\bar{p}p \rightarrow e^+e^-$  annihilation, shown in Figure 1.4, gives access to the proton electromagnetic form factors in the time like region  $q^2 > 4m_p^2c^2$ , where  $m_p$  is the proton mass.

Figure 1.4: Feynman diagrams for electron scattering on proton (left) and its crossed channel  $\overline{p}p \rightarrow e^+e^-$  (right).

In the space-like region the form factors are real functions of  $q^2$ , and they are the Fourier transforms of the spatial charge  $(G_E)$  and the magnetization distribution  $(G_M)$ . In the time-like region the form factors are complex functions, and represent the frequency spectrum of the electromagnetic response of the nucleon. The  $\bar{p}p \rightarrow e^+e^-$  in one photon approximation is a linear combination of  $|G_E|^2$  and  $|G_M|^2$ . The  $q^2 < 15 GeV/c^2$  region of the proton time-like form factor have been measured by E760 and E835 experiments at Fermilab, but due to limited statistics  $|G_E|$  and  $|G_M|$  have not been measured separately. Thanks to its improved statistics and wide angular coverage, PANDA will measure the  $G_E$  and  $G_M$  separately with an unprecedented precision up to  $14 GeV/c^2$  and the absolute and differential cross section up to  $22 GeV/c^2$ . Therefore it is possible to test the transition to the perturbative QCD regime, where an asymptotic behavior is predicted for the proton magnetic form factor, moreover The PANDA rich particle identification plays an important role in the rejection of the  $\bar{p}p \rightarrow \pi^-\pi^+$  background with a cross section 106 times higher.

### 1.2 The PANDA Detector

It will provide:

- a  $4\pi$  solid angle coverage around the interaction point between the antiproton beam and the fixed target

- high event rate capability  $(2 \cdot 10^7 annihilations/s)$

- detection and identification of charged particles in a wide momentum range (100 MeV/c 15 GeV/c)

• high momentum (1%) and tracking resolution of charged particles

The detector is divided in two parts: a target spectrometer surrounding the interaction region and a forward spectrometer mounted behind the target spectrometer. Using these spectrometers it is possible a full angular coverage of the spatial region around the interaction point.

#### Target spectrometer

The target spectrometer, surrounding the interaction point, measures charged tracks for polar angles larger than 22°. It is made by:

- Solenoid Magnet: superconducting solenoid coil providing a maximum magnetic field of 2T with a homogeneity better than 2% over the volume of the vertex detector and central tracker. It has an inner radius of 90cm and a length of 2.8m.

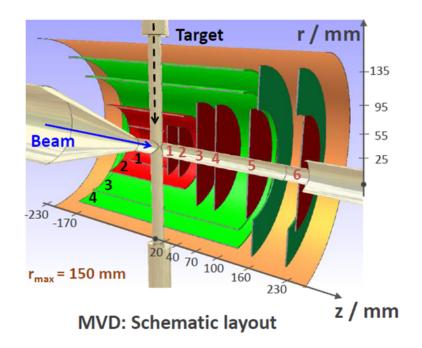

- Micro Vertex Detector (MVD): the closest detector to the interaction point, it is based on radiation hard solid state detectors, both pixel and microstrip. It is designed in order to track the charged particle for the vertex reconstruction and measure the energy loss per unit path-length  $\left(\frac{dE}{dx}\right)$  for slow charged particle identification. In the current MVD design, there are two barrels of pixel detectors, two barrels of strip detectors and six disks arranged perpendicularly to the beam pipeline. The inner four layers of the disks are made of pixels, the following two are made of pixels on the inner part and strips on the outer one.

- Central Tracker: based on a barrel detector surrounding the MVD useful to obtain a good detection efficiency for secondary vertices. There are two methods proposed to achieve the desired detection efficiency. The first one is covering a large area around the MVD with straw tubes (STT) or a time-projection chamber (TPC). The second one is based on three sets of gas electron multipliers (GEMs) employed to detect particles emitted at angles below 22° which are not covered by STT or TPC.

- Cherenkov Detectors and Time-of-Flight barrels: the first ones cover the part of the momentum spectrum above 1GeV/c while the second ones identify slower particles. Combining the information from both detectors it is possible to determinate the mass of detected particles.

- Electromagnetic Calorimeters: required to cover a large energy range (few MeV up to several GeV), it is based on lead-tungstate inorganic scintillators. Lead-tungstate is chosen for its good energy resolution in photon, electron and hadron detection, fast response and high density.

• Muon Detectors: made by 72 strips of plastic scintillator counters mounted behind the iron yoke of the target spectrometer. In addition, an equal number of strips will be placed perpendicular to the beam axis, at the front of the solenoid magnet.

#### Forward spectrometer

The forward spectrometer detect small angle tracks. It is made by:

- Dipole Magnetic: covers the entire angular acceptance  $(\pm 10^{\circ})$  in the horizontal direction and  $\pm 5^{\circ}$  in the vertical direction). It is used for momentum analysis of charged particles in forward spectrometer: the maximum bending power, 2Tm, could deflect an antiproton beam at the maximum momentum of 15GeV by 2.2° from the original track.

- Forward Trackers: based on a set of wire chambers allowing to track particles with high momenta as well as very low momentum particles. The expected momentum resolution of the system for 3GeV protons is  $\frac{\delta p}{p} = 0.2\%$ . Furthermore, it makes possible to reconstruct tracks in each chamber separately, in case of multi-track events.

- Forward Particle Identification: based on a Ring Imaging Cherenkov (RICH) which separates  $\pi/K/p$  through two radiators: silica aerogel and  $C_4F_{10}$  gas.

- Forward Electromagnetic Calorimeter: based on lead-scintillator sandwiches readout with wavelength shifting fibers, it is a Shashlyk-type calorimeter with high resolution used to detect photons and electrons.

- Forward Muon Detector: based on 20 vertical strips for muon detection similar to the muon system of target spectrometer

#### 1.3 Micro Vertex Detector (MVD)

Currently, the PANDA MVD group is engaged in different research and development activities for an optimized detector design starting from the experimental requirements. In particular, the INFN microelectronic group of Turin is studying the front-end electronics for the MVD taking into account the simulations of  $\bar{p}p$ and  $\bar{p}N$  collisions results. The basic specification for the MVD are:

- Spatial Resolution:  $\delta^3 x \leq 100 \mu m$  is required for a clear detection of the displaced vertices.

- Material Budget: since the MVD is the innermost detector it does not have to affect the outer detector components, therefore the MVD material budget has to be kept as low as possible.

- Time Resolution: the mean time between two interactions is 50ns, so a time resolution  $\delta t \leq 10ns$  is required in order to associates the MVD hits with the correct interaction.

- Readout Speed: taking into account the estimated MVD particle hit rate of  $3 \cdot 10^9$  the overall readout speed has to be in the order of  $\sim 100Gbit/s$ . This is due to the fact that the MVD has to send out to the offline electronics all the data which contains information on the hit position, timing and energy loss, since the PANDA detector will not have a centralized trigger system.

- Radiation Hardness: a fundamental parameter for the reliability of both sensors and electronics since the close position of the MVD to the interaction point and the high event rate.

- Device Thickness: lower than 1mm (1% of radiation length), to be able to detect low momentum particles and to avoid multiple scattering.

In the MVD will be used both silicon pixel detectors and double-sided silicon strip detectors (DSSD) as shown in Figure 1.5.

Figure 1.5: MVD schematic layout. The red area is covered with pixel sensors, the green one with DSSD.

The pixels will be used in the inner part, where the density of particles is higher, and each pixel sensor will have an active area of  $100\mu m \times 100\mu m$ , while the strips

will be used in the outer part, where the density of particles is lower. Since the subject of this thesis is to describe the front-end implementation for microstrip sensors, henceforward we'll focus on the description of DSSD.

#### **Double-Sided silicon Strip Detectors**

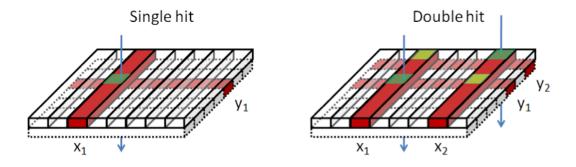

The DSSD are made by an upper layer of strips arranged in rows and by a lower layer arranged in columns. When a particle hits the detector, its position is given by the intersection of the strip of the upper layer and the strip of the lower layer in order to obtain a two dimensional information. The use of this kind of sensor is preferred to pixel sensors since it allows the reduction of readout channels maintaining the same spatial resolution. In fact, a number  $N_{pixel} = \frac{A}{(\Delta x)^2}$  of channels is required to cover a square area A with a spatial resolution  $\Delta x$ , on the other hand with  $N_{strip} = 2\sqrt{N_{pixel}}$  strip readout channels it is possible to have the same performances with a significant reduction of the material budget. The main drawback of DSSD is the ghost hit. When two particles hit the detector at the same time, generating similar signals, it is more difficult to obtain the exact position of each particle by analyzing the cross points between the upper and the lower layer hit because more combinations are possible: the cross points where there is no interaction with the particle hitting are called ghost hits (Figure 1.6).

Figure 1.6: Ghost hit during a double hit on a double sided strip sensor.

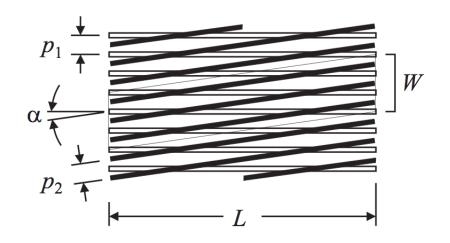

A possible solution to this problem is to reduce the stereo angle, that is the angle between the strips of the two layers, rather than 90°. The area subtended by two sensing strips of length  $L_1$  and  $L_2$  arranged at an angle 90° is  $A = L_1L_2$ , so the probability of ghost hits is maximal. However if we use a stereo angle  $\alpha < 90^\circ$ , as shown in Figure 1.7, the capture area, in the approximation  $L_1 = L_2 \equiv L$ , is:

$$A \approx L^2 \frac{p_2}{p_1} tan\alpha + Lp_2 \tag{1.1}$$

Figure 1.7: DSSD with a stereo angle  $\alpha < 90^{\circ}$ .

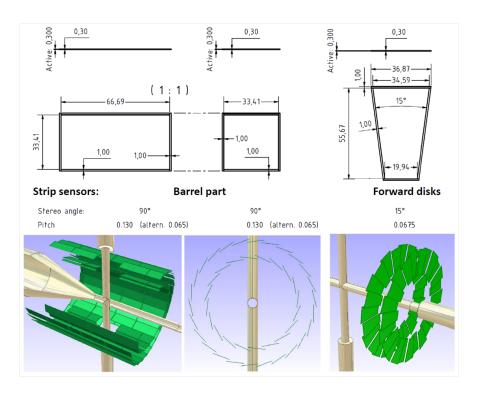

It is important to observe that decreasing the stereo angle  $\alpha$  minimize the probability to have a ghost hit but the price is a reduction of resolution in the longitudinal coordinate. This issue does not affect pixel detectors since in a matrix of pixels, each element correspond to one only pixel and, consequently, when a particle hits the detector, there isn't ambiguity about its position [13]. That is the reason why pixel detectors are employed in the inner part of the MVD and strip detectors in the outer layers where the hit rate is lower. The strips are rectangular shaped in the barrel part and trapezoidal in the disk part (Figure 1.8), their width (pitch) and stereo angle determines the spatial resolution. The pitch chosen is  $130\mu m$  for rectangular sensors and  $70\mu m$  for trapezoidal sensors, while the stereo angles are 90° and 15° respectively. There will be 12 million pixel and 200,000 strip readout channels with a total power dissipation of 4kW.

Figure 1.8: Double-Sided silicon Strip Detectors implementation.

The key parameters of the strip system that will drive the design of the front-end electronics are summarized in Table 1.1.

| Parameter                            | Value                        |

|--------------------------------------|------------------------------|

| width                                | $\leq 8mm$                   |

| depth                                | $\leq 8mm$                   |

| input pad pitch                      | $\approx 50 \mu m$           |

| channels per front-end               | $2^6 \div 2^8$               |

| rectangular short strips capacitance | < 10 pF                      |

| rectangular log strips capacitance   | < 50 pF                      |

| trapezoidal sensors capacitance      | < 20 pF                      |

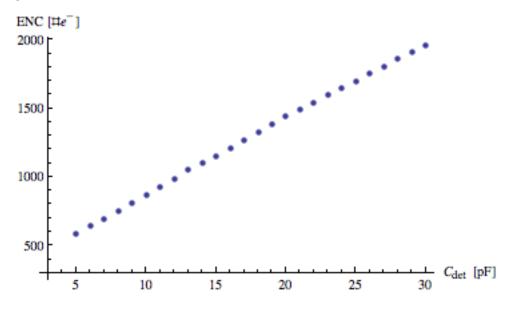

| input ENC with $C_{det} = 10 pF$     | $< 800e^{-}$                 |

| input ENC with $C_{det} = 25pF$      | $< 1000e^{-1}$               |

| dynamic range                        | $240ke^{-} (\approx 38.5fC)$ |

| minimum SNR for MIPS                 | 12                           |

| peaking time                         | $\approx (5 \div 25)  ns$    |

| digitization resolution              | $\geq 8bit$                  |

| overall power dissipation            | < 1W                         |

Table 1.1: Requirements for the strip front-end ASIC.

## Chapter 2

# Front-End Amplifier

The term "front-end" indicates the very input stage in any electronic readout chains for nuclear physics detectors. With this term is usual to intend a combination of two stages: preamplifier and shaper. The first is directly connected to the sensor and it's the first device that process the signal generated by the charge released by the hitting particle, the second, as its name suggests, is responsible to manipulate the signal shape in order to make it easier to analyze it in the following stages. In this chapter we'll focus at first on ideal cases considering linear, time-invariant networks that are simpler to handle using the Laplace transforms; then we will discuss the effects of non-idealities and in the last part we'll approach to the noise calculations.

#### 2.1 The preamplifier

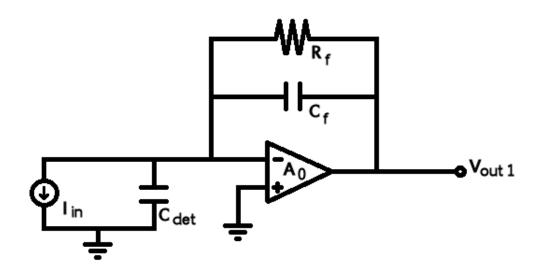

The preamplifier stage is represented by a Charge Sensitive Amplifier. As it's easy to understand from its name, a Charge Sensitive Amplifier (CSA) is the block responsible to amplify the input charge signal. A CSA is built by connecting a capacitor  $C_f$  in the feedback path of a high gain voltage amplifier as shown in Figure 2.1.

Figure 2.1: Charge Sensitive Amplifier implementation.

However, to achieve an appropriate bias point through the negative feedback mechanism, it is necessary to guarantee also a DC path between the output and the input of the amplifier, and this explains the presence of a feedback resistor  $R_f$  in the CSA block. Henceforward, we'll do some basic assumption to study the transfer function of the readout chain:

- The feedback resistor  $R_f$  has a value so high that its contribution to the signal processing can be neglected.

- The input signal can be approximated with a  $\delta$ -like pulse (easier to manage with respect to triangular shaped signals), so  $I_{in}(t) = Q_{in}\delta(t)$ .

- The core amplifier has infinite gain and bandwidth.

Under the assumptions mentioned above, the input-output relationship of the CSA can be written as:

$$V_{out}(t) = \frac{1}{C_f} \int I_{in}(t)dt = \frac{Q_{in}}{C_f} u(t)$$

(2.1)

where u(t) is the unit step function that is the integral of the Dirac- $\delta$ . For the time being, in all the graphics that will be presented the signals will be shifted by a proper amount of time from the origin with the purpose of a better visualization, so we'll use  $\delta(t - t_0)$  and  $u(t - t_0)$ . Adjusting the input charge and the feedback capacitor values in order to obtain an output signal of 1V, the response of the CSA to a  $\delta$ -like pulse is shown in Figure 2.2. To have a 0V baseline, one would have a dual power supply, but in most applications a single rail powering is for system simplicity. This implies that the quiescent point of a circuit is usually different from the ground level. However, this is not relevant for our purposes, therefore we will represent signals starting from a 0V level.

Figure 2.2: Output signal of the CSA with  $\frac{Q_{in}}{C_f} = 1V$ .

#### 2.2 The shaper

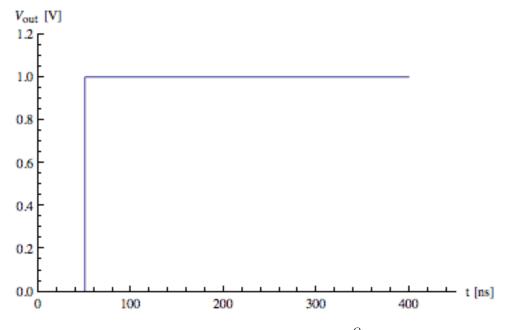

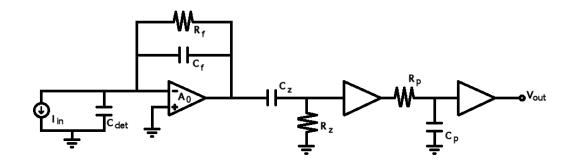

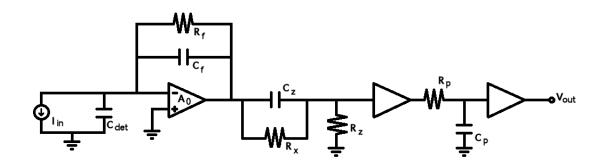

Shaping implies manipulating and altering the frequency content of the original waveform, therefore a pulse shaper is primarily an analog filter [15, 3, 16, 10, 9, 14, 6]. As it is possible to observe in Figure 2.3, the simplest type of pulse shaper consists of two filters separated by a voltage buffer in order to decouple the time constants, while the rightmost buffer allows to drive the load of the following stages. The transfer function of this chain can be written as:

$$V_{out}(s) = \frac{Q_{in}}{sC_f} \cdot \frac{s\tau_z}{1+s\tau_z} \cdot \frac{1}{1+s\tau_p}$$

(2.2)

The first term represent the transfer function of the preamplifier stage, neglecting as assumed the contribute of the feedback resistor  $R_f$ , that is a simple integration stage; the second is the typical input-output relationship of a high-pass filter where  $\tau_z = R_z C_z$  takes the name of derivation time constant, while the third is due to the low-pass filter with  $\tau_p = R_p C_p$  called integration time constant.

Figure 2.3: CR-RC shaping stage.

It is important to observe that the zero at s = 0 introduced by the high-pass filter is cancelled by the pole in the same position due to the CSA stage, because this will become an issue when we'll drop off the hypothesis that  $R_f$  has an infinite value. The signal representation in the time domain, valid for  $\tau_z \neq \tau_p$ , is:

$$V_{out}(t) = \frac{Q_{in}}{C_f} \frac{\tau_z}{\tau_z - \tau_p} \left( e^{-\frac{t}{\tau_z}} - e^{-\frac{t}{\tau_p}} \right)$$

(2.3)

In the particular case  $\tau_z = \tau_p \equiv \tau$  the signal representation in the Laplace and time domain are, respectively:

$$V_{out}(s) = \frac{Q_{in}}{C_f} \frac{\tau}{(1+s\tau)^2}$$

(2.4)

$$V_{out}(t) = \frac{Q_{in}}{C_f} \left(\frac{t}{\tau}\right) e^{-\frac{t}{\tau}}$$

(2.5)

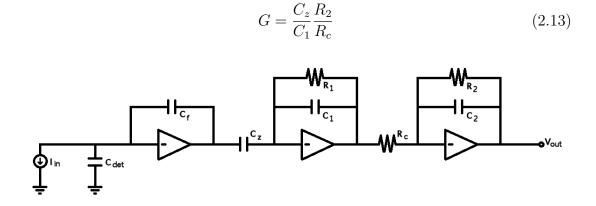

The value of the ratio  $\frac{\tau_p}{\tau_z}$  is a very important parameter since its optimization gets to the best compromise between the signal length and amplitude. If we fix  $\tau_z$  trying different values for  $\tau_p$  we obtain the graphic shown in Figure 2.4: it's easy to observe that the greater is  $\tau_p$  the lower is the signal amplitude whose shape become smoother and smoother. Moreover when  $\tau_p > \tau_z$ , the integration time constant starts to dominate the signal duration, but this is not a surprise since for  $\tau_p \gg \tau_z$  the signal equation becomes:

$$V_{out}(t) \approx \frac{Q_{in}}{C_f} \left(\frac{\tau_z}{\tau_p}\right) e^{-\frac{t}{\tau_p}}$$

(2.6)

with  $\tau_p$  playing the role of the decay time constant.

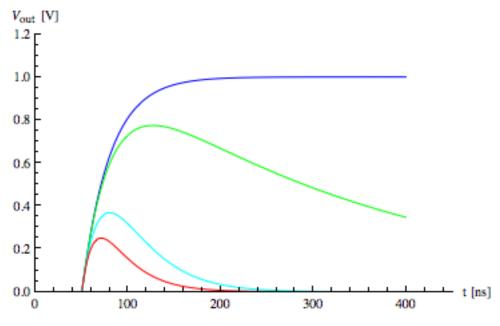

Figure 2.4: Optimization of  $\frac{\tau_p}{\tau_z}$ : fixed  $\tau_z = 30ns$ .

The next step is to fix  $\tau_p$  varying  $\tau_z$ , in this case the results are shown in Figure 2.5. The most interesting observation is for  $\tau_z = \infty$ , that is when there is no derivation of the signal as we can see from the equation below:

$$V_{out}(t) = \frac{Q_{in}}{C_f} \left( 1 - e^{-\frac{t}{\tau_p}} \right)$$

(2.7)

in this case the step at the CSA output is a smoother signal with a 10% to 90% rise time of ~  $2.2\tau_p$  assuming  $\frac{Q_{in}}{C_f} = 1V$ . Decreasing  $\tau_z$  the signals starts to be cut cut both in amplitude and duration and when  $\tau_z < \tau_p$  the slower time constant dominates the return of the signal to the baseline and only the amplitude is reduced.

According to these results,  $\frac{\tau_p}{\tau_z} = 1$  represent the best choice for the time constant values, in fact for a specific pulse duration this is the configuration that maximize the signal amplitude, so henceforward we'll consider only the case with  $\tau_z = \tau_p \equiv \tau$ . The time constant  $\tau$  plays a key role in the signal processing as we can observe solving the following equation:

$$\frac{\partial V_{out}(t)}{\partial t} = \frac{\partial}{\partial t} \left[ \frac{Q_{in}}{C_f} \left( \frac{t}{\tau} \right) e^{-\frac{t}{\tau}} \right] = \frac{Q_{in}}{C_f} \left( \frac{1}{\tau} e^{-\frac{t}{\tau}} - \frac{t}{\tau^2} e^{-\frac{t}{\tau}} \right) = 0$$

(2.8)

the solution to this equation gives the time at which the signal reaches its maximum value, that is its peaking time  $T_p = \tau$ . The peak of the output signal is obtained by the following expression:

$$V_{out,max} = V_{out}(\tau) = \frac{Q_{in}}{C_f} \frac{1}{e}$$

(2.9)

If necessary, the gain loss equal to  $\frac{1}{e}$  can be recovered adjusting the gain of one of the buffers of the shaping block (Figure 2.3).

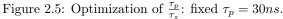

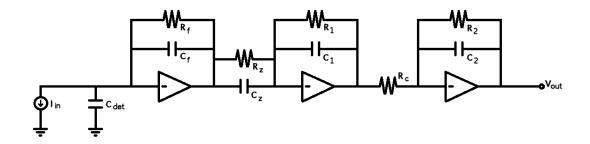

Another way to implement the shaping stage is to use two transimpedence amplifiers as shown in Figure 2.6. In this configuration we can notice a first difference with respect to the architecture mentioned above, that is the absence of any buffer stage to decouple the filters time constants since the low output impedance of the voltage amplifier is exploited to provide it. The transfer function of this chain is:

$$V_{out}(s) = \frac{Q_{in}}{C_f} \frac{C_z}{C_1} \frac{R_2}{R_c} \frac{\tau}{(1+s\tau)^2}$$

(2.10)

with  $\tau = R_1 C_1 = R_2 C_2$ . The signal expression in the time domain is then:

$$V_{out}(t) = \frac{Q_{in}}{C_f} \frac{C_z}{C_1} \frac{R_2}{R_c} \left(\frac{t}{\tau}\right) e^{-\frac{t}{\tau}}$$

(2.11)

and even in this case we found the relationship  $T_p = \tau$  with:

$$V_{out,max} = V_{out}(\tau) = \frac{Q_{in}}{C_f} \frac{C_z}{C_1} \frac{R_2}{R_c} \frac{1}{e}$$

(2.12)

where it's easy to observe a key difference with respect to the result obtained with a passive network, that is the presence of an additional gain given by:

Figure 2.6: CR-RC shaping stage implemented with TIAs (TransImpedence Amplifiers).

#### **2.2.1** $CR-(RC)^n$ shapers

The study we made so far can be used to explore the effects of adding other low-pass filtering stages, in order to modify the signal shape according to the informations of interest we want to extrapolate. The transfer function of such configuration can be written as:

$$V_{out}(s) = \frac{Q_{in}}{C_f} \frac{\tau}{(1+s\tau)^{n+1}}$$

(2.14)

where  $\tau = R_z C_z = R_{p1} C_{p1} = R_{p2} C_{p2} = \ldots = R_{pn} C_{pn}$  since the considerations about the filters time constant made above are still valid. We can notice that the signal expression in the Laplace domain has n+1 poles: 1 introduced by the high-pass filter and the remaining n given by the n low-pass filters. This result is referred to a structure like that of Figure 2.3, but is valid also if we consider an architecture such as that of Figure 2.6 as long as we add the gain factor  $\frac{C_z}{C_1} \frac{R_2}{R_c}$ . The chain pulse response in the time domain is given by:

$$V_{out}(t) = \frac{Q_{in}}{C_f} \frac{1}{n!} \left(\frac{t}{\tau}\right)^n e^{-\frac{t}{\tau}}$$

(2.15)

By solving the following equation we can easily obtain the expression of the peaking time  $T_p$ :

$$\frac{\partial V_{out}(t)}{\partial t} = \frac{\partial}{\partial t} \left[ \frac{Q_{in}}{C_f} \frac{1}{n!} \left( \frac{t}{\tau} \right)^n e^{-\frac{t}{\tau}} \right] =$$

$$= \frac{Q_{in}}{C_f} \frac{1}{n!} \left[ \frac{n}{\tau} \left( \frac{t}{\tau} \right)^{n-1} e^{-\frac{t}{\tau}} - \left( \frac{t}{\tau} \right)^n \frac{1}{\tau} e^{-\frac{t}{\tau}} \right] = 0 \Longrightarrow T_p = n\tau \qquad (2.16)$$

so it's easy to dimension the components of the low-pass filters in order to obtain the desired peaking time and maximum amplitude voltage according to the following relationship:

$$V_{out,max}(n) = V_{out}(n\tau) = \frac{Q_{in}}{C_f} \frac{n^n}{n!} e^{-n}$$

(2.17)

For a better understanding of this kind of architecture, we'll study two different cases:

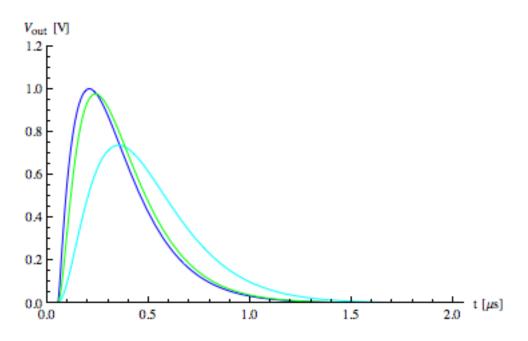

1. Increasing n without changing  $\tau$ Assuming that  $\frac{Q_{in}}{C_f} = 1V$  we obtain as result the plots shown in Figure 2.7. We can notice that increasing n we have: higher peaking time, lower signal amplitude (that could anyway be adjusted by a proper additional gain), higher symmetry in signal shape. However, the amplitude attenuation is less remarkable in the transition  $n \to n+1$  as we can notice observing the following expression:

$$\lim_{n \to \infty} \frac{V_{out,max}(n+1)}{V_{out,max}(n)} = \lim_{n \to \infty} \left(1 + \frac{1}{n}\right)^n \frac{1}{e} = e \cdot \frac{1}{e} = 1$$

(2.18)

which implies that the amplitude drop stops for shapers of really high order.

Figure 2.7: CR- $(RC)^n$  with  $\tau = 30ns$ .

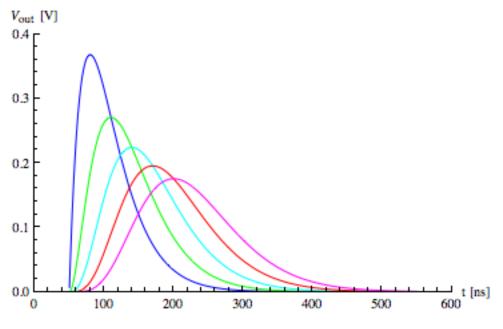

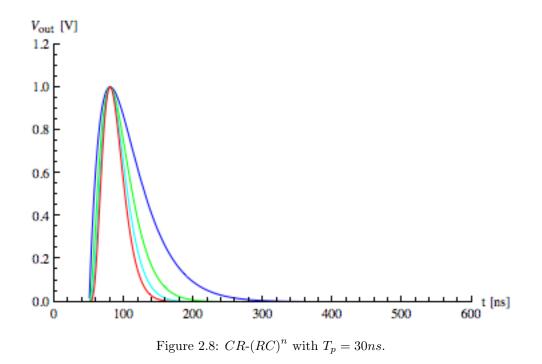

#### 2. Increasing n adjusting $\tau$ to have the same $T_p$

In this case we fix a certain value for  $T_p$ , so the time constant value will be  $\tau = \frac{T_p}{n}$ . The results of a n swing from 1 to 4 is shown in Figure 2.8, where the amplitudes have been normalized to 1V. The most interesting observation is that the higher is n, the faster is the signal return to the baseline value, but this doesn't surprise since increasing n both the derivation and integration time constants get shorter. In other words, higher order shapers allow for a faster signal with no drawback in terms of peaking time, so they represent a better choice for high rate applications.

#### 2.3 Non-ideal behavior

As stated in Section 2.1, all the results obtained so far are valid under certain condition reported below:

- The feedback resistor  $R_f$  has a value so high that its contribution to the signal processing can be neglected.

- The input signal can be approximated with a  $\delta$ -like pulse (easier to manage with respect to triangular shaped signals), so  $I_{in}(t) = Q_{in}\delta(t)$ .

- The core amplifier has infinite gain and bandwidth.

In this Section we'll discuss what happens when we drop off this assumptions.

#### 2.3.1 Finite feedback resistor effects

When a finite value of  $R_f$  is considered, the total impedance in the feedback path of the CSA is given by:

$$Z_f = \frac{R_f}{1 + sR_fC_f} \tag{2.19}$$

As a result, the full transfer function modify into the following expression:

$$V_{out}(s) = \frac{Q_{in}}{C_f} \frac{\tau_f}{1 + s\tau_f} \cdot \frac{s\tau}{1 + s\tau} \cdot \frac{1}{1 + s\tau}$$

(2.20)

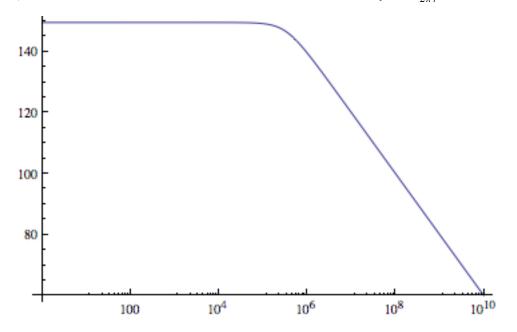

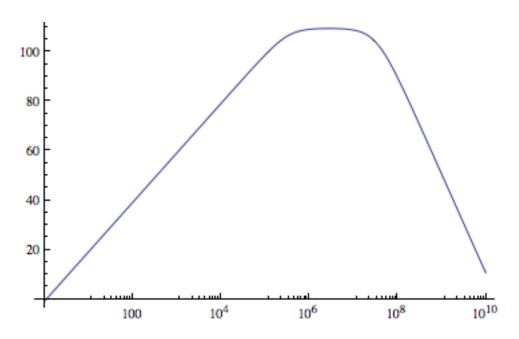

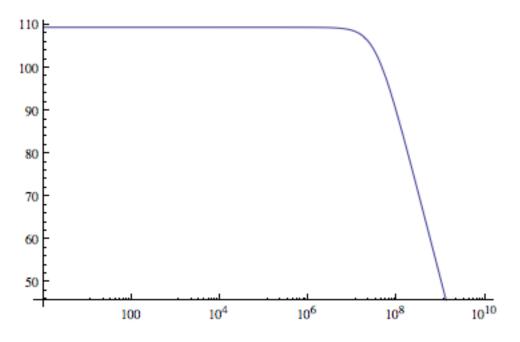

where  $\tau_f = R_f C_f$  is the time constant associated to the feedback network of the CSA. As in the previous section, for simplicity we'll consider an architecture like that of Figure 2.3 and a simple CR-RC shaping stage, but the results could be easily applied to the already studied cases. The most remarkable consequence of the finite value of  $R_f$  is the displacement of the preamplifier pole from  $s_{CSA} = 0$  to  $s_{CSA} = -\frac{1}{\tau_f}$  avoiding the cancellation with the zero at  $s_{hp} = 0$  introduced by the high-pass filter of the shaping stage. The effects of both these modifications in the transfer function can be observed considering the Bode plots of the CSA and of the full chain, shown in Figure 2.9 and Figure 2.10. From the first Bode plot, the one of the preamplifier stage, we can notice the first order low-pass filter behavior of the CSA: after the cut-off frequency  $f_{CSA} = \frac{1}{2\pi\tau_f}$  the gain drops with a slope of 20dB/decade. Studying the second Bode plot, regarding the full front-end chain, is evident a band-pass filter behavior: since the zero has been left in the origin, the gain rises with a slope of 20dB/decade, after the cut-off frequency  $f_{CSA}$  the effect of the zero is cancelled and the gain remains constant until the roll-off of 40dB/decade due to the double pole at the frequency  $f_{Shaper} = \frac{1}{2\pi\tau}$ .

Figure 2.9: Bode plot of a CSA with finite feedback resistor  $R_f = 30M\Omega$  and feedback capacitor  $C_f = 100 f F$ .

Figure 2.10: Bode plot of a CR-RC shaper with finite feedback resistor  $R_f = 30M\Omega$ , feedback capacitor  $C_f = 100 fF$  and shaping time  $\tau = 30ns$ .

This "new" situation have both advantages and drawbacks: the low-pass filter behavior of the CSA leads to the suppression of DC impact and slow variations occurring in the CSA, on the other hand it may cause undesired consequences on the signal shape. These considerations become clear if we consider the signal expression in the time domain reported below:

$$V_{out}(t) = \frac{Q_{in}}{C_f} \frac{\tau_f}{\tau_f - \tau} \left[ \left( \frac{t}{\tau} \right) e^{-\frac{t}{\tau}} + \frac{\tau}{\tau_f - \tau} \left( e^{-\frac{t}{\tau}} - e^{-\frac{t}{\tau_f}} \right) \right]$$

(2.21)

For a better understanding of the above relationship it's more useful to consider the case with  $\tau_f \gg \tau$ :

$$V_{out}(t) \approx \frac{Q_{in}}{C_f} \left[ \left( \frac{t}{\tau} \right) e^{-\frac{t}{\tau}} - \left( \frac{\tau}{\tau_f} \right) e^{-\frac{t}{\tau_f}} \right] = \left[ V_{out}(t) \right]_{R_f = \infty} - \frac{Q_{in}}{C_f} \left( \frac{\tau}{\tau_f} \right) e^{-\frac{t}{\tau_f}}$$

(2.22)

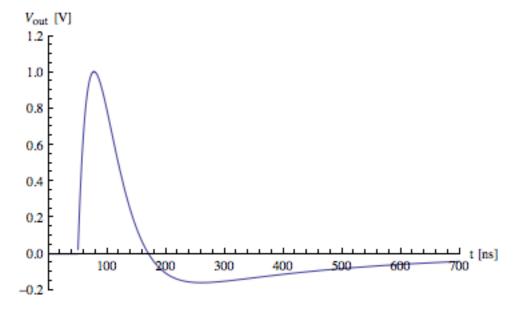

In this case it's easier to see the introduction of a negative term, the rightmost, that is subtracted to the main signal  $\begin{bmatrix} V_{out}(t) \end{bmatrix}_{R_f=\infty}$ . The pulse response to such a configuration is reported in Figure 2.11 that shows how the output signal goes well below the baseline value before it comes back to the 0V level in a time scale

defined by  $\tau_f$ . This negative tail takes the name of undershoot and if it lasts for a significant time the rate capability of the system might be compromised.

Figure 2.11: CR-RC pulse response with finite CSA feedback resistor.

This phenomenon is due to the presence of  $C_z$ , this capacitor connected in series to the CSA filters any DC component coming from this stage that, as a result, cannot intervene on the DC voltage level at the shaper output. Considering this, we can understand the appearance of the undershoot since the bipolar nature of the signal comes from the necessity to have a null contribution to the output DC value coming from the shaper. The most important effect of the undershoot is the baseline drift at high rates shown in Figure 2.12: the baseline value moves downwards until it reach a new voltage level the gives a zero average value of the output. This situation is referred to input signals with a constant rate, so does not occur in realistic physics cases where the signals produced by a sensor are randomly distributed in time, usually according to the Poisson statistics, generating baseline up and down fluctuations rather then the drift to a constant value. For a better understanding of this phenomenon, that needs to be mastered to avoid it's undesired effects, is useful to study what happens in the case  $t \gg \tau$  when the undershoot signal can be approximated as:

$$V_{undershoot}(t) \approx -\frac{Q_{in}}{C_f} \left(\frac{\tau}{\tau_f}\right) e^{-\frac{t}{\tau_f}}$$

(2.23)

This relationship shows that increasing  $\tau_f$  leads to two effects: reduction of the undershoot amplitude, increase of its duration. The reduction of the undershoot

amplitude, obtained increasing the value of  $R_f$ , does not prevent the baseline drift, that is generated by the AC coupling between the preamplifier and the shaper stages, but it worsen instead the rate capability since the constant drift value is reached in a significant longer time.

Figure 2.12: Example of baseline drift induced by a train of pulses with constant rate.

#### 2.3.1.1 Pole-Zero Cancellation

The first solution to the undershoot issue is to move the zero introduced by the high-pass filter of the shaper in order to have  $s_{hp} = s_{CSA} = -\frac{1}{\tau_f}$ . The technique used to achieve this consists in connecting a resistor  $R_x$  in parallel to the capacitor  $C_z$  as shown in Figure 2.13.

Figure 2.13: Pole-Zero Cancellation.

The new transfer function will be:

$$V_{out}(s) = \frac{Q_{in}}{C_f} \frac{\tau_f}{1 + s\tau_f} \cdot \frac{R_z \left(1 + sC_z R_x\right)}{R_z \left(1 + sC_z R_x\right) + R_x} \cdot \frac{1}{1 + s\tau}$$

(2.24)

Looking at this relationship, it's obvious that if  $R_x = \frac{C_f}{C_z}R_f$  the zero in  $s_{hp} = -\frac{1}{C_z R_x}$  is cancelled with the pole in  $s_{CSA} = -\frac{1}{\tau_f}$  obtaining the expression:

$$V_{out}(s) = \frac{Q_{in}}{C_f} \frac{\tau_{hp}}{1 + s\tau_{hp}} \frac{1}{1 + s\tau}$$

(2.25)

where

$$\frac{1}{\tau_{hp}} = \frac{1}{\tau} + \frac{1}{\tau_f}$$

(2.26)

define a new pole in  $s_{hp} = -\frac{1}{\tau_{hp}}$ . It's interesting to notice that if we want to match the derivation and the integration time constants, we need to put  $R_p C_p = \tau_{hp}$ rather then  $R_p C_p = \tau$ , but this issue does not occur if we use a chain like that of Figure 2.6 and operate a pole-zero cancellation by connecting a resistor  $R_x$  in parallel to  $C_z$  as shown in Figure 2.14.

Figure 2.14: Pole-Zero Cancellation with a CR-RC shaper implemented through TIAs.

In this case the total transfer function is:

$$V_{out}(s) = \frac{Q_{in}}{C_f} \frac{C_z}{C_1} \frac{R_2}{R_c} \frac{\tau}{(1+s\tau)^2}$$

(2.27)

that is exactly the same obtained in the ideal case  $R_f = \infty$ , leading of course to the same expression in the time domain. As shown in Figure 2.15, the Bode plot of the entire chain highlights a strict low-pass filter behavior, so any signal starting from DC is amplified. A interesting study regards the comparison between the CSA output signal and the total output signal when a train of pulses with constant rate is sent as input. The result is shown in Figure 2.16: there is a significant baseline drift on the CSA output, which however doesn't occur at the end of the chain. This phenomenon found it's explanation observing that the current signal presented as input to the shaper is nothing but a replica of the sensor signal scaled by the factor

$$\frac{C_z}{C_f} = \frac{R_f}{R_z} \tag{2.28}$$

In other words, the combination of CSA and pole-zero cancellation network works as a fast current amplifier.

Figure 2.15: Bode plot of a CR-RC shaper with pole-zero cancellation.

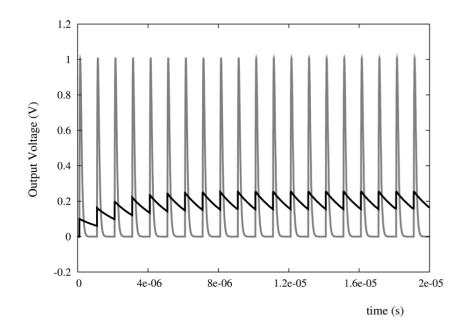

Figure 2.16: CSA and CR-RC shaper, with pole-zero cancellation, response to a train of pulses with constant rate.

#### 2.3.1.2 Baseline Holder

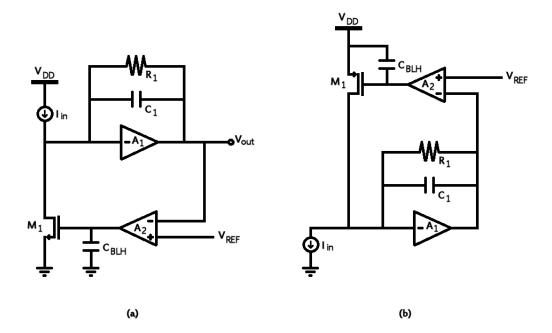

As observed in the last part of the previous subsection, the circuit of Figure 2.14 behave as a low-pass filter, so it is sensitive to DC or low frequency variations occurring at its input. For many applications, such as semiconductor detectors, this can represent a serious issue considering that a silicon sensor has an intrinsic leakage current that must be absorbed by the front-end without compromising the system performance. The detector leakage current may also increase because of the exposition to radiation fields the damage the device bulk leading to a significant worsening, from common values of  $\sim$ nA even to  $\sim$  $\mu$ A per channel. To overcome this problem an AC coupling between the different stages is necessary. The simplest way to achieve an AC coupling is a capacitor connected in series in the path from one block to the following one, however in many cases this wouldn't be enough and a more elaborated technique is required. The first solution is an architecture called Baseline Holder, shown in Figure 2.17.

Figure 2.17: Baseline Holder: (a) implementation with nMOS; (b) implementation with pMOS.

To understand the way it works, let's consider for example the schematic (b): without the Baseline Holder a negative input current, like that drawn in Figure 2.17 (b), would flows in  $R_1$  raising the output voltage. Therefore, the input of the Baseline Holder differential amplifier, given by  $V_{BL} - V_{out}$ , decreases leading to a lower gate voltage for  $M_1$  that reacts increasing the current it pushes into the input node. Through this mechanism it is possible to hold the baseline voltage value  $V_{BL}$ , as long as the loop gain is properly high. The Baseline Holder block can be considered as a single transconductance amplifier, with gain  $G_m = A_{d2}g_{m1}$ where  $A_{d2}$  is the differential voltage gain of  $A_2$  and  $g_{m1}$  is the transconductance of  $M_1$ . At this point we can proceeds with a more quantitative analysis. Let's suppose that  $A_2$  has a transfer function like the following one:

$$A_{d2}(s) = \frac{(A_{d2})_0}{1 + s\tau_2} \tag{2.29}$$

The capacitor  $C_{BLR}$  is necessary to limit the differential stage bandwidth since we want only low frequency signals to be processed by the additional feedback loop. The Baseline Holder gain  $G_m$  can be rewritten exploiting the transfer function expression:

$$G_m(s) = A_{d2}(s)g_{m1} = \frac{(A_{d2})_0 g_{m1}}{1 + s\tau_2} = \frac{G_{m0}}{1 + s\tau_2}$$

(2.30)

where  $G_{m0}$  is the overall low frequency transconductance gain. A first assumption that simplifies the study of the circuit is  $\tau_2 \gg \tau_1 = R_1 C_1$  since in this case we can neglect the capacitive part of the feedback impedance of  $A_1$  and consider only the resistive one. Considering the input node of  $A_1$  as a virtual ground, the input node equation can be written as:

$$I_{in} + \frac{V_{BL} - V_{out}}{R_1} - I_{BLH} = 0 \Longrightarrow I_{in} = I_{BLH} + \frac{V_{out}}{R_1}$$

(2.31)

The  $I_{BLH}$  current of the Baseline Holder can be written as:

$$I_{BLH} = G_m V_{out} \tag{2.32}$$

leading to the input-output relationship of the circuit that is reported below:

$$\frac{V_{out}}{I_{in}} = \frac{R_1}{1 + G_m R_1} = \frac{R_1}{1 + \frac{G_{m0}R_1}{1 + s\tau_2}} = \frac{R_1}{1 + G_{m0}R_1} \frac{1 + s\tau_2}{1 + s\frac{\tau_2}{1 + G_{m0}R_1}} = \frac{R_1}{1 + G_{m0}R_1} \frac{1 + s\tau_2}{1 + s\tau_{BLH}}$$

(2.33)

with

$$\tau_{BLH} = \frac{\tau_2}{1 + G_{m0}R_1} \tag{2.34}$$

that represents the pole introduced by the Baseline Holder. It's interesting to observe that in the case s = 0, that is the low frequency case, the above expression turns into the following one:

$$\frac{V_{out}}{I_{in}} = \frac{R_1}{1 + G_{m0}R_1} \tag{2.35}$$

To appreciate the task performed by the Baseline Holder, it's necessary to make a numerical example: assuming that  $R_1 = 100k\Omega$ ,  $g_{m1} = 100\mu S$  and  $(A_{d2})_0 = 10000$  the low frequency gain is equal to  $1\Omega$  and it means that a DC input variation of  $1\mu A$  produces a change in the output voltage of  $1\mu V$  rather than the 100mV obtained without the additional feedback. For s > 0 the zero at the frequency  $f_2 = \frac{1}{2\pi\tau_2}$  produce a rising edge with a slope of 20dB/decade until the pole at  $f_{BLH} = \frac{1}{2\pi\tau_{BLH}}$  is found. Above the pole frequency, we can use the approximation  $G_{m0}R_1 \gg 1$ , so the gain expression can be written as:

$$\frac{V_{out}}{I_{in}} \approx \frac{R_1}{G_{m0}R_1} \frac{s\tau_2}{\frac{s\tau_2}{1+G_{m0}R_1}} = R_1$$

(2.36)

This result shows that high frequency signals are amplified by  $R_1$ . This separation in frequency is really important since the  $G_m$  feedback have to compensate only the undesired DC, or close to DC, components. The last study we are interested to do regards the Baseline Holder response to a sudden change in the input DC current. Representing the current variation in the Laplace domain as  $I_{in}(s) = \frac{I_{in0}}{s}$ , that is the Laplace transformation of a step in the time domain, and neglecting the time constant  $\tau_1 = R_1 C_1$ , the transfer function of the circuit is:

$$V_{out}(s) = \frac{I_{in0}}{s} \frac{R_1}{1 + G_{m0}R_1} \frac{1 + s\tau_2}{1 + s\tau_{BLH}}$$

(2.37)

that corresponds to a signal in the time domain like the following one:

$$V_{out}(t) = \frac{R_1 I_{in0}}{1 + G_{m0} R_1} \left[ \left( \frac{\tau_2 - \tau_{BLH}}{\tau_{BLH}} \right) e^{-\frac{t}{\tau_{BLH}}} + 1 \right]$$

(2.38)

Considering the case with  $\tau_2 \gg \tau_{BLH}$  the above relationship becomes:

$$V_{out}(t) \approx I_{in0} \left( R_1 e^{-\frac{t}{\tau_{BLH}}} + \frac{R_1}{1 + G_{m0}R_1} \right)$$

(2.39)

that shows well that for t = 0 is fully amplified by  $R_1$ . Then the first term decays exponentially to zero with  $\tau_{BLH}$  as time constant, obtaining the already studied suppressed DC gain represented by the second term. Therefore  $\tau_{BLH}$  defines the time-scale that the system needs to recover the baseline value after a sudden input change. Another important consideration regards the DC loop gain  $G_{m0}R_1$ that defines both the position of the pole, through  $\tau_{BLH}$ , and the low frequency attenuation. In a more realistic case we have to consider the contribution of the feedback capacitance  $C_1$ , so that the transfer function turns into the following expression:

$$\frac{V_{out}}{I_{in}} = \frac{R_1 \left(1 + s\tau_2\right)}{s^2 \tau_1 \tau_2 + s \left(\tau_1 + \tau_2\right) + 1 + G_{m0} R_1}$$

(2.40)

obtained replacing  $R_1$  with the complex impedance

$$Z_1 = \frac{R_1}{1 + sR_1C_1} = \frac{R_1}{1 + s\tau_1} \tag{2.41}$$

The first important observation is that we have a second order transfer function, this means that in principle it could contains also complex poles leading to the circuit instability. To avoid this possible issue we need to impose that:

$$(\tau_1 + \tau_2)^2 > 4\tau_1\tau_2 (1 + G_{m0}R_1)$$

(2.42)

Supposing that  $\tau_2 \gg \tau_1$  and  $G_{m0}R_1 \gg 1$  the above condition becomes:

$$\tau_2 > 4\tau_1 G_{m0} R_1 \tag{2.43}$$

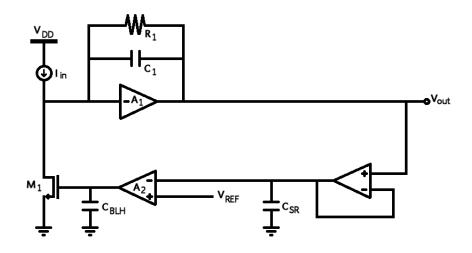

that gives a relationship between the low frequency time constant  $\tau_2$ , the shaping time constant  $\tau_1$  and the loop gain  $G_{m0}R_1$ . Such a structure offers two main advantages with respect to the use of a simple capacitance to perform the AC coupling: the cut-off frequency can be set by a proper chose of the current to be injected in the differential stage or by sizing the capacitor  $C_{BLH}$ ; moreover we can lock the output DC voltage in order to exploit the full dynamic range and to couple this stage with the following ones. A drawback of this architecture is that since the transfer function of the stage shows that it works like a high-pass filter, an undershoot occurs when it is driven by unipolar signals leading to the already discussed phenomenon of the baseline drift. The solution consists in an additional non-linerar network providing a severe slew-rate limitation [7], made by a unity gain buffer dumped by a capacitor at the output (Figure 2.18), whose purpose is to distinguish between fast pulses (which must be left unaffected by the Baseline Holder) and slow variations (that we need to compensate through the Baseline Holder).

Figure 2.18: Baseline Holder with slew-rate limitation.

## 2.3.2 Sensor signal variation effects

Depending on the detector size and geometry, the signal produced by an hitting particle may have a quite complicated shape since the charge collection time is finite. A simple, but still significant, example useful to understand the effects of sensor signal shape consists in the use of an input current pulse that follows an exponential law, such as the one reported below:

$$I_{in}(t) = I_0 e^{-\frac{t}{\tau_c}}$$

(2.44)

In this case, the total charge delivered by the pulse will be:

$$Q_{in} = \int_0^\infty I_0 e^{-\frac{t}{\tau_c}} dt = I_0 \tau_c$$

(2.45)

where  $I_0$  is the peak current and  $\tau_c$  is the time constant representing the charge collection time. The Laplace transform of such a current pulse is given by:

$$I_{in}(s) = \frac{I_0 \tau_c}{1 + s \tau_c} \tag{2.46}$$

The transfer function of a CR-RC shaper considering that the input is not anymore a Dirac  $\delta$ -like pulse becomes:

$$V_{out}(s) = \frac{I_0 \tau_c}{C_f (1 + s\tau_c)} \cdot \frac{\tau}{(1 + s\tau)^2}$$

(2.47)

The signal expression in the time domain will be:

$$V_{out}(t) = \frac{Q_{in}}{C_f} \left[ \frac{t}{\tau - \tau_c} e^{-\frac{t}{\tau}} + \frac{\tau_c}{\left(\tau - \tau_c\right)^2} \left( e^{-\frac{t}{\tau_c}} - e^{-\frac{t}{\tau}} \right) \right]$$

(2.48)

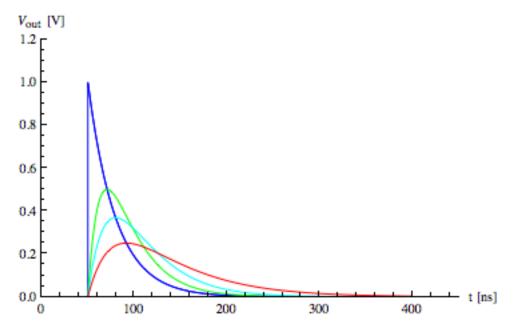

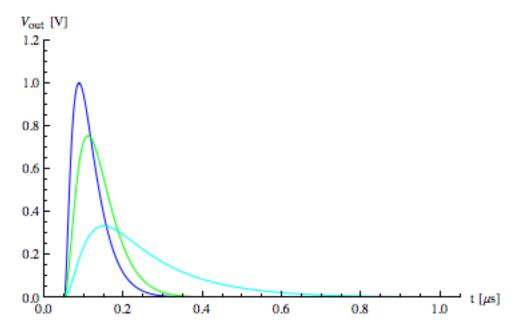

A interesting analysis can be performed by sweeping  $\tau_c$  adjusting  $I_0$  in order to have  $Q_{in} = const$ . Figure 2.19 shows that the circuit response when  $\tau_c \ll \tau$  is the same observed with a  $\delta$ -like input pulse, in fact the signal expression can be approximated as  $V_{out}(t) \approx \frac{Q_{in}}{C_f} \left(\frac{t}{\tau}\right) e^{-\frac{t}{\tau}}$  that is the result we obtained in the ideal case, but as  $\tau_c$  increases we can see that the peaking time gets longer and the signal amplitude falls down.

Figure 2.19: Response of a CR-RC shaper with  $T_p = 30ns$  to exponential current pulses with different collection times.

We are in presence of a form of ballistic deficit that is an amplitude loss occurring whenever two different mechanisms compete with each other with comparable speed: the signal formation and the reset of the system. It is really important to notice that this effect has been obtained considering a fully noiseless front-end. As we can observe in the Figure 2.20, a solution to this issue is to increase the shaping time  $\tau$ , but the price to pay is the worsening of the circuit rate capability.

Figure 2.20: Response of a CR-RC shaper with  $T_p = 150 ns$  to exponential current pulses with different collection times.

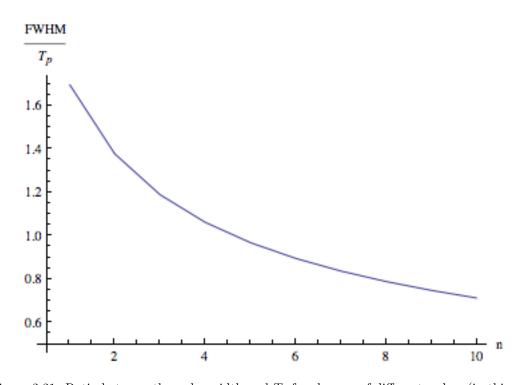

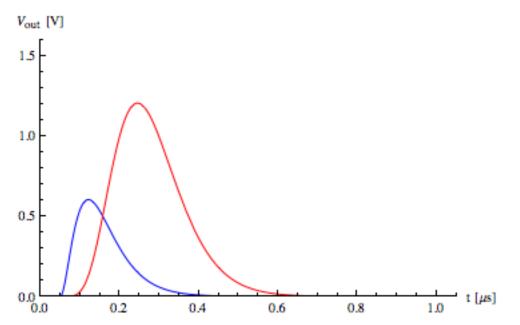

However, we have seen in the previous section that increasing the order of the shaper allows to have bigger peaking time maintaining a restrained signal duration and this is well proved observing the Figure 2.21. The graphic of Figure 2.22 compares the modifications of the pulse responses of a simple CR-RC and a CR-RC<sup>5</sup> shaper in presence of ballistic deficit due to an exponential current pulse input delivering the same charge with a fixed charge collection time  $\tau_c$ : we can notice that with high order filters the signal amplitude loss is smaller [2].

Figure 2.21: Ratio between the pulse width and  $T_p$  for shapers of different orders (in this case we assumed  $T_p=\tau_c=30ns).$

Figure 2.22: Comparison between the response of a CR-RC and a CR- $(RC)^5$  shapers with  $T_p = 30ns$  to exponential current pulses with  $\tau_c = 50ns$ .

There is one more issue related to shape variations in the detector signal depending on the fact that these have a statistic nature. The charge collection time changes on an event by event basis, therefore the same deposited charge may generate signals with different shape and peaking time. A possible solution consists into sampling and integrating the full waveform exploiting the possibility to obtain the output voltage  $V_{out}(t)$  applying the convolution theorem:

$$V_{out}(t) = I_{in}(t) * h(t) = \int_{-\infty}^{\infty} I_{in}(u)h(t-u)du$$

(2.49)

where h(t) is the system response to a  $\delta$ -like pulse. Now we need to calculate the integral of the output signal:

$$\int_{-\infty}^{\infty} V_{out}(t) = \int_{-\infty}^{\infty} I_{in}(t) * h(t)dt = \int_{-\infty}^{\infty} \left[ \int_{-\infty}^{\infty} I_{in}(u)h(t-u)du \right] dt =$$

$$= \int_{-\infty}^{\infty} I_{in}(u) \left[ \int_{-\infty}^{\infty} h(t-u)dt \right] du$$

(2.50)

The above integral can be further processed to obtain

$$\int_{-\infty}^{\infty} V_{out}(t) = \left[\int_{-\infty}^{\infty} I_{in}(u) du\right] \left[\int_{-\infty}^{\infty} h(t) dt\right] = Q_{in} \int_{-\infty}^{\infty} h(t) dt$$

(2.51)

which proves that integrating the output signal give us an information about the total charge.

## 2.3.3 Gain and bandwidth limitations in CSAs

The last case we need to discuss regards the effects of a charge sensitive amplifier with limited gain and bandwidth.

## 2.3.3.1 Effects of finite gain

For our purpose, we can study the effects of a finite gain of the CSA neglecting the contribution of the feedback resistor  $R_f$ . When an amplifier has a finite gain  $A_0$ , the input node cannot be considered anymore as a virtual ground, so that the nodal equation for the input is:

$$I_{in} + V_{in}sC_{det} + [V_{in} - V_{out}]sC_f = 0$$

(2.52)

and since  $V_{out} = -A_0 V_{in} \iff V_{in} = -\frac{V_{out}}{A_0}$ , the input-output relationship is:

$$\frac{V_{out}}{I_{in}} = -\frac{A_0}{s \left[C_{det} + (1 + A_0) C_f\right]}$$

(2.53)

In order to obtain the ideal transfer function of such a state, we need to impose 2 conditions:

- $A_0 \gg 1$

- $(1+A_0) C_f \gg C_{det}$

The Miller theorem allows to split the feedback capacitance  $C_f$  into a capacitance  $C_{f(in)} = (1 + A_0) C_f$  connected between the input node and the ground, and a capacitance  $C_{f(out)} = (1 + \frac{1}{A_0}) C_f$  between the output and the ground. This gives us an interpretation of the second condition, in fact  $C_{det}$  and  $C_{f(in)}$  are connected in parallel, so that the input charge will be:

$$Q_{in} = Q_{det} + Q_{f(in)} = V_{in} \left( C_{det} + C_{f(in)} \right)$$

(2.54)

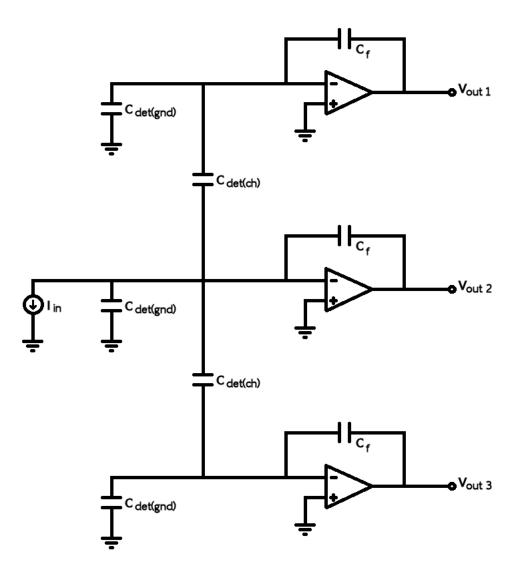

However only  $Q_{f(in)}$  contributes to the signal and that means that the charge  $Q_{det}$  is lost to further processing. Moreover in a multichannel system the capacitance  $C_{det}$  can be seen as the combination of a capacitance  $C_{det(gnd)}$  connected to the ground and an inter-channel capacitance  $C_{det(ch)}$  creating a path between the input node and the two adjacent channels (Figure 2.23) leading to the cross-talk phenomenon.

Figure 2.23: Cross-talk between a channel and the two adjacent one.

# 2.3.3.2 Effects of bandwidth limitation

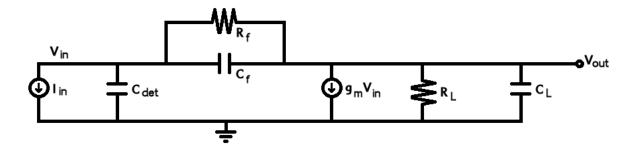

Even in this case, we can neglect the contribution of the feedback resistor. As CSA we can use the model of a simple transistor, so that the small signal equivalent will be that represented in Figure 2.24 where  $R_L$  and  $C_L$  are the equivalent load resistance and capacitance, respectively.

Figure 2.24: Small signal equivalent circuit of a CSA.

To obtain the transfer function we need to solve the following system:

$$\begin{cases} I_{in}(s) + V_{in}(s)sC_{det} + [V_{in}(s) - V_{out}(s)]sC_f = 0\\ g_m V_{in}(s) + [V_{out}(s) - V_{in}(s)]sC_f + V_{out}(s)\left(\frac{1}{R_L} + sC_L\right) = 0 \end{cases}$$

(2.55)

Considering the case with  $R_L \to \infty$ , the system transfer function will be:

$$V_{out}(s) = -\frac{I_{in}(s)\left(1 - s\frac{C_f}{g_m}\right)}{sC_f\left(1 + s\tau_r\right)}$$

(2.56)

where

$$\tau_r = \frac{C_L C_{det} + (C_L + C_{det}) C_f}{g_m C_f}$$

(2.57)

is the rise time constant. The response to a  $\delta$ -like input current in the time domain is given by:

$$V_{out}(t) = -\frac{Q_{in}}{C_f} \left(1 - e^{-\frac{t}{\tau_r}}\right)$$

(2.58)

To better understand the effects of bandwidth limitation, we need to consider two different cases.

1.  $C_{\rm f} \gg C_{\rm L}$

In this case we have that  $\tau_r \approx \frac{C_L + C_{det}}{g_m}$  and assuming to have  $C_{det} \gg C_L$  we can further simplify the expression obtaining  $\tau_r \approx \frac{C_{det}}{g_m}$ . It is important to observe that the speed of the signal is weakly sensitive to the value of  $C_f$  and mainly depends on  $C_{det}$ .

2.  $C_f \ll C_L$ Here we have that  $\tau_r \approx \frac{C_L C_{det}}{g_m C_f}$  so that the signal speed is limited by the ratio  $\frac{C_{det}}{C_f}$ .

For both cases we can observe that limiting the CSA bandwidth leads to an output signal that is not anymore an ideal step reaching the value  $\frac{Q_{in}}{C_f}$  in a null time, but it takes a time  $\tau_r$  to get to that level. In a more realistic case we cannot neglect the feedback resistor  $R_f$  and the transfer function turns into the following expression:

$$V_{out}(s) = \frac{I_{in}(s)R_f}{(1+s\tau_r)(1+s\tau_f)}$$

(2.59)

valid under the assumption that

$$\tau_f = R_f C_f \gg \frac{C_L + C_{det}}{g_m} \tag{2.60}$$

The pulse response in the time domain is then:

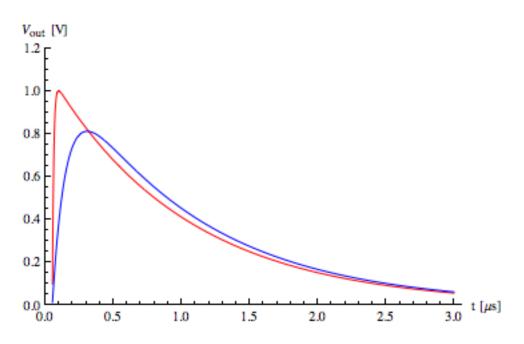

$$V_{out}(t) = \frac{Q_{in}}{C_f} \frac{\tau_f}{\tau_r - \tau_f} \left( e^{-\frac{t}{\tau_r}} - e^{-\frac{t}{\tau_f}} \right)$$

(2.61)

Solving the equation

$$\frac{\partial V_{out}(t)}{\partial t} = 0 \tag{2.62}$$

we can find the signal peaking time:

$$T_p = \frac{\tau_r \tau_f}{\tau_r - \tau_f} ln\left(\frac{\tau_r}{\tau_f}\right)$$

(2.63)

In the end, we can evaluate  $V_{out}(T_p)$  obtaining:

$$V_{out,max} = \frac{Q_{in}}{C_f} \left(\frac{\tau_f}{\tau_r}\right)^{\frac{\tau_r}{\tau_r - \tau_f}}$$

(2.64)

So the step amplitude is modulated by a term depending on the ratio between the feedback time constant  $\tau_f$  and the signal rise time  $\tau_r$ . To have an idea of what kind of modulation are we talking about, if  $\frac{\tau_f}{\tau_r} = 100$  the signal amplitude attains 95.4% of its theoretical value and 99.3% if  $\frac{\tau_f}{\tau_r} = 1000$  (Figure 2.25). This amplitude loss is another example of ballistic deficit, but in this case it is the finite CSA bandwidth that limits the signal formation time rather then the detector.

Figure 2.25: Response of a CSA with finite rise time constant with  $\tau_f = 1\mu s$  in the case of  $\tau_r = 100ns$  (blue curve) and  $\tau_r = 10ns$  (red curve).

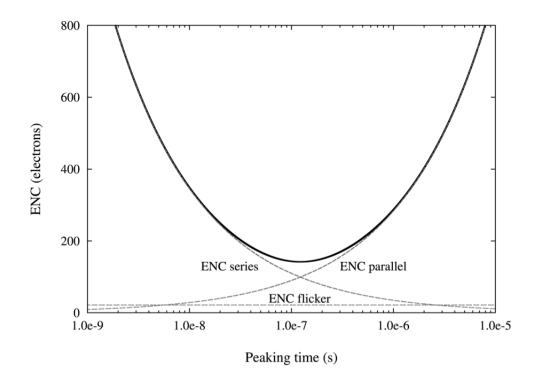

# 2.4 Noise calculations

A key parameter in the design of a front-end for physics detectors is the noise of the system expressed through the Equivalent Noise Charge. The ENC is the number of electrons one would have to collect from a silicon sensor in order to create a signal whose peak corresponds to the rms noise of this sensor. The first step to obtain such an information is to identify the noise sources of the system under analysis and to model them with voltage or current generators. It is usual to refer to a noise source modeled with a voltage generator as "series noise", and as "parallel noise" if we are in presence of a current noise source. The ENC can be expressed through the following expression:

$$ENC = \frac{V_{n(out),rms}}{V_{peack}(Q_{in} = q)} \Longrightarrow [ENC] = number of electrons$$

(2.65)

where  $q = 1.6022 \cdot 10^{-19} C$  is the elementary charge corresponding to 1 electron. So, if we want to evaluate the ENC, we have to calculate the  $V_{n(out),rms}$  that is given by:

$$V_{n(out),rms}^{2} = \int_{0}^{\infty} S_{n}^{2} * |T_{n}(j\omega)|^{2} d\omega$$

(2.66)

with  $S_n^2$  representing the power spectral density associated to a certain noise source, while  $T_n(j2\pi f) = \frac{V_{n(out)}}{V_{n(in)}}$  so that this transfer function might not coincide with the signal transfer function. If we are in presence of more uncorrelated noise sources, the total rms noise is obtained using the expression below:

$$V_{n(out),rms}(tot) = \sqrt{V_{n(out),rms}^2(1) + V_{n(out),rms}^2(2) + \dots + V_{n(out),rms}^2(N)}$$

(2.67)

It is important to notice that all our considerations take into account a system whose output is a voltage, however the method does not change in the case of a system with a current as output.

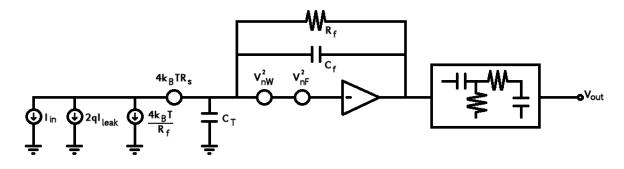

#### 2.4.1 Noise sources in a front-end amplifier

Figure 2.26 shows a front-end amplifier with the equivalent noise generators representing the effects due to different kind of noise. It is important to notice that the voltage noise sources  $V_{nW}^2 \in V_{nF}^2$ , representing the white and the flicker noise respectively, are connected between the input and the output of the CSA (through the feedback path) since they are part of the core amplifier itself.

Figure 2.26: Noise sources in a front-end amplifier.

The generator who plays the role of the white noise can be split into several contributors:

• White noise due to the amplifier input transistor:

$$V_{nW1}^2 = 4k_B T \frac{1}{g_{m1}} \Gamma$$

(2.68)

where  $k_B$  is the Boltzmann constant, T is the absolute temperature,  $g_{m1}$  is the transconductance of the input transistor and  $\Gamma$  is the inversion coefficient that depends on the biasing region of the device.

• White noise due to the parasitic resistance of the gate of the input transistor and any internal resistor in series with the input (represented by  $R_{S,int}$  in the expression below):

$$V_{nW2}^2 = 4k_B T R_{S,int} (2.69)$$

• White noise due to the current source biasing the input stage:

$$V_{nW3}^2 = 4k_B T \frac{g_{m2}}{g_{m1}^2} \Gamma$$

(2.70)

where  $g_{m2}$  is the transconductance of the transistor providing the bias for the input stage.

The expression for the flicker noise, that is the other term representing a noise contribution generated by the amplifier itself, is reported below:

$$V_{nF}^2 = \frac{K_f}{C_{ox}WL} \frac{1}{f} \tag{2.71}$$

where  $K_f$  is a constant for a given device gate length and bias condition,  $C_{ox}$ , W and L are respectively the capacitance of the oxide layer, the width and the length of the input transistor gate, while f is the frequency of the input signal.

The last series noise source is given by the following expression:

$$V_{nR_S}^2 = 4k_B T R_S \tag{2.72}$$

where  $R_S$  represents the contribution due to any external resistance connected in series to the input stage.

As regards the parallel noise sources, modeled as current generators connected in parallel with the input current pulse representing the sensor signal, the main contributions are:

• Parallel noise due to the feedback resistor  $R_f$  of the CSA:

$$I_{nR_f}^2 = \frac{4k_B T}{R_f}$$

(2.73)

it is important to notice that the greater is  $R_f$ , the lower will be its contribution to the noise of the system.

• Parallel noise introduced by any additional current source directly connected to the input stage:

$$I_{nDC}^2 = 4k_B T g_{mDC} \Gamma \tag{2.74}$$

where  $g_{mDC}$  is the transconductance of the transistor implementing the current source providing the DC path to the sensor leakage current or the biasing of the active feedback network in the input stage.

These two terms refer to devices of the front-end amplifier, we have now to describe the contributions to the noise of the system given by the sensor and its biasing network:

• Parallel noise due to the detector leakage current who plays a key role in semiconductor sensors:

$$I_{n,leak}^2 = 2qI_{leak} \tag{2.75}$$

• Noise due to the sensor bias resistance:

$$I_{n,bias}^2 = \frac{4k_BT}{R_{bias}} \tag{2.76}$$

A really important observation is that all the parallel noise sources have white spectral density. Henceforward we will combine all the white series noise sources into one unique term

$$V_{nW}^2 = V_{nW1}^2 + V_{nW2}^2 + V_{nW3}^2$$

(2.77)

and all the white parallel noise sources into

$$I_n^2 = I_{n,leak}^2 + I_{n,bias}^2$$

(2.78)

Moreover the Figure 2.26 shows the presence of a capacitance named  $C_T$  that is given by:

$$C_T = C_{det} + C_f + C_{in} \tag{2.79}$$

where  $C_{det}$  is the detector capacitance,  $C_f$  is the feedback capacitance and  $C_{in}$  is the amplifier input capacitance, so that  $C_T$  represents the sum of all the capacitance seen between the input node and the ground. While for the other capacitances is easy to see that are connected between those two points, it is necessary a clarification as regards  $C_f$  since we have to consider the loading effect produced by the feedback capacitor on the amplifier. According to all these hypothesis, the following subsections will show the analytical calculations of all the main noise contributors for a simple CR-RC shaper generalizing later the results to higher order filters.

## 2.4.2 Noise in a CR-RC shaper

The first contribution we want to study is that of the white series noise corresponding to the voltage generator  $V_{nW}^2$ . The noise voltage is converted into a current by the capacitance  $C_T$  and this current is integrated on the feedback capacitance  $C_f$ :

$$V_{nW(CSA)}^2 = V_{nW}^2 \left(\frac{C_T}{C_f}\right)^2 \tag{2.80}$$

This voltage is then processed by the CR-RC shaper transfer function reported below:

$$T(s) = \frac{s\tau}{\left(1 + s\tau\right)^2} \tag{2.81}$$

According to what we have seen in the previous subsection, we need to make an integration in the frequency domain putting  $s = j\omega \longrightarrow \tau = \frac{1}{\omega_0}$ . Using this formalism, that is exactly the same if we use the frequency f rather than the angular frequency  $\omega$ , the shaper transfer function becomes:

$$T(j\omega) = \frac{j\frac{\omega}{\omega_0}}{\left(1 + j\frac{\omega}{\omega_0}\right)^2}$$

(2.82)

and the noise voltage at the end of the shaper is thus given by:

$$V_{nW(out),rms}^{2} = \frac{1}{2\pi} \int_{0}^{\infty} V_{nW(CSA)}^{2} * |T(j\omega)|^{2} d\omega =$$

$$1_{1} = \frac{1}{2\pi} \int_{0}^{\infty} \frac{\omega^{2}}{1} + \frac{1}{2\pi} \int_{0}^{\infty} \frac{1}{2\pi} \left(\frac{C_{T}}{2}\right)^{2} d\omega =$$

$$= \frac{1}{2\pi} V_{nW}^2 \left(\frac{C_T}{C_f}\right) \int_0^{\infty} \frac{\omega^2}{\left(\omega_0 - \frac{\omega^2}{\omega_0}\right)^2 + 4\omega^2} d\omega = \frac{1}{8} V_{nW}^2 \left(\frac{C_T}{C_f}\right) \omega_0 \qquad (2.83)$$

It is also possible to express the above result as a function of the peaking time  $T_p$ , in fact:

$$\begin{cases} T_p = \tau \\ \tau = \frac{1}{\omega_0} \end{cases} \implies \omega_0 = \frac{1}{T_p}$$

(2.84)

leading to the following relationship:

$$V_{nW(CSA),rms}^{2} = \frac{1}{8} V_{nW}^{2} \left(\frac{C_{T}}{C_{f}}\right)^{2} \frac{1}{T_{p}}$$

(2.85)

Whereas we aim at calculating the ENC, we need the expression of  $V_{peak}(q)$  that in the case of a CR-RC shaper is, as seen in Section 2.2, given by:

$$V_{peak}(q) = \frac{q}{C_f} \frac{1}{e}$$

(2.86)

and finally we obtain:

$$ENC_W = \frac{V_{nW}C_T}{q} \sqrt{\frac{e^2}{8} \frac{1}{T_p}}$$

(2.87)

The main observation is that  $ENC_W \propto C_T \cdot \sqrt{\frac{1}{T_p}}$ , meaning that the ENC due to white noise increases linearly with the total capacitance  $C_T$  and decreases with the square root of the peaking time. The next step is to evaluate the flicker noise whose spectral density is:

$$V_{nF}^2 = \frac{A_f}{f} \tag{2.88}$$

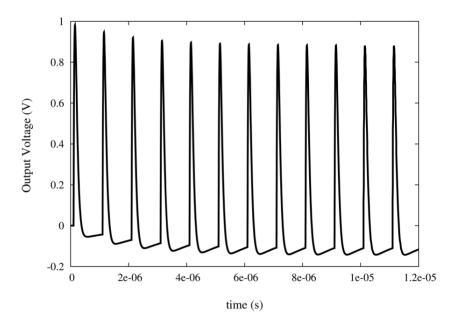

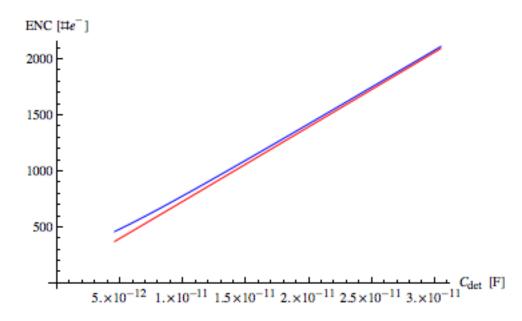

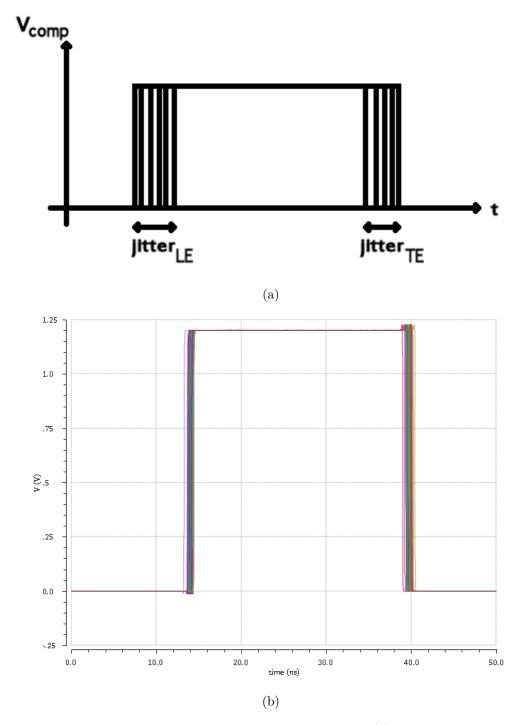

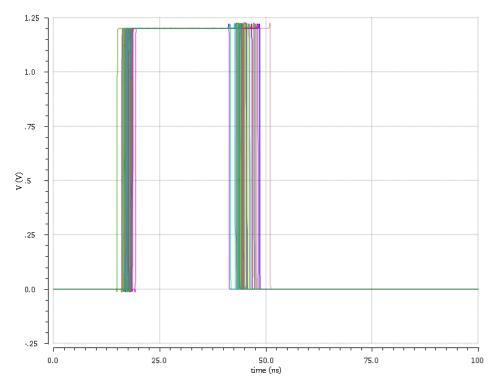

This noise voltage source gives as output of the CSA the following expression: