## UNIVERSITA' DEGLI STUDI DI TORINO DIPARTIMENTO DI FISICA SPERIMENTALE DOTTORATO DI RICERCA IN FISICA CICLO XIX

Settore scientifico-disciplinare FIS/01 FISICA SPERIMENTALE

# DESIGN, TEST AND SYSTEM INTEGRATION OF FRONT-END ELECTRONICS FOR PARTICLE DETECTION IN HIGH-ENERGY NUCLEAR AND SUBNUCLEAR EXPERIMENTS

Tesi Presentata da:

Victor Sorin Martoiu

Relatori: **Prof. Alberta Marzari-Chiesa Dott. Angelo Rivetti** Controrelatore: **Prof. Alberto Aloisio** Coordinatore: **Prof. Stefano Sciuto**

Anni accademici: 2003/2004–2004/2005–2005/2006

© Copyright by Victor Sorin Martoiu, 2007

In memory of my father

# **Table of Contents**

| Ta | Table of Contentsv         |        |                                                                                                                       |      |  |  |  |  |

|----|----------------------------|--------|-----------------------------------------------------------------------------------------------------------------------|------|--|--|--|--|

| A  | ckno                       | wledge | ements                                                                                                                | viii |  |  |  |  |

| In | ntrod                      | uction |                                                                                                                       | 1    |  |  |  |  |

| 1  | Exp                        | oerime | ntal challenges in nuclear and particle physics                                                                       | 4    |  |  |  |  |

|    | 1.1                        | Short  | history of experimental nuclear and particle physics                                                                  | 4    |  |  |  |  |

|    | 1.2                        | Overv  | iew of the present objectives in nuclear and high-energy physics                                                      | 8    |  |  |  |  |

|    |                            | 1.2.1  | Overview of the Standard Model                                                                                        | 8    |  |  |  |  |

|    |                            | 1.2.2  | The search for Higgs Boson.                                                                                           | 10   |  |  |  |  |

|    |                            | 1.2.3  | Inside the hadronic matter                                                                                            | 11   |  |  |  |  |

|    |                            |        | 1.2.3.1 Spin of the nucleon $\ldots$ | 12   |  |  |  |  |

|    |                            |        | 1.2.3.2 Glueballs and hybrids                                                                                         | 13   |  |  |  |  |

|    |                            |        | 1.2.3.3 Charmed quark systems                                                                                         | 14   |  |  |  |  |

|    |                            |        | 1.2.3.4 Hypernuclei                                                                                                   | 16   |  |  |  |  |

|    |                            |        | 1.2.3.5 Phases of nuclear matter $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                         | 17   |  |  |  |  |

|    | 1.3 P326 and CKM mechanism |        |                                                                                                                       |      |  |  |  |  |

|    |                            | 1.3.1  | Background rejection in P326                                                                                          | 24   |  |  |  |  |

|    |                            | 1.3.2  | Experimental setup                                                                                                    | 26   |  |  |  |  |

|    |                            |        | 1.3.2.1 The beam $\ldots$            | 26   |  |  |  |  |

|    |                            |        | 1.3.2.2 The detector $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                          | 26   |  |  |  |  |

|    |                            | 1.3.3  | Gigatracker requirements                                                                                              | 29   |  |  |  |  |

|    | 1.4                        | PANE   | DA and QCD                                                                                                            | 30   |  |  |  |  |

|    |                            | 1.4.1  | Experimental setup                                                                                                    | 32   |  |  |  |  |

|    |                            | 1.4.2  | MVD requirements                                                                                                      | 34   |  |  |  |  |

|    | 1.5                        | ALIC   | E and quark-gluon plasma                                                                                              | 36   |  |  |  |  |

|    |                            | 1.5.1  | QGP probes in heavy-ion collisions                                                                                    | 36   |  |  |  |  |

|          |     | 1.5.2                                                                                                  | The ALICE detector                                     | 38 |  |  |  |  |

|----------|-----|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----|--|--|--|--|

|          |     | 1.5.3                                                                                                  | The Inner Tracking System                              | 41 |  |  |  |  |

|          |     | 1.5.4                                                                                                  | The Silicon Drift Detector subsystem                   | 44 |  |  |  |  |

| <b>2</b> | Sen | miconductor detectors and front-end electronics in high-energy                                         |                                                        |    |  |  |  |  |

|          | phy | sics                                                                                                   |                                                        | 46 |  |  |  |  |

|          | 2.1 | Silicor                                                                                                | 1 detectors                                            | 46 |  |  |  |  |

|          | 2.2 | 2.2 Detector technology $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ |                                                        |    |  |  |  |  |

|          |     | 2.2.1                                                                                                  | Microstrip detectors                                   | 52 |  |  |  |  |

|          |     | 2.2.2                                                                                                  | Silicon drift chambers                                 | 53 |  |  |  |  |

|          |     | 2.2.3                                                                                                  | Pixel detectors                                        | 55 |  |  |  |  |

|          |     | 2.2.4                                                                                                  | Resolution considerations                              | 56 |  |  |  |  |

|          |     | 2.2.5                                                                                                  | Choice of detector topology                            | 61 |  |  |  |  |

|          |     | 2.2.6                                                                                                  | Trends in semiconductor detectors                      | 63 |  |  |  |  |

|          |     |                                                                                                        | 2.2.6.1 Hybrid pixels based on 3D integration          | 63 |  |  |  |  |

|          |     |                                                                                                        | 2.2.6.2 Monolithic pixel detectors                     | 64 |  |  |  |  |

|          |     |                                                                                                        | 2.2.6.3 Active edge 3D detectors                       | 66 |  |  |  |  |

|          | 2.3 | Front-                                                                                                 | end electronics                                        | 67 |  |  |  |  |

|          |     | 2.3.1                                                                                                  | Noise optimization                                     | 67 |  |  |  |  |

|          |     | 2.3.2                                                                                                  | Mixed-signal front-ends                                | 70 |  |  |  |  |

|          |     | 2.3.3                                                                                                  | Radiation tolerance                                    | 71 |  |  |  |  |

|          |     | Scaling effects on the design and performance of front-end elec-                                       |                                                        |    |  |  |  |  |

|          |     |                                                                                                        | tronics                                                | 72 |  |  |  |  |

|          |     |                                                                                                        | 2.3.4.1 Constant-field scaling                         | 73 |  |  |  |  |

|          |     |                                                                                                        | 2.3.4.2 Noise and dynamic range                        | 74 |  |  |  |  |

|          |     |                                                                                                        | 2.3.4.3 Transistor mismatch                            | 76 |  |  |  |  |

|          |     |                                                                                                        | 2.3.4.4 Radiation tolerance                            | 76 |  |  |  |  |

| 3        | Sys | tem in                                                                                                 | tegration of the Silicon Drift Detector (SDD) in ALICE | 78 |  |  |  |  |

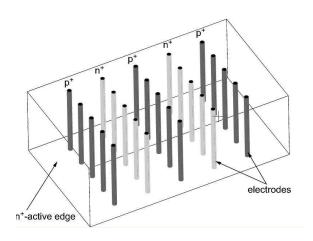

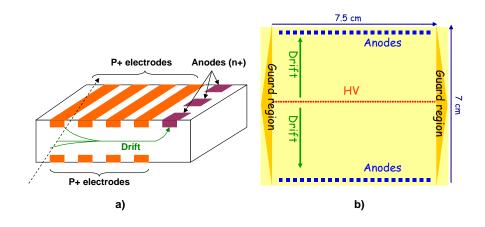

|          | 3.1 | SDD detector                                                                                           |                                                        |    |  |  |  |  |

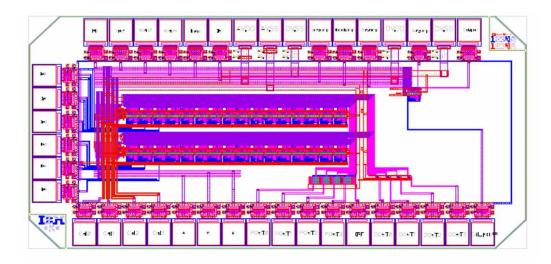

|          | 3.2 |                                                                                                        | end electronics architecture                           | 81 |  |  |  |  |

|          |     | 3.2.1                                                                                                  | PASCAL                                                 | 81 |  |  |  |  |

|          |     | 3.2.2                                                                                                  | AMBRA                                                  | 83 |  |  |  |  |

|          | 3.3 | Syster                                                                                                 | n integration                                          | 84 |  |  |  |  |

|          |     | 3.3.1                                                                                                  | Layout of the SDD system                               | 84 |  |  |  |  |

|          |     | 3.3.2                                                                                                  | Production flow                                        | 86 |  |  |  |  |

|          | 3.4 |                                                                                                        |                                                        |    |  |  |  |  |

|          |     | 3.4.1                                                                                                  | Overview                                               | 88 |  |  |  |  |

|          |     | 3.4.2                                                                                                  | Chipcable, hybrid and module test system               | 92 |  |  |  |  |

## vi

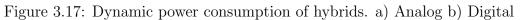

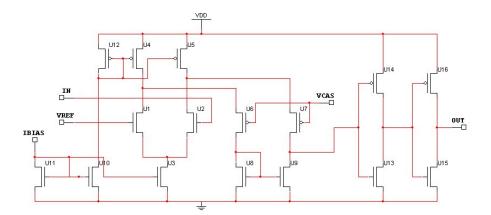

|              |              | 3.4.3 Yield and performance measurements                                       | 96           |

|--------------|--------------|--------------------------------------------------------------------------------|--------------|

| 4            | Des          | ign and test of front-end electronics for MVD pixel detectors in               | L            |

|              | PA           | NDA                                                                            | 101          |

|              | 4.1          | Requirements                                                                   | 101          |

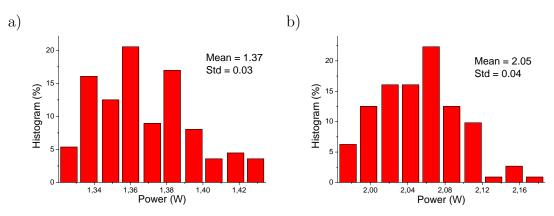

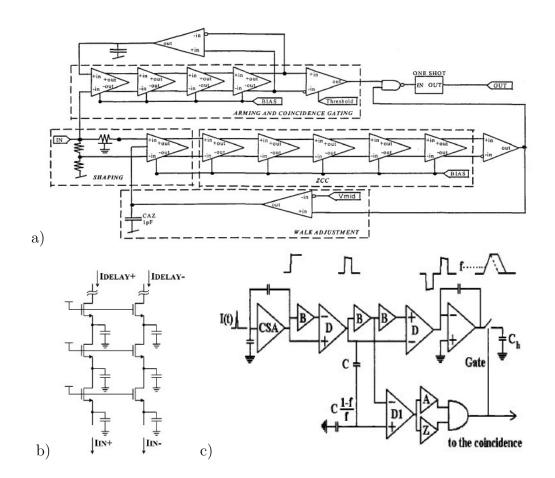

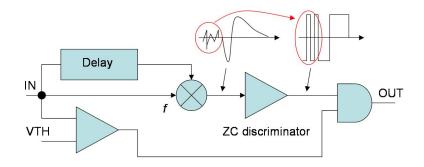

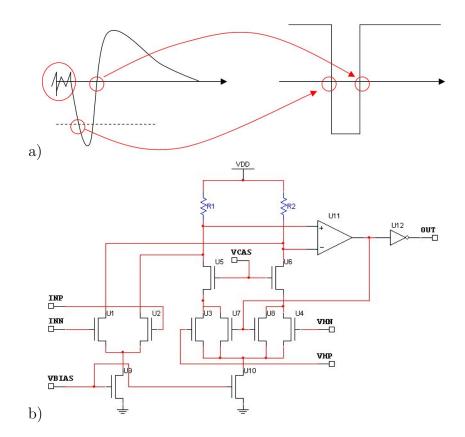

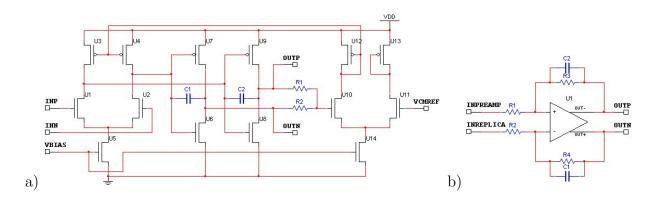

|              | 4.2          | Front-end architecture                                                         | 102          |

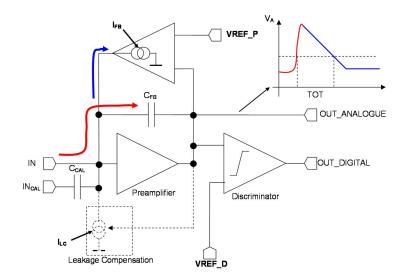

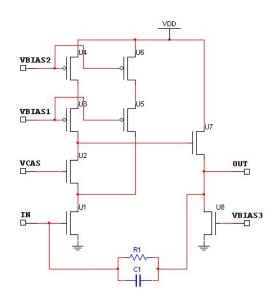

|              |              | 4.2.1 Preamplifier                                                             | 102          |

|              |              | 4.2.2 Discriminator                                                            | 104          |

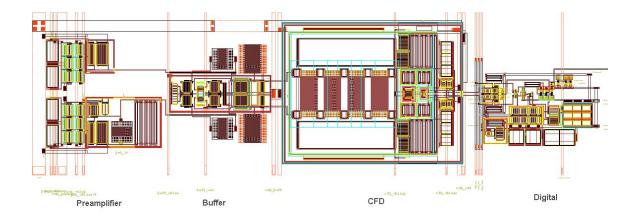

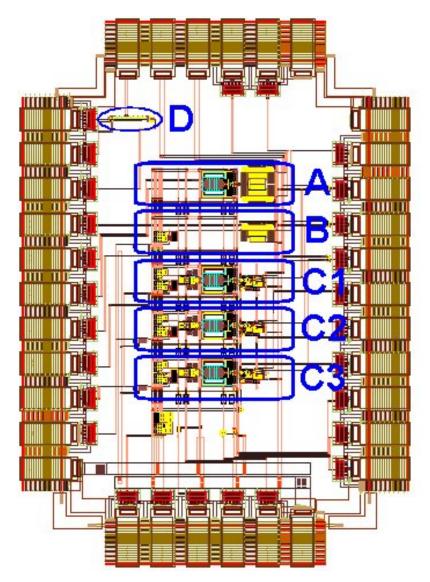

|              |              | 4.2.3 Layout of the analog pixel cell                                          | 105          |

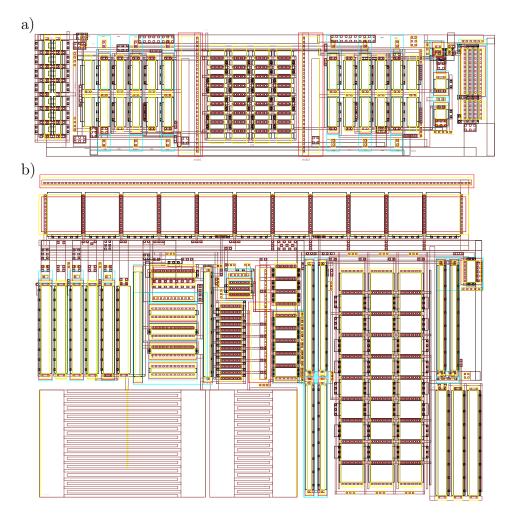

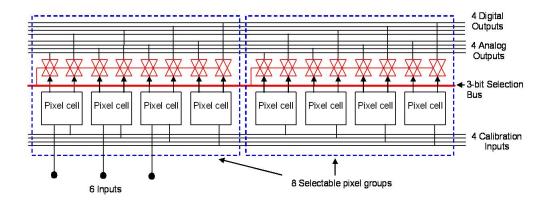

|              | 4.3          | First prototype chip                                                           | 106          |

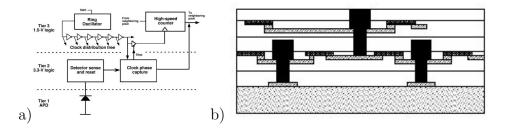

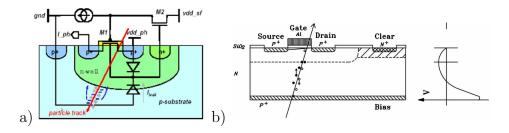

|              |              | 4.3.1 Chip architecture                                                        | 106          |

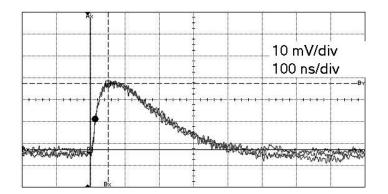

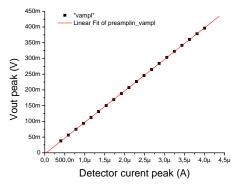

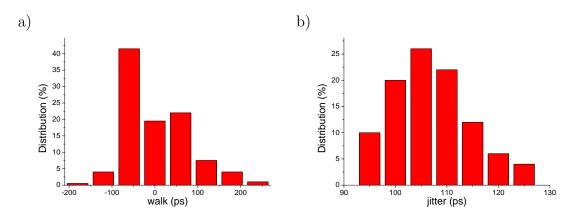

|              |              | 4.3.2 Measurements                                                             | 107          |

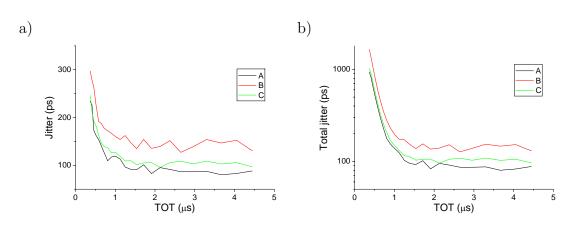

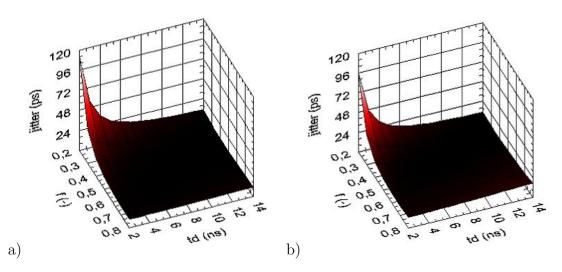

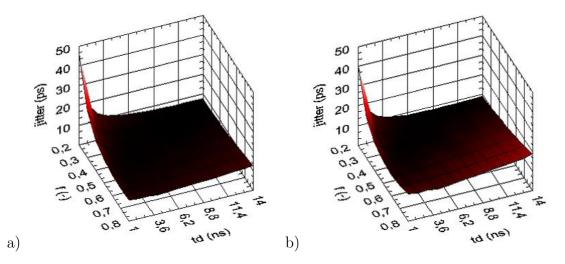

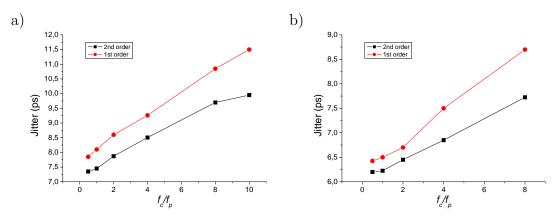

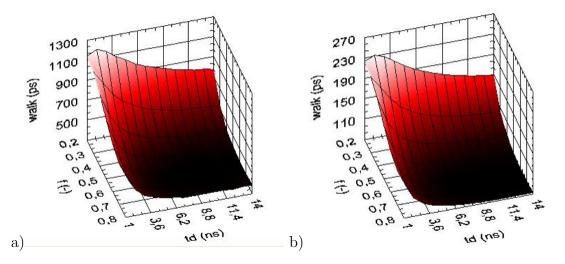

|              |              | 4.3.3 Time resolution analysis                                                 | 112          |

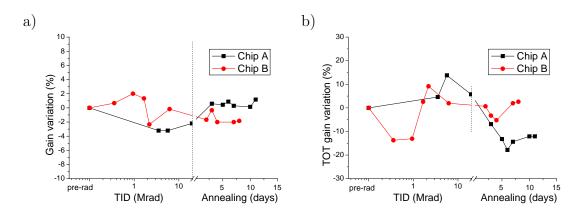

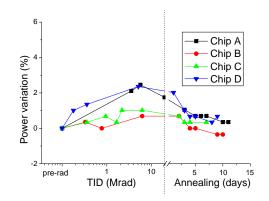

|              |              | 4.3.4 Radiation hardness                                                       | 115          |

| ٣            | Dee          | in of front and clostnonics for the Cinetro close silicon gived house          |              |

| 5            |              | ign of front-end electronics for the Gigatracker silicon pixel beam<br>loscope | 119          |

|              | 5.1          | •                                                                              | 119<br>119   |

|              | $5.1 \\ 5.2$ | 1                                                                              | 119          |

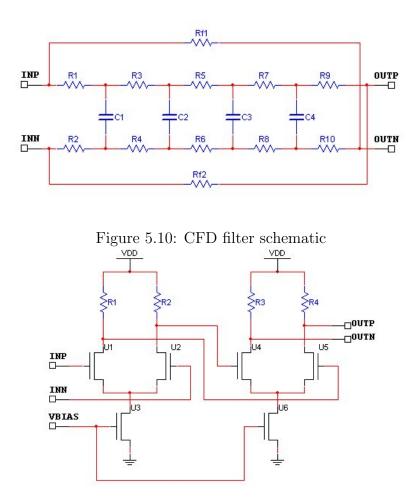

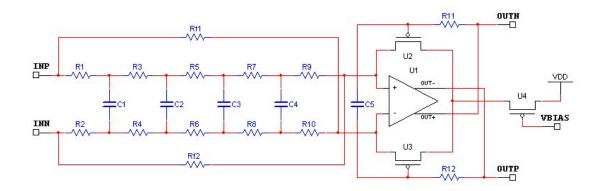

|              | 0.2          |                                                                                | $120 \\ 123$ |

|              | 5.3          | - •                                                                            | $123 \\ 129$ |

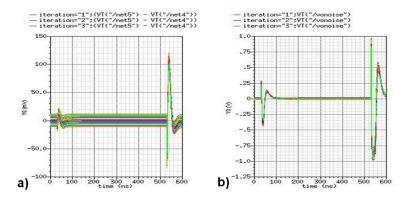

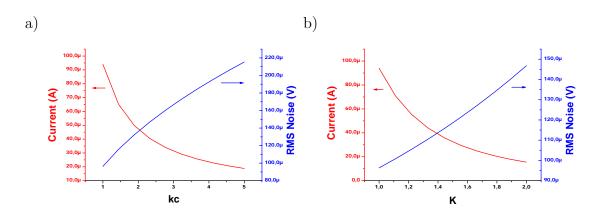

|              | 0.5          |                                                                                | 129<br>129   |

|              |              |                                                                                | $129 \\ 133$ |

|              |              |                                                                                |              |

|              |              |                                                                                | 135          |

|              | ۲ 4          |                                                                                | 137          |

|              | 5.4          |                                                                                | 138          |

|              | 5.5          | Prototype chip                                                                 | 140          |

| $\mathbf{C}$ | onclı        | isions                                                                         | 142          |

| B            | ibliog       | graphy                                                                         | 145          |

# Acknowledgements

I would like to thank Alberta Marzari-Chiesa and Angelo Rivetti, my supervisors, for their many suggestions and constant support during this research. I am also thankful to Luciano Ramello for his guidance and support.

I want to thank Giovanni Anneli, Elena Bruna, Sorin Cheran, Daniela Calvo, Ozgur Cobanoglu, Elisabeta Crescio, Paolo De Remigis, Ernesto Filoni, Paolo Giubelino, Flavio Marchetto, Mario-Ivan Martinez, Gianni Mazza, Andrea Mignone, Francesco Rotondo, Sabino Salerno, George Serbanut, Luca Toscano, Flavio Tosello, Richard Wheadon for their collaboration and fruitful discussions. Special thanks to Ozgur Cobanoglu for helping with the layout of the last submission.

I am grateful to my parents and to Ramona for their patience and *love*. Without them this work would never have come into existence (literally).

Finally, I wish to thank the following:

(the *other*) Sorin (for holding the rope tight while climbing); Andrea, Davide, Guido and Stefano (for the painful introduction to ski-alpinism); Alejandra, Alessandro, Alex, Catalin, Dede, Laura and her friends, Luca, Mario-Ivan, Nasim, Ozgur, Sarolta, Sorin, Stefano,... (for all the good and bad times we had together); and Adi, Andrei, Cuky, Dan, Florica, Maca, Mihai, Sile, Sorel, Victor... (for still remembering me after so many years spent away).

Torino, Italy February, 2007 Sorin Martoiu

# Introduction

The ambitious physics goals of the LHC experiments set new frontier in particle detector domain, pushing performance and complexity to unprecedented challenging levels. Silicon-based detectors are an example of particle detection systems that benefited from the extensive research and development work related to the LHC based highenergy physics experiments. Several years ago silicon drift detectors were confined to small scale experiments with relatively low sensitive area like, for instance, medical or spectroscopy applications, while hybrid pixels were an expensive silicon detection system both in terms of design and practical realization. Nowadays, with the extensive use of silicon drift detectors in large scale heavy-ion collision experiments like RHIC and ALICE, and the use of large area high granularity hybrid pixel systems in all four LHC-based experiments, both technologies offer a mature alternative for the implementation of medium or large scale tracking detectors. Non-LHC experiments that are planned to start operation in near future, proposing high interaction rates, and the already foreseen LHC upgrade push on this R&D work. Emerging technologies like CMOS sensors and 3D silicon detectors also gain increasingly interest in the HEP community.

The need for better resolution and higher granularity in tracking detectors calls for higher number of readout channels and more compact front-end electronics. The material budget, limited by the precision in momentum measurement, imposes for both low power design and the use of new technologies in interconnections, mechanical support, cooling, etc. In these conditions, preserving laboratory performance of individual sub-detectors, while replicating them into large-area detector subsystem, is a demanding task. Eliminating large-system specific features like crosstalk, digital spurious noise, ground level bouncing, to nominate only a few, asks for careful design and extensive production qualification effort. Consequently, system integration in high-energy physics became a research and development domain by itself, owing from domains like electronic and mechanical engineering to materials science.

This work follows the design, realization and test of front-end electronics for particle detection using silicon drift and silicon pixel detectors applied in nuclear and high-energy physics experiments. Reflecting a research experience that started in 2004 within the ALICE SDD group of INFN Torino and the University of Torino, a period when all LHC-based detectors were finalizing the design phase and starting the final integration, this work begins with the system integration aspect of the large scale SDD detection system and continues with the design, prototyping and test of new front-end electronics for silicon detector systems for the PANDA and P326 experiments at GSI and CERN, respectively. The apparent "mis-arrangement" of the design-test-integration flow, apart from being an exact photography of the research experience reported here, also underlines the repetitive and self-consistent nature of the sequence, as all knowledge gathered from completed design-to-integration flow is the starting base for a new one. Specific problematic and technological issues with accent on quality assurance scheme of the integration of the Silicon Drift detector system of the ITS of ALICE experiment is presented together with characterization of the custom designed VLSI front-end electronics. The work also presents design and prototype characterization of new VLSI front-end electronics for pixel detectors that were realized using the currently commercially available deep-submicron CMOS technology. The migration from silicon drift to pixel detectors is a natural trend driven by newly available VLSI fabrication technologies, in the view of future luminosity upgrade of LHC and other high intensity HEP experiments.

# Chapter 1

# Experimental challenges in nuclear and particle physics

This chapter gives an overview of the main aspects the modern nuclear and particle physics focuss on, from both theoretical and experimental point of view. The chapter serves as extended introduction to the three experiments that this work contributes to (ALICE, P326, PANDA) setting their scientific environment and, finally, giving specific motivation and description for each of them.

# 1.1 Short history of experimental nuclear and particle physics

At the end of 19th century the concept of atom formulated by Democritus of Abdera as *the* fundamental indivisible constituent of matter was still in the general belief of the scientists. In 1898 J. J. Thompson proposed that the long-standing puzzle known as "cathoderays" were in fact negative charged *corpuscules*, later called *electrons*<sup>1</sup>. This hypothesis was later confirmed by experiments carried out by Thompson and others. Moreover the mass of this *corpuscules* was found to be about one thousand times smaller than the mass of the lightest atom. This extraordinary discovery was the first to contradict the indivisible nature of the atom. It lead to the atomic model known as *the plum pudding model* proposed in 1904 by Thompson, picturing the atom as composed by electrons surrounded by a soup of positive charge to balance the electron's negative charge, like plums surrounded by pudding.

Thirteen years later, in 1911, following the alpha-scattering experiment performed by Hans Geiger and Ernest Marsden, one of the Thompson's students - Ernest Rutherford concludes that the atom has a concentrated positive nucleus. Several years later Rutherford finds the first evidence for a proton (1919). He manages to bombard the nucleus with alpha particles, using nitrogen as target. The nitrogen nucleus absorbs the alpha particle resulting an oxigen nucleus and a free proton. The neutron was first postulated by Rutherford and later in 1932 discovered by James Chadwick. He demonstrated that the "radiation of great penetration power" resulted from the bombardment of beryllium with  $\alpha$ -particles was, in fact, "particles of mass 1 and charge 0, or neutrons" [1].

In 1927 Rutherford urged the experimental physics community to develop sources of particles of higher energies than those provided by natural radioactivity, in order to explore deeper into the structure of the atom. John Cockcroft and E. T. S. Walton from Rutherford's Cavendish Laboratory in Cambridge developed a proton

<sup>&</sup>lt;sup>1</sup>The term *electron* was initially used by G. Johnstone Stoney in 1874 to explain the phenomenon of electrolysis, but they were not regarded as constituents of the atom at the time.

accelerator scheme using a high-voltage transformer and a voltage multiplier. In parallel, Robert Van de Graaff built a particle accelerator based on an electrostatic high-voltage generator. His idea survived through the century being still today the most commonly used potential-drop accelerator.

At the beginning of 1930s Ernest Lawrence, together with its graduate student Stanley Livingston, applied a new concept of particle accelerator, inventing the cyclotron. He used a magnetic field to curve the trajectory of a charged particle, forcing it to cross many times a potential gap in a repetitive fashion, while the potential is switched between positive and negative as the particle crosses the gap in one direction or the other. In this way the particle is accelerated at each gap-crossing until the curvature radius of its trajectory reaches the boundary of the device and the particle escapes. After more than 10 years of hard work and successive prototyping they built a 184-inch cyclotron capable of accelerating various charged particles to energies higher than 100 MeV.

In the mid 1940s, two new types of accelerators were developed: the linear accelerator and the synchrotron, using the newly invented phase stability concept. This inventions paved the way for a new phase of the experimental physics. The number of particle accelerators grew substantially over the years, as well as their complexity and energy range. Rutherford's scattering experiment was reproduced at nucleon scale in 1968 at the Stanford Linear Accelerator Center. This time, the large angle scattering pattern of the high-energy electron-proton collision revealed the quark structure of the proton.

Among other advanced accelerator facilities, the two largest proton synchrotrons, at CERN, near Geneva, and at Fermilab near Chicago, started operation in the mid

1970s. Fixed-target experiments were soon replaced by collision experiments where two particles, both accelerated close to the speed of light, are forced to collide one into another, increasing the center of mass energy, and thus the physics yield. Table 1.1 gives a short summary of some of the collider facilities around the world and their contribution.

| Machine          | Location | Beam       | Energy (GeV) | Radius            | Highlight    |

|------------------|----------|------------|--------------|-------------------|--------------|

| AdA <sup>1</sup> | Frascati | $e^+e^-$   | 0.25 + 0.25  |                   |              |

| SPEAR            | Stanford | $e^+e^-$   | 3 + 3        |                   | c,	au        |

| DORIS            | Hamburg  | >>         | 5 + 5        |                   | b            |

| CESR             | Cornell  | >>         | 8 + 8        | $125 \mathrm{~m}$ | 22           |

| PEP              | Stanford | >>         | 18 + 18      |                   | b lifetime   |

| PETRA            | Hamburg  | >>         | 22 + 22      | $300 \mathrm{m}$  | g            |

| SPS              | CERN     | $\bar{p}p$ | 300 + 300    | $1~{\rm Km}$      | W, Z         |

| TEVATRON         | Fermilab | >>         | 1000 + 1000  |                   | t            |

| SLC              | Stanford | $e^+e^-$   | 50 + 50      | _                 | Ζ            |

| LEP-I            | CERN     | "          | "            | $5~{ m Km}$       | Ζ            |

| LEP-II           |          | "          | 100 + 100    | "                 | W            |

| HERA             | Hamburg  | ep         | 30 + 800     | $1~{\rm Km}$      | _            |

| LHC              | CERN     | pp         | 7,000+7,000  | $5~{ m Km}$       | Higgs? SUSY? |

<sup>1</sup> In italian, "Anello di Accumulazione" - the first storage ring build by Bruno Touschek in 1960[2].

Table 1.1: Past and present colliders.

# 1.2 Overview of the present objectives in nuclear and high-energy physics

### 1.2.1 Overview of the Standard Model

There are four fundamental interactions in nature.

The Electromagnetic Interaction is the unified representation of the forces at the origin of electric and magnetic phenomena. It causes the attraction felt by particles of opposite electric charges and the repulsion between those that carry the same sign. This interaction therefore holds the atomic structure together in which negatively charged electrons orbit around a positively charged nucleus. The interaction is conveyed by the photon, which acts like a messenger particle between electrically charged particles.

The weak interaction is the force at the origin of physics phenomena like radioactivity which spontaneously transforms a neutron into a proton or the thermonuclear production of energy at the heart of the sun. The conveyors of this interaction are the W and Z bosons discovered at CERN.

The Strong Interaction is the force that binds together the quarks within hadrons, like in protons and neutrons. The interaction is conveyed by the eight gluons. It also keeps protons and neutrons together within the atomic nucleus against the action of the electromagnetic force. The particular property of the Strong force is that its effect increases with distance, making it impossible for the quarks to be observed individually in nature.

The Gravitational Interaction is responsible for the attraction between masses. Its effect in our macroscopic every-day life is widely known, as the fact that any object

on earth is attracted toward its center. It is at astronomical level that it reveals its most subtle effects in phenomena such as the movement of celestial objects or the curvature of the light paths in the vicinity of massive objects. Messenger particles of the gravitational field called "gravitons" is supposed to exist. However there is no experimental evidence of its existence as yet. Gravitational force is so weak that its effects are totally negligible in the subatomic world.

Electroweak theory proposed around 1960 by Sheldon Glashow, Abdus Salam, and Steven Weinberg [3], unifies the electromagnetic and weak interactions. Quantum chromodynamics, on the other side, is the best theoretical quantum-field description of the strong force. The Standard Model is a result of the combination of the electroweak theory (GSW theory) with quantum chromodynamics (QCD), covering all the interactions governing the nature, except the gravitational force.

Within the Standard Model, the elementary constituents of nature are fermions, particles with intrinsic spin of 1/2. There are 12 different matter particles, six quarks (*up*, *down*, *strange*, *charm*, *bottom*, *top*) and six leptons (*electron*, *muon*, *tau* and their corresponding *neutrinos*).

The six flavors of quark come in three generations of weak isospin doublets that lead to SU(2) symmetry. Each quark has three possible colors. The fact that quarks come in three colors is used as the basis for SU(3) symmetry. The SU(3) color symmetry is exact since the three colored quarks of each flavor are identical in every respect except color. The SU(3) symmetry of colored quarks would automatically require eight  $(3^2 - 1 = 8)$  gauge bosons. These are the eight gluons characterized by color-anticolor combinations, similar to the colored quark-antiquark pairs used to obtain meson multiplets. The gluons are responsible for mediating the strong color force that binds hadrons. The Standard Model results when the electroweak theory group represented by  $SU(2) \times U(1)$  is extended to include the SU(3) colored quark group which represents QCD. The Standard Model can account for all hadronic (strong interaction) and electroweak phenomena. Meson exchange effects that are still useful in describing low energy nuclear phenomena are residual effects of the strong color force in the same way that molecular forces are consequences of the electromagnetic force.

Most of the fundamental predictions of the Standard Model have been experimentally confirmed. The discovery of the W and Z bosons, as well as the excellent accordance between their measured and predicted properties are very strong confirmations of the electroweak theory. On the other hand QCD has enjoyed the same experimental success. All quarks predicted by the theory were observed in a series of experiments. Moreover, the experiments carried out using the LEP collider at CERN have demonstrated that only three weakly-interacting neutrinos exists, with mass lower than half of the mass of Z boson. This implies the existence of three generations of quarks and leptons, as predicted by theory.

### 1.2.2 The search for Higgs Boson.

One of the pieces of the puzzle still missing, is the Higgs boson. This particle is an observable component of the Higgs field, which is characterized by a non-zero vacuum expectance value (VEV), being responsible for the mass of every elementary particle, including the Higgs boson. In particular, the Higgs mechanism spontaneously breaks the electroweak gauge symmetry, which otherwise would require that Z and W boson were massless, just as their electromagnetic counterpart, the photon.

Although unconstrained by the theory, available experimental data provide upper and lower bounds on the Higgs mass. Direct searches at LEP2 have ruled it must exceed 114.4 GeV at 95% confidence level [4]. On the other hand, electroweak precision measurements sets an upper bound on the mass of the Higgs boson at 219 GeV with the same confidence level [5]. Given the logarithmic sensitivity of electroweak precision measurements to  $m_H$ , the upper bound extends at a factor of a few above this limit. Both ATLAS and CMS collaborations at CERN will search for the Higgs boson in the mass range of  $10^2 - 10^3$  GeV.

### **1.2.3** Inside the hadronic matter

One of the fundamental difference between QCD and Quantum Electrodynamics is the fact that the gluons carry color charges, as opposed to photons which are electrically neutral. The color charge makes the gluons interact amongst themselves, giving birth to a new set of phenomena and key features of QCD such as confinement (the absence of free colour-charged objects in nature) and asymptotic freedom (the fact that quarks and gluons interact weakly at high momenta or short distances).

At distances below 0.1 Fermi, the QCD coupling strength is small, allowing for a perturbative treatment of the strong interaction. On the other hand, at distance scales of the order of 1 Fermi, the coupling become large and a perturbative approach is no longer valid. In this regime, the theoretical treatment involves colorless baryons and mesons rather than quarks and gluons.

Generally there are two methods for experimental exploration of both regimes, perturbative and nonperturbative

• studying the responses of hadronic systems to high-precision probes at various

energy scales,

• creating conditions of high density or temperature in high-energy heavy-ion collisions.

#### 1.2.3.1 Spin of the nucleon

In recent years we have learned that quarks are not the only contributors to the total spin of the nucleon, but also the gluons and possibly the orbital angular momentum of the quarks and gluons do contribute.

The contribution of the quarks to the total spin of the nucleon has been worked out from the longitudinal spin distribution (or helicity) in polarized deep-inelastic scattering experiments, carried out at CERN, DESY and SLAC. The results read that the total quark spin contribution is in the order of 10% to 30%, indicating that additional carriers of angular momentum are needed in the nucleon.

Some recent experiments or proposals try to measure the gluon contribution from photon-gluon fusion events in deep-inelastic scattering experiments. In these processes the virtual photon annihilates with a gluon from the target to produce a quark and its antiquark, while the asymmetry of the process is sensitive to the gluon polarization.

The identification of photon-gluon fusion events through detection of charmed particles or high- $p_T$  pairs of hadrons at COMPASS (CERN) will provide precise measurement of the gluon polarization. Complementary data is expected to come from the RHIC-spin program at BNL using polarized proton beams.

#### 1.2.3.2 Glueballs and hybrids

Another consequence of the gluon-gluon interaction is the existence of gluon-rich bound states known as glueballs, and of mixed states of quarks and gluonic excitations known as hybrids.

The experimental observation of these exotic particles, in particular glueballs, would confirm one of the most important features of QCD. On the other hand, the non-existence of such states would pose a genuine problem for our understanding of hadronic physics in the context of QCD.

One of the best candidate for the ground state glueball has been observed in proton-antiproton annihilation experiments performed at LEAR  $(f_0(1500))[6]$  and later by other experiments. Its mass is very close to what Latice QCD predicts for the ground state glueball, while its decay modes and production mechanism appear peculiar in the quark structure hypothesis. Other candidates are the  $f_0(1370)$  and  $f_0(1710)$  resonances. They appear to be combinations of  $q\bar{q}$  states and  $non-q\bar{q}$  states, making the analysis of their glueball content a difficult task.

Most of the available experimental data in the glueballs and hybrids sector is limited to the mass range below 2.2  $GeV/c^2$ .

Other gluon-rich processes, like proton-proton collisions or radiative  $J/\psi$  decay, that may lead to the production of such exotic states have disadvantages in the high energy range. In the first case production of higher mass states is limited by the fall-off of the cross section with the inverse square of the mass of the state. Radiative  $J/\psi$  decay, which could produce gluonic hadrons up to  $3 \ GeV/c^2$ , lacks the required statistics. For a more complete understanding of the nature of gluonic excitations, a careful study of the spectrum of glueballs and hybrids up to  $5GeV/c^2$  is an absolute necessity[7]. Theory suggests that for masses above 4.3 GeV/c2 the mixing with normal mesons should be suppressed. As a consequence they are predicted to be rather narrow and easy to identify experimentally.

GSI plannes a new ambitious physics program where the search for gluonic excitations in the charmonium sector and the continuing hunt for glueballs, including highly excited states with exotic quantum numbers have a central part. The program uses the PANDA detector at the High-Energy Storage Ring (HESR), and will carry on fixed-target experiments with high quality antiproton beam, including protonantiproton annihilation with energies up to 15GeV.

Lattice QCD calculations predics the existence of about 15 glueball states, in the mass range that is accessible to the HESR project. Searches for glueballs and hybrids in this energy region can be performed in parallel with studies of charmonium spectroscopy at the proposed PANDA detector. In addition, by comparing different production mechanisms it should be possible to find unambiguous signatures of these exotic states.

#### 1.2.3.3 Charmed quark systems

The charmonium system has a particular importance, compared to the other quarkonia  $s\bar{s}$  and  $b\bar{b}$ , because it lies in the region of intermediate distances where the domains of perturbative and nonperturbative QCD come together. It is for this reason that the charmonium system provides a unique testing ground for QCD. Indeed, the masses and widths of the  $c\bar{c}$  states directly reflect the basic  $q\bar{q}$  interaction. Moreover, the charmonium spectroscopy may lead to the determination of the gluon condensate of the QCD vacuum. Charmonium spectroscopy was extensively studied at  $e^+e^-$  colliders during 1974 - 1980. However, the technique of studying charmonium via  $e^+e^-$  annihilation had important limitations. The masses of several states were well determined but not, in general, their widths.

Experiments R704 at CERN and E760/E835 at Fermilab demonstrated that charmonium formation using  $p\bar{p}$  annihilation has two significant advantages compared to  $e^+e^-$  annihilation. The first is that, since  $p\bar{p}$  annihilation must proceed via two or three intermediate gluons, it can lead to the direct formation of charmonium states with all possible quantum numbers. This means that the precision achievable for all states depends only on the quality of the antiproton beam and not on the detector properties. The second advantage comes from the possibility of cooling antiproton beams (stochastically and/or with electrons) to obtain a momentum resolution of one part in 10<sup>5</sup>, which translates directly into improved mass resolution.

Despite these efforts, there remain a number of unresolved fundamental questions concerning the charmonium system. These will be addressed by experiments focused on charmonium spectroscopy, using the PANDA detector system at GSI/HESR. This facility will offer improvements beyond the Fermilab program, by providing higherenergy antiproton beams (15 GeV), higher luminosity, better cooling, and a state-ofthe-art hermetic detector for both electromagnetic and charged particles.

When running at full luminosity, HESR will produce a large number of D-meson pairs. Thus, it can also be regarded as a hadronic factory for tagged open charm. The high yield and the well-defined production kinematics of these pairs would allow studies of rare processes in the charm system such as CP-violation or flavour mixing, and determinations of the decay constants of charmed mesons.

#### 1.2.3.4 Hypernuclei

An ordinary nucleus is composed of neutrons and protons. The exchange of one of the up or down quarks in the nucleus with a *strange* quark leads to a new type of nucleus called hypernucleus. Due to the strangeness conservation in strong and electromagnetic interactions, such bound state lives long enough to have sharp nuclear energy levels. Since the presence of a *strange* quark adds a new quntum number to the nucleus, hypernuclear physics merges isospin and strangeness into the enlarged field of flavour SU(3) many-body dynamics.

Hypernuclei were discovered more than 50 years ago by Marian Danysz and Jerzy Pniewski in a nuclear emulsion exposed to cosmic radiation. Significant progress have been made in the last 15 years, mainly at BNL, KEK and COSY. Recently at DA $\Phi$ NE in Italy, FINUDA experiment started a research program aiming at production of large number of hypernuclei using low-energy  $K^-$  particles. Recently, spectrum measurements of  ${}^{12}_{\Lambda}C$ , as well as evidence of hypernuclei with high N/Z ratio,  ${}^{6}_{\Lambda}H$  and  ${}^{7}_{\Lambda}H$ , has been reported [8, 9].

More insight in hypernuclear physics will be available also at GSI. Collisions of antiprotons with nuclei is foreseen, which will lead to detaile spectroscopic study of hypernuclei with single and multiple strangeness. Charmed hypernuclei (nuclei containing a charmed baryon) will also be available, opening a new chapter in hypernuclear physics that may lead to new insights new insights into the dynamics related to breaking of SU(4) flavour symmetry by the large mass of the charmed quark.

#### 1.2.3.5 Phases of nuclear matter

Another tantalizing aspect of hadronic world is how do the properties of hadrons and hadronic bound states change due to thermodynamic conditions. Moreover, there is the question whether compressed / heated systems of protons and neutrons exhibit different phases depending on the local nuclear temperature and density, similar to macroscopic matter that may exist in three phases: solid, liquid or gas, and what is the influence of this behaviour at macroscopic level.

In their normal states of lowest energy, nuclei show liquid-like characteristics and have a density of 0.17  $nucleons/fm^3$ . At moderately high baryon densities a firstorder liquid-gas transition may takes place. In the gas state, the nuclear matter consists of free nucleons and pions.

After the discovery of asymptotic freedom in QCD it was realized by Collins and Perry [10] and independently by Cabibbo and Parisi [11] that a hadronic system at sufficiently high density or temperature should convert into a new state of matter, called quark-gluon plasma (QGP). Lattice QCD calculation predicts that the transition to quark-gluon plasma occurs at a critical temperature  $T_c = 175 \pm 15 MeV$ .

Above this temperature, the hadrons lose their particle identity, as the colour charges are screened at distances larger than the Debye screening length[12], creating a deconfined state where quarks and gluons can move quasi-freely inside the initial volume.

The high temperature and density conditions for the transition to QCP can be created in laboratory through high-energetic heavy-ion collisions. The scenario of QGP formation and its evolution in highly central nucleus-nucleus collision is as follows:

- following the collision, the nuclei disintegrate into their parton structure, building up a region of high entropy called *fireball*;

- the energy released in the collision begin to thermalize, increasing the pressure and the energy density inside the *fireball* leading to deconfinenment of quarks and gluons and plasma formation;

- as the plasma is cooling down, it expands and then hadronizes when the temperature crosses back  $T_c$

Several experiments have been dedicated to this research field (NA35, NA44, NA45 (CERES), NA50 at the SPS at CERN, STAR at RICH, etc.). A first evidence for the quark-gluon plasma might be the anomalous  $J/\psi$  suppression observed in Pb-Pb collisions by NA50 at CERN. The chromoelectric Debye screening effect, characteristic to the deconfined state, cuts off the binding force between the constituent charm and anticharm quarks of  $J/\psi$ , and thus signals the occurrence of such state.

The study of QGP formation and its properties may unveil valuable information about hadronic matter and the strong interaction. The scientific importance of this particular state extends to astrophysics and cosmology, as it is generally believed that the universe was in the first instants after the *Big Bang* in a deconfined state with nearly perfect thermal and chemical equilibrium. Good understanding of the laboratory generated QGP and the hadronization phase may lead to better understanding of the universe was formed.

## 1.3 P326 and CKM mechanism

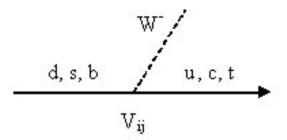

In 1973 Kobayashi and Maskawa proposed the existence of a third generation of quarks[13] in order to explain the CP-violation first observed in kaon decays in the mid 1960s at the alternating gradient synchrotron at BNL[14]. Their suggestion came before the first experimental evidence of charm, beauty or top quarks. Their theory introduces a 3x3 *complex* and *unitary* matrix called Cabibbo-Kobayashi-Maskawa (CKM) matrix governing the couplings between different quark generations [12] (see figure 1.1):

Figure 1.1: Flavour changing diagram example.

$$\begin{pmatrix} d'\\ s'\\ b' \end{pmatrix} = V_{CKM} \begin{pmatrix} d\\ s\\ b \end{pmatrix}$$

(1.3.1)

$$\begin{pmatrix} V_{ud} & V_{us} & V_{ub} \end{pmatrix}$$

$$V_{CKM} = \begin{pmatrix} U_{cd} & U_{cs} & U_{cb} \\ V_{cd} & V_{cs} & V_{cb} \\ V_{td} & V_{ts} & V_{tb} \end{pmatrix}$$

(1.3.2)

Using the traditional Wolfenstein parameterization[15] the CKM matrix can be written as follows:

$$V_{CKM} = \begin{pmatrix} 1 - \frac{\lambda^2}{2} & \lambda & A\lambda^3(\rho - i\eta) \\ -\lambda & 1 - \frac{\lambda^2}{2} & A\lambda^2 \\ A\lambda^3(\rho - i\eta) & -A\lambda^2 & 1 \end{pmatrix} + \partial V_{CKM} \quad (1.3.3)$$

$$\partial V_{CKM} = \begin{pmatrix} 0 & 0 & 0 \\ -iA^2\lambda^5 & 0 & 0 \\ A\lambda^5\frac{\rho + i\eta}{2} & A\lambda^4(1/2 - \rho - i\eta) & 0 \end{pmatrix} \quad (1.3.4)$$

Within this theoretical frame, a non-zero value of the parameter  $\eta$  in equation (1.3.3) is responsible for all CP-violating phenomena in flavor changing processes.

The unitarity of the CKM matrix implies

$$\sum_{i} V_{ij} V_{ik}^* = \delta_{jk} \tag{1.3.5}$$

$$\sum_{j} V_{ij} V_{kj}^* = \delta_{ik} \tag{1.3.6}$$

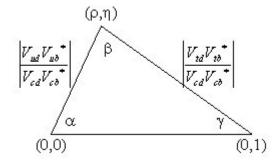

Figure 1.2: Unitarity triangle.

One of the most commonly used unitarity relation and of particular importance for what follows is:

$$V_{ud}V_{ub}^* + V_{cd}V_{cb}^* + V_{td}V_{tb}^* = 0 (1.3.7)$$

which can be graphically represented as a triangle in the complex plane (figure 1.2). The apex of the triangle is  $(\overline{\rho}, \overline{\eta})$ , where

$$\overline{\rho} + i\overline{\eta} = -(V_{ud}V_{ub}^*)/V_{cd}V_{cb}^* \tag{1.3.8}$$

take into account also higher order terms in the Wolfenstein parameterization:

$$\overline{\rho} = \rho(1 - \lambda^2/2 + ...)$$

(1.3.9)

$$\overline{\eta} = \eta (1 - \lambda^2 / 2 + ...)$$

(1.3.10)

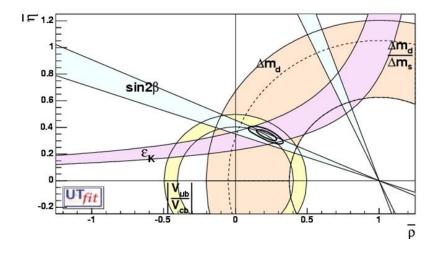

This parameterization is extensively used, many of the experiments aiming to constrain CKM elements expressing their results in the  $(\bar{\rho}, \bar{\eta})$  plane. Figure 1.3 shows a compilation of the experimental constraints on the apex of the unitarity triangle.

| $V_{ij}$ | Value   | Error   | Rel. error  |

|----------|---------|---------|-------------|

| $V_{ud}$ | 0,97377 | 0,00027 | $0,\!03\%$  |

| $V_{us}$ | 0,22570 | 0,00210 | 0,93%       |

| $V_{ub}$ | 0,00431 | 0,00030 | $6{,}96\%$  |

| $V_{cd}$ | 0,23000 | 0,01100 | 4,78%       |

| $V_{cs}$ | 0,95700 | 0,09300 | 9,72%       |

| $V_{cb}$ | 0,04160 | 0,00060 | $1,\!44\%$  |

| $V_{td}$ | 0,00740 | 0,00080 | $10,\!81\%$ |

| $V_{ts}$ | 0,04060 | 0,00270 | $6,\!65\%$  |

| $V_{tb}$ | 0,77000 | 0,24000 | $31,\!17\%$ |

Table 1.2: Magnitude of the CKM matrix elements

The elements of the CKM matrix have been extracted from flavor changing reactions involving mostly kaon, D and B decays and their CP-violation behavior. The values obtained up to date and their relative uncertainties are reported in table 1.2, from [12]. Some of them are not yet independent of theoretical assumptions like, for instance the case of  $|V_{td}|$  which assumes  $|V_{tb}| = 1$ .

Figure 1.3: Experimental constraints on the apex of the unitarity triangle.

The P326 collaboration proposes to give a 10% accurate estimate of  $|V_{td}|$  using the very rare kaon decay  $K^+ \to \pi^+ \nu \overline{\nu}$  at the CERN SPS [16]. This measurement will improve the knowledge of the CKM matrix and provide a decisive test of Standard Model.

The rare kaon decays of  $K \to \pi \nu \nu$  form are of particular interest in the Standard Model framework. Flavor Changing Neutral Current (FCNC) processes are allowed only via loop diagrams that include internal quarks or intermediate bosons. The importance of rare semileptonic FCNC decays,  $K_L \to \pi^0 \nu \bar{\nu}$  and  $K^{\pm} \to \pi^{\pm} \nu \bar{\nu}$ , is amplified by their clean theoretical character[17]. This particular property comes from the following facts:

• the low energy hadronic matrix elements required are just the matrix elements

of quark currents between hadron states, which can be extracted with good accuracy from non-rare semileptonic decays;

- the main contribution to the FCNC processes comes from the region of very small distances ( $\sim 1/m_t, 1/m_Z$ ) where perturbative QCD holds;

- these processes are sensitive to new physics like, for instance, contributions from heavy supersymmetric particles.

The branching ratio for  $K^+ \to \pi^+ \nu \bar{\nu}$  can be written as [18]

$$Br(K^+ \to \pi^+ \nu \bar{\nu}) = k_+ \left[ \left( \frac{Im\lambda_t}{\lambda^5} X(x_t) \right)^2 + \left( \frac{Re\lambda_t}{\lambda^5} X(x_t) + \frac{Re\lambda_c}{\lambda^5} P_c \right)^2 \right] \quad (1.3.11)$$

$$k_{+} = r_{K^{+}} \frac{3\alpha Br(K^{+} \to \pi^{0} e^{+} \nu)}{2\pi^{2} sin^{4} \theta_{W}} \lambda^{8} = (5.04 \pm 0.17) \times 10^{-11} \left(\frac{\lambda}{0.2248}\right)^{8}$$

(1.3.12)

where  $\lambda = V_{us}$ ,  $\lambda_c = V_{cs}^* V_{cd}$ ,  $\lambda_t = V_{ts}^* V_{td}$ ,  $x_t = m_t^2/m_W^2$  and the  $r_{K^+} = 0.901$ is the isospin breaking correction. The coefficients X and  $P_c$  are being computed numerically and the most recent Next-to-Next-to-Leading Order  $\chi PT$  calculation predicts[19]:

$$Br(K^+ \to \pi^+ \nu \bar{\nu}) = (8.0 \pm 1.1) \times 10^{-11}$$

(1.3.13)

where the error is almost entirely due to uncertainties in  $m_c$  and the CKM matrix elements.

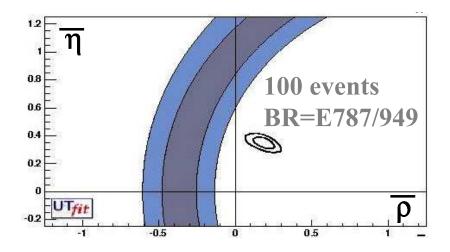

Investigation of both  $K^+ \to \pi^+ \nu \bar{\nu}$  and  $K^0 \to \pi^0 \nu \bar{\nu}$  provides an alternative way for determination of the apex of the unitarity triangle. The comparison between this apex and the one obtained from other methods like the *B*-mesons allows a clean test of the Standard Model. The study of such rare decay may appear difficult, but recent experiments have demonstrated that it is possible. BNL-AGS-E787 (E949)[20] have identified three such events in a three year data taking period. The follow-up experiment BNL-AGS-E949[21] is expected to increase the statistics, possibly reaching 10 events in the following years. As opposed to P326 proposal, the measurement has been performed with kaon decays at rest. Another initiative at Fermilab called *Charged Kaon at the Main injector* (CKM) proposed in-flight measurement of  $K^+ \rightarrow \pi^+ \nu \bar{\nu}$  branching ratio, targeting around 100 events statistics. Unfortunately the initiative lacked funding and was prematurely terminated.

The value of the branching ratio resulted from BNL-AGS-E787 (E949) is

$$Br(K^+ \to \pi^+ \nu \bar{\nu}) = (14.7^{+13.0}_{-8.3}) \times 10^{-11}$$

(1.3.14)

The central value in (1.3.14) is higher than the Standard Model expectation in (1.3.13), but the result is compatible with SM if the large errors are accounted for. Figure 1.4 shows the mismatch between the present determination of the apex of the unitary triangle, based on Standard Model prediction (ellipses), and the projection in  $(\bar{\rho}, \bar{\eta})$  plane of  $Br(K^+ \to \pi^+ \nu \bar{\nu})$  due to BNL-AGS-E787 (E949). This deviation might be the indication of new physics beyond the Standard Model, that may differentiate between B-meson and kaon sectors[17].

### 1.3.1 Background rejection in P326

The main background in studying  $K^+ \to \pi^+ \nu \bar{\nu}$  comes from the hadronic two-body decay  $K^+ \to \pi^+ \pi^0$  and the leptonic two-body decay  $K^+ \to \mu^+ \nu$ , with branching ratios 10 orders of magnitude higher than the signal. In particular, the cases where the neutral pion of the hadronic decay is missed, or the muon is mistakenly identified

Figure 1.4: Possible new physics from the measurement of  $K^+ \to \pi^+ \nu \bar{\nu}$ . Ellipse represent the present determination of the unitarity triangle apex; bands represent BNL-AGS-E787 (E949)result.[17]

as pion can fake the signal. Thus, a very good photon rejection (from the neutral pion decay) and particle identification (for muon detection) are needed, in conjunction with kinematical constraints. Other decay modes of the kaon are summarized in 1.3, together with the corresponding rejection method.

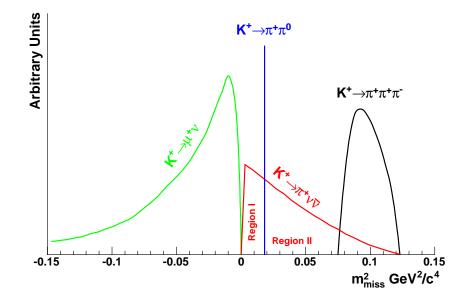

Figure 1.5 shows the missing mass distribution calculated for the  $K^+ \to \pi^+ \nu \bar{\nu}$ signal and the most important background decay modes. Two acceptance regions can be identified with missing mass ranging from 0 to the minimum missing mass in  $K^+ \to \pi^+ \pi^+ \pi^-$  decay, separated by a narrow gap around  $m_{\pi^0}^0$ . The width of the gap is determined by the missing mass resolution of the experiment.

Simulations have shown[16] that signal-to-background ratio better than 10 and signal acceptance higher than 10% can be obtained considering neutral pion rejection inefficiency in the order of  $10^{-8}$  and muon veto inefficiency of  $5 \times 10^{-6}$ , with a missing

| Decay Mode                  | BR  | Background Rejection              |

|-----------------------------|-----|-----------------------------------|

| $K^+ \to \mu^+ \nu$         | 63% | $\mu$ PID, kinematics             |

| $K^+ \to \pi^+ \pi^0$       | 21% | photon veto, kinematics           |

| $K^+ \to \pi^+ \pi^+ \pi^-$ | 6%  | charged particle veto, kinematics |

| $K^+ \to \pi^+ \pi^0 \pi^0$ | 2%  | photon veto, kinematics           |

| $K^+ \to \pi^0 \mu^+ \nu$   | 3%  | photon veto, $\mu$ PID            |

| $K^+ \to \pi^0 e^+ \nu$     | 5%  | photon veto, $E/p$                |

Table 1.3: Background decay modes

mass resolution of

$$(\Delta m)^2 \simeq 8 \times 10^{-3} GeV^2/c^4$$

(1.3.15)

## 1.3.2 Experimental setup

#### 1.3.2.1 The beam

P326 is using a 400GeV primary proton beam from the SPS at CERN with an intensity of  $3 \times 10^{12}$  protons per 5s pulse. The protons hit a beryllium target in order to produce the positive kaons required for the experiment. A series of achromats selects particles with central momentum of 75GeV, with momentum resolution about 1%.

A differential Cerenkov counter called CEDAR is responsible for tagging the positive kaons which represent 6% of the beam content.

#### 1.3.2.2 The detector

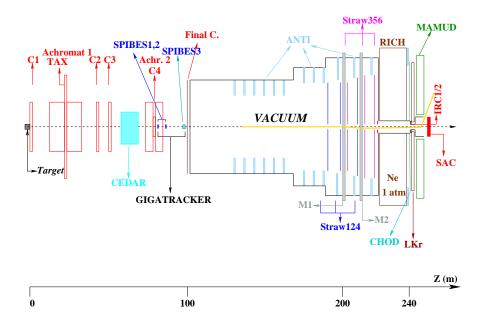

Figure 1.6 shows the entire experimental setup of the P326 experiment. It basically consists of two spectrometers, one for the beam and another for the decay products

Figure 1.5: Missing mass distribution for  $K^+ \to \pi^+ \nu \bar{\nu}$  and the concurrent decay modes

in the forward direction. Particle identification, photon vetoing and track momentum measurements are used with a certain degree of redundancy. The elements of detector together with a brief description are summarized below:

- GIGATRACKER: Three planes of thin silicon pixel detectors perform redundant momentum measurement on the beam components (beam spectrometer).

- ANTI: Ring-shape anti-counters surrounding the vacuum tank provide full coverage for photons originating from the decay region with angles up to 50 mr.

- STRAW TRACKER: A double magnetic spectrometer consisting of chambers of straw tubes measures the direction of the merging pion providing a redundant measurement of its momentum.

Figure 1.6: P326 experimental setup

- RICH: The ring Imaging Cherenkov counter provides muon and pion identification.

- CHOD: A multi-gap glass RPC hodoscope performs triggering and precise timing of the charged track.

- LKR: A liquid Krypton electromagnetic calorimeter acts as photon veto in the angular region between 1.0 and 15.0 mr.

- MAMUD: A magnetized hadron calorimeter performs high efficiency muon identification.

- IRC1-2, SAC: Intermediate ring and small angle photon veto calorimeters cover the angular regions around and in the beam.

# **1.3.3** Gigatracker requirements

The missing mass resolution required in order to reject kinematically the background can be obtained with kaon and pion momentum resolutions of 0.3% and 1%, respectively, and an angular resolution of the angle between the kaon and pion directions in the order of  $50 - 60\mu rad$  [16].

This specifications define the required performance of the upstream and downstream spectrometer, namely the Gigatracker and the Double Spectrometer.

While the spatial resolution of the beam spectrometer has small influence on the missing mass resolution, allowing for a relatively big pixel size  $(300 \times 300 \mu m^2)$ , time resolution has an important influence. Giving the high particle rate crossing the three silicon stations ( $60 \ MHz/cm^2$  in average), a pion track measured in the downstream spectrometer may be wrongly associated to a kaon candidate in the Gigatracker, so the kinematical rejection power is degraded.

For time resolution of 150ps, simulations show that about 36% of the events have more than one track in the Gigatracker. On the other hand, the probability of wrong matching is about 8% for cases with two tracks in the Gigatracker. The later is dependent on the matching algorithm, therefore may improve when software features are enhanced.

Another consequence is the need for a local time-to-digital converter with bin size as low as 150ps at the front-end level. This enhances the complexity of the chip and puts pressure on the power budget distribution. Several iterations at the collaboration level have set a compromise between the beam geometry and the layout of the silicon station allowing for smaller dimensions of the readout chip than initially proposed. A configuration of  $2 \times 5$  readout chips with pixel column length of 13.5 mm has been agreed on. This provides better management of on chip resources and power delivery scheme.

Another important requirement is the material budget. The target is  $0.4\% X_0$ , with silicon sensor thickness of 200  $\mu m$  and readout chip thickness of  $100\mu m$ .

The radiation environment must also be considered. The accumulated design fluence for the Gigatracker sensors is  $1.8 \times 10^{14}$  1MeV *neutrons/cm*<sup>2</sup> maximum, corresponding to a radiation exposure total dose (estimated for 100 days operation) of about 10 Mrad. Available radiation hard technologies for both sensor and front-end fabrication may not assure operation up to this dose, without substantial degradation in performance. Therefore, it is proposed to replace the silicon stations after a maximum threshold fluence and to operate the sensors at lower temperature (a couple of degrees below zero), in order to extend their lifetime under radiation[22].

# 1.4 PANDA and QCD

The proposed PANDA experiment will enable the new FAIR facility at GSI to play a significant role in strong interaction physics, providing a link between nuclear physics and hadron physics. The experiment proposes to study interactions of antiprotons with nucleons and nuclei in a fixed target experimental setup.

Antiproton beams in 1-15GeV energy range, stored in the High-Energy Storage Ring (HESR) for in-ring experiments, will provide access to the heavier strange and charm quarks and to copious production of gluons. The proposed program, using resonant antiproton-proton annihilation, is a quantitative and qualitative extension of successful experiments performed recently at the antiproton accumulator at FNAL, USA. Accessible energies are enhanced by a factor of almost 2, while luminosity by a one order of magnitude reaching  $2 \times 10^{32} cm^{-2} s^{-1}$ . At FAIR, advanced antiproton cooling techniques will enable high energy resolution (momentum spread of  $10^{-4} - 10^{-5}$ ) and a more versatile detector setup will be employed allowing for the first time a measurement of both electromagnetic and hadronic decays with high precision. The goal is to achieve comprehensive precision spectroscopy of the charmonium system for a detailed study, particularly of the confinement part of the QCD potential. This in turn will help to understand the key aspects of gluon dynamics which are being investigated and quantitatively predicted in the framework of Lattice QCD. The charm quark is sufficiently heavy to lend itself to non-relativistic perturbative treatment far more reliably than the light up, down, and strange quarks. Thus, an optimal testing ground for a quantitative understanding of confinement is provided by charmonium spectroscopy, i.e. the spectroscopy of mesons built of charmed quark-antiquark pairs ( $c\bar{c}$ ).

A central part of the antiproton program presented in this proposal is the first search for gluonic excitations, glueball and hybrids, in the charmonium mass range where they are expected to be less mixed with the multitude of normal mesons. The unambiguous determination of the gluonic modes would establish an important missing link in the confinement problem of hadrons.

The proposed experimental program at the HESR will address the open problem of interactions and in-medium modifications of hadrons with charm quarks in nuclei. On the one hand, this is an extension of the present GSI research program. On the other hand, the program will provide the first insight into the gluonic charmonium-nucleon and charmonium-nucleus interaction. A quantitative knowledge of charmonium-nucleon cross sections is considered to be of crucial importance in the identification of the formation of the quark-gluon plasma in ultra-relativistic heavyion collisions.

Antiproton beams at the proposed facility will allow efficient production of hypernuclei with more than one strange hadron. The program opens new perspectives for nuclear structure studies and is a novel complement to the proposal to study the structure of nuclei with radioactive beams. The nucleon with the strange quark (hyperon) is not restricted in the population of nuclear states as neutrons and protons are. These exotic nuclei offer a variety of new and exciting perspectives in nuclear spectroscopy and for studying the forces among hyperons and nucleons.

The observed dominance of matter in the universe may be attributed to CP violation, an effect directly observed in the decay of neutral kaons and, very recently, in B mesons. CP violation can be studied in the charm meson sector and in hyperon decays, with the HESR storage ring running at full luminosity. An observation of significant CP violation would indicate physics beyond the Standard Model.

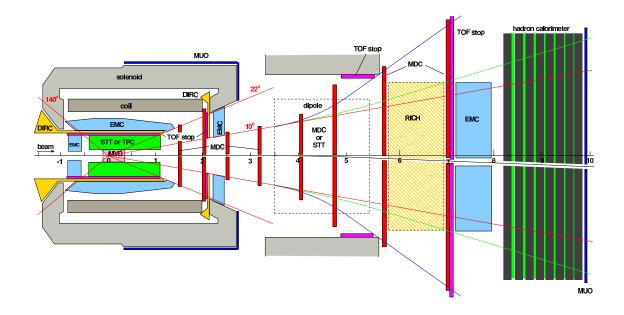

# 1.4.1 Experimental setup

The general layout of PANDA is based on two magnetic spectrometers. A target spectrometer consisting of a solenoid surrounds the interaction region and a forward spectrometer with a dipole magnet provides angular coverage for the most forward angles. The combination of two spectrometers offers full angular coverage, taking into account the wide range of energies and the flexibility requirement. It is foreseen that some of the components of the detector setup be exchanged or added for specific experiments that may require so. Both spectrometers include instrumentation for charged-particle track reconstruction, particle identification, energy and momentum measurement, as well as photon and neutral particle detection.

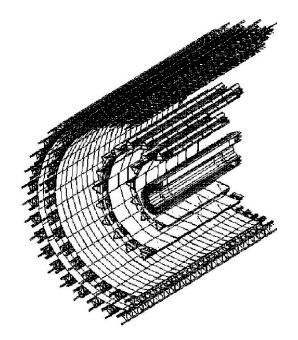

Figure 1.7: Top view of the PANDA detector

The target spectrometer consists of several detectors in a shell-like arrangement. Most of the instruments are contained within the coils of the solenoid:

- a complex silicon micro-vertex detector (MVD) for tracking and particle identification;

- a second tracking detector built out of straw tubes (STT) or a time projection chamber (TPC);

- a ring-imaging Cherenkov (RICH) counter for particle identification;

- two sets of mini drift chambers (MDC);

- another Cherenkov detector based on aerogel RICH or detection of internally reflected Cherenkov light (DIRC);

- an electromagnetic calorimeter (EMC) for photon detection.

Outside the return yoke of the solenoid scintilator bars for muon identification are foreseen (MUO).

The forward spectrometer covers the angular region below 10° and 5° in horizontal and vertical direction, respectively. The current design is based on a 1 m gap dipole and tracking planar devices distributed perpendicular to the beam direction for momentum analysis of charged particles. A shashlyk-type calorimeter consisting of lead scintillator sandwiches (EMC) will detect the photons in the forward range, while other neutral and charged particles with high momentum will be detected in the hadron calorimeter and the muon counters (MUO).

An additional time-of-flight measurement across the two spectrometers is under discussion. It would consist of a start detector within the MVD (possibly one of the layers of the MVD) and stop detectors at the exit window of the target spectrometer within the forward spectrometer.

# 1.4.2 MVD requirements

Experiments aiming at the identification of open charm and strangeness depend on the identification of secondary decays of particles in displaced vertices. Strange hadrons have decay lengths on the order of cm while charmed mesons and baryons decay within several tens to a few hundred  $\mu m$ . The vertex detector and the tracking capability of the target spectrometer will have to be suited for both. While PANDA will focus on charm production, the identification of kaons will greatly enhance the efficiency for

D mesons with large branchings into channels accompanied by kaons. Thus, a design that can handle both length scales will greatly improve the efficiency of PANDA.

With the interaction rates foreseen for the PANDA experiment, expected in experiments using heavy targets, the innermost detector layers will be exposed to high particle densities. A pixel design is favored for the innermost detectors.

The micro vertex detector (MVD) is foreseen to be mounted very close to the interaction point. It consists of five barrel shaped layers plus five disk-shaped detectors in forward direction. The three innermost layers are composed of pixel detectors to achieve best resolution and to be able to easily detect decay vertices displaced from the interaction point. The outer layers may be composed of microstrip detectors which are easier to handle. The baseline technology chosen for the pixel detectors is the hybrid active pixel sensor for which extensive knowledge is provided by several LHC experiments. The use of already mature designs from those experiments, as well as completely new custom design are the options. As alternatives to silicon pixels, GaAs based detectors are considered as well as much thinner monolithic pixel sensors where the problem of radiation hardness would have to be solved.

PANDA will have to handle significantly slower particles as well. This offers the opportunity to contribute to the particle identification with energy loss measurements. However, the detector thickness will be a crucial parameter for the detector design compared to other applications.

Spatial resolution requirements derived from the secondary vertex resolution favors a  $100 \times 100 \mu m^2$  pixel size, which is smaller than the existing LHC designs. The electronics will have to feature high dynamic range amplitude measurement matching the momentum range of the particles crossing MVD. Since the operation of the PANDA experiment does not foresee any selective trigger, in order to maximize physics yield, the front-end electronics must provide continuous readout. All this arguments favor a custom solution for the MVD pixel design.

# 1.5 ALICE and quark-gluon plasma

# 1.5.1 QGP probes in heavy-ion collisions

Traditionally the QGP probes are classified in three classes[23]:

- *soft-probes* with typical momentum below 1 GeV/c;

- *heavy flavour-probes* particles containing heavy quarks like c or b quarks;

- high- $p_T$  probes particles with momentum range above several tens of GeV/c.

The last two probes are collectively known as hard probes.

#### Soft-probes

The measurement of global event observables, like the charged-particle multiplicity or the charged-particle pseudo-rapidity distribution, can bring interesting information about the thermodynamical parameters of the reacting matter after collision. The initial energy density  $\varepsilon$  in the central interaction region is linked to the transverse energy distribution through the Bjorken formula:

$$\varepsilon = \frac{1}{\pi R^2 c \tau_0} \frac{dE_T}{dy} \tag{1.5.1}$$

where R is the radius of the nuclei and  $\tau_0$  is the initial equilibration time  $\sim 1 fm/c$ [24]. The temperature T can be expressed by the average transverse momentum  $\langle p_T \rangle$ . This means that  $\varepsilon - T$  plot (one possible representation of the nuclear equation of state) can be studied by representing  $\langle p_T \rangle$  as function of  $dE_T/dy$ .

In reality, the Bjorken formula is model dependent especially through  $\tau_0$ , so it cannot point out a phase transition alone.

Moreover, the multiplicity information can test hadroproduction models. For instance, the phenomenological approach[25] predicts that the pseudo-rapidity distribution  $dN_{ch}/d\eta$  is a linear combination of the number of participants  $N_{part}$  and the number of binary collisions  $N_{coll}$ .

Leptons can escape from the dense and strongly interacting reaction region, thus providing information about the condition at the time of their creation. In particular,  $\rho$ ,  $\omega$  or  $\phi$  vector mesons, with the lifetime comparable to that of the QGP and which can decay into resonant lepton pair  $(l\bar{l})$ , may change their mass or width when they are produced inside the dense medium. Partial chiral symmetry restoration or final state interaction may be responsable for this phenomena. The latter can be sorted out by comparing the results obtained in the hadronic and leptonic decay modes. Previous nucleus-nucleus collision experiments at SPS at CERN have reported significantly higher dilepton yield in the low mass region (below 600 MeV), for central collisions, than the yield expected from hadron decays.

Another interesting aspect is the difference between the lifetimes of  $\rho(\sim 1.32 fm/c)$ and  $\omega(\sim 23.4 fm/c)$ . Therefore the relative effect on the properties of the two mesons may represent a dynamic probe of the QGP.

Other important phenomena at this energy range is the predicted strangeness enhancement due to a lower threshold for strangeness production in de-confined medium [26], and can flag the QGP formation.

#### Heavy-flavour probes

Hard partons created in the first instants of the nuclear collision in primary partonic scatterings are expected to lose energy by gluon radiation while crossing the dense medium created after the collision [27]. Due to "dead-cone" effect, the energy loss of massive partons like the charm or beauty quarks will be smaller than the energy loss of "light" quarks. Therefore, comparing the attenuation of D or B mesons with lighter counterparts will allow to test the consistency of the interpretation of quenching effects as due to energy loss in a deconfined medium and to investigate the density of the QGP medium.

Another effect on heavy probes is the quarkonium suppression due to the Debye screening in the deconfined matter.  $J/\psi$  suppression has been already observed at SPS[28], but the situation may be complicated at higher energies by possible charmonium recombination in the hot medium. The recombination effect is less likely to affect bottomium, due to its higher mass.

### High- $p_T$ probes

High- $p_T$  partons produced in initial parton-parton scatterings fragment into jets that cross the deconfined matter, suffering significant energy losses. This effect has already been observed at RHIC as high- $p_T$  jet suppression[29] and the suppression of back-to-back jet correlations[30].

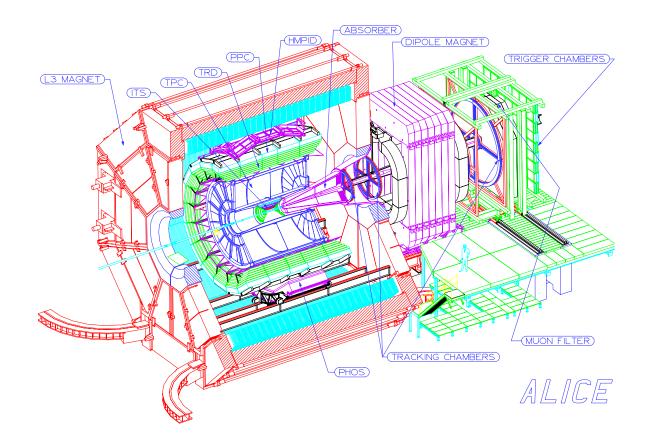

# 1.5.2 The ALICE detector

ALICE (A Large Ion Collider Experiment) was defined in its proposal document[31] as a general-purpose heavy-ion experiment designed to study the physics of strongly interacting matter and the quark-gluon plasma (QGP) in nucleus-nucleus collisions at

Figure 1.8: The ALICE detector

LHC. In addition to the heavy A-A collision program, the experiment will gather data in p-A and p-p runs in order to provide reference data for the heavy-ion program, but also for genuine p-p and p-A studies. The foreseen collision energy for the heaviest ion is  $\sqrt{s} = 5.5 TeV$ , which is 30 times higher than RHIC.

The detector is divided in central and forward parts (see figure 1.8). The first gathers detectors for hadrons, electrons and photons, covering the mid-rapidity region, while the forward part is a muon spectrometer.

The central part consists of the Inner Tracking System (a silicon based tracking detector), the Time-Projection Chamber (a cylindrical gaseous chamber for tracking and momentum measurement of charged particles), three detctors for particle identification (Time-of-Flight (TOF) detector, Transition-Radiation detector (TRD) and a single-arm ring Cherenkov imaging (HMPID) detector) and a single-arm electromagnetic calorimeter (PHOS). All central detectors are embedded in a large L3 solenoidal magnet. The forward muon spectrometer consists of a massive absorber, a dipole magnet and 14 planes of tracking muon chambers. Zero-Degree Calorimeters (ZDC) cover the beams' rapidity in order to measure the spectator nucleons in heavy-ion collision.

The track reconstruction efficiency is about 90% at  $p_T > 1 GeV/c$ , being dominated by the TPC. At lower momentum the tracks are reconstructed mainly in the ITS. All detectors of the central part, except the electromagnetic calorimeter, have particle identification capabilities. The total momentum coverage for particle identification is from 0.1 GeV/c to a few GeV/c. The choice of the magnetic field (0.5T) is a compromise between the reconstruction efficiency and the resolution in the high- $p_T$ region.

Figure 1.9: Section of the Inner Tracking System

# 1.5.3 The Inner Tracking System

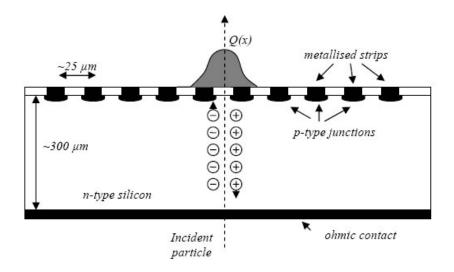

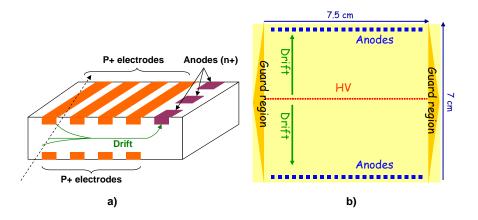

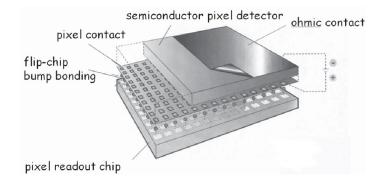

The ITS is a 6-layer cylindrical tracking detector based on three silicon technologies (figure 1.9: silicon pixel detectors (SPD) for the inner 2 layers, silicon drift detectors (SDD) for the middle 2 layers and silicon microstrip detectors (SSD) for the outer 2 layers.

The SPD detectors provide only spatial resolution and high granularity, being equipped with binary readout. The SDD and SSD have analog readout offering momentum measurement and particle identification capability in the non relativistic region.

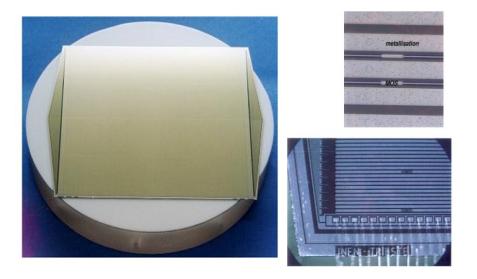

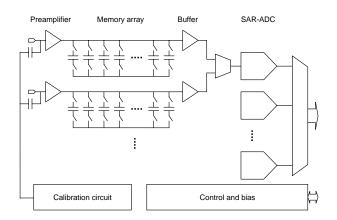

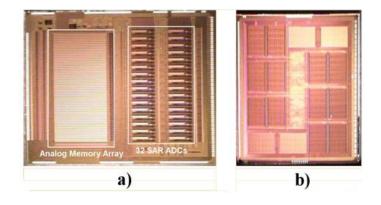

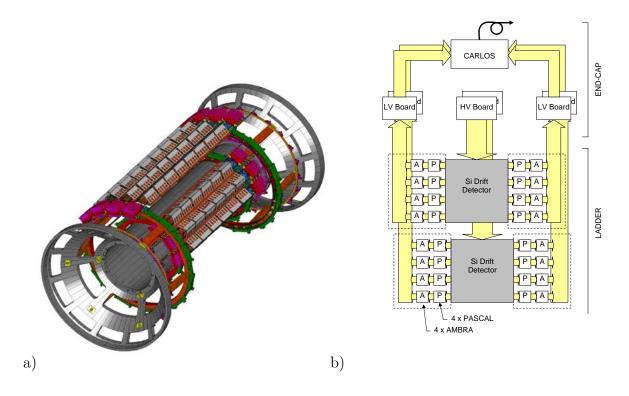

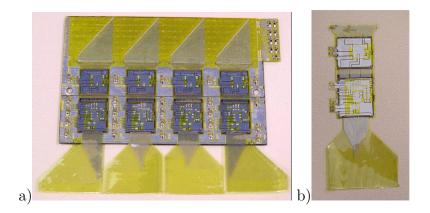

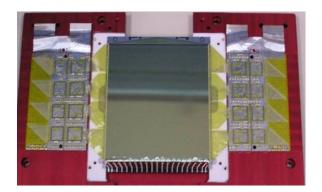

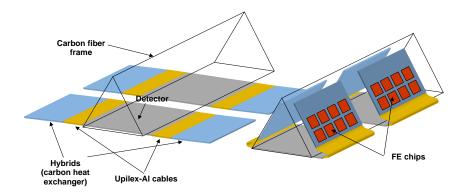

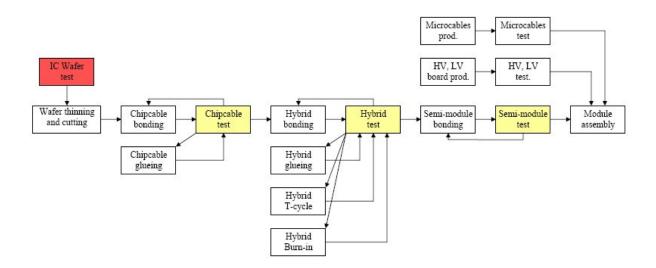

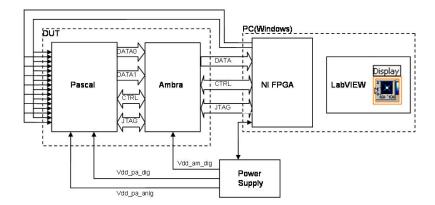

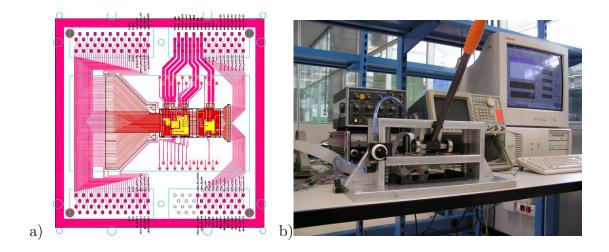

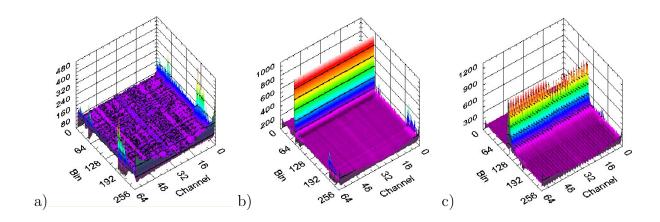

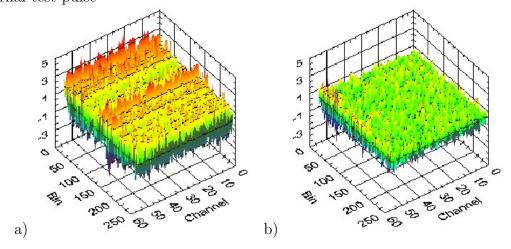

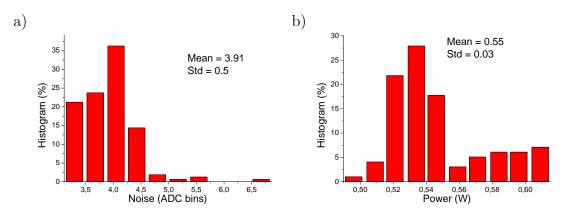

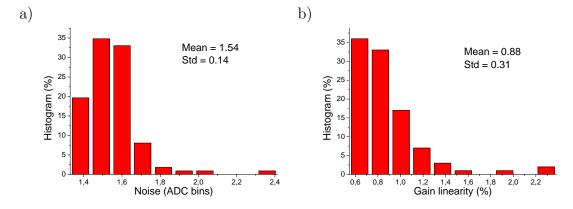

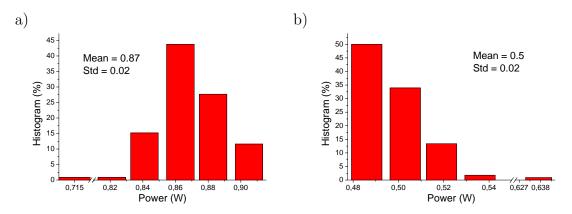

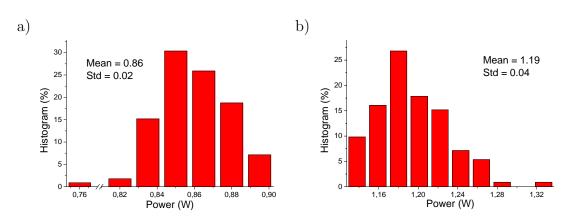

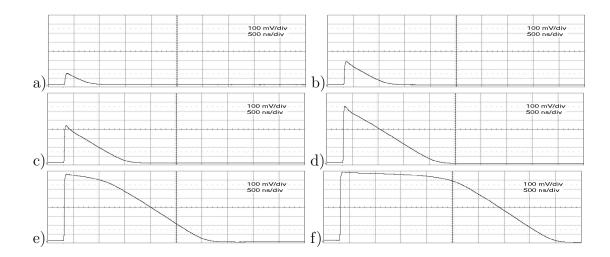

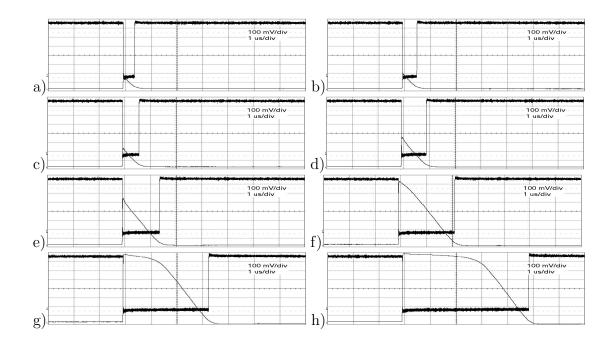

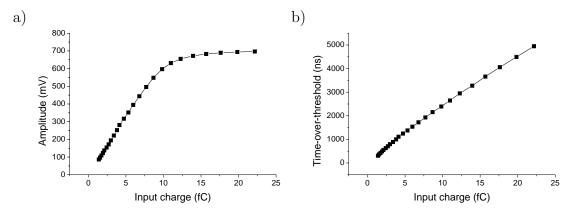

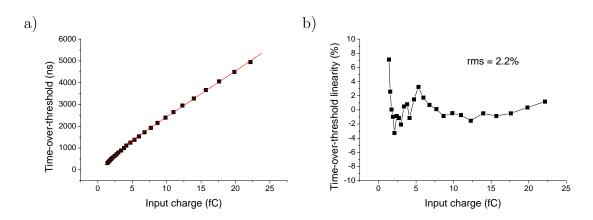

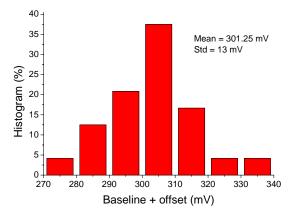

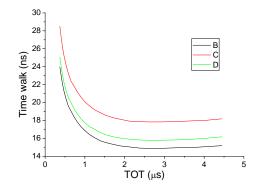

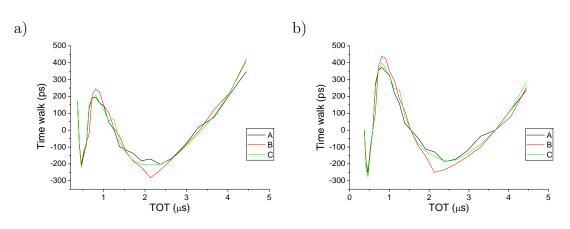

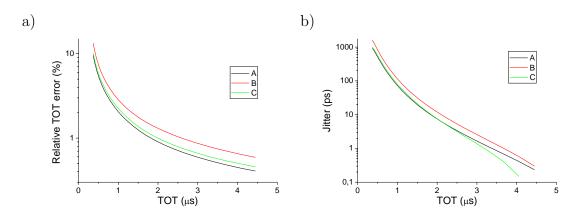

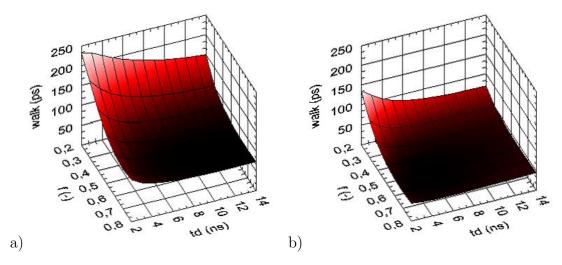

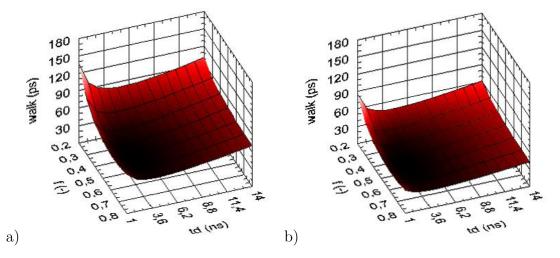

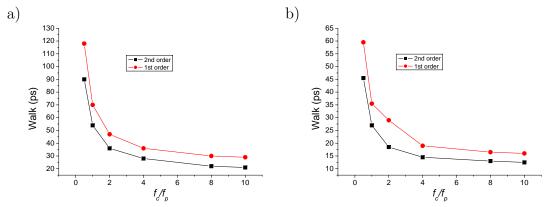

Featuring high granularity and spatial resolution, as well as sufficient momentum resolution via energy loss measurement in the lower momentum range, the ITS contributes to the determination of multiplicity distributions and inclusive particle