# Università degli Studi di Torino Scuola di Dottorato in Scienza e Alta Tecnologia Indirizzo di Fisica e Astrofisica XXVII Ciclo

Development of Integrated Pixel Front-End Electronics in 65 nm CMOS Technology for Extreme Rate and Radiation at HL-LHC

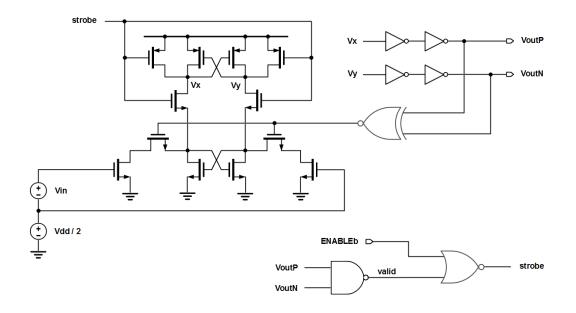

Luca Pacher

### Candidate

Luca Pacher

### Supervisor

Dr. A. Rivetti Istituto Nazionale di Fisica Nucleare (INFN) Sezione di Torino

### **External Reviewer**

Prof. G. Traversi Dipartimento di Ingegneria e Scienze Applicate Università degli Studi di Bergamo

### Ph.D. Tutor

Prof. M. Costa Dipartimento di Fisica Università degli Studi di Torino

### Ph.D. Coordinator

Prof. M. Gallio Dipartimento di Fisica Università degli Studi di Torino

### Date of dissertation

April 20, 2015

Signature from head of Ph.D. committee

All'unica persona a cui avrei voluto poter dedicare queste pagine. Grazie davvero...

Now I know we said things, did things that we didn't mean And we fall back into the same patterns, same routine. But your temper's just as bad as mine is, You're the same as me. When it comes to love you're just as blinded. Baby, please come back it wasn't you, baby it was me. Maybe our relationship isn't as crazy as it seems Maybe that's what happens when a tornado meets a volcano...

### Contents

| Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Part I - Background and motivations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 11                                                   |

| 1 ASIC requirements for the CMS pixel detector upgrade at HL-LHC         1.1 Introduction         1.2 General concepts and definitions         1.3 The CMS experiment at the LHC         1.4 Current layout of the CMS silicon pixel tracker         1.5 State of the art hybrid pixel ASIC in CMS         1.6 LHC operations in 2009-2014 and upgrade scenarios         1.7 Evolution of the CMS pixel detector through 2020         1.8 Pixel ASIC requirements for HL-LHC         1.9 IC technology choice         1.10 New pixel ASIC research communities on 65 nm CMOS | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

| Part II - Research activity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 51                                                   |

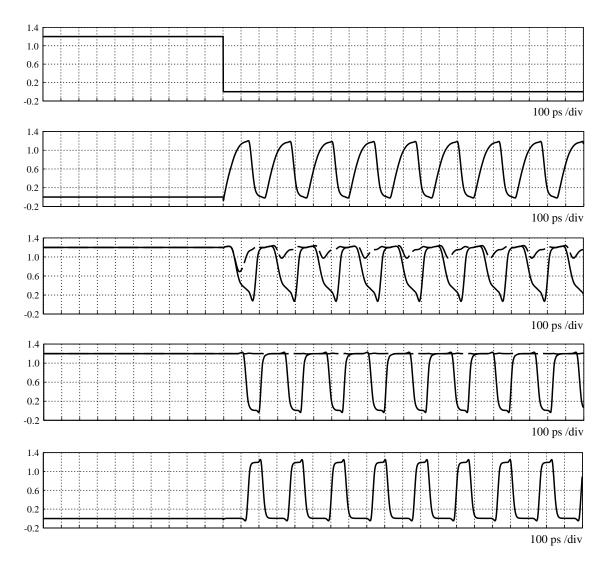

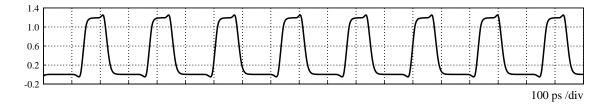

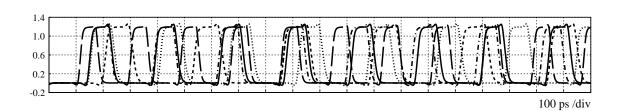

| <ul> <li>2 Synchronous pixel Front-End design in 65 nm CMOS technology</li> <li>2.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

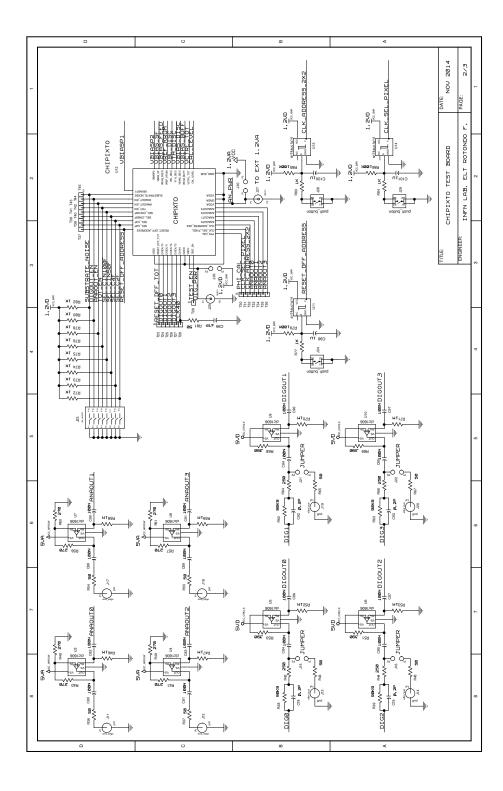

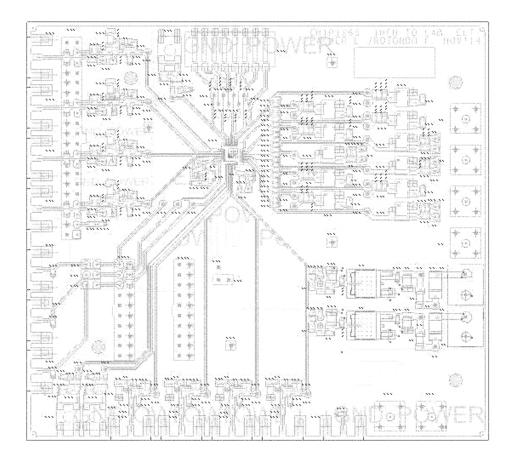

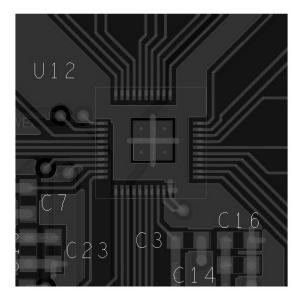

| <ul> <li>3 The first CHIPIX65 submission</li> <li>3.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 178<br>183<br>183<br>187                             |

#### Contents

|                                                                     | Clock and digital control signals distribution                | 192                                                         |

|---------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------|

|                                                                     | Bias generation and power distribution                        | 195                                                         |

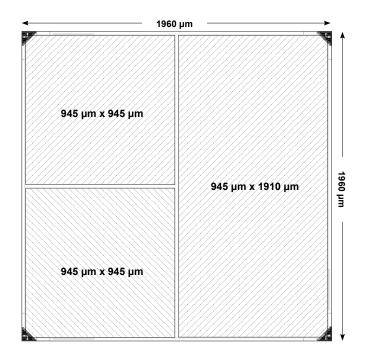

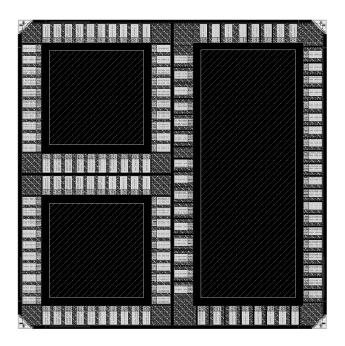

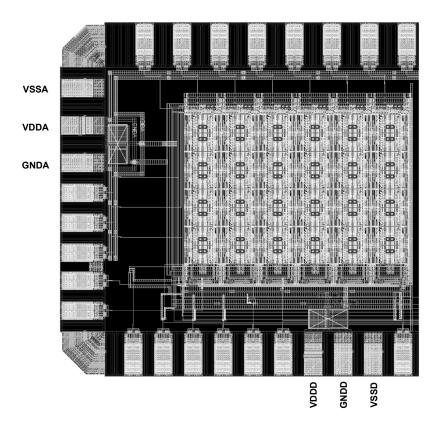

|                                                                     | Core pixel matrix layout assembling                           | 201                                                         |

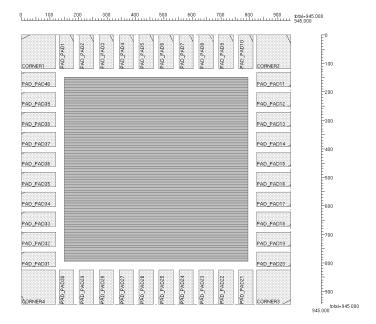

|                                                                     | I/O power partitioning and final pad frame assembling         | 206                                                         |

| 3.6                                                                 | CHIPIX_VFE1/2x1 assembling                                    | 213                                                         |

|                                                                     | Serial readout and configuration                              |                                                             |

|                                                                     | Chip integration                                              | 217                                                         |

| 3.7                                                                 | Sign-off and foundry transfer                                 | 220                                                         |

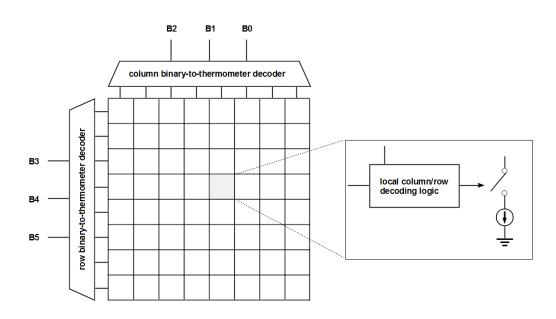

| 3.8                                                                 | Standard-cell based design of a column/row decoder            | 221                                                         |

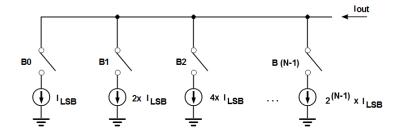

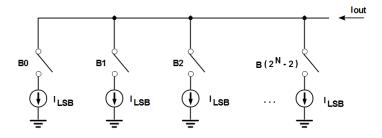

|                                                                     | DAC architecture and specifications                           | 221                                                         |

|                                                                     | HDL design entry and synthesis for the column/row DAC decoder | 226                                                         |

|                                                                     | Automated place-and-route (PNR)                               | 231                                                         |

|                                                                     | Design export/import and final verification                   | 233                                                         |

| 3.9                                                                 | Summary                                                       | 235                                                         |

|                                                                     | • • • • • • •                                                 | 0.0 <b>7</b>                                                |

| 4  Exp                                                              | perimental setup and measurements                             | 237                                                         |

| <b>4 Exp</b><br>4.1                                                 | Introduction                                                  |                                                             |

| -                                                                   |                                                               | 237                                                         |

| 4.1                                                                 | Introduction                                                  | 237<br>238                                                  |

| $4.1 \\ 4.2$                                                        | Introduction                                                  | 237<br>238<br>239                                           |

| $ \begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \end{array} $                  | Introduction                                                  | 237<br>238<br>239<br>245                                    |

| $ \begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \end{array} $                  | Introduction                                                  | 237<br>238<br>239<br>245<br>245                             |

| $ \begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \end{array} $                  | Introduction                                                  | 237<br>238<br>239<br>245<br>245<br>252                      |

| $ \begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \end{array} $                  | Introduction                                                  | 237<br>238<br>239<br>245<br>245<br>245<br>252<br>252        |

| 4.1<br>4.2<br>4.3<br>4.4                                            | Introduction                                                  | 237<br>238<br>239<br>245<br>245<br>245<br>252<br>252        |

| $ \begin{array}{r} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ \end{array} $ | Introduction                                                  | 237<br>238<br>239<br>245<br>245<br>252<br>252<br>252<br>253 |

### Abstract

The recent discovery at the CERN Large Hadron Collider (LHC) of resonances consistent with a Higgs boson with a mass of about 125  $\text{GeV/c}^2$  gives today a compelling and concrete case to define and justify future exploration strategies. As a matter of fact, the LHC will remain the most powerful accelerator ever built in the world for at least two decades. In order to fully exploit the discovery potential of this machine, the foreseen LHC research program extends over more than 20 years, investigating and validating the mathematical consistency of the Standard Model (SM) at the TeV energy scale and searching for evidences of new physics signatures.

According with the expected increase of the machine performance in the forthcoming years, several upgrade projects involving existing LHC general-purpose detectors ATLAS and CMS have already started. Detailed RD programs are necessary in order to explore and develop new cutting-edge detector technologies and dedicated readout electronics. This is mandatory since the typical time scale required for the design, construction and commissioning of such large and complex systems is of the order of 5 to 10 years.

In particular, the CMS experiment tracking community is already engaged in long-term upgrade plans (~2022-2023) when the foreseen High-Luminosity (HL) LHC operating conditions will impose significant upgrades for the inner tracking system, demanding the installation of a new silicon pixel detector. With increased performance the machine will deliver pp collisions with an instantaneous luminosity of the order of  $10^{35}$  cm<sup>-2</sup>s<sup>-1</sup>, one order of magnitude higher with respect to the current design value. The upgrade aims to reach an integrated luminosity of 3000 fb<sup>-1</sup> in 10 years, providing a chance to access extremely rare physics processes.

New LHC operating conditions introduce several challenges in the design of the new pixel detector. With such a luminosity and a centre-of-mass energy of 14 TeV, the nominal collision rate of 40 MHz will lead to unprecedented pileup (up to 200), introducing extreme rates and radiation levels. More layers equipped with sensors featuring high granularity, speed and adequate radiation hardness will be required. Hence hybrid silicon pixel detectors will continue to play a fundamental role.

The innermost pixelated layer will have to cope with unprecedented Total Integrated Dose (TID), up to 10 MGy in 10 years. Smaller pixels of the order of 50  $\mu$ m × 50  $\mu$ m will be required to maintain high spatial resolution and tracks separation under high pileup conditions. The particle flux will increase to about 500 MHz/cm<sup>2</sup>, leading to unprecedented hit rates (1-2 GHz/cm<sup>2</sup>) and an estimated rate per pixel of the order of 50-100 kHz in the innermost layer. Thus a development plan devoted to the design of a new pixel Application Specific Integrated Circuit (ASIC) for CMS has started. More on-chip intelligence will be introduced to deal with the increased hit rates. The expected increased L1 trigger latency (up to 20  $\mu$ s) will require more local data storage capabilities, efficient zero-suppression schemes and higher output bandwidths.

The foreseen usage of thinner sensors of the order of 100-150  $\mu$ m to increase the radiation tolerance determines reduced signals, needing low-noise (ENC < 150  $e^-$  RMS at nominal 100 fF total input capacitance) and low-threshold (about 1000  $e^-$  minimum detectable charge) performance for the pixel analogue Front-End. Moreover, an in-time response below 25 ns is required in order to cope with the nominal LHC bunch interaction rate, while keeping bias currents to acceptable values and targeting to a maximum total power dissipation of 10  $\mu$ W/pixel.

Different approaches for both the analogue signal processing (preamplification and shaping) and the charge digitization (binary-only readout, time-over-threshold techniques, usage of local or shared A/D converters) are under consideration. However, in order to fully exploit speed and integration densities offered by ultra-deep submicron (UDSM) technologies, most of the signal processing will be performed into the digital domain, with a chance to move as much as possible temporary data storage (buffering) and trigger matching from the chip periphery to the pixel level.

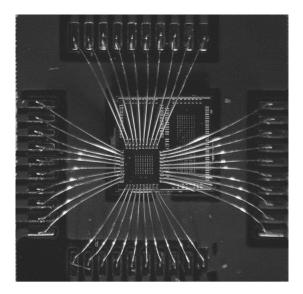

Radiation tolerance and higher integration level constraints led to the choice of a commercial 65 nm CMOS technology as the presently favoured IC fabrication technology for the design of the new pixel chip. At present 65 nm represents the most advanced technology node adopted to implement full-custom solutions for radiation detection and measurements in particle physics and medical imaging applications. Technology qualification and radiation hardness studies using this 65 nm CMOS process are now part of the international RD53 collaboration research program officially supported by CERN, that involves both ATLAS and CMS pixel ASIC communities as well as other non-LHC experiments and groups interested in designing in 65 nm. Furthermore, Italian CMS and ATLAS groups have submitted in July 2013 a detailed proposal to INFN/CSN5 to finance a new three-years research program on CMOS 65 nm, leading to the approval of the CHIPIX65 project.

This thesis presents my personal contributions on the design and test of both analogue and digital integrated circuits in such a commercial 65 nm CMOS technology. All design activities were carried out with extensive usage of professional and industry-standard Computer Aided Design (CAD) softwares for circuit simulation and mask layout provided by the VLSI Design Laboratory of the Torino section of INFN. The entire research work has been supported by the CHIPIX65 collaboration and the Torino CMS Tracker group.

Preliminary pixel Front-End test structures, small pixel matrix prototypes and other analogue, digital and mixed-signal building blocks have been submitted on October 2014 by the CHIPIX65 collaboration to the foundry access service. They were received back from the manufacturer for laboratory test measurements and bench characterizations at the beginning of 2015. These studies have provided the necessary first steps towards the design of a future complete hybrid pixel ASIC demonstrator suitable for the long-term CMS pixel detector upgrade.

Luca Pacher - Ph.D. Thesis

# Part I Background and motivations

### Chapter 1

### ASIC requirements for the CMS pixel detector upgrade at HL-LHC

An extrapolation to HL-LHC unprecedented operating conditions of state of the art integrated circuit solutions for the readout of hybrid pixel detectors introduces major challenges on several fronts. This chapter provides necessary background information and motivations to frame the overall Ph.D. research activity, devoted to the development of first prototypes of integrated pixel Front-End electronics in a commercial 65 nm CMOS technology suitable for the long-term CMS experiment pixel detector upgrade at HL-LHC.

Keywords: Particle tracking, silicon pixel detectors, LHC, luminosity, pileup, radiation damage, CMS experiment, VLSI, ASIC, readout chip, trigger, CMOS technology, upgrade, RD53, CHIPIX65

### **1.1 Introduction**

Precise and efficient tracking and vertexing procedures are of utmost importance in high energy physics experiments. The reconstruction of the tracks provides measurements of charged particles momenta exploiting the curvature of trajectories in a magnetic field. Hits measured closest to the interaction region are fundamental in determining the position of the primary vertex (PV) and of secondary vertices (SV) originated by the decays of short-living particles. Pattern recognition, reconstruction of vertices and precise measurements of their impact parameters in a high track multiplicity environment necessary require sensors featuring high granularity, spatial resolution, speed and radiation hardness.

The last generation of particle physics experiments has seen substantial progresses in the usage of segmented silicon detectors for particle tracking. [Weilhammer 2000, Spieler 2005, Hartmann 2009]. Silicon sensors offer high spatial resolutions (5-10  $\mu$ m) and maximum granularity, therefore can cope with huge track densities. Sensors in which the charge collection is driven by drift exhibit fast response and radiation hardness. In addition, good energy resolutions can be obtained with a low amount of material. The linear energy transfer for a Minimum Ionizing Particle (MIP) traversing a bulk of silicon is  $\approx 390 \text{ eV}/\mu\text{m}$ . This leads to about 32'000 electron/hole pairs in 300  $\mu$ m of thickness thanks to the low ionising energy (3.6 eV) of silicon. Hence internal charge multiplication is usually not required. At the same time, a particle hit can be measured with no appreciable effect for the particle itself, because the energy loss is small ( $\approx 0.1 \text{ MeV}$  in 300  $\mu$ m). Furthermore, multiple Coulomb scattering effects are minimized. However, maintaining good signal-to-noise ratios in hostile radiation environments requires low operating temperatures in order to keep leakage currents at low levels. Finally, silicon exhibits excellent mechanical properties and affordable production cost to instrument large areas.

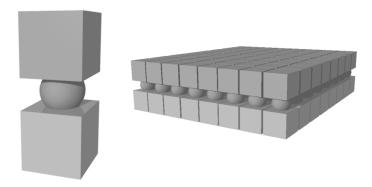

Figure 1.1: Schematic view of hybrid pixel sensors technology. Sensor and readout electronics are fabricated on different silicon wafers and then connected through the bump-bonding technique.

Among the reach variety of silicon sensor technologies developed for radiation detection, hybrid pixel detectors are a well-established and mature detector technology. They have been proved to be an efficient and reliable solution for particle tracking.

As reviewed in Figure 1.1, hybrid pixel detectors consists of an array of sensitive cells connected to a dedicated readout chip through the bump bonding technique [Rossi 2006]. Sensor and readout electronics are therefore fabricated separately on different silicon wafers and than mated together using a flip-chip processing. Tiny balls of conducting solders, typically In or Pb-Sn, are deposited on special bonding pads. Despite flip-chip technology is extensively adopted in semiconductor industry for the packaging of integrated circuits with ball grid array (BGA) surface mounting, the small pixel sizes demanded for particle physics and imaging applications require the usage of advanced cutting-edge processing.

Each pixel cell is a reverse-biased junction formed by a high resistivity substrate and a collection electrode connected to its own Front-End electronics. A ionizing particle that crosses the sensor generates electron/holes pairs that move in the depletion region under the action of the electric field. Hence the charge collection in the sensor is driven by drift, providing fast response and radiation hardness. The current signal induced at the electrode is processed by an optimized analogue Front-End chain that provides necessary amplification and filtering. Additional signal processing in the analogue and digital domains is performed according to the target application.

The usage of a custom designed mixed-signal Application Specific Integrated Circuit (ASIC) is the only means to achieve the integration density required to read out the large number of pixel cells and implement all functionalities demanded for the application. Furthermore, commercially available deep-submicron CMOS technologies have been also demonstrated to be radiation tolerant, as discussed later in the chapter.

Innermost layers of pixel detectors arranged in a barrel geometry around the interaction region and equipped with highly specialized readout circuits represent therefore a standard configuration for tracking detectors of a collider experiment. This is the case of pixel tracking systems installed at the CERN Large Hadron Collider (LHC) near Geneva. Operating conditions for a pixel tracking system at the LHC are challenging. In order to better understand and justify upgrade scenarios as well as pixel ASIC specifications and performance requirements discussed through the chapter, the next section introduce some fundamental concepts and common terminology related to the LHC environment. A description of the Compact Muon Solenoid (CMS) experiment is given in Section 1.3. According to the aim of this work, most of the attention will be then focused on pixel readout electronics.

#### **1.2** General concepts and definitions

The LHC machine [Evans 2008] was conceived to deliver both proton-proton and nucleon-nucleon (lead ions) collisions at nominal unprecedented operating conditions. The choice of a hadron collider is well suited to the task of exploring new energy domains, resulting de facto into a discovery machine. For a symmetrical collider with two head-to-head<sup>1</sup> interacting beams of energy  $E_b$  each one, the available centre-of-mass energy in the lab frame is  $\sqrt{s} = 2E_b$ . Indeed, the fundamental constituents participating in the scattering are partons, which carry a fraction x of the 4-momentum of the particles in the beam. Hence the centre-of-mass energy of the effective hard scattering process is  $\sqrt{\hat{s}} = \sqrt{x_1 x_2 s}$  and can span several orders of magnitude. According to proton parton distribution functions, on average  $x \approx 0.15 - 0.20$ . The nominal centre-of-mass energy of the LHC has been therefore chosen  $\sqrt{s} = 14$  TeV in order to explore particle physics at the 1-2 TeV energy scale.

For a given physics channel with production cross section  $\sigma_{ev}$  the number of events per second (event rate) generated in a collider system is usually written as

$$\frac{dN_{\rm ev}}{dt} \; = \; \sigma_{\rm ev} \, L(t)$$

where L(t) is a fundamental machine parameter referred to as *instantaneous luminosity*. It depends on collider parameters such as number of particles per bunch, number of bunches per beam, collision frequency (bunch crossing rate) and beams intersection area, but not on the physics process. The luminosity represents therefore the number of collisions per unit time and cross-sectional area of the beams. The production cross-section for a certain process of interests depends instead on the energy scale, spanning several order of magnitude depending on the physics under consideration. Furthermore, for each unstable particle produced in the interaction, a wide range of decay channels open, each one characterized by a certain branching ratio (BR).

Certainly the statistical significance of various data analyses relies on the total number of events produced across several data taking runs,

$$N_{\rm ev}~=~\sigma_{\rm ev}~L_{\rm int}$$

being

$$L_{\rm int} = \int_0^{T_{\rm run}} dt \ L(t)$$

the *integrated luminosity*. Due to intrinsic inefficiencies of detectors (either because one or more detector subsystems are temporarily unavailable, or simply because the detector is out of data taking for some reason) the integrated luminosity recorded by the experiments is lower than the total luminosity delivered by the machine. Both delivered and recorded integrated luminosity values are therefore carefully tracked as a function of time during on-line activities.

<sup>&</sup>lt;sup>1</sup> Actually, a non-zero crossing angle is required to identify the position of the interaction.

| Parameter                         | Design value $(pp \text{ interactions})$ |

|-----------------------------------|------------------------------------------|

| Circumference                     | 27 km                                    |

| beam energy                       | $7 { m TeV/beam}$                        |

| centre-of-mass energy $\sqrt{s}$  | 14  TeV                                  |

| Number of bunches per beam        | 2808                                     |

| Number of particles per bunch     | $\approx 10^{11}$                        |

| Bunch radius at interaction point | $15 \ \mu \mathrm{m}$                    |

| Bunch length                      | 53 mm                                    |

| Bunch crossing rate               | 40 MHz                                   |

| Luminosity                        | $10^{34} \text{ cm}^{-2} \text{ s}^{-1}$ |

Table 1.1: LHC nominal design parameters [Evans 2008].

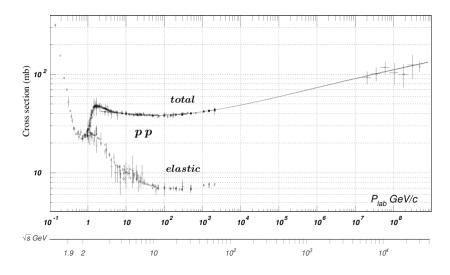

Figure 1.2: Total and elastic proton-proton cross section as a function of the centre-of-mass energy [Amsler 2008]. The foreseen total cross section at nominal LHC ( $\sqrt{s} = 14$  TeV) is about 100 mb. Note that experimental data are available only from cosmic ray measurements.

High luminosities and high centre-of-mass energies in a hadron collider are therefore fundamental requirements in order to discovery or confirm physics processes with predicted small cross sections. At the LHC, protons are accelerated from 450 GeV up to 7 TeV. One beam circulates clockwise and the other one counterclockwise in separate but close orbits. They are forced to collide in specific regions around which the experiments are located. Protons are grouped into 2808 bunches, each one containing about  $10^{11}$  particles. Protons constituting a bunch are confined in a cylindrical volume of 30  $\mu$ m diameter and 5.3 cm length. According to nominal parameters, the accelerator has been designed to deliver proton-proton interactions every 25 ns at nominal beam energy of 7 TeV/beam and luminosity up to  $10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> [Evans 2008]. Indeed, due to the complexity and unprecedented operating conditions of such a giant machine, actual LHC performance from the first commissioning phase to physics data taking periods did not yet reach nominal values and continuously evolved in time in terms of collision frequency, luminosity and beam energy. Nevertheless, following considerations assume nominal design values. A more detailed description of effective LHC operations in 2009-2013 and its foreseen evolution through 2020 is remanded to Section 1.6. Most important nominal LHC design parameters are summarized in Table 1.1.

Figure 1.2 shows the total proton-proton cross section as a function of the centre-of-mass energy. At the design value  $\sqrt{s} = 14$  TeV, the total proton-proton cross section is expected to be roughly 110 mb (1 b = 10 fm × 10 fm). Main contributions to the total cross-section are about 60 mb from non-diffractive processes, 10 mb from diffractive processes and 40 mb from elastic scattering. The total inelastic cross section is therefore about 70 mb. This implies that at the nominal LHC luminosity  $10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>, general-purpose detectors ATLAS and CMS have to cope with a total interaction rate of the order of  $10^9$  inelastic events/s. Indeed, interesting physics processes have cross sections that involve the production of a Higgs boson at the LHC are of the order of a few tens pb. Most of particles created in each beams interaction do not contain any interesting new physics signatures, but only contribute to a huge background of particles with low transverse momentum  $p_T$ . Commonly referred to as minimum bias, this leads to an overwhelming background compared to the expected interesting physics channels.

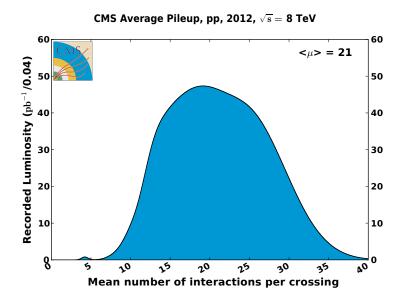

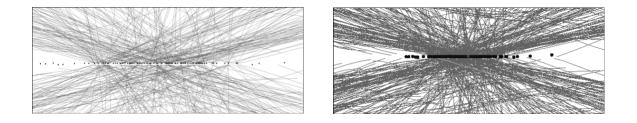

The event rate is further increased by the fact that multiple proton-proton hard-scatter interactions can occur in the same bunch crossing, resulting into multiple primary vertices (PV) reconstructed by tracking algorithms. Commonly referred to as *pileup* (PU), this increases the overall number of particles emerging from the interaction region at each beams intersection. As a matter of fact, major challenges for ATLAS and CMS experiments arise from particle tracking under high PU conditions. As an example, Figure 1.3 shows an event display recorded by the CMS experiment during the 2012 data taking period with more than 20 reconstructed primary vertices in the same bunch crossing. The effective number of interactions for each beams intersection randomly varies and depends on instantaneous bunch-by-bunch luminosities. Figure 1.4 presents the typical distribution for the mean number of primary vertices per bunch crossing reconstructed in CMS. As a first approximation the PU distribution roughly fit a Poisson distribution. Detailed procedures have been deployed to compute PU distributions from delivered and recorded instantaneous luminosity measurements<sup>2</sup>. The average PU is proportional to the total proton-proton cross section, to the luminosity and inversely proportional to the bunch crossing rate. Hence the average PU increases by increasing the instantaneous luminosity. At LHC design luminosity  $10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> a mean of about 20 inelastic interactions superimpose in the same bunch crossing. As discussed later in the chapter, the foreseen luminosity upgrade by one order of magnitude up to  $10^{35}$  cm<sup>-2</sup> s<sup>-1</sup> at HL-LHC will therefore increase the average PU up to 200, introducing unprecedented experimental challenges.

<sup>&</sup>lt;sup>2</sup>The bunch-by-bunch recorded luminosity is usually determined by means of very-forward hadron calorimeters.

Figure 1.3: Event display recorded by the CMS experiment during the 2012 data taking period at  $\sqrt{s} = 8$  TeV with more than 20 reconstructed primary vertices in the same bunch crossing.

Figure 1.4: Distribution for the mean number of reconstructed primary vertices per bunch crossing (average pileup) in CMS during the 2012 data taking period. CMS public results.

Charged particles are detected by silicon tracking systems built around the interaction point. As discussed, at nominal LHC design luminosity, about  $10^3$  charged particles from more than 20 overlapping proton-proton interactions emerge on average from the interaction region every 25 ns. Silicon pixel detectors are placed closest to the beam line. Assuming an innermost barrel pixel detector located at 5 cm radius, this leads to a nominal maximum charged particle flux<sup>3</sup> of  $\approx 50 \text{ MHz/cm}^2$  [Rossi 2006]. A detector technology featuring high granularity, fast response, low occupancy<sup>4</sup> and radiation hardness is therefore essential, justifying the extensive usage of hybrid silicon pixel detectors in the innermost regions of LHC experiments. Certainly by increasing sensor granularity to reduce the occupancy increases the number of readout electronics channels, requiring the implementation of highly specialized, low-power, radiation-hard readout electronics.

A few remarkable considerations are related to *trigger* aspects. As previously discussed, nominal LHC operating conditions lead to a total event rate in ATLAS and CMS experiments which is of the order of 1 GHz. Since it is impossible to store and process the large amount of data associated to all proton-proton collisions delivered by LHC, a drastic reduction of the event rate has to be performed. In practice, only about 100 events/s can be stored for subsequent data analysis, corresponding to 250 MB/s. Furthermore, most of the events are minimum bias and do not contain any interesting physics signature. A selection criteria must be therefore envisaged to filter out non interesting events, reducing the event rate to about 100 kHz that can be written to permanent storage. The goal of the trigger is to perform such a required huge data reduction by a factor  $10^7$ . As described shortly thereafter, trigger requirements and output data rate introduce major implications in the design of suitable pixel readout electronics.

Trigger systems implemented at LHC experiments are complex, multi-step selection criteria. The time available to accept or reject an event is limited to the nominal bunch crossing time of 25 ns. According to a common terminology adopted for both ATLAS and CMS experiments, the event rate is reduced in two steps called Level-1 (L1) trigger and High-Level Trigger (HLT). The L1 trigger is mainly hardware-based. In order to increase flexibility, L1 hardware components are implemented in commercial FPGA technology wherever possible, but also custom-designed ASIC solutions are used where speed, density and radiation tolerance requirements must be satisfied. The L1 trigger information is basically extracted from coarsely segmented data provided by calorimeters and external muon detectors. The HLT is instead a software-based trigger system executed in dedicated computing farms equipped with thousands commercial CPUs. It processes all the events accepted by the L1 trigger, accessing the complete read-out detector raw data.

The L1 trigger inspects each bunch crossing. Nevertheless, the trigger decision, commonly referred to as L1-Accept (L1A), is communicated to all sub-detectors only after a certain amount of time or the order of  $\mu$ s. The L1 trigger latency is defined as the time between a given bunch crossing and the arrival time of the L1A to sub-detectors. Only events associated to an L1A must be readout (zero-suppression) thus requiring a dedicated trigger matching logic to accomplish this task. At present, the nominal trigger latency adopted in CMS is 3.2  $\mu$ s, corresponding to 128 bunch intersections assuming a 40 MHz collision rate.

The necessity of a trigger introduces therefore fundamental requirements for the design of the readout electronics. Events information must be in facts continuously registered while waiting for the L1 trigger decision, requiring temporary data storage (*buffering*) features. Each event must be therefore properly associated to the corresponding bunch crossing (*time-stamping*) starting from a 40 MHz machine clock distributed to all detector sub-systems.

In case of pixel detectors, data buffering and retrieval capabilities must be embedded into the digital readout architecture of the Front-End ASIC, as there is no time to move the large amount of hit raw data anywhere else. As discussed later, this introduces additional challenges in perspective of the design of a new pixel ASIC suitable for HL-LHC.

$<sup>^3\,</sup>$  Also referred to as track rate.

$<sup>^4</sup>$  For a given detector subsystem, the occupancy is defined as the number of busy channels at a time with respect to the total number of available readout channels. It is usually expressed as a percentage.

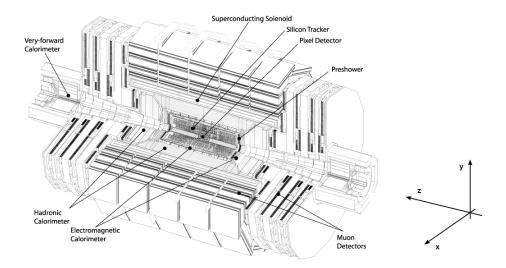

### 1.3 The CMS experiment at the LHC

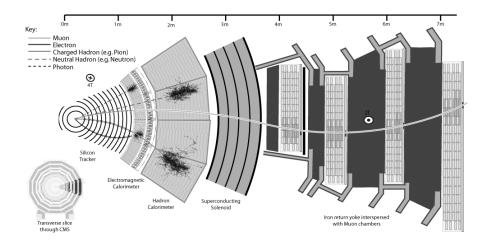

The Compact Muon Solenoid (CMS) detector [Chatrchyan 2008] operating at the CERN LHC has been conceived as a multi-purpose experiment to study proton-proton and lead-lead collisions at the TeV energy scale. In the following, a brief summary of the the CMS detector design is presented. A perspective view of the CMS apparatus is shown in Figure 1.5, completed by a transverse view in Figure 1.6. The overall layout follows the typical arrangement of a hermetic detector at a symmetric collider experiment, covering as much as possible the volume around the interaction region. Main components are therefore an innermost tracking system surrounded by electromagnetic and hadronic calorimeters and external muon detectors, arranged in a cylindrical geometry completed by endcaps structures.

The fundamental aspect in the detector design is the choice of a solenoidal<sup>5</sup> configuration of the magnetic field for tracking measurements. At the core of the CMS detector sits in fact a 13 m long, 6 m diameter, 4 T superconducting solenoid<sup>6</sup>, which provides a large 12 Tm bending power which ensures good momentum resolution for charged particles with transverse momenta up to 1 TeV. The flux of the magnetic field is returned by a by a 10'000 tonnes iron yoke, composed of 5 barrel wheels and 6 endcap disks. The yoke also provides mechanical support for the entire system. The choice of a solenoidal configuration led therefore to a very compact design, allowing calorimeters and the inner tracking system to be installed inside the free bore of the magnet coil, resulting into a strong improvement in the detection and energy measurement of electrons and photons.

The overall tracking volume occupies a cylinder of 5.8 m length and 2.6 m diameter inside the 4 T homogeneous magnetic field provided by the solenoid. The CMS physics program requires excellent track reconstruction and vertexing performance. Efficient and precise reconstruction of charged particles tracks with transverse momenta above 1 GeV in the pseudorapidity range  $|\eta| < 2.5$  are of primary importance for CMS. Moreover, precise reconstruction of secondary vertices and measurements of impact parameters are fundamental in the identification of short-living particles which are produced in many of interesting physics channels. Together with electromagnetic calorimeter and and the muon system, tracker information is used to identify electrons and muons respectively. Furthermore, tracking information is heavily used in the high level trigger of CMS. Hence a detector technology featuring high granularity, fast response and radiation hardness is essential in order to cope with the intense particle flux emerging from the interaction region at each bunch crossing. The main challenge in the design of the tracking system was to develop detector components able to operate in the LHC harsh environment for a long lifetime. High granularity, speed and radiation tolerance requirements led to a tracker design entirely based on silicon detector technologies.

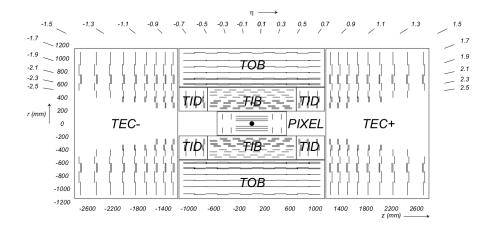

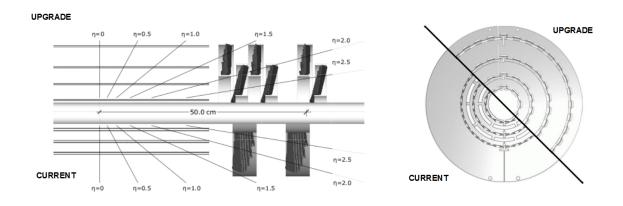

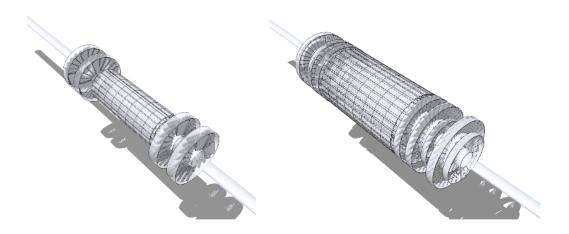

A schematic cross section of the CMS inner tracking system is shown in Figure 1.7. The tracker is composed of an innermost Silicon Pixel Tracker (SPT) and an outer Silicon Strip Tracker (SST). The SPT is a system of 3 barrel layers equipped with hybrid pixel detectors at radii 4.4 cm, 7.3 cm and 10.2 cm, closest to the interaction region. The volume between 20 cm of radius and 116 cm is occupied instead by the SST, which is composed of 10 barrel layers of silicon microstrip detectors. Each barrel layer is completed by endcaps disks on each side, consisting of 2 disks in the pixel tracker and 3 plus 9 disks in the strip tracker. With a total active silicon area of about 200 m<sup>2</sup>, the CMS tracker is the largest full-silicon tracking system ever built, with 1440 pixel-modules and 15'148 strip modules, corresponding to 66 million pixels and 9.3 million silicon strips.

A more exhaustive description of the current layout of the CMS pixel detector and its Front-End electronics is remanded to Section 1.4 and 1.5 respectively.

$<sup>^5\,</sup>$  In contrast, the ATLAS (A Toroidal LHC ApparatuS) detector uses a toroidal configuration, as suggested by the name of the experiment.

$<sup>^6~</sup>$  Despite 4 T is the nominal value, a magnetic field of 3.8 T has been adopted during the first 2009-2013 data taking period.

Figure 1.5: Perspective view of the CMS detector. The global coordinate system adopted by the collaboration has the origin centered at the nominal collision point inside the experiment. The z-axis points along the beam line, the y-axis points vertically upwards and the x-axis points radially inward to the centre of the LHC ring. The azimuthal angle  $\phi$  is measured from the x-axis in the x - y plane and the radial coordinate in this plane is denoted as r. The polar angle  $\theta$  is measured from the z-axis. Pseudorapidity is defined as  $\eta = -\ln [\tan \theta/2]$  and is extensively used to quote angular distributions.

Figure 1.6: Transverse slice of the CMS detector and signatures for different particles crossing the volume. From inward to outward: all-silicon tracking system, ECAL, HCAL, superconducting solenoid and external muon chambers hosted by the iron yoke for the return of the magnetic field.

Figure 1.7: Schematic cross section of the CMS inner tracking system, 5.8 m length times 2.6 m diameter. Each line represents a detector module. The Silicon Pixel Tracker (SPT) is composed of 3 barrel layers and 2 endcap disks each side. The Silicon Strip Tracker (SST) is partitioned into two different sub-systems, referred to as Tracker Inner Barrel (TIB) and Tracker Outer Barrel (TOB). The TIB extends in radius towards 55 cm and |z| < 65 cm. It is composed of 4 barrel layers supplemented by 3 endcap disks at each end, referred to as Tracker Inner Disks (TID). The TIB system is surrounded by the TOB, consisting of 6 barrel layers completed by 9 lateral disks, referred to as Tracker End Caps (TEC).

The tracking volume is surrounded by an electromagnetic calorimeter (ECAL) to achieve accurate measurements of energy and position of electrons and photons, which are fundamental objects for the CMS physics program. The need for a good energy resolution and di-photon mass resolution ( $\approx 1\%$  at 100 GeV) led to the choice of a homogeneous calorimeter composed of finely segmented lead-tungstate (PbWO<sub>4</sub>) crystals with coverage up to  $|\eta| < 3$ , featuring fast response and necessary radiation tolerance. The scintillation light is detected by silicon avalanche photodiodes (APD) in the barrel region and vacuum phototriodes in the endcap regions. A preshower system is installed in front of the endcaps for  $\pi^0 \to \gamma\gamma$  rejection.

The calorimetry system is then completed by a hadronic calorimeter (HCAL) for the measurement of the energy and direction of jets and reconstruction of missing transverse-energy contributions. A large geometric coverage is therefore of primary importance for this purpose. Coverage up to  $|\eta| < 3$  is provided by a brass/scintillator sampling calorimeter surrounding ECAL and coupled to wavelenght-shift optical fibres which convert the scintillation light detected by hybrid photodiodes (HPD). Coverage up to  $|\eta| < 5$  is obtained by an iron/quartz-fibre calorimeter which Cherenkov light is detected by standard photomultiplier tubes (PMT).

The iron return yoke of the magnet is large enough to host the external muon identification system, composed by 4 stations of aluminium Drift Tubes (DT) in the barrel region and Cathode Strip Chambers (CSC) in the endcap region, both complemented by Resistive Plate Chambers (RPC) which ensure redundancy and robustness for the muon trigger system.

The overall dimensions of the CMS detector are 21.6 m length and 14.6 m diameter, with a total weight of 12'500 tonnes and geometric coverage up to  $|\eta| < 5$ .

#### 1.4 Current layout of the CMS silicon pixel tracker

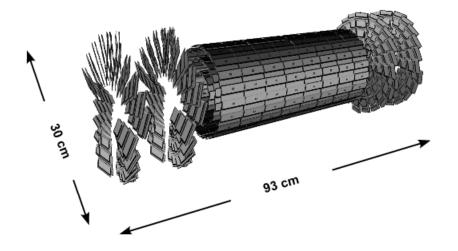

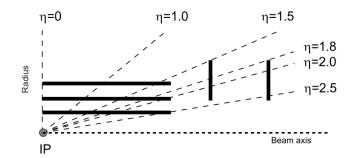

The current layout of the CMS silicon pixel tracker is depicted in Figure 1.8. The pixel detector is placed closest to the interaction region, covering a pseudorapity range  $|\eta| < 2.5$  and matching the acceptance of the outer silicon strip tracker. The pixel tracker consists of three barrel layers (BPIX) complemented by two endcap disks on each side (FPIX). Barrel layers are 53 cm long and are located at mean radii 4.4 cm, 7.3 cm and 10.2 cm. Endcap disks are placed at  $\pm$  35.5 cm and  $\pm$  45.5 cm from the nominal interaction point, extending in radius from about 6 cm to 15 cm. The total pixelated active area is about 1 m<sup>2</sup> and occupies a cylindrical volume of about 93 cm length and 30 cm diameter. This layout ensures 3 tracking points over almost the full  $|\eta| < 2.5$ range. Figure 1.9 shows the geometrical acceptance as a function of pseudorapidity  $\eta$ . The barrel pixel detector covers the central region and the endcap disks the forward region. The transition barrel/forward occurs at  $|\eta| \approx 1.5$ .

The pixel tracker is instrumented with 285  $\mu$ m thickness hybrid silicon pixel detectors. In order to achieve comparable spatial resolutions in both  $r\phi$  and z directions, an almost-square pixel size of 100  $\mu$ m × 150  $\mu$ m has been adopted. Hit reconstruction algorithms heavily rely on the charge information measured for each pixel cell. The effect of charge-sharing among adjacent pixels induced by the large Lorentz drift in the 4 T magnetic field is in fact exploited to enhance the spatial resolution with a charge interpolation [Chatrchyan 2014]. The detector modules are therefore deliberately not tilted in the barrel layers. In the endcap disks instead, they are arranged in a turbine-like geometry to introduce charge-sharing. Nominal spatial resolutions are about 10  $\mu$ m in the transverse coordinate and 20  $\mu$ m in the longitudinal coordinate.

The operating conditions for the pixel tracker are challenging. As already discussed, at the LHC design luminosity of  $10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> on average  $10^3$  charged particles from more than 20 overlapping proton-proton interactions are created every bunch crossing. The position of the pixel detector close to the interaction region implies very high track densities and particle fluences that require both radiation-hard sensors and readout electronics. At nominal luminosity the innermost barrel layer placed at at radius  $\approx 4$  cm has to withstand a charged particle flux of the order of 100 MHz/cm<sup>2</sup>, which in turn leads to pixel rate of about 10 kHz/pixel by adopting a 100  $\mu$ m  $\times$  150  $\mu$ m pixel size. This ensures a low occupancy of the order of  $10^{-4}$  per bunch crossing, below 1%. The nominal charged particle flux decreases to 600  $\rm kHz/cm^2$  at radius 22 cm and 30  $\rm kHz/cm^2$  at 115 cm. Nominal radiation levels and particle fluences in different radial layers of the CMS tracker for an integrated luminosity of 500 fb<sup>-1</sup> (corresponding to  $\approx 10$  years of nominal LHC operations) are summarized in Table 1.2. As one can see, assuming LHC design values the innermost barrel layer placed at radius 4.4 cm experiences a particle fluence of the order or  $3 \times 10^{14} n_{eg}/\text{cm}^2$  per year. Radiation hardness requirements led to the choice of pixel sensors implemented as heavily doped  $n^+$  electrodes into a high resistance n-type substrate. Despite the higher costs due to the double sided processing, the n-on-n concept was chosen as the collection of electrons ensures a high signal charge with moderate bias voltages after high hadron fluences, below 600 V. Extremely high operating voltages can be therefore avoided. This reduces the issues of leakage currents and high voltage breakdowns in a highly miniaturized environment. Most important CMS pixel sensor specifications are summarized in Table 1.3.

According to the hybrid pixel architecture, each pixel cell is bump-bonded to a full-custom ASIC. The overall readout electronics employed in the CMS tracking system has been designed in a commercial 0.25  $\mu$ m CMOS technology by following special layout design rules which ensure the required radiation hardness [Snoeys 2000]. As a result, the lifetime of the silicon pixel tracker is limited by the radiation damage to silicon sensors. The innermost barrel layer has been designed to survive at least 2 years at nominal LHC luminosity, whereas the expected lifetime extends to more than 10 years for the third layer. Nevertheless, due to readout limitations in the current pixel Front-End ASIC, a replacement of the entire pixel tracker is already planned for 2016-2017, as discussed later in the chapter. In the following, the present Front-End ASIC coupled to CMS pixel sensors is described.

Figure 1.8: The current layout of the CMS Silicon Pixel Tracker (SPT) consists of three 53 cm long barrel layers (BPIX) at radii 4.4 cm, 7.3 cm and 10.2 cm complemented by two endcap disks on each side (FPIX) at  $z = \pm 35.5$  cm and  $\pm 45.5$  cm, extending in radius from about 6 cm to 15 cm. With a total active area ~1 m<sup>2</sup> the CMS pixel tracker occupies a cylindrical volume of about 93 cm length and 30 cm diameter around the nominal interaction point.

Figure 1.9: Geometrical coverage of the current CMS pixel detector in terms of pseudorapidity around the nominal interaction point [Chatrchyan 2008]. The three barrel layers cover the central region and the endcap disks the forward region. The transition barrel/forward occurs at  $\eta \approx 1.5$ . The current layout ensures 3 tracking points over almost the full  $|\eta| < 2.5$  range.

| radius [cm] | charged particle flux $[\text{cm}^{-2} \text{ s}^{-1}]$ | dose $[kGy]$ | fluence of fast hadrons $[\rm cm^{-2}]$ |

|-------------|---------------------------------------------------------|--------------|-----------------------------------------|

| 4           | $10^{8}$                                                | 840          | $32 \times 10^{14}$                     |

| 11          |                                                         | 190          | $4.6 \times 10^{14}$                    |

| 22          | $6 \times 10^6$                                         | 70           | $1.6 \times 10^{14}$                    |

| 75          |                                                         | 7            | $0.3 \times 10^{14}$                    |

| 115         | $3 \times 10^5$                                         | 1.8          | $0.2 \times 10^{14}$                    |

Table 1.2: Hadron fluence and radiation dose in different radial barrel layers of the CMS tracker assuming nominal LHC operating conditions and 500 fb<sup>-1</sup> integrated luminosity, corresponding to  $\approx 10$  years operations [Chatrchyan 2008]. The fast hadron fluence is a good approximation to the 1 MeV neutron equivalent fluence. The innermost pixelated layer has to withstand a nominal charged particle flux of the order of 100 MHz/cm<sup>2</sup> and  $\approx 1$  MGy Total Ionizing Dose (TID) in 10 years.

| Parameter               | Specification                                                  |

|-------------------------|----------------------------------------------------------------|

| sensor technology       | $n^+$ -on- $n$                                                 |

| pixel size              | $100 \ \mu { m m} \ (r\phi) \ \times \ 150 \ \mu { m m} \ (z)$ |

| sensor thickness        | $285 \ \mu \mathrm{m}$                                         |

| Lorentz shift at 4 T    | $\approx 59 \ \mu m$ (barrel region)                           |

| nominal reverse bias    | -300 V                                                         |

| bump-bonding            | 15-20 $\mu$ m diameter indium bumps                            |

| sensor capacitance      | 80-100 fF per pixel                                            |

| nominal leakage current | 10 nA per pixel                                                |

Table 1.3: Summary table for most important CMS pixel sensor specifications [Chatrchyan 2008]. The choice of an almost-square pixel size along with the charge-sharing among adjacent pixels lead to a nominal resolution of 10  $\mu$ m in  $r\phi$  and 20  $\mu$ m in z.

### 1.5 State of the art hybrid pixel ASIC in CMS

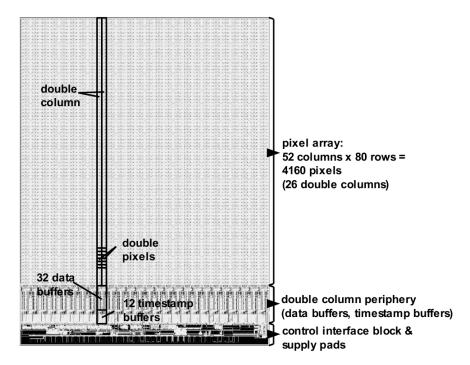

CMS pixel sensors are made of 4160 cells arranged into 52 columns × 80 rows. Each sensitive cell covers an area of 100  $\mu$ m × 150  $\mu$ m. Signals generated by charged particles traversing the detector are processed and readout by a full-custom ASIC bump-bonded to the sensor. The initial concept of the chip dates back more than 15 years ago. Originally implemented in a dedicated 0.8  $\mu$ m radiation tolerant process, the latest version of the ASIC, named PSI46V2, has been produced in a commercial 0.25  $\mu$ m CMOS technology<sup>7</sup> officially supported by CERN [Barbero 2004, Erdmann 2005, Gabathuler 2005, Kastli 2006].

Despite the usage of a commercial solution, the integrated electronics has been made radiation-hard by design (RHBD) using special layout techniques, such as enclosed-layout transistors (ELT) and guard rings structures in order to ensure necessary radiation tolerance [Anelli 1999, Snoeys 2000]. According to a common terminology recently adopted within the LHC pixel ASIC community, the current CMS pixel readout chip (ROC) is a first generation pixel ASIC [Garcia-Sciveres 2013].

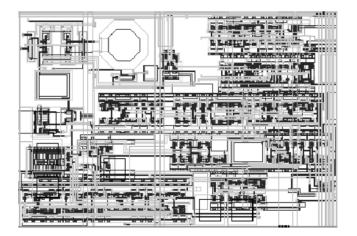

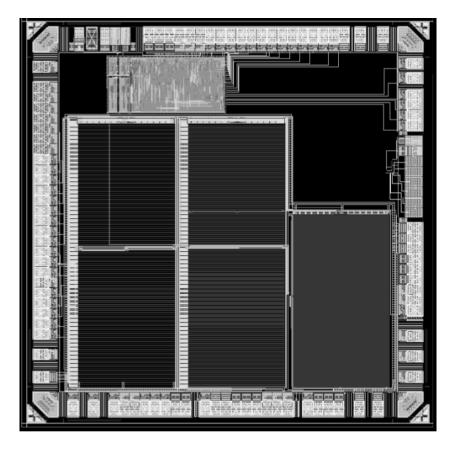

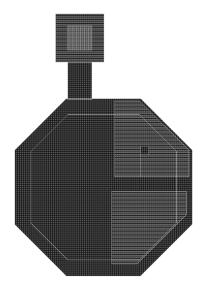

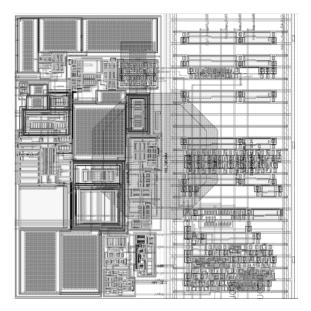

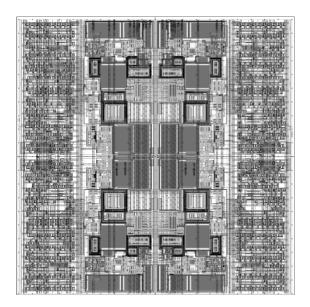

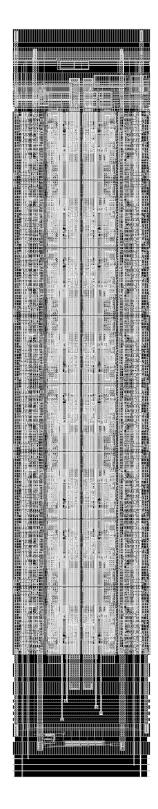

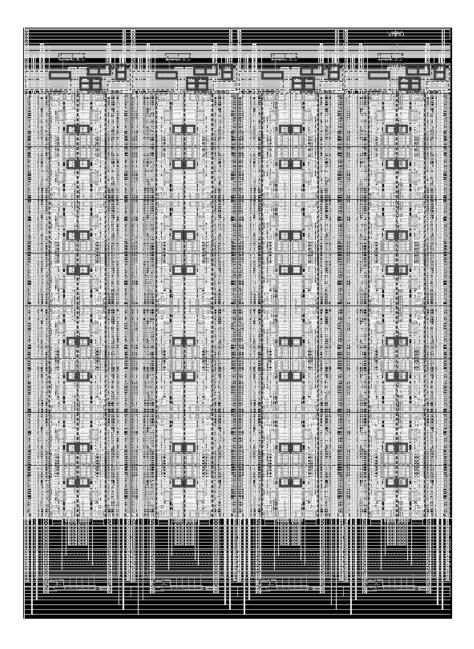

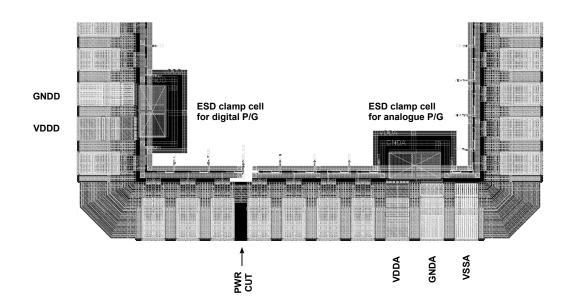

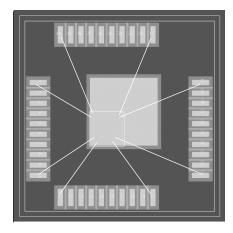

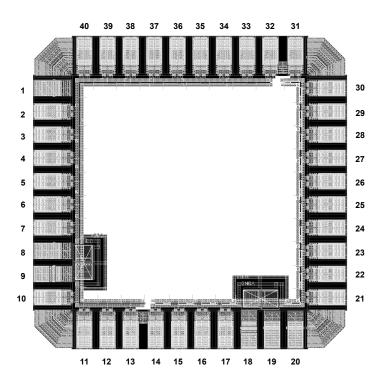

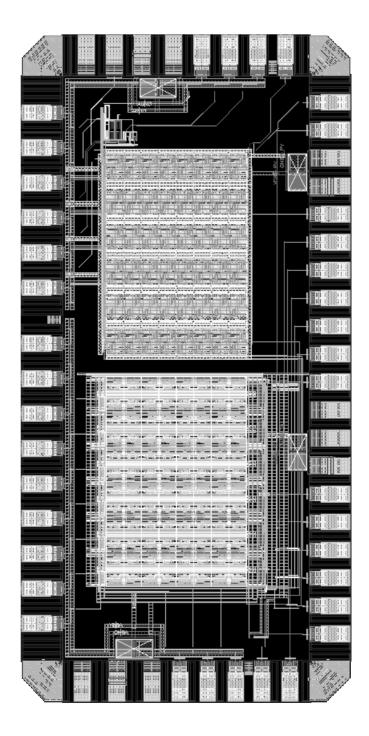

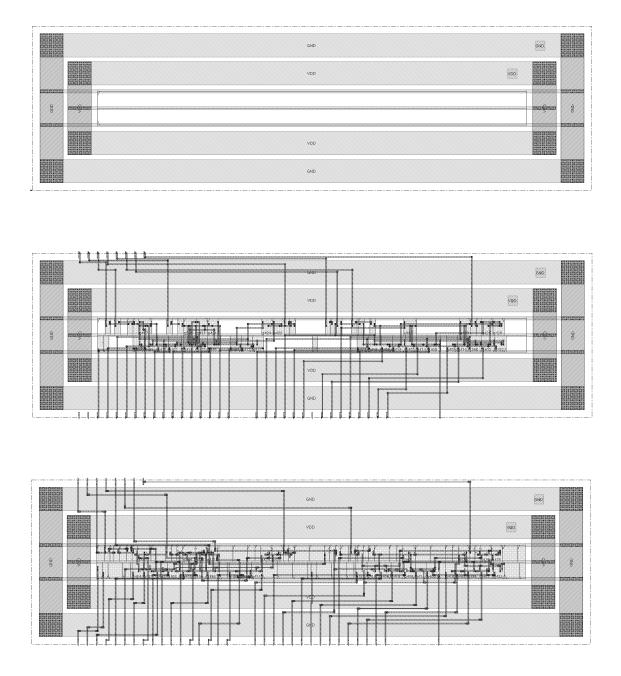

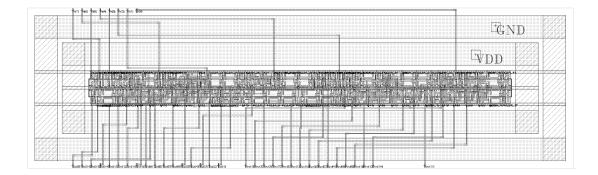

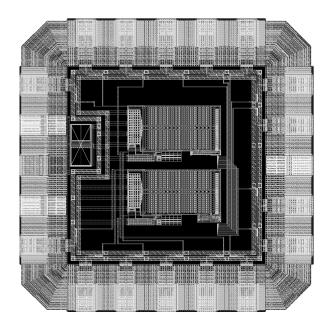

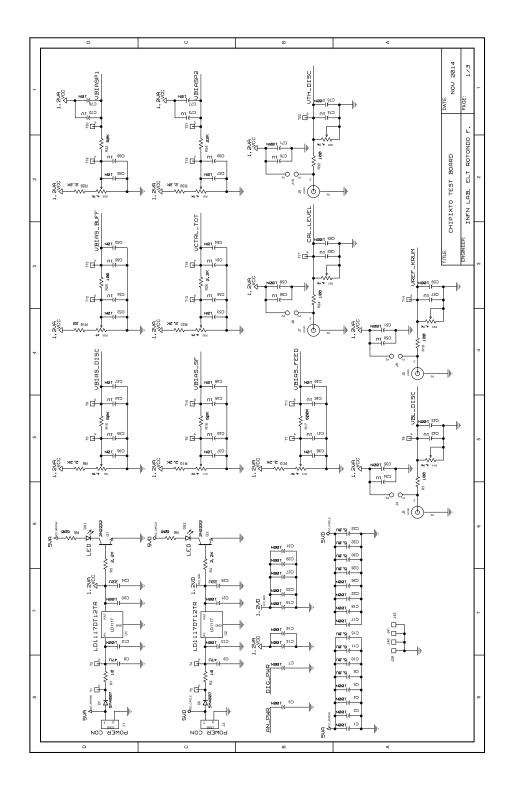

A complete view of a PSI46V2 chip layout is presented in Figure 1.10. Most important ASIC specifications are summarized in Table 1.4. The overall dimensions are 7.8 mm × 9.8 mm. The chip consists of a 7.8 mm × 8 mm core pixel matrix and a 7.8 mm × 1.8 mm chip periphery. The core active area contains 52 columns × 80 rows of 100  $\mu$ m × 150  $\mu$ m pixel cells bump-bonded to a sensor. As usually performed in most of pixel ASICs, two adjacent columns form a double-column in order to share power distribution, bias, data buses and common services.

As already discussed, a pixel ASIC operating at the LHC has to provide on-chip temporary data storage (buffering) and time-stamping capabilities in order to transfer off-detector only zerosuppressed (triggered) data. On the one hand, each pixel cell has to process and register the signals produced by particles in the sensor. On the other hand, the bunch crossing information, the pixel address and the amount of collected charge of all channels must be stored during the whole L1 trigger latency, sending out data only for those bunch crossings for which an L1A has been distributed to sub-detectors. Hit information generated in each single pixel unit cell (PUC) are therefore sent to the chip periphery where are temporary stored on buffers while waiting for a first level trigger decision. In particular, the PSI46V2 employs a full-analogue readout of the charge information of each pixel. As discussed shortly thereafter, charge information is retrieved in analogue form using a sample-and-hold (S/H) circuit placed in each pixel cell, transferred to analogue buffers in the chip periphery and buffered until the L1 trigger decision is taken. The actual off-chip data readout is performed in analogue form as well, using 40 MHz serial analogue links. A digitization of the charge information is performed only in counting rooms using VME modules equipped with 10-bit A/D converters. One remarkable aspect is the totally absence of synthesized logic in the pixel ASIC. All digital components have been implemented as full-custom solutions without the support of any automated synthesis and place-and-route engines.

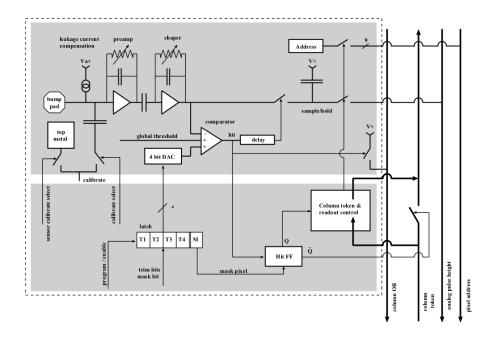

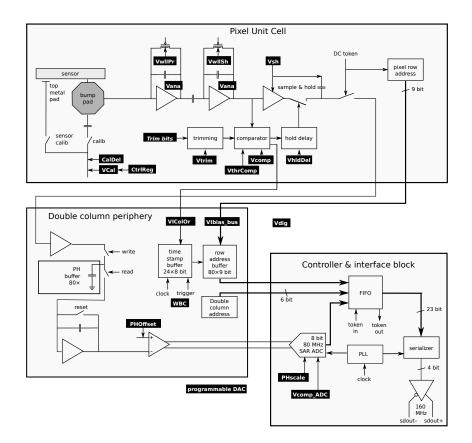

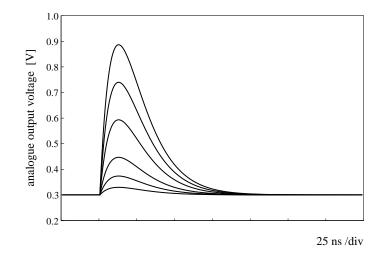

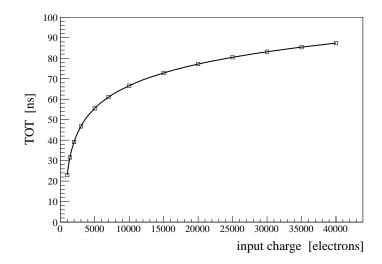

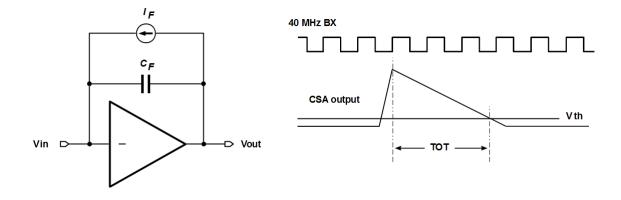

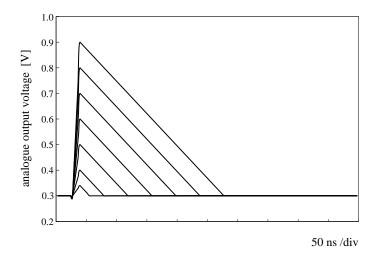

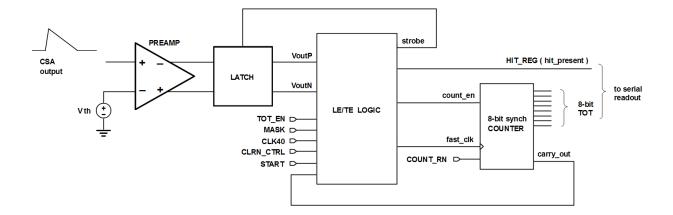

A schematic block diagram of a pixel unit cell is presented in Figure 1.11, completed by a layout view in Figure 1.12. Each pixel cell is partitioned into an analogue part and a digital part. The signal originated in a pixel sensor is transferred through the bump-bonding and enters a two-stage analogue Front-End system composed of a charge sensitive amplifier (CSA) and a shaper. Alternatively, test charge calibration signals can be injected through a selectable 4.8 fF injection capacitor directly connected to the CSA input node. The overall analogue Front-End chain has been optimized for a sensor capacitance of 80-100 fF.

$<sup>^7~</sup>$  Almost all full-custom electronic systems currently installed at LHC experiments have been implemented using such a 0.25  $\mu \rm m$  CMOS technology radiation-hardened by design using special layout techniques.

Figure 1.10: Full size layout view of a PSI46V2 readout chip (ROC) currently employed in the CMS silicon pixel tracker [Gabathuler 2005]. The active matrix of  $52 \times 80$  pixels has a size of 8 mm  $\times$  7.8 mm. Pixel columns are grouped into 26 double-columns. The chip periphery has a length of 1.8 mm and hosts analogue buffers, time-stamp buffers, I/O interfaces, control D/A converters and voltage regulators.

| Parameter                | Specification/value                           |

|--------------------------|-----------------------------------------------|

| pixel size               | $100 \ \mu m \times 150 \ \mu m$              |

| chip size                | $7.9 \text{ mm} \times 9.8 \text{ mm}$        |

| fabrication technology   | CMOS 0.25 $\mu$ m (RHBD)                      |

| number of pixels         | $52 \text{ columns} \times 80 \text{ rows}$   |

| readout                  | full-analogue                                 |

| nominal charge threshold | $3 \text{ k}e^{-1}$                           |

| readout speed            | 40 MHz                                        |

| supply voltages          | $1.5~\mathrm{V}$ (A) and $2.5~\mathrm{V}$ (D) |

| power consumption        | $\approx 30 \ \mu W/pixel$                    |

Table 1.4: PSI46V2 ASIC specifications summary table.

Figure 1.11: Schematic block diagram of a pixel unit cell (PUC) in the current CMS pixel readout chip PSI46V2 [Kastli 2006].

Figure 1.12: PSI46V2 pixel unit cell layout, 150  $\mu\mathrm{m}$   $\times$  100  $\mu\mathrm{m}.$

AC coupling is performed between CSA and shaper stages. It removes DC offsets caused by the sensor leakage current and it is part of the closed-loop gain of the shaping stage. The gain is given by the ratio between the coupling-capacitance and the feedback-capacitance. The nominal operating point of both amplifiers sits in the middle between the power and ground rails and it is independent of voltage drops across the chip because the analogue power rails have been kept symmetric and well separate from other power rails. This minimizes systematic variations of thresholds and feedback transistors. Passive feedback resistors are implemented with PMOS transistors working in linear region. Furthermore, both gate and substrate potential have been made adjustable in order to control the resistance of the feedback resistors. A programmable current source compensates the sensor leakage current, nominally 10 nA per pixel.

The shaper output is fed to a continuous-time voltage comparator. A global threshold is distributed to all pixels, generated at the chip periphery by a D/A converter. In order to compensate for channel-to-channel threshold variations, each pixel cell includes a local 4-bit D/A converter to trim the threshold. The overall threshold dispersion before correction is approximately 300  $e^-$  RMS, reduced to 80  $e^-$  after trimming. Furthermore, a mask bit allows to disable noisy pixels. Due to high energy particle irradiation, information stored in the chip can be corrupted by Single Event Upset (SEU) effects. In order to protect trim and mask storage cells, a capacitor is inserted in parallel to the classical cross-coupled inverters structure extensively adopted to achieve memory in CMOS digital circuits. At nominal LHC luminosity the SEU rate has been estimated to be less that  $3 \times 10^{-2}$  Hz. The occupancy of each pixel is monitored online and pixels that show significant changes with respect to calibrations are reprogrammed.

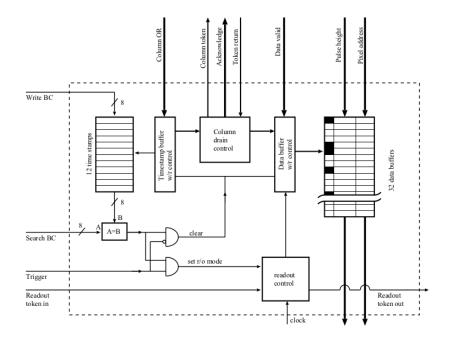

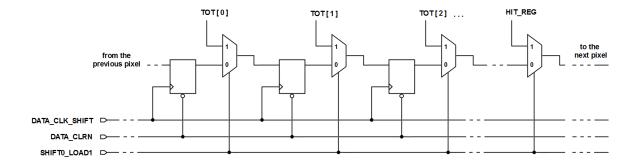

If the analogue pulse is above the threshold, the shaper output signal is sampled onto a capacitor and the pulse amplitude is stored for later readout. Charge information is therefore retrieved in fullanalogue form. At the same time, a digital signal is sent to the chip periphery via an asynchronous column fast-OR bus to inform the chip periphery of the presence of a hit information. The pixel becomes insensitive and waits to be read out. No clock or bunch crossing time-stamp is distributed over the pixel array, resulting into a bare minimum digital switching activity in the core pixel array. The chip periphery synchronizes the wired-OR with the LHC machine clock and latches the current bunch crossing number in a time-stamp buffer whenever a hit is found. The state of the pixels that have a hit at that time is frozen and their data is subsequently collected. A token passing from pixel to pixel controls the data transfer. When a token arrives to the pixel cell, the pulse amplitude previously stored on the sampling capacitor is sent to the periphery together with the pixel address, where they are associated to the bunch crossing and stored in a second buffer. The token flag is then passed on and the pixel resumes data taking. All 26 double-columns are readout in parallel. Pixels in the same double column are read clockwise from the bottom left to the bottom right position. The time necessary to drain a double column depends on the number of hit pixels. Finally, a double-column logic at the chip periphery controls the data transfer, stores the hit information in analogue buffers for the whole trigger latency and performs the trigger verification. A schematic block diagram of the logic is presented in Figure 1.13. The trigger matching is performed as follows. The data buffer consists of 32-units, each made of a marker bit to indicate the beginning of a new event and to synchronize data and time-stamp, one analogue storage cell and 9 digital storage cells for the pulse height and the pixel address respectively. The oldest entry in the time-stamp buffer is continuously compared to the an 8-bit counter delayed with respect to the bunch crossing by a programmable amount of time corresponding to the trigger latency (Search Bunch Crossing counter, SBC). Time-stamp numbers and analogue data can be stored in the corresponding buffers for a maximum trigger latency of 3.2  $\mu$ s, corresponding to 128 bunch crossing at 40 MHz bunch interaction rate. In case of agreement, the trigger is checked. If an L1A is present, the system enters in readout mode and the double column stops data acquisition to prevent overwriting of ready data. Otherwise, time-stamps and data buffers are cleared.

Figure 1.13: Schematic view of a double-column periphery logic [Kastly 2006].

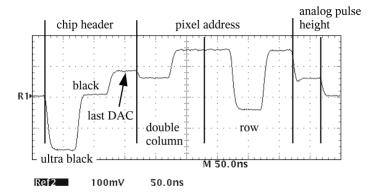

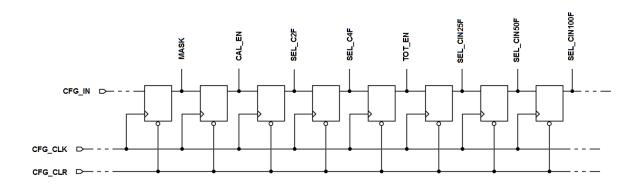

Figure 1.14: Full-analogue readout sequence of a ROC with one pixel hit [Kastly 2006]. Both the pixel address and the charge information are DC analogue levels.

Data losses can occur when one of the buffers is completely filled up. In case of a full data buffer the double-column gets reset. If the time-stamp buffer is full instead, data acquisition is paused until the next buffer cell is freed. Most of the chip periphery area is therefore occupied by double-columns buffers. As discussed later in Section 1.7, the number of buffers in the chip periphery currently represents the main limitation of the PSI46V2 chip in perspective of a first LHC luminosity increase foreseen before 2020. An improved version of the ASIC has been already implemented in order to sustain a luminosity twice the nominal value, up to  $2 \times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>. The chip periphery also hosts necessary slow controls and supply blocks such as such bandgap references and voltage regulators. The chip requires two external supply voltages, 1.5 V for the analogue sections and 2.5 V for the digital parts. The total power consumption is 120 mW per chip, corresponding to about 29  $\mu$ W per pixel and a total power density of the order of 250 mW/cm<sup>2</sup>. As discussed later in the chapter, this parameter will become a severe constraint for any future pixel ASIC design. Voltage regulators are programmable, hence the voltages can be set for each chip separately. The overall chip configuration uses a serial programming interface, based on a modified I<sup>2</sup>C protocol running at 40 MHz. More than 30 D/A converters are used to configure and calibrate the chip, resulting into a very flexible system.

Zero-suppressed data are sent off-chip using a full-analogue serial readout running at 40 MHz (alternatively, it can be switched to 20 MHz) through optical links that connects a group of pixel chips to the remote electronics placed in counting rooms. Since the readout uses only analogue differential signals, the pixel address in digital form is encoded into 6 analogue discrete levels by means of D/A converters. Pixel address and signal pulse height can be transferred in 6 clock cycles. As already mentioned, digitization of pixel information is performed only in counting room.

A sample readout sequence for a single pixel hit is shown in Figure 1.14. The readout sequence starts with a header of three clock cycles. A large negative signal level well outside of the range of pixel data (ultra-black) followed by a zero differential level (black) indicates the begin of the data stream. In the third clock cycle of the chip header a DC level inversely proportional to the value of the to the most recently programmed DAC (last-DAC) is sent. Header information is followed by the double-column address (2 clock cycles), the row address (3 clock cycles) and the analogue pulse height for each hit pixel.

Barrel layers and the endcap disks of the CMS pixel tracker are composed of pixel detector modules. Each module contains a variable number of PSI46V2 readout chips bump-bonded to a common silicon sensors (8 or 16 in the barrel, 22 or 23 in the endcap disks). The overall CMS silicon pixel tracker consists of about 66 million pixels and 1400 detector modules.

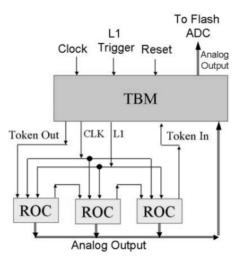

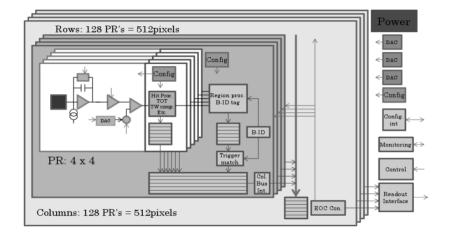

The serial readout of triggered data for a group of PSI46V2 chips part of the same module is controlled by an auxiliary custom-designed ASIC implemented in the same radiation-hardened by design 0.25  $\mu$ m CMOS technology, the Token Bit Manager (TBM) [Bartz 2005]. As depicted in Figure 1.15, a readout token is passed from chip to chip, connecting each of them to the analogue readout bus. The TBM is also responsible for the formatting of the serial data stream. Furthermore, it distributes L1 triggers and 40 MHz clocks to each ROC in the module. An arbitrary number of PSI46V2 chips can be chained and sequentially read out in a single token scan.

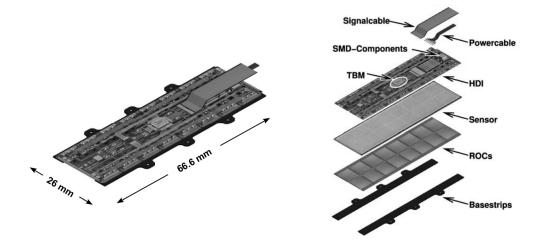

The basic structure of pixel module in the innermost barrel layes is shown in Figure 1.16. The overall dimensions are 26 mm  $(r\phi) \times 66.6$  mm (z). Two basestrips made of 250  $\mu$ m thick silicon nitride provide the mechanical support for the entire module. The pixelated sensitive layer has a total active area of 64 mm  $\times$  16 mm, with silicon sensor of 280  $\mu$ m thickness. As mentioned, 16 or 8 PSI46V2 readout chips are bump-bonded to the sensor. On the opposite side of the module there is a flexible and low mass 3-layers printed circuit board, the High Density Interconnect (HDI), which distributes signals and power to the electronics. At the centre of the HDI is placed the TBM chip. The nominal power dissipation is 2 W/module.

Figure 1.15: Schematic block diagram of a readout chain consisting of a TBM chip and a group of pixel ROCs [Bartz 2005].

Figure 1.16: Perspective view of a CMS barrel pixel module. Each module contains 16 or 8 PSI46V2 readout chips bump-bonded to 280  $\mu$ m thick silicon sensors with 100  $\mu$ m × 150  $\mu$ m pixel size. On the opposite side a flexible HDI hosts the TBM chip that controls the full-analogue serial readout of the ROCs. All signals are transferred using an impedance matched Kapton/copper cable.

#### **1.6** LHC operations in 2009-2014 and upgrade scenarios

The LHC machine has been designed to reach nominal 14 TeV centre-of-mass energy and luminosity  $10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> at 40 MHz bunch crossing rate. Indeed, given the unprecedented complexity of such a giant machine, nominal values have not yet been reached. After the preliminary commissioning phase, LHC operations continuously evolved in time in terms of bunch crossing rate, beam energy and delivered instantaneous luminosity. Furthermore, several upgrade scenarios and technical plans have been investigated since the initial concept of the accelerator, following the expected evolution of machine performance and involving both short-term and long-term improvements and upgrades in the forthcoming 10-15 years.

The first LHC physics program, referred to as *Run* 1, includes collisions delivered between first operations in November 2009 up to a first 2-years long shutdown (LS1) started on February 2013. The original schedule of the accelerator was delayed by about one year due to an accident on September 2008 just a few days after the first proton beams were circulated in the main ring. Most likely the cause of the problem was a faulty electrical connection between two magnets, causing a loss of approximately 6 tonnes of liquid helium, which was vented into the LHC tunnel. Vacuum conditions in the beam pipe were lost and a total of 53 superconducting magnets were damaged. Most of 2009 was therefore spent to repair the LHC machine and reviewing the damage caused by the quench incident. Only on November 2009 first proton-proton collisions at limited 450 GeV centre-of-mass energy were delivered to experiments. The energy was then gradually increased up to the unprecedented value of 1.18 TeV/beam, beating the previous record of 0.98 TeV/beam held by the Tevatron machine at Fermilab, US.

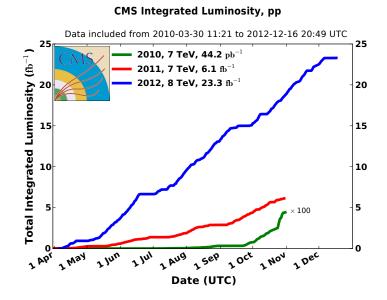

After necessary commissioning, at the end of March 2010 two proton beams in the LHC collided at the unprecedented centre-of-mass energy of 7 TeV, marking the begin of the effective LHC physics research program. The LHC has been operated through the rest of 2010 at the same beam energy of 3.5 TeV/beam and 150 ns bunch spacing time. The instantaneous luminosity was increased either by increasing the current intensity of the beam or increasing the number of bunches per beam, targeting to reach  $10^{32}$  cm<sup>-2</sup> s<sup>-1</sup> before the end of 2010. In such a first low luminosity phase the LHC experiments started their physics programs by measuring large cross section processes, confirming the Standard Model with a large number of recorded events despite the low luminosity. The early LHC physics represented a fundamental benchmark for LHC experiments, validating overall detectors performance and allowing a fine tuning of reconstruction algorithms and necessary calibration constants with real data. The first proton run officially ended on November 2010, reaching a total integrated luminosity of about 47 pb<sup>-1</sup>. The first run with lead ions started on 8 November 2010 and ended on 6 December 2010.

At the end of the heavy ions run, the LHC was shutdown for a 3-months technical maintenance and restarted on March 2011. Another milestone was reached on April 2011, when the LHC delivered an unprecedented peak luminosity of  $4.67 \times 10^{32}$  cm<sup>-2</sup> s<sup>-1</sup> beating once again the Tevatron record of  $4 \times 10^{32}$  cm<sup>-2</sup> s<sup>-1</sup>. With a further luminosity increase up to  $\approx 3 \times 10^{33}$  cm<sup>-2</sup> s<sup>-1</sup> ATLAS and CMS experiments reached 5 fb<sup>-1</sup> of collected data in October 2011, reporting first hints of a signal in the search for a SM Higgs boson. With the real possibility of a discovery before the foreseen first 2-years long shutdown in 2013-2014, it was decided to increase the beam energy up to 4 TeV/beam, slightly changing the schedule of the LHC. On April 2012, the first collisions were delivered at the new unprecedented centre-of-mass energy of 8 TeV. On July 4th 2012 ATLAS and CMS collaborations announced the discovery of new particle with mass  $\approx 125$  GeV/c<sup>2</sup> consistent with a Higgs boson. Without doubts, such a discovery represents the major achievement of the first LHC physics run. A further 11 fb<sup>-1</sup> integrated luminosity has been delivered through summer 2012, with instantaneous peak luminosities approaching  $7 \times 10^{33}$  cm<sup>-2</sup> s<sup>-1</sup>.

| Parameter                                            | 2010                 | 2011                  | 2012                 | design value          |

|------------------------------------------------------|----------------------|-----------------------|----------------------|-----------------------|

| beam energy [TeV]                                    | 3.5                  | 3.5                   | 4                    | 7                     |

| bunch spacing [ns]                                   | 150                  | 75-50                 | 50                   | 25                    |

| peak luminosity $[\mathrm{cm}^{-2} \mathrm{s}^{-1}]$ | $2.1 \times 10^{32}$ | $3.7 \times 10^{33}$  | $7.7 \times 10^{33}$ | $1 \times 10^{34}$    |

| number of bunches                                    | 368                  | 1380                  | 1380                 | 2808                  |

| number of protons/bunch                              | $1.2 \times 10^{11}$ | $1.45 \times 10^{11}$ | $1.7 \times 10^{11}$ | $1.15 \times 10^{11}$ |

| maximum pileup                                       | 4                    | 17                    | 37                   | 20                    |

Table 1.5: Summary table for most important performance parameters during LHC operations in 2010-2013 and comparison with nominal design values. LHC machine performance public results.

Figure 1.17: Integrated luminosity versus day delivered to the CMS experiment during stable beams and proton-proton collisions in 2010-2011-2012. CMS public results.

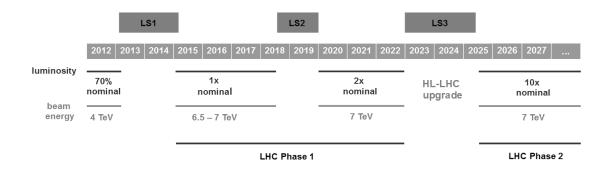

Figure 1.18: Foreseen evolution of LHC performance in terms of beam energy and luminosity through 2020 and beyond.

Electron cloud effects in the beam pipe have been identified as a major performance limitation for the LHC when operating at nominal 40 MHz bunch crossing rate, introducing complex issues related to beams instability [Rumolo 2011, Iadarola 2014]. Proton-proton collisions delivered to experiments for data taking during 2011 used bunch trains with either 75 ns or 50 ns bunch spacing, whereas a bunch spacing of 50 ns has been adopted through 2012. Only in dedicated special runs at the end of 2012 LHC operated at nominal 25 ns. Most important performance parameters for LHC operations during 2010-2013 and a comparison with nominal design values are summarized in Table 1.5. The total integrated luminosity versus day delivered to the CMS experiment during stable beams and proton-proton collisions in 2010-2012 is presented in Figure 1.17. By the end of the 2012 both ATLAS and CMS collaborations collected more than 20 fb<sup>-1</sup>.

All machine and data taking activities have terminated on February 2013, successfully concluding the so called *Phase-*0 of the LHC schedule. After more than 3 years of operations, a massive program of technical maintenance for LHC magnets and its injector chain has been accomplished in the first 2-years long shutdown (LS1) in 2013-2014, targeting after restart to reach nominal luminosity  $10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> and 14 TeV centre-of-mass energy in proton-proton collisions without the need of major hardware modifications. In the same period, LHC experiments gained from machine inactivity for necessary consolidation, maintenance, technical repairs and improvements. With the end of LS1, the LHC is entering in its *Phase-*1 schedule. At the time of writing, the machine has just restarted, circulating first particle beams at low energy. After commissioning, particle collisions at new unprecedented beam energy of 6.5 TeV/beam are expected on June 2015, marking the begin of *Run* 2. Despite the plan is to operate with a nominal 25 ns bunch spacing, further operations at 50 ns cannot be ruled out at this time.

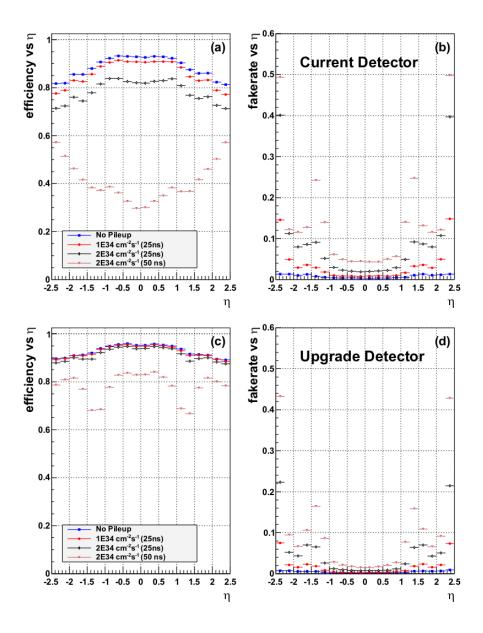

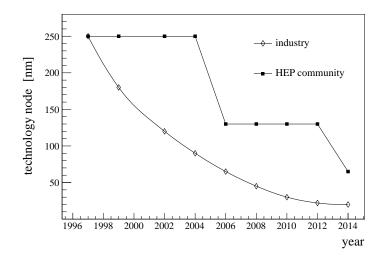

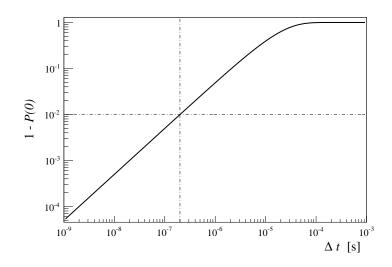

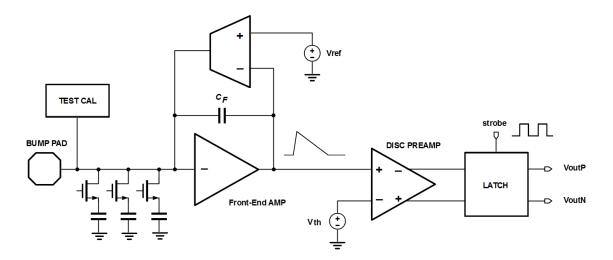

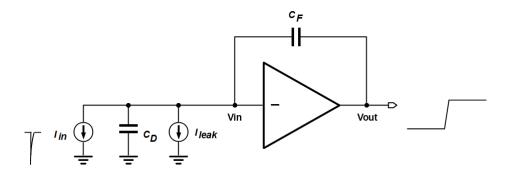

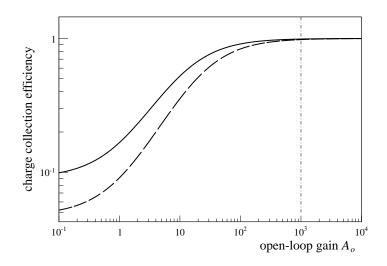

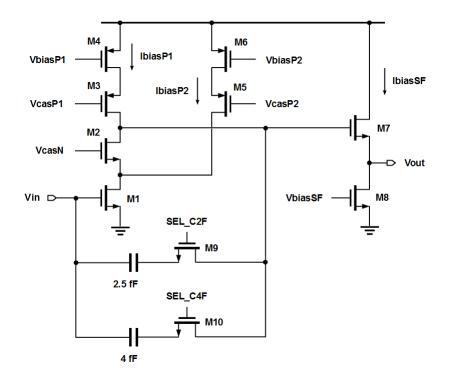

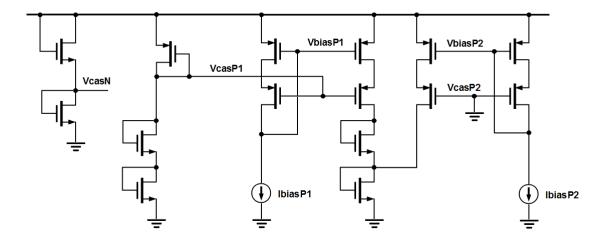

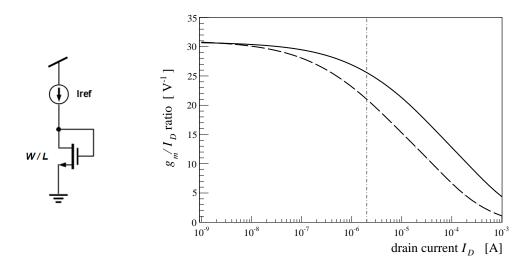

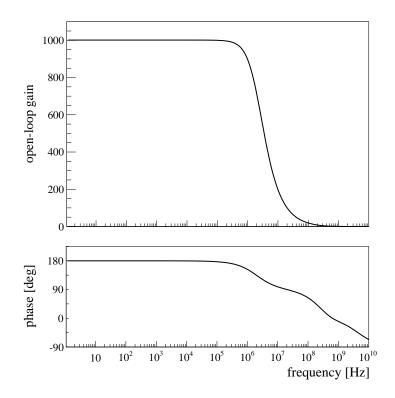

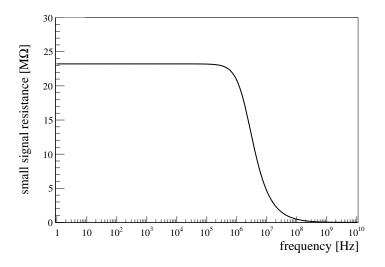

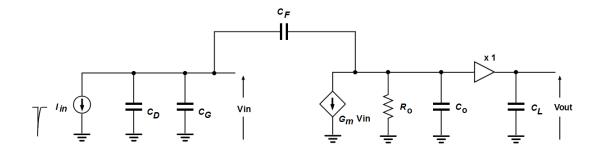

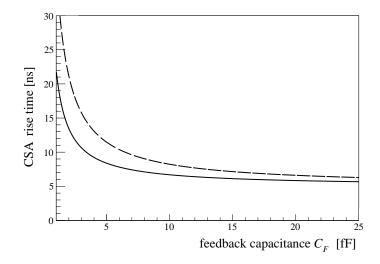

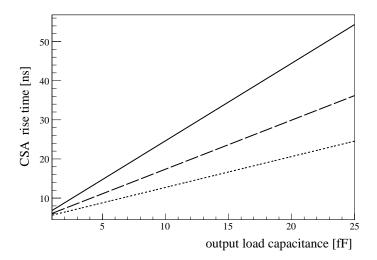

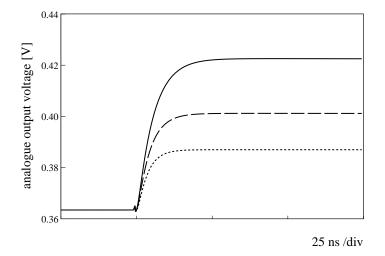

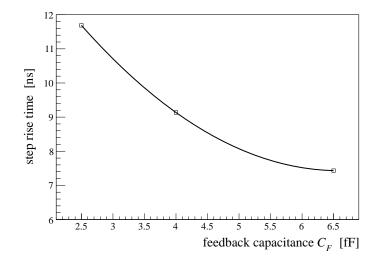

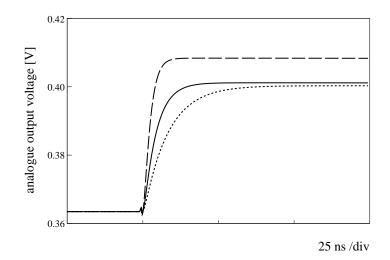

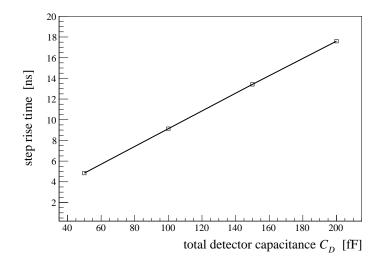

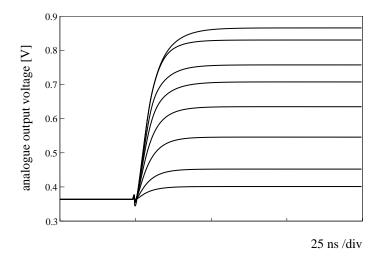

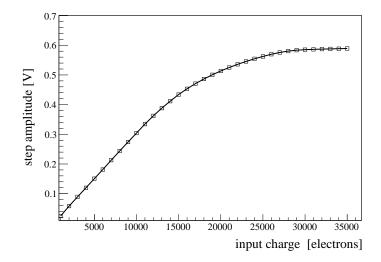

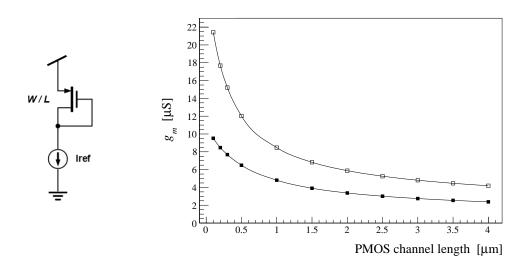

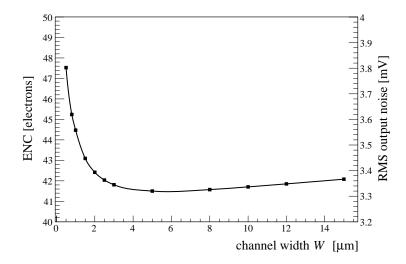

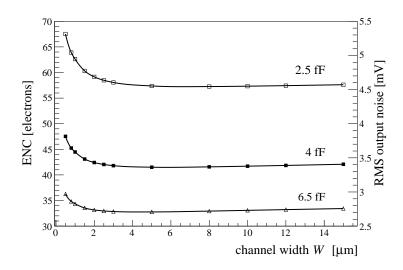

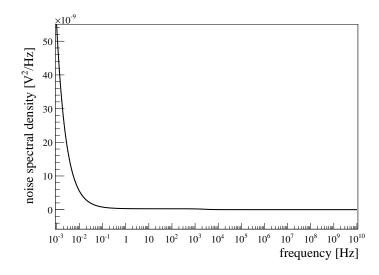

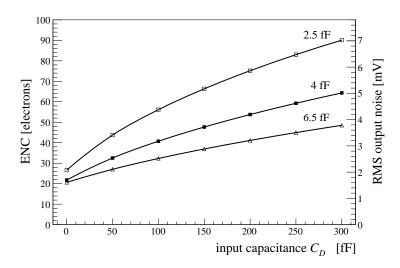

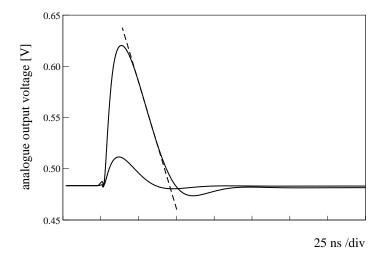

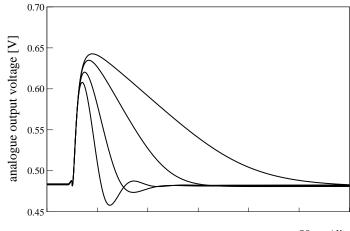

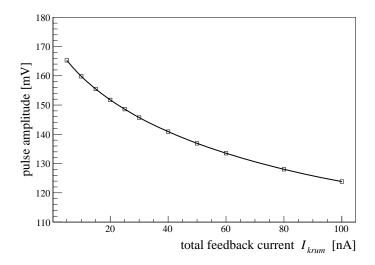

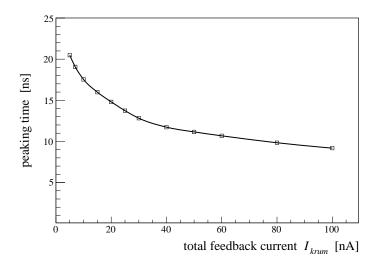

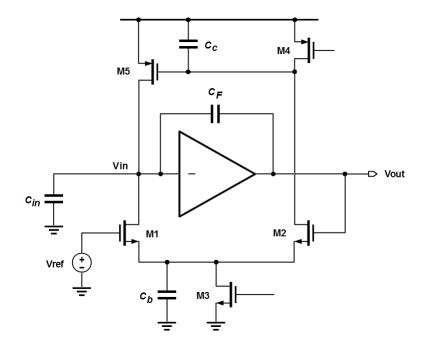

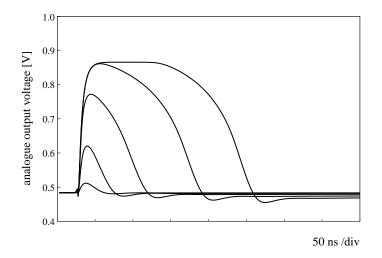

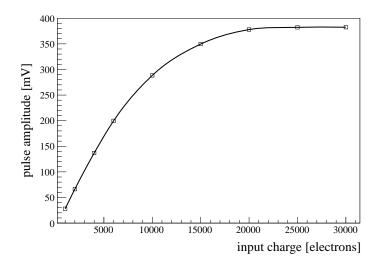

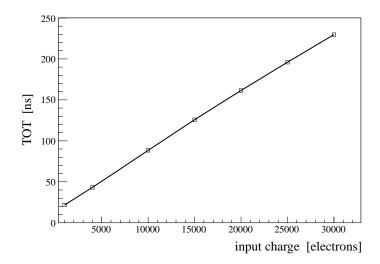

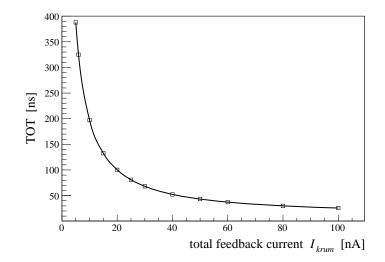

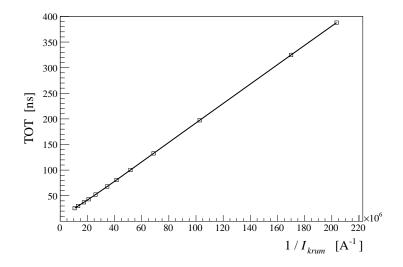

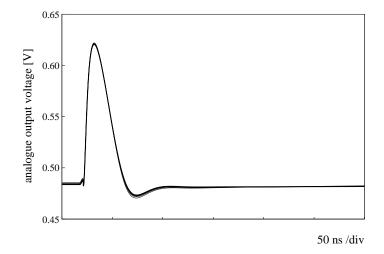

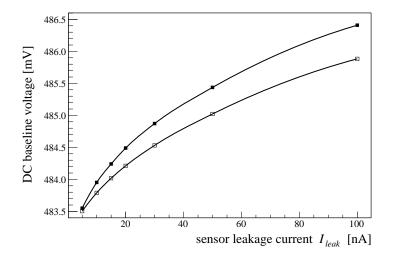

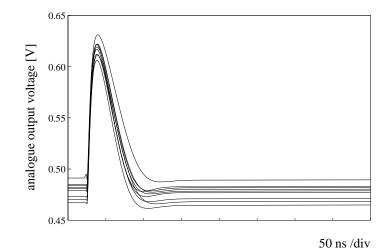

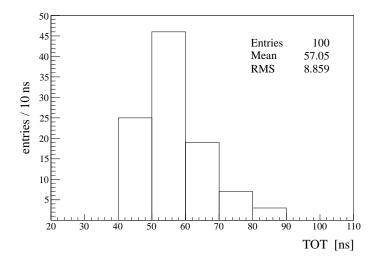

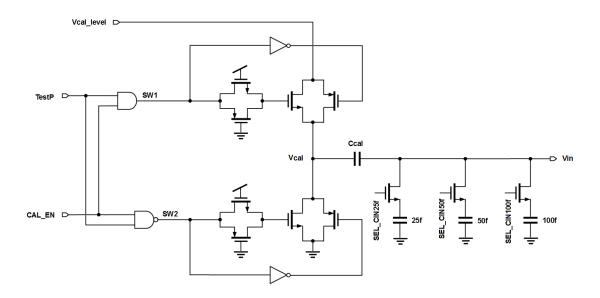

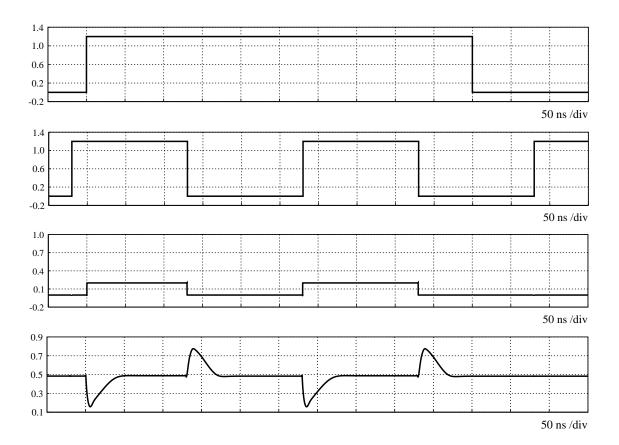

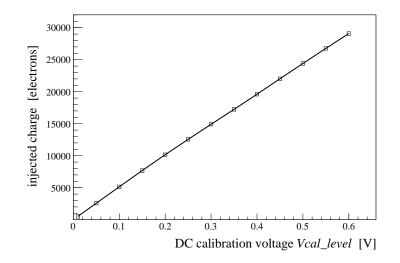

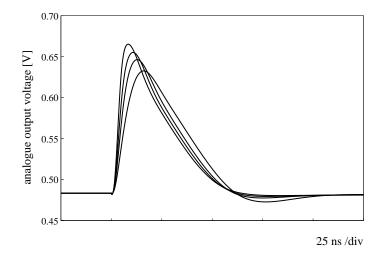

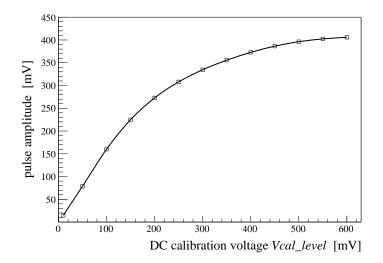

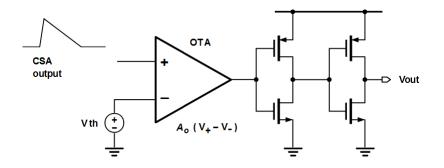

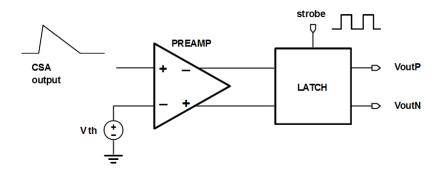

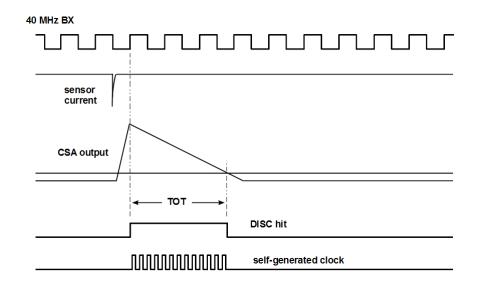

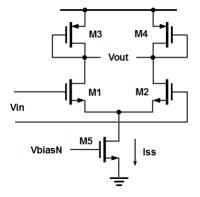

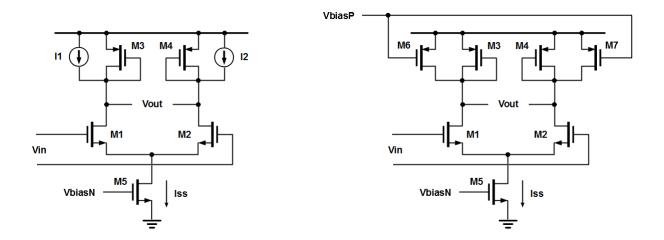

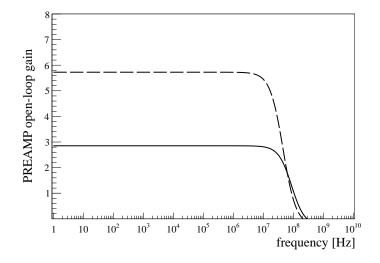

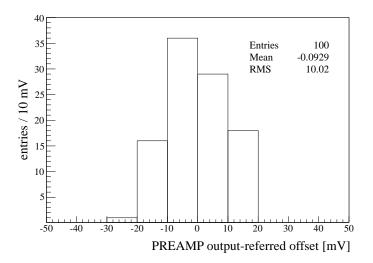

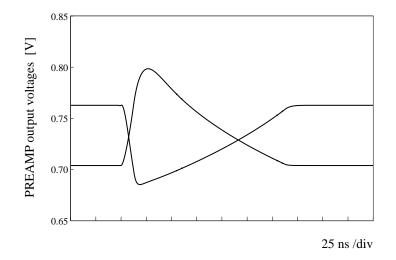

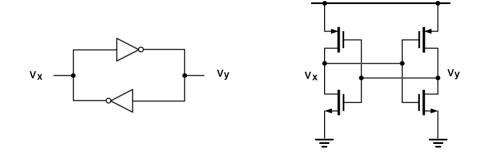

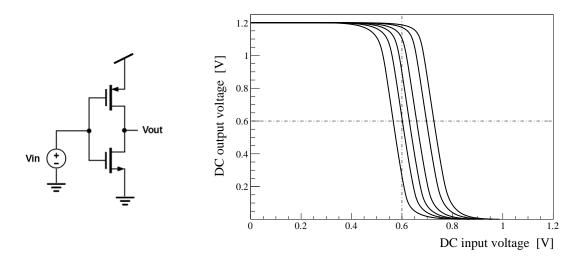

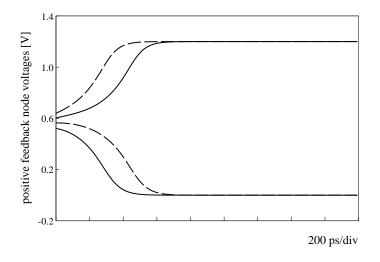

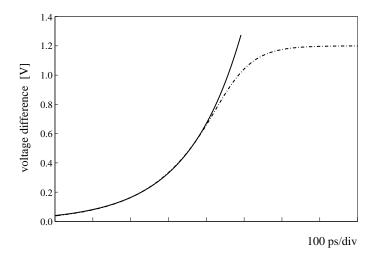

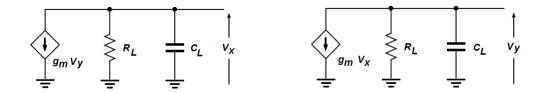

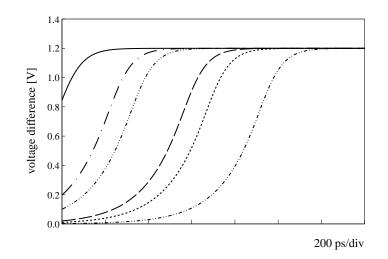

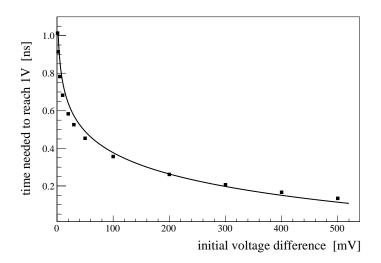

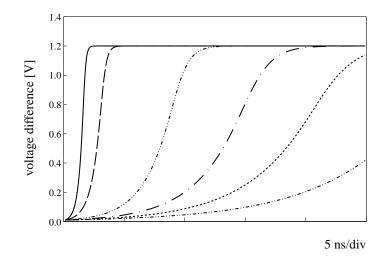

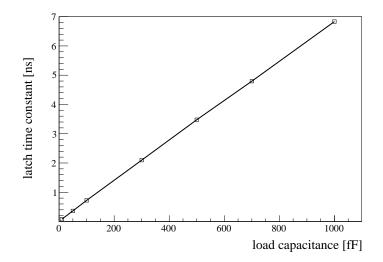

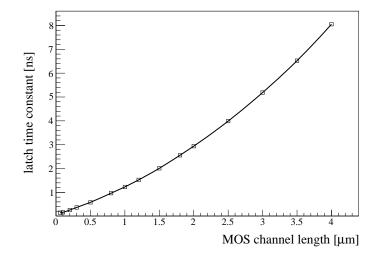

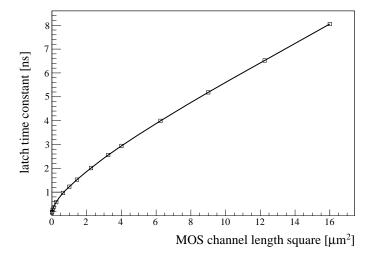

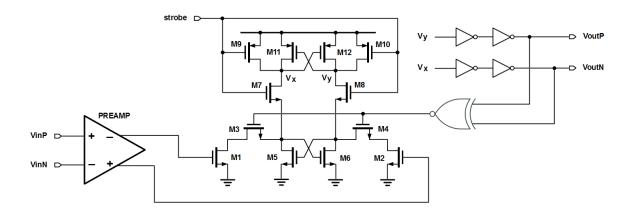

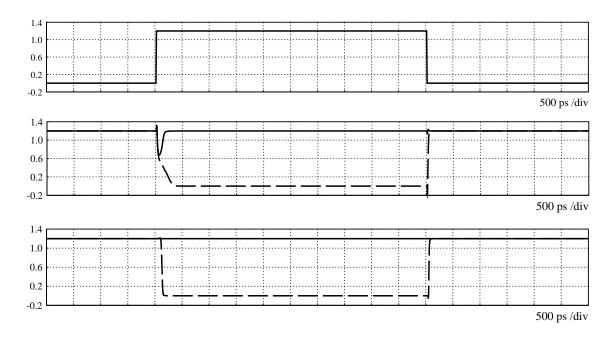

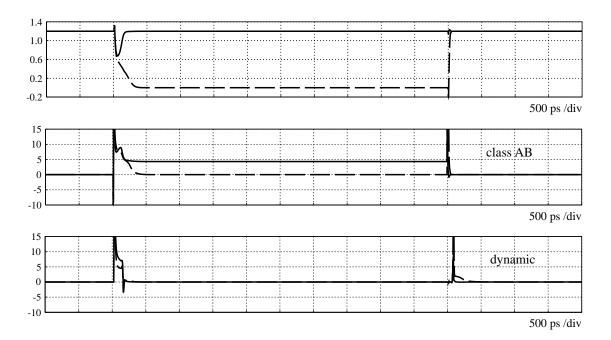

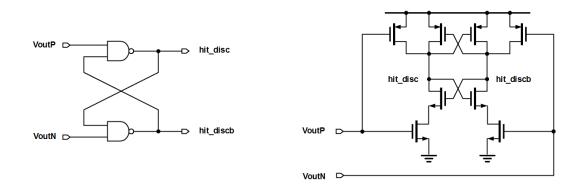

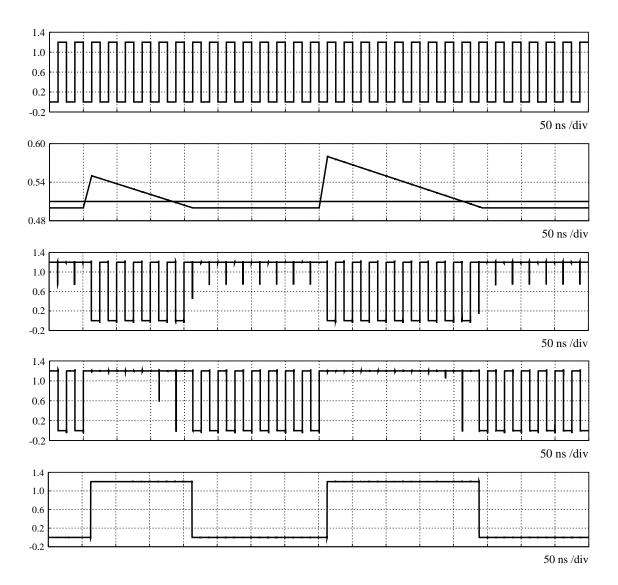

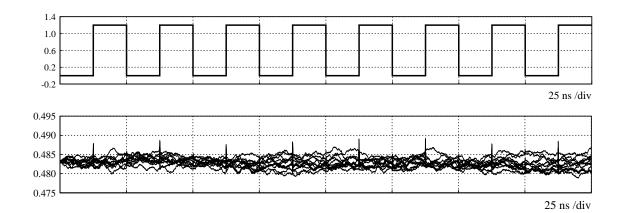

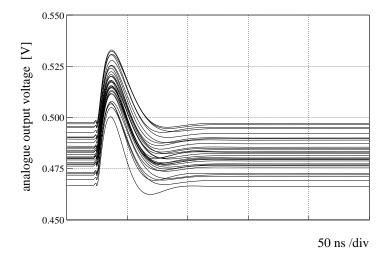

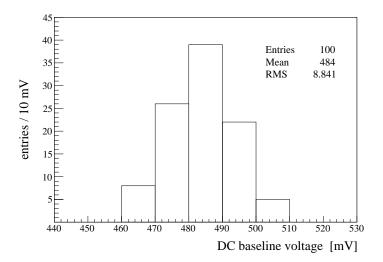

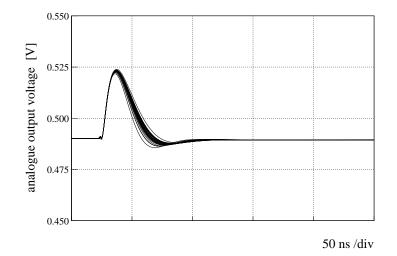

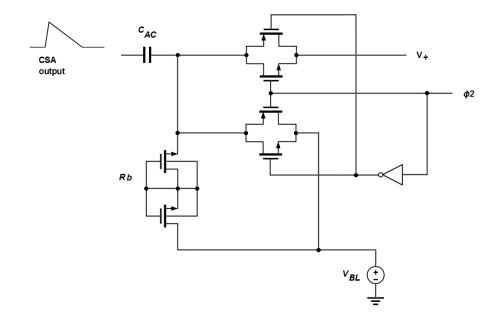

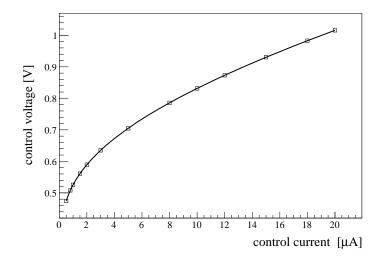

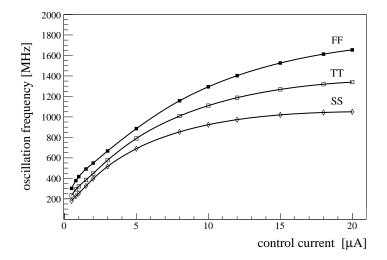

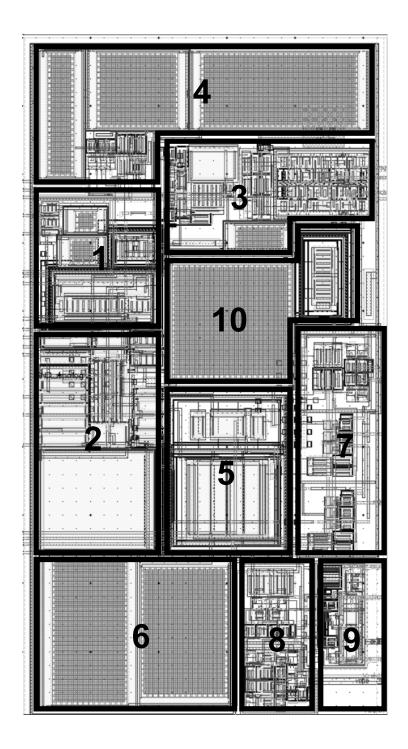

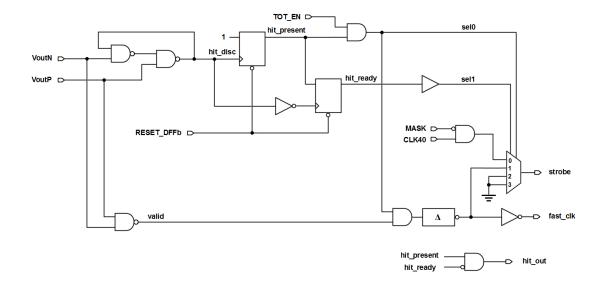

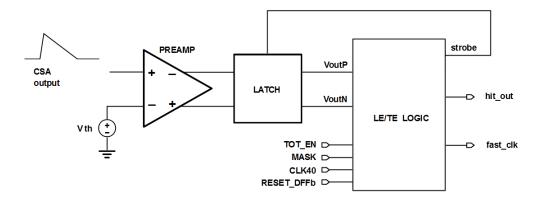

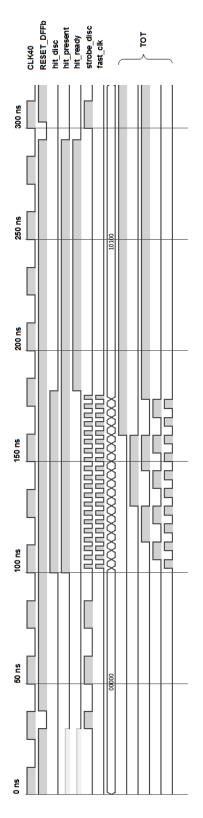

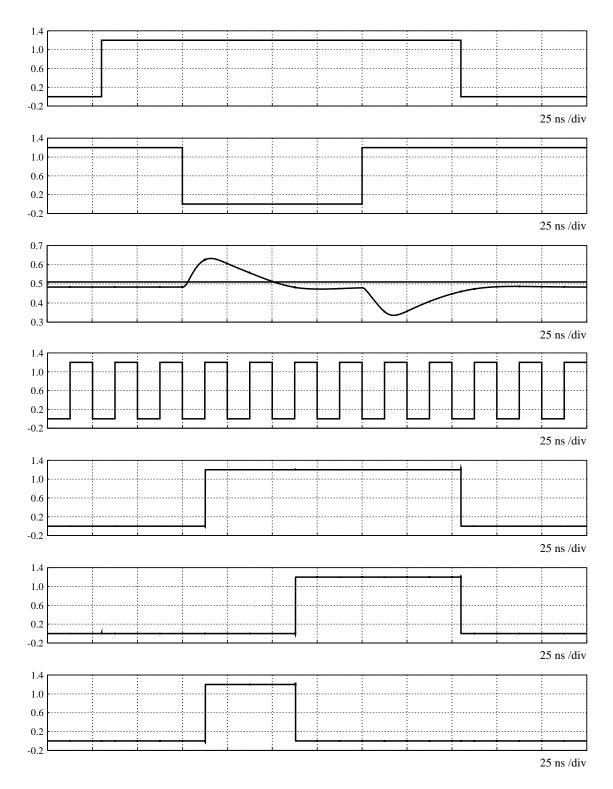

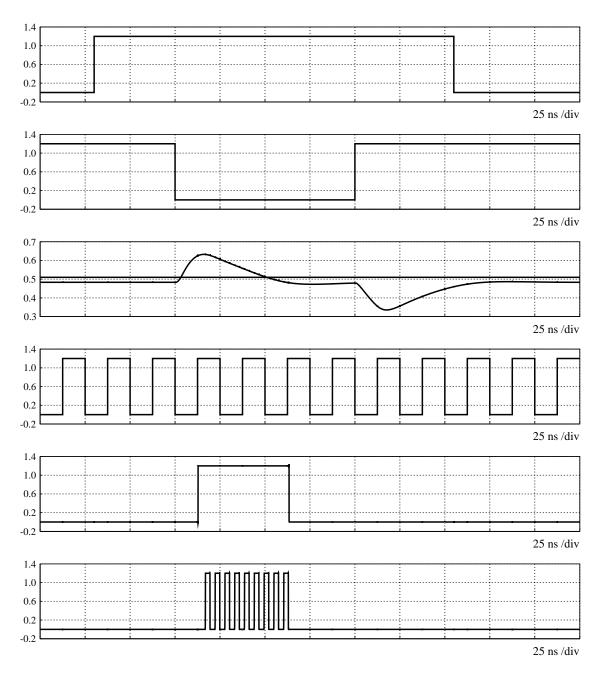

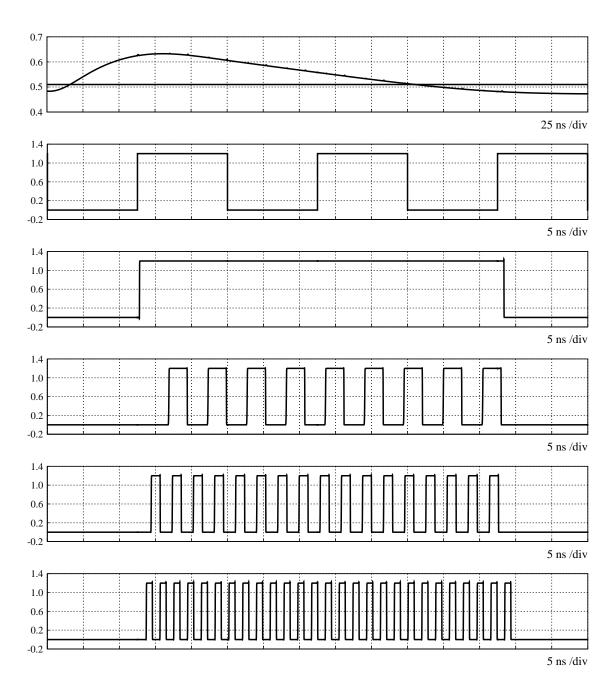

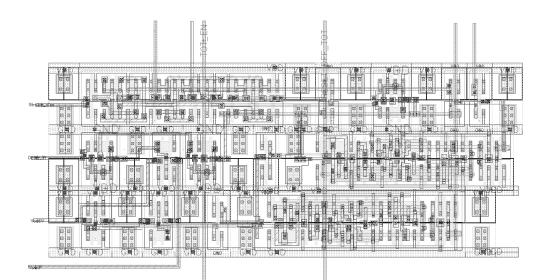

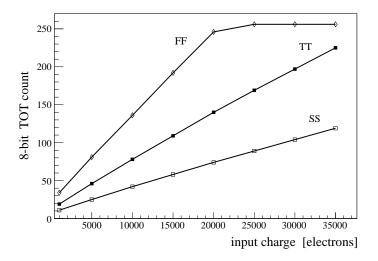

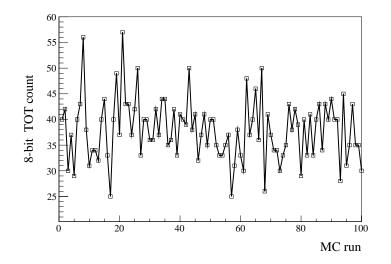

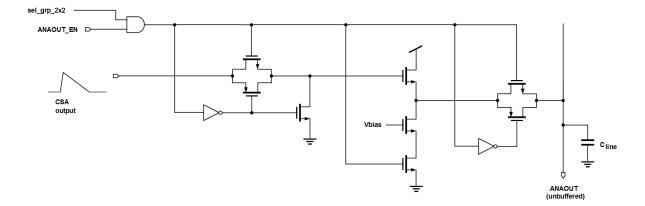

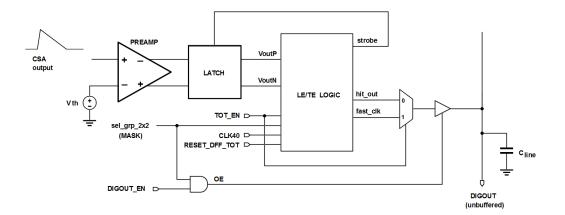

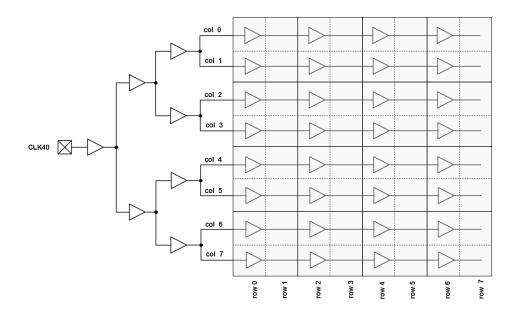

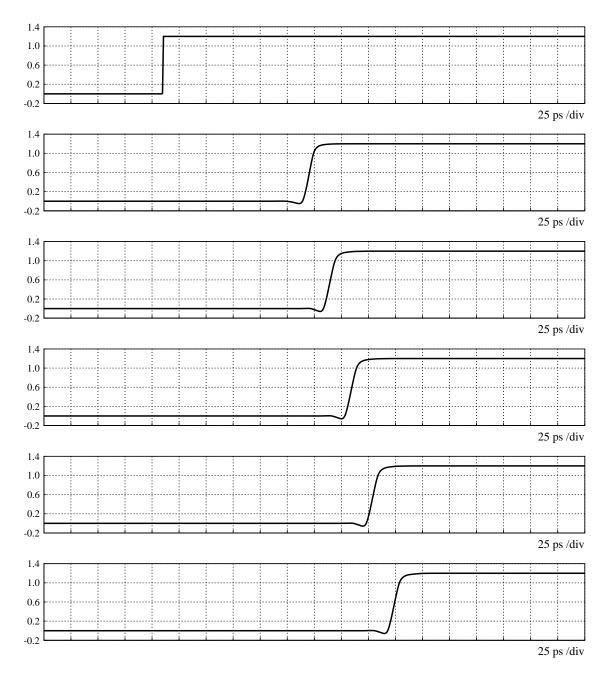

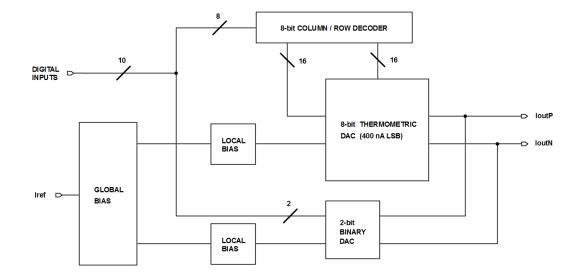

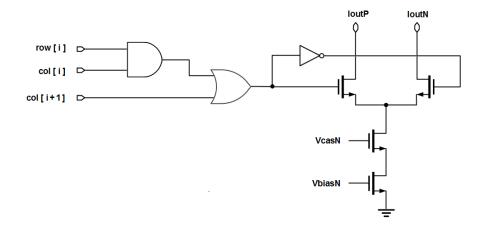

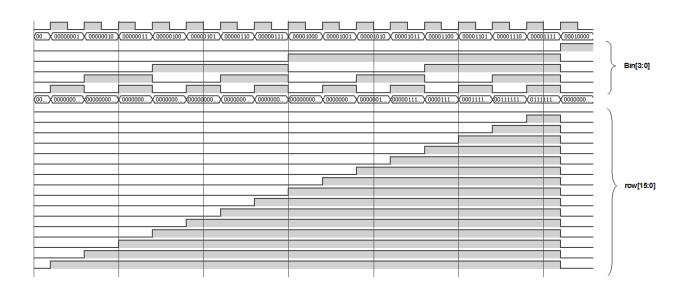

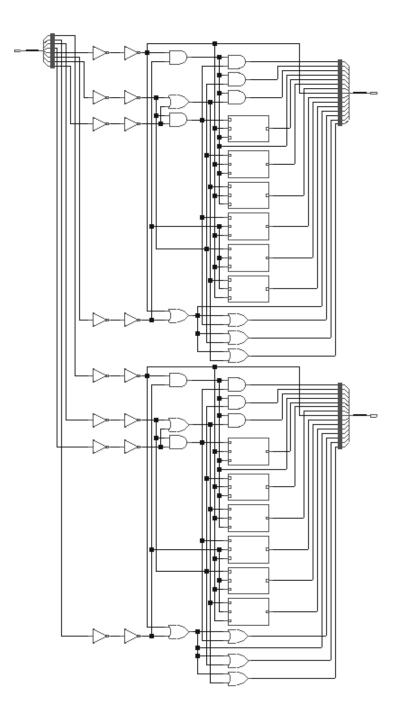

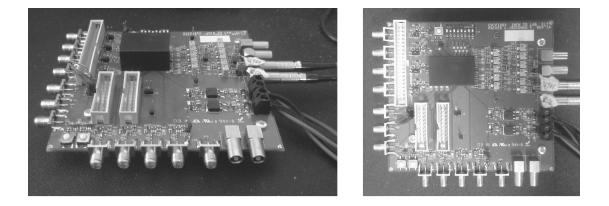

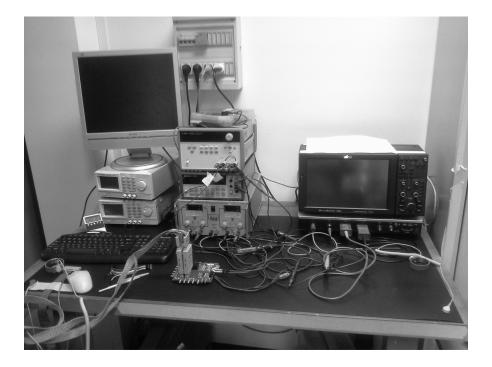

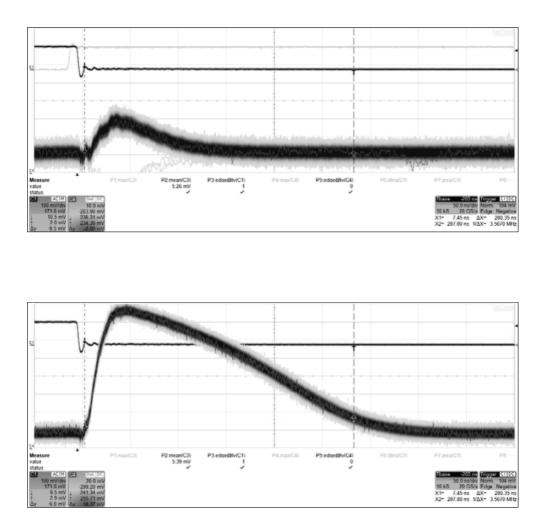

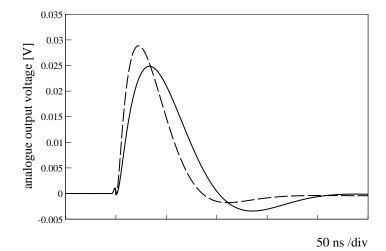

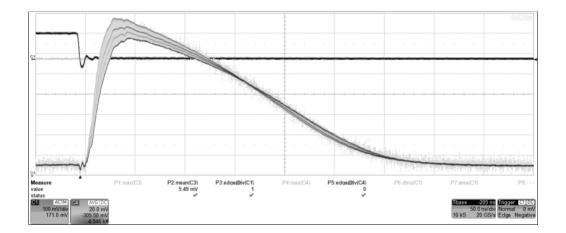

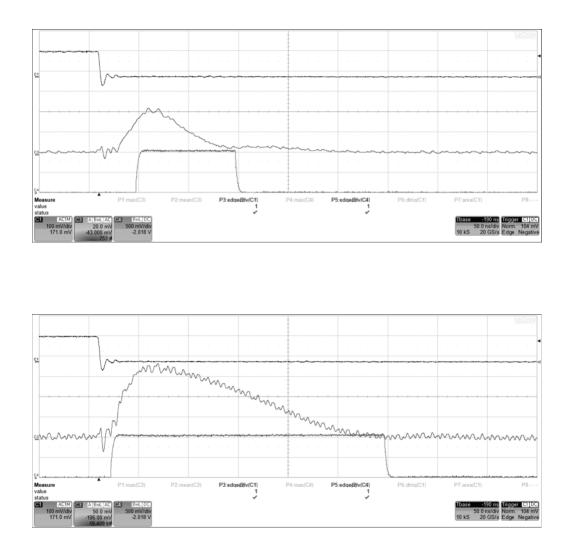

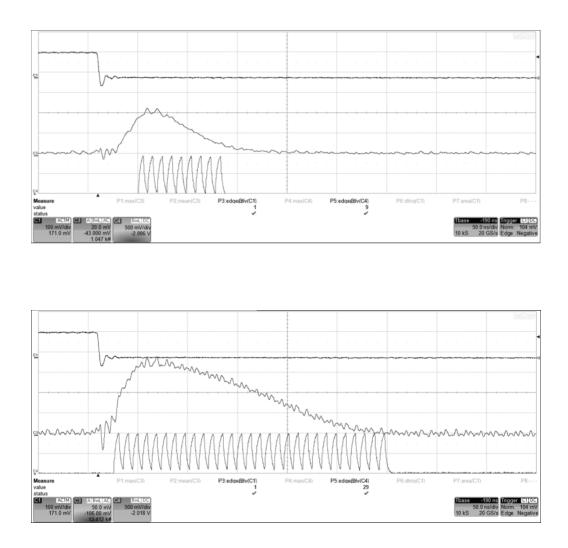

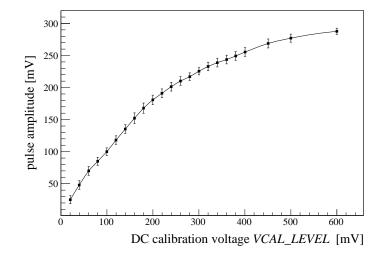

The LHC will remain the most powerful accelerator ever built in the world for at least two decades. In order to fully exploit the discovery potential of this machine, the foreseen LHC research program will extend over more than 20 years, investigating and validating the mathematical consistency of the Standard Model at the TeV energy scale and searching for evidences of new physics signatures. According with the expected increase of the machine performance in the forthcoming years, current planning for the LHC and its injector chain foresee a series of two additional long shutdowns, which will require major hardware modifications for both the machine and its experiments. A long-term plan for the evolution of the machine has been discussed during a Review of LHC Injector Upgrade Projects (RLIUP) workshop held at the end of October 2013, identifying the strategy that should lead to achieve an unprecedented integrated luminosity of 3000 fb<sup>-1</sup> in proton-proton collisions. Based on this input, the long-term schedule depicted on Figure 1.18 was established on December 2013.