# Design of integrated front chip in $0.35 \mu m$ CMOS for cellular signal recording systems based on diamond arrays

Candidato Sara Garbolino Relatore Prof. Diego Gamba Co-Relatore Dott. Angelo Rivetti

Tesi di Laurea Magistrale in Fisica delle Tecnologie Avanzate

Facoltà di Scienze Matematiche Fisiche Naturali Università degli studi di Torino July, 2008

### Abstract

The target of this work is to study and design a layout for an Analog Front End for cellular electrical signal recording systems based on diamond microelectrodes. The diamond is the most recent material considered for microelectrode implementation. Its surface becomes conductive through the hydrogenation process. It is biocompatible and optically transparent and its noise level is lower than the conventional metal microelectrodes. For this reason it is important to minimize the noise introduced by the electronics employed in the signal processing.

The advent of the microelectrode array (MEA) makes it possible to have hundreds of recording channels. To avoid signal attenuation and minimize noise the preamplifier has to be close to the recording electrodes and if it occupies a small area the number of the channels could be increased.

To comply with noise and space requirements we choose to design an integrate circuit in CMOS AMS  $0.35\mu m$  technology.

Main AFE requirements are very low noise, low power consumption, DC voltage rejection and a cut off frequency of some kHz.

The thesis is structured as follows:

- 1. **Introduction** It contains a brief description of neurons structure and their electrical activity, commonly used biosensors and experimental setup.

- 2. Front End Architecture The starting point [1] of the circuit is there described.

- 3. Layout and packaging This chapter deals with design rules and analog layout techniques.

- 4. **Preamplifier layout** and **Filter layout** A first layout has been designed starting from the architecture of Chapter 2. Problems related to the layout bahavior and solutions are exposed in this chapters, which contain also the study of more complex and more performant architectures.

- 5. Complete chip layout It describes the final submitted architecture layout and a summary of obtained results.

Acknowledgements

## Contents

|          | Abs  | stract |                                               | ii     |

|----------|------|--------|-----------------------------------------------|--------|

|          | Ack  | nowle  | dgements                                      | iii    |

|          | List | of Fig | gures                                         | viii   |

|          | List | of Ta  | bles                                          | ix     |

| 1        | Intr | oducti | ion                                           | 1      |

|          | 1.1  | Neuro  | ons and biosensors                            | <br>1  |

|          |      | 1.1.1  | Neuron's structure                            | <br>1  |

|          |      | 1.1.2  | Neuron's electrical activity                  | 2      |

|          |      | 1.1.3  | Recording methods                             | 4      |

|          | 1.2  | AFE I  | basic requirements                            | <br>7  |

| <b>2</b> | Fro  | nt End | l Architecture                                | 8      |

|          | 2.1  | Harris | son preamplifier                              | <br>8  |

|          |      | 2.1.1  | MOS-bipolar pseudoresistor                    | 9      |

|          |      | 2.1.2  | Low-noise, high gain and low-power OTA design | <br>10 |

|          | 2.2  | Filter | stage                                         | <br>13 |

|          |      | 2.2.1  | First OP-AMP stage                            | <br>13 |

|          |      | 2.2.2  | Second OP-AMP stage                           | <br>15 |

|          |      | 2.2.3  | Miller compensation                           | <br>15 |

|          |      | 2.2.4  | Two filters in cascade                        | <br>16 |

|          |      | 2.2.5  | Channel-to-channel mismatch                   | <br>16 |

|          | 2.3  | Outpu  | it buffer                                     | <br>17 |

| 3        | Lay  | out an | nd packaging                                  | 19     |

|          | 3.1  | Design | n rules                                       | <br>19 |

|          |      | 3.1.1  | Minimum allowable rules                       | <br>19 |

|          |      | 3.1.2  | Maximum allowable rules                       | <br>20 |

|          | 3.2  | Analo  | g layout techniques                           | <br>21 |

|          |      | 3.2.1  | Multifinger transistors                       | <br>21 |

|          |      | 3.2.2  | Symmetry                                      | <br>22 |

|          |      | 3.2.3  | Reference distribution                        | <br>26 |

|          |      | 3.2.4  | Passive devices                               | <br>27 |

|          |      | 3.2.5  | Interconnects                                 | <br>29 |

|              | $3.3 \\ 3.4$ | 3.2.6       Pads and ESD protection                                             | 31 |

|--------------|--------------|---------------------------------------------------------------------------------|----|

| 4            | Pre          | amplifier layout                                                                | 33 |

|              | 4.1          | Parasitic diodes                                                                | 33 |

|              | 4.2          | Noise issues                                                                    | 42 |

|              |              | 4.2.1 Single stage OTA                                                          | 42 |

|              |              | 4.2.2 Two stage OTA                                                             | 52 |

|              |              | 4.2.3 Output offset                                                             | 60 |

| <b>5</b>     | Filt         | er layout                                                                       | 62 |

|              | 5.1          | Random offset dependence on source degeneration resistance                      | 62 |

|              | 5.2          | AC coupling                                                                     | 64 |

|              |              | 5.2.1 $g_m - \frac{1}{q_m}$ AC coupling block                                   | 64 |

|              |              | 5.2.2 Current controlled AC coupling block $\ldots \ldots \ldots \ldots \ldots$ | 67 |

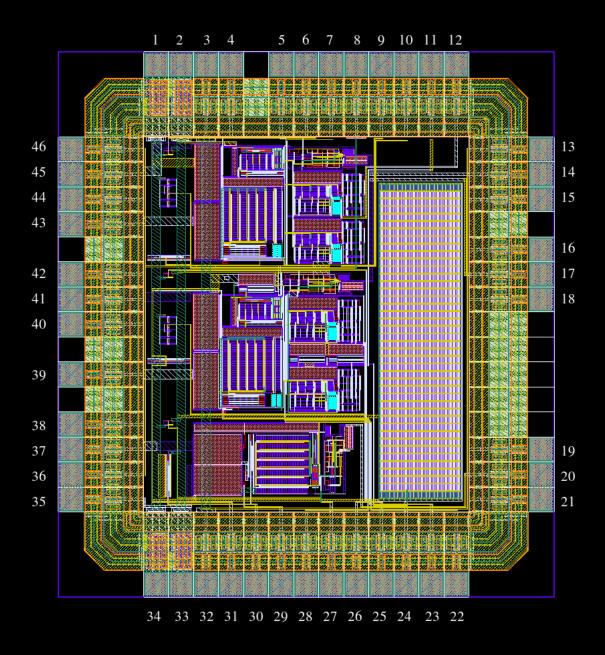

| 6            | Con          | nplete chip layout                                                              | 71 |

|              | 6.1          | External offset compensation voltage channel layout                             | 73 |

|              | 6.2          | AC coupled channel                                                              | 75 |

|              | 6.3          | Standard preamplifier OTA architecture                                          | 77 |

|              | 6.4          | Complete chip layout simulations                                                | 77 |

| 7            | Con          | clusions and future work                                                        | 81 |

|              | Con          | clusions and future work                                                        | 81 |

|              | App          | pendix                                                                          | 83 |

| $\mathbf{A}$ | Chi          | p data sheet                                                                    | 83 |

|              | Bib          | liography                                                                       | 87 |

## List of Figures

| 1.1  | Neuron main structure                                                                                                                                       | 2  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Double layer cellular membrane structure [2]                                                                                                                | 2  |

| 1.3  | Action potential progress                                                                                                                                   | 3  |

| 1.4  | Patch clamping                                                                                                                                              | 4  |

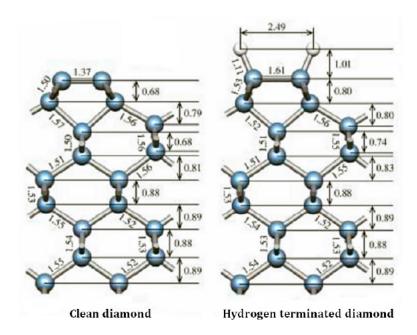

| 1.5  | pure and hydrogenated diamond (001) surfaces                                                                                                                | 5  |

| 1.6  | Diamond macroelectrode experimental setup                                                                                                                   | 6  |

| 1.7  | Time and frequency domain analysis of neuron spontaneous electro-                                                                                           |    |

|      | physiological activity [3]                                                                                                                                  | 7  |

| 2.1  | Block diagram of a single channel                                                                                                                           | 8  |

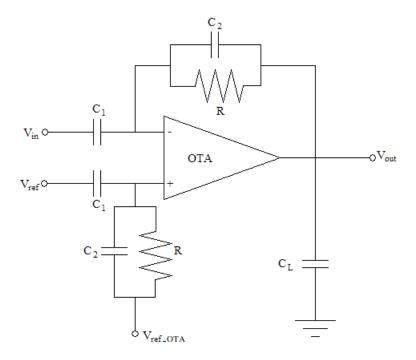

| 2.2  | Schematic of Harrison's bandpass preamplifier                                                                                                               | 9  |

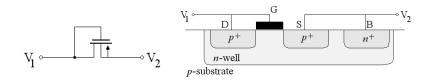

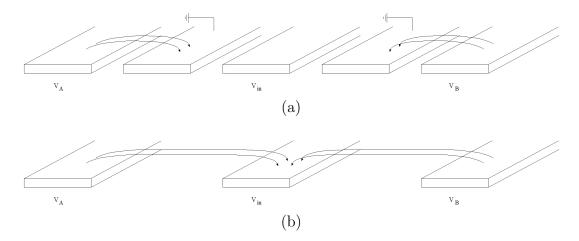

| 2.3  | MOS-bipolar pseudoresistor                                                                                                                                  | 9  |

| 2.4  | MOS-bipolar pseudoresistor working                                                                                                                          | 10 |

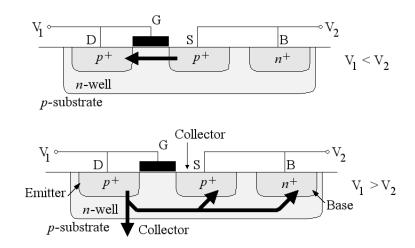

| 2.5  | I-V relationship and incremental resistance of single MOS-bipolar el-                                                                                       | -  |

|      | $\operatorname{ement} \ldots \ldots$ | 10 |

| 2.6  | Schematic of OTA used in Harrison preamplifier                                                                                                              | 12 |

| 2.7  | Schematic of filter OP-AMP                                                                                                                                  | 14 |

| 2.8  | Source degeneration resistance scheme                                                                                                                       | 14 |

| 2.9  | Schematic of filter stage                                                                                                                                   | 16 |

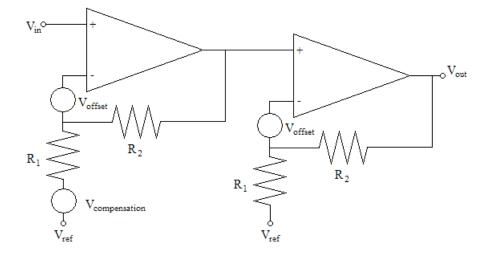

| 2.10 | Filter stage offset compensation system                                                                                                                     | 17 |

|      | Schematic of output buffer OP-AMP                                                                                                                           | 18 |

|      | Output buffer scheme                                                                                                                                        | 18 |

|      |                                                                                                                                                             | 10 |

| 3.1  | (a) Layout susceptible to antenna effect. (b) Discontinuity in <i>metal</i>                                                                                 | 20 |

| 2.2  | 1 layer to avoid antenna effect                                                                                                                             | 20 |

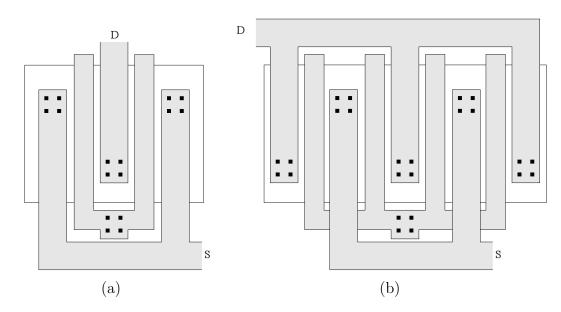

| 3.2  | (a) Simple folded transistor. (b) Multifinger structure of a MOSFET                                                                                         | 21 |

| 3.3  | Layout of a transistor using (a) three fingers, (b) five fingers                                                                                            | 22 |

| 3.4  | Layout of a transistor with many fingers                                                                                                                    | 22 |

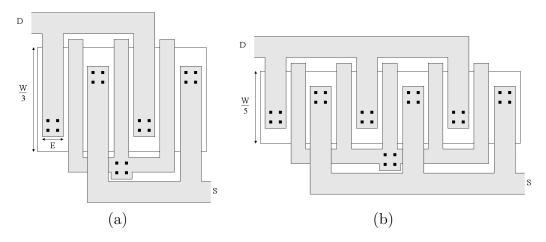

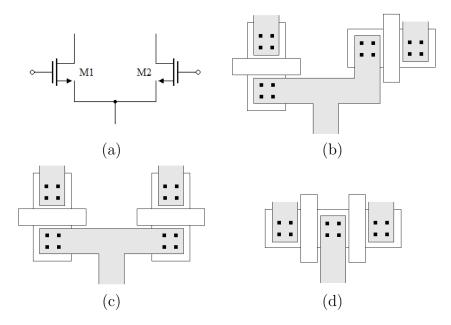

| 3.5  | (a) Differential pair. (b) An example of an asymmetric layout and                                                                                           |    |

|      | (c), (d) two symmetric layouts of the differential pair                                                                                                     | 23 |

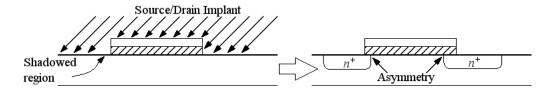

| 3.6  | Gate shadowing effect                                                                                                                                       | 23 |

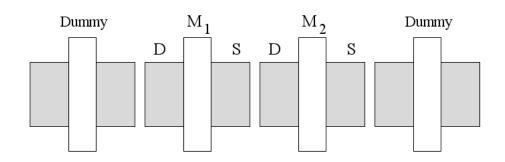

| 3.7  | Addition of dummy devices to improve symmetry                                                                                                               |    |

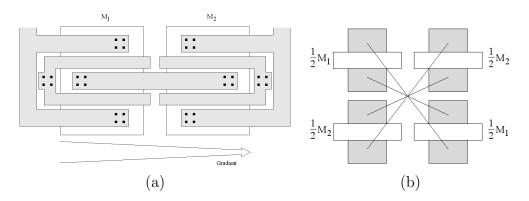

| 3.8  | (a) Effect of gradient on a differential pair. (b) Common centroid layout                                                                                   | 24 |

| 3.9  | One-dimensional cross coupling                                                                                                                              | 25 |

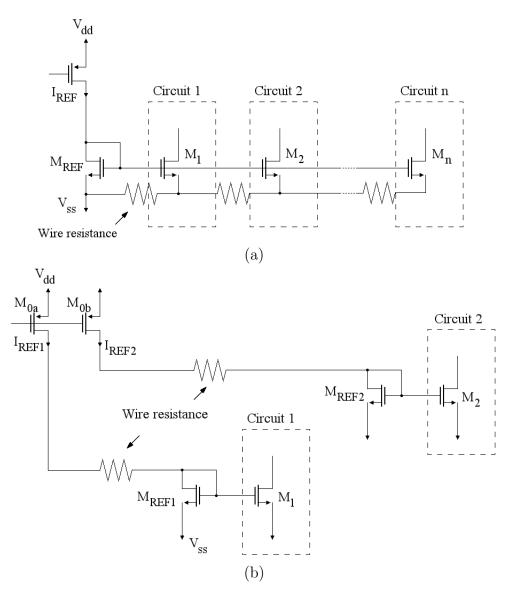

| 3.10 | (a) Distribution of a reference voltage for current mirror biasing. (b)                                                                                     |    |

|      | Distribution of current to reduce the effect of interconnect resistance .                                                                                   | 26 |

| 3.11 | (a) Layout of large resistor. (b) Serpentine topology                                                                                                       | 27 |

| 3.12 | Capacitors made using allowable conductive layers                                                                                                           | 28 |

|              | Diodes in CMOS technology                                                                                                                                                                                                                                       | 29<br>30   |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 3.15         | Simple EDS protection circuit                                                                                                                                                                                                                                   | 31         |

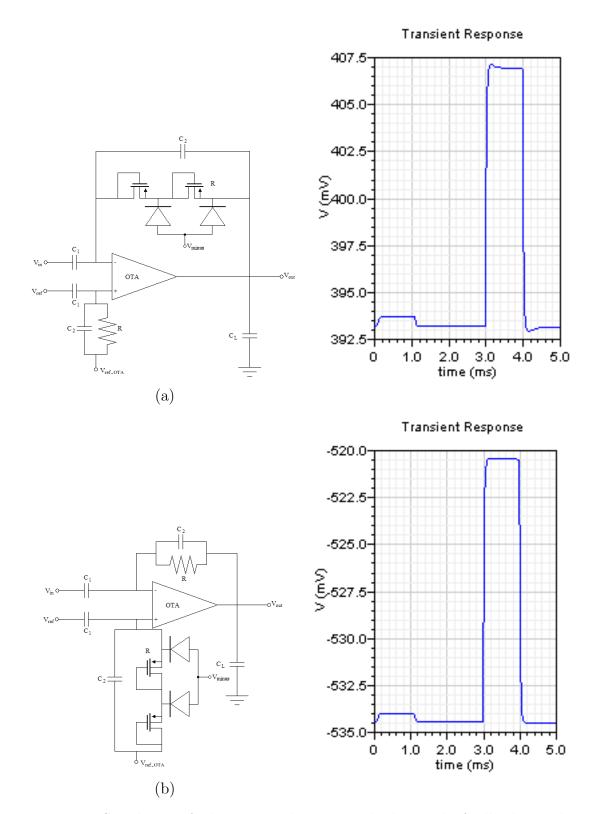

| 4.1<br>4.2   | Harrison preamplifier layout transient simulation                                                                                                                                                                                                               | 34<br>34   |

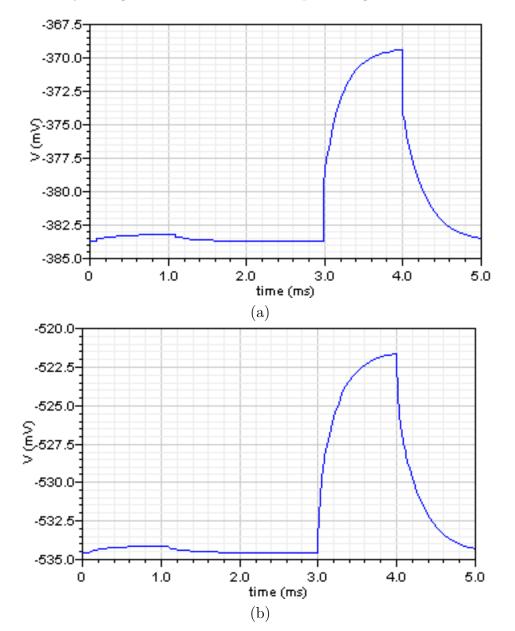

| 4.3<br>4.4   | Introduction of parasitic diodes in the schematic transient simulation<br>Simulation of schematic with parasitic diodes on the feedback pseu-<br>doresistor (a) and on the pseudoresistor at the positive input (b)                                             | 35<br>36   |

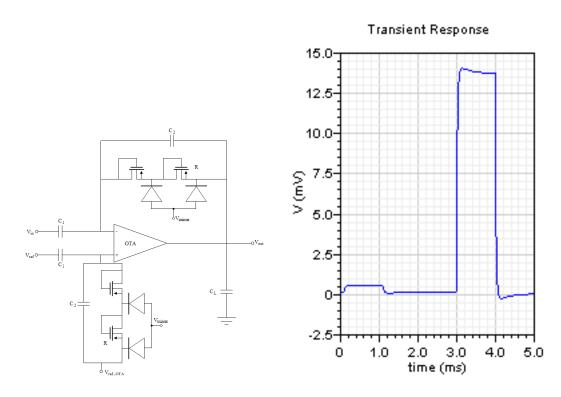

| $4.5 \\ 4.6$ | Simulation with reversed pseudoresistor                                                                                                                                                                                                                         | $37 \\ 37$ |

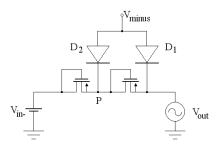

| 4.7          | Transient response of point P on the model (a) and on the preamplifier<br>(b)                                                                                                                                                                                   | 38         |

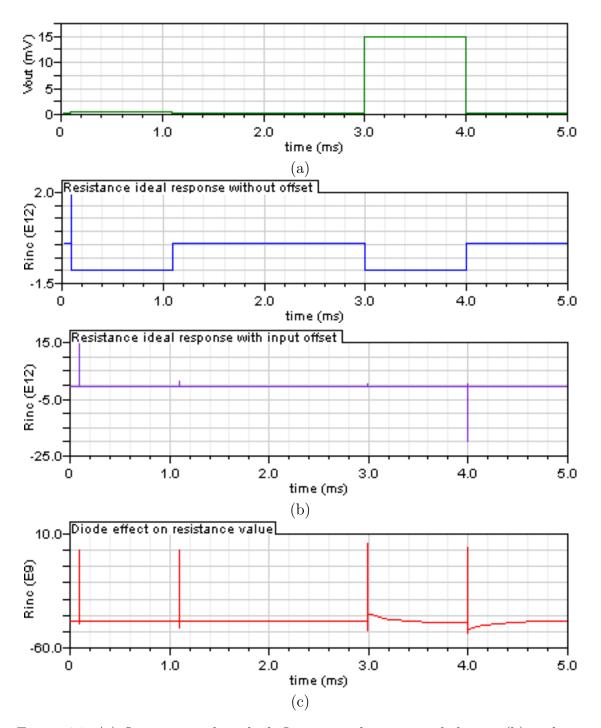

| 4.8          | (a) Output signal applied. Incremental resistance behavior (b) with-<br>out and (c) with parasitic diodes                                                                                                                                                       | 39         |

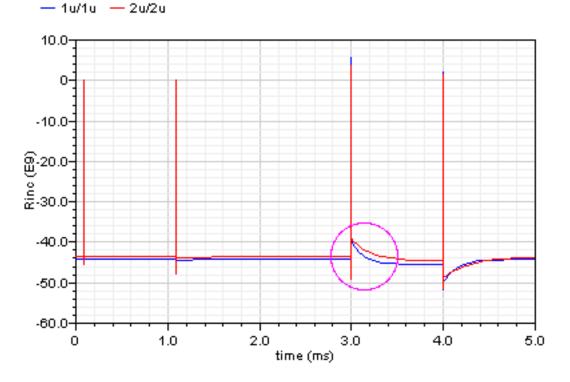

| 4.9          | Shorter MOS-bipolar pseudoresistor settling time using smaller tran-<br>sistors                                                                                                                                                                                 | 40         |

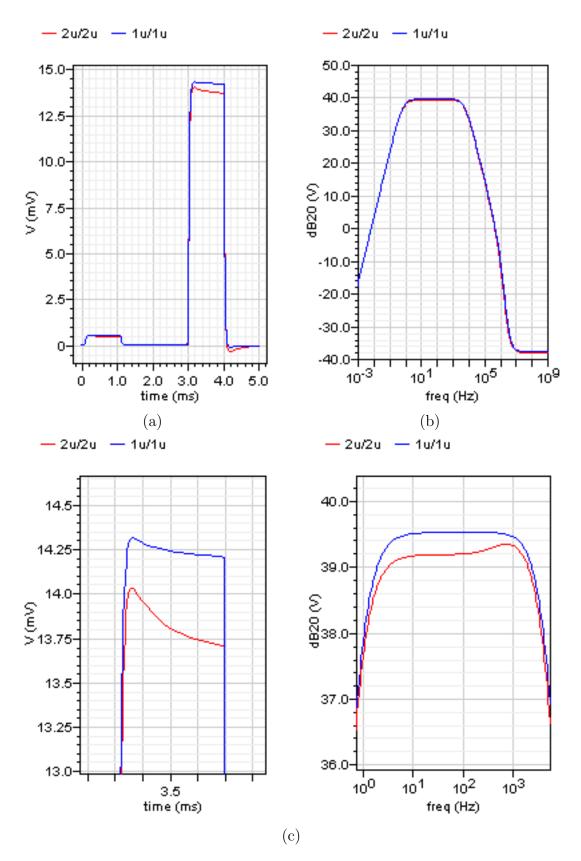

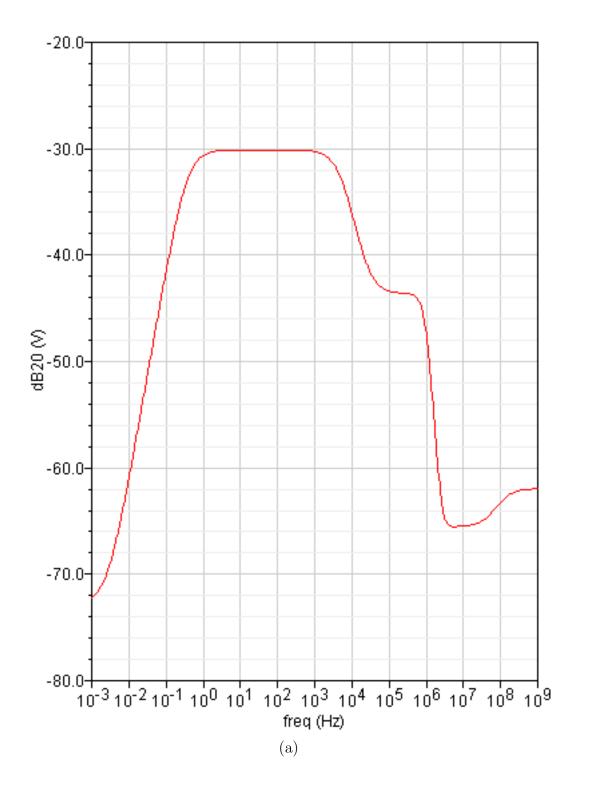

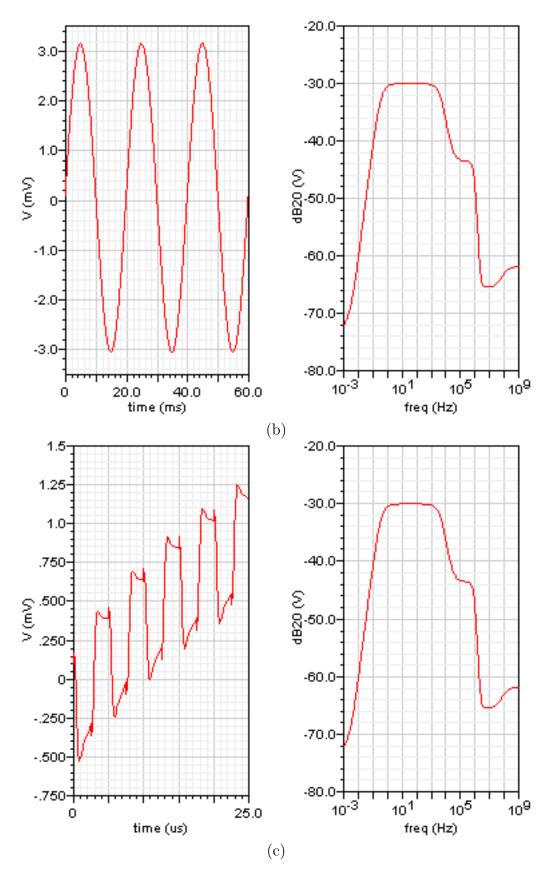

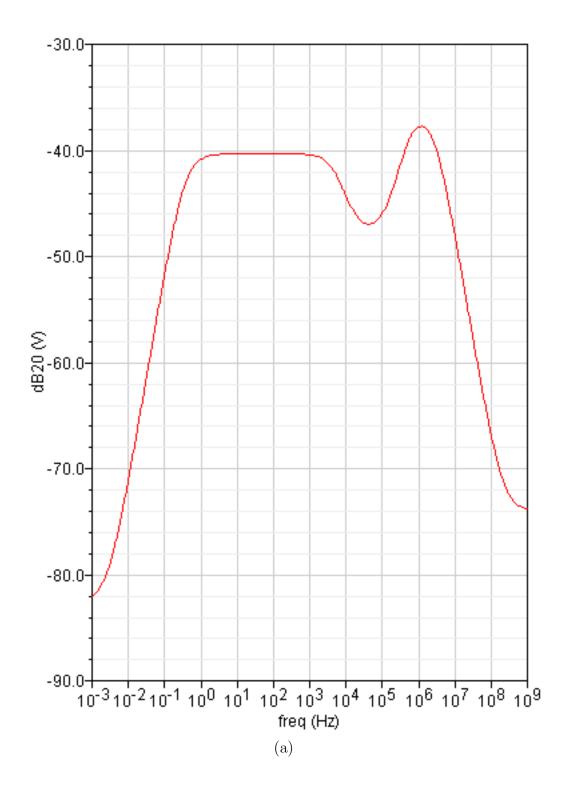

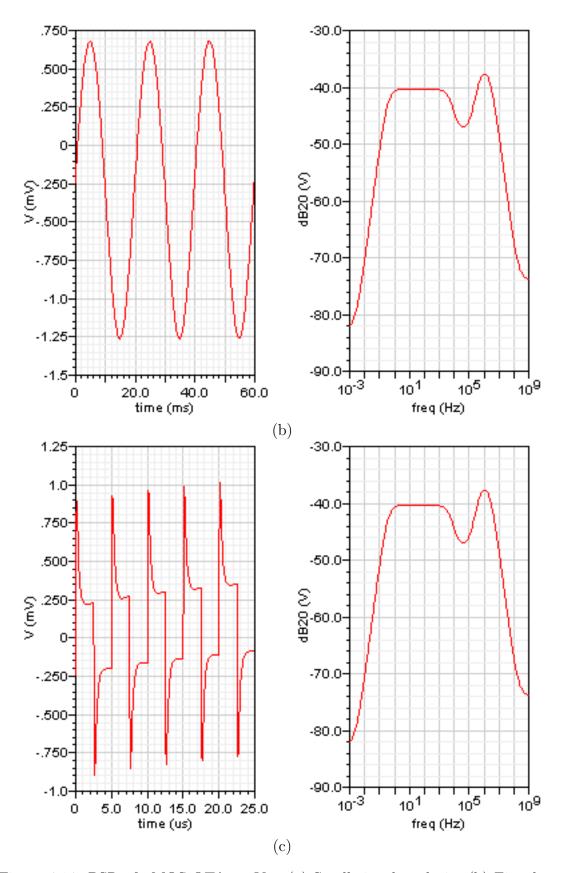

| 4.10         | Preamplifier transient (a) and AC (b) responses. (c) Zoom on more affected regions                                                                                                                                                                              | 41         |

|              | <i>n</i> -type symmetrical OTA                                                                                                                                                                                                                                  | 42         |

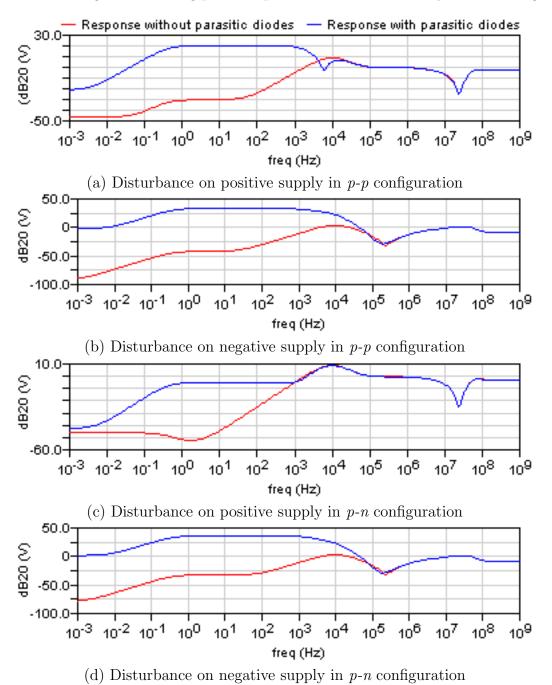

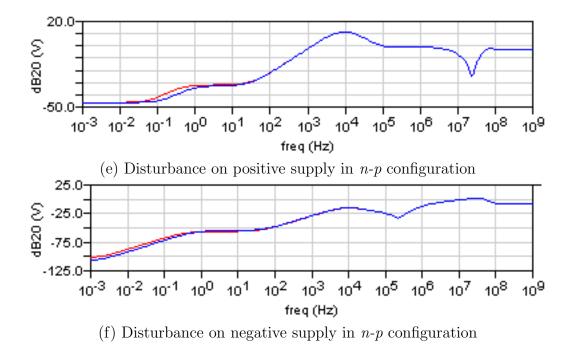

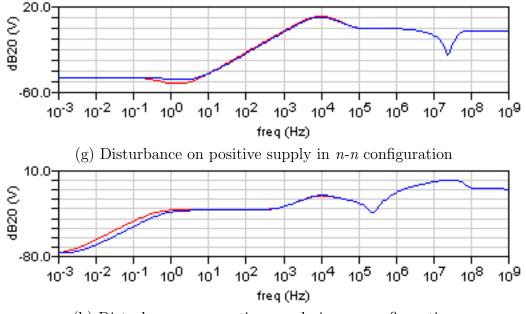

|              | signal analysis. (c) Second large signal analysis $\dots \dots \dots \dots \dots$<br>PSR of pMOS OTA on $V_{ss}$ . (a) Small signal analysis. (b) First large                                                                                                   | 45         |

| 4.14         | signal analysis. (c) Second large signal analysis $\dots \dots \dots \dots$<br>PSR of nMOS OTA on $V_{dd}$ . (a) Small signal analysis. (b) First large                                                                                                         | 47         |

| 4.15         | signal analysis. (c) Second large signal analysis $\dots \dots \dots \dots$<br>PSR of nMOS OTA on $V_{ss}$ . (a) Small signal analysis. (b) First large                                                                                                         | 49         |

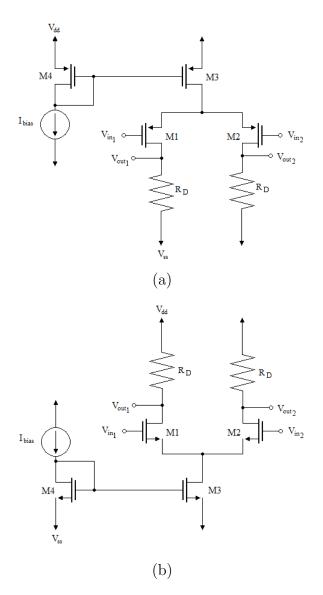

| 4.16         | signal analysis. (c) Second large signal analysis Fully differential OTA with resistive loads with (a) pMOS and (b)                                                                                                                                             | 51         |

| 4.17         | nMOS input transistors                                                                                                                                                                                                                                          | 52         |

| 4.18         | sitic diodes in MOS-bipolar pseudoresistors                                                                                                                                                                                                                     | $55 \\ 57$ |

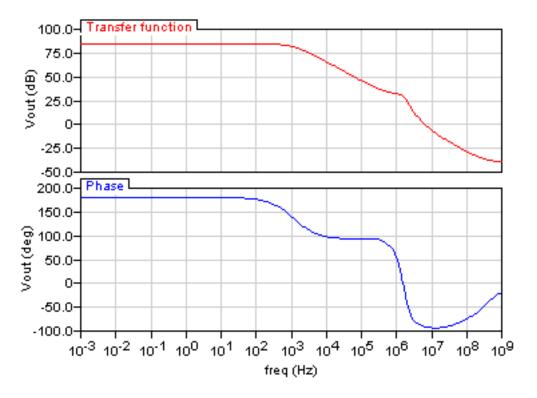

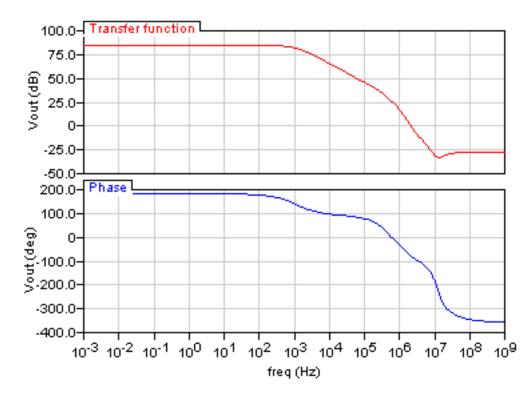

|              | Two stage transfer function after Miller compensation $(c_{C1})$                                                                                                                                                                                                | 59         |

|              | Two stage transfer function after second output compensation $(c_{C2})$ .                                                                                                                                                                                       | 59         |

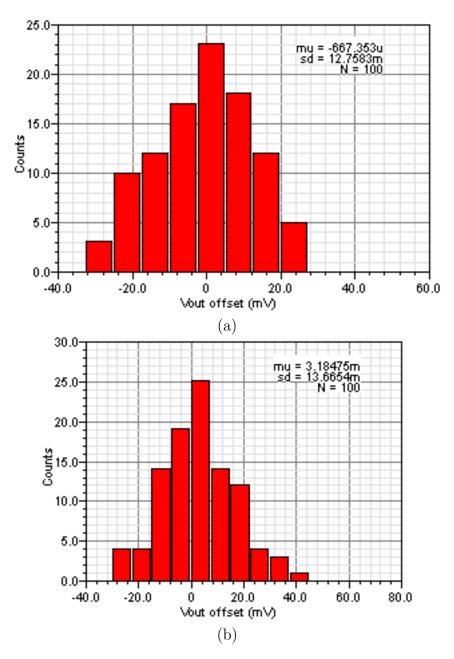

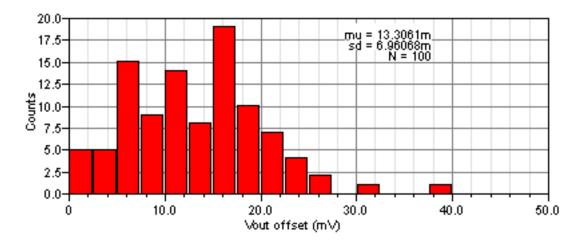

|              | Montecarlo simulations of Harrison preamplifier layout using (a) single stage OTA with pMOS inputs and (b) double stage OTA in $n-n$                                                                                                                            |            |

|              | configuration                                                                                                                                                                                                                                                   | 60         |

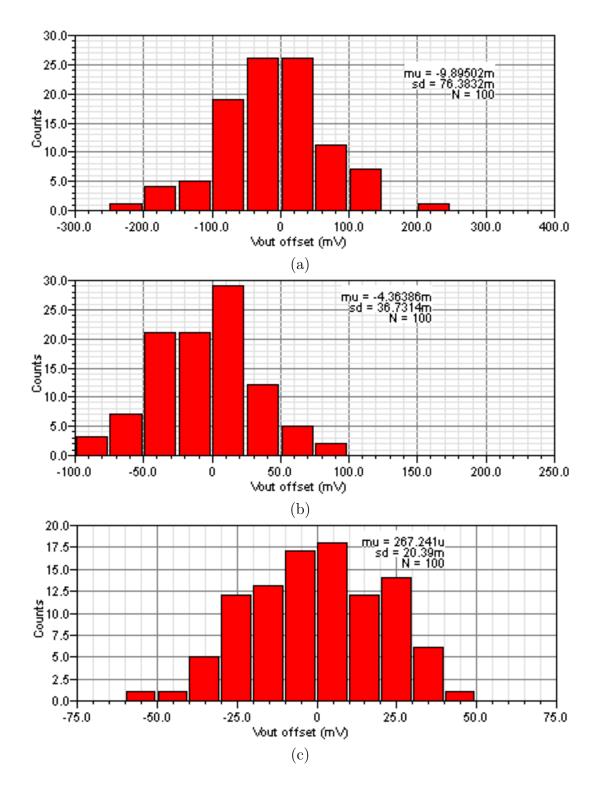

| 5.1          | Variation of random offset depending on $R_S$ value. (a) A $500mV_{pp}$ offset was found using $R_S \sim 1M\Omega$ . (b) Halving $R_S$ it reduces to $\sim 200mV_{pp}$ and (c) a $\sim 110mV_{pp}$ offset was estimated reducing once again $R_S$ of a factor 2 | 63         |

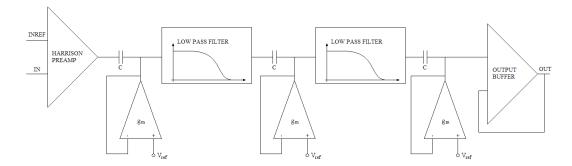

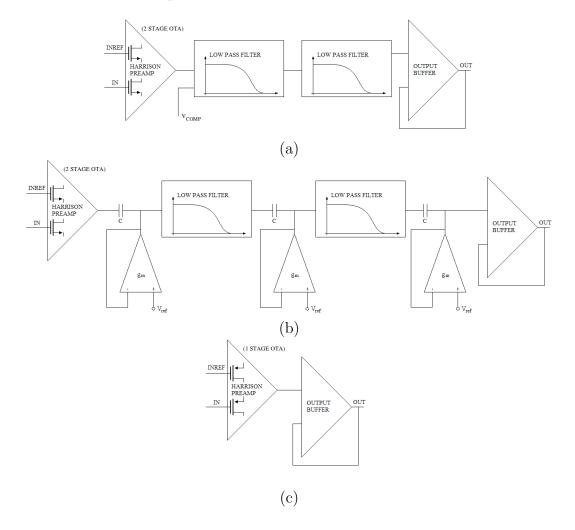

| 5.2          | Channel block scheme with AC coupling circuits                                                                                                                                                                                                                  | 64         |

|              |                                                                                                                                                                                                                                                                 |            |

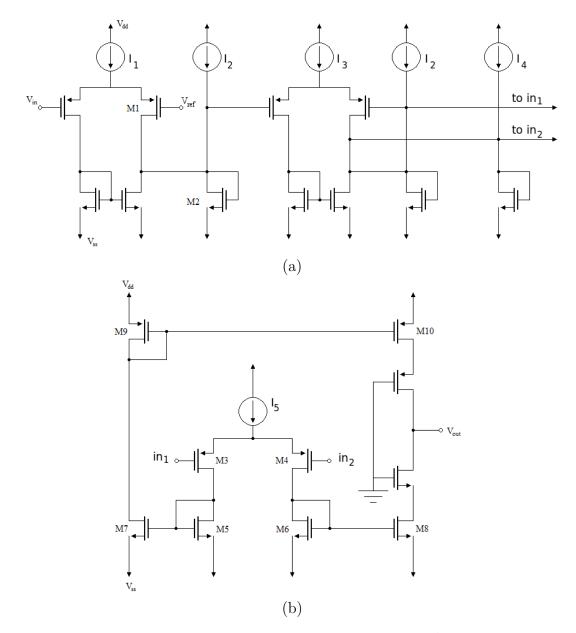

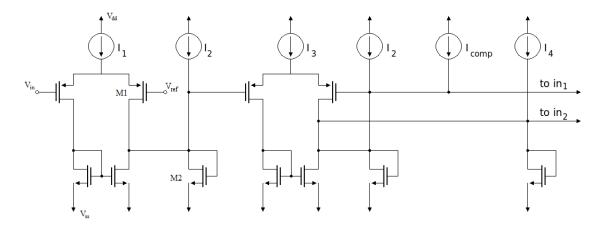

| $5.3 \\ 5.4$ | (a) First and (b) second stage of $g_m - \frac{1}{g_m}$ chain               | 65 |

|--------------|-----------------------------------------------------------------------------|----|

|              | stage in order to balance offsets in the second stage                       | 67 |

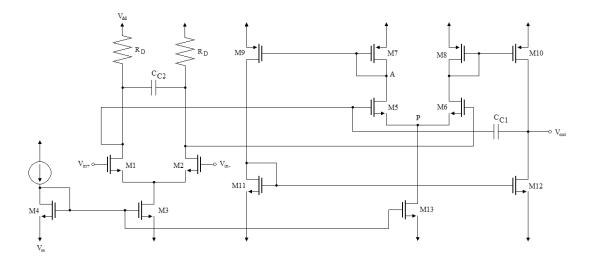

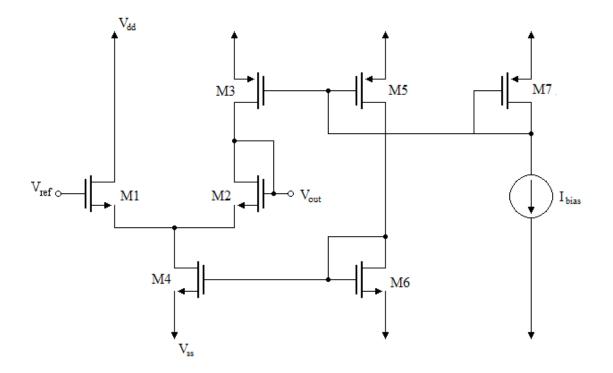

| 5.5          | OTA used for the AC coupling block                                          | 68 |

| 5.6          | Monte Carlo random offset simulation of the AC coupling block $\ldots$      | 69 |

| 6.1          | (a) First, (b) second and (c) third channels schematics used in chip        |    |

|              | layout                                                                      | 71 |

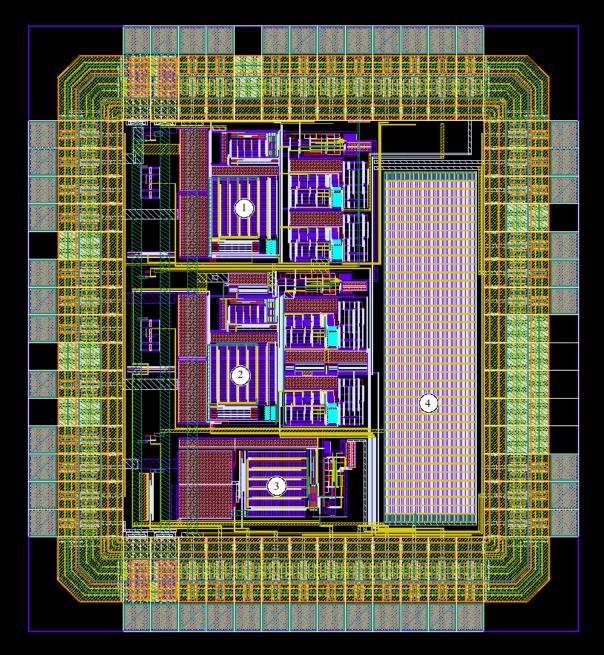

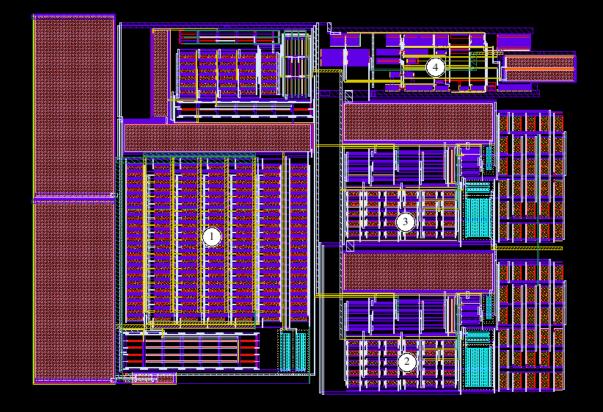

| 6.2          | Complete chip layout. $(1, 2, 3)$ Each channel is enlarged in Fig. from     |    |

|              | 6.3 to 6.7. (4) AC coupling circuit current mirror                          | 72 |

| 6.3          | Layout of the channel using external voltage offset compensation. $(1)$     |    |

|              | Harrison preamplifier using two stage OTA, $(2)$ first filter, $(3)$ second |    |

|              | filter and (4) output buffer                                                | 73 |

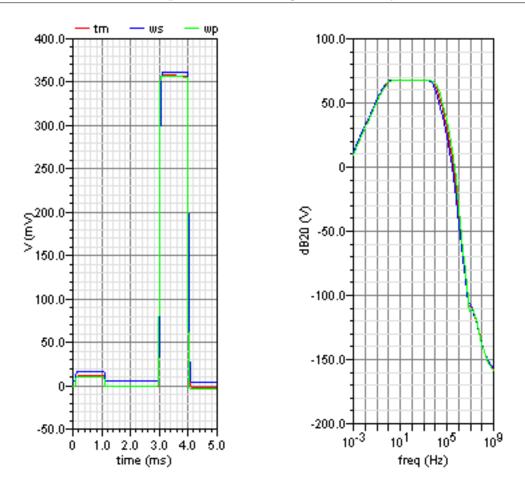

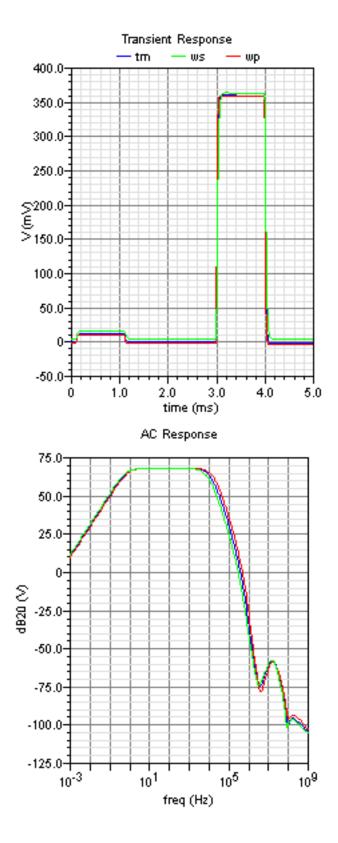

| 6.4          | Transient and AC response in worst cases of the first channel layout .      | 74 |

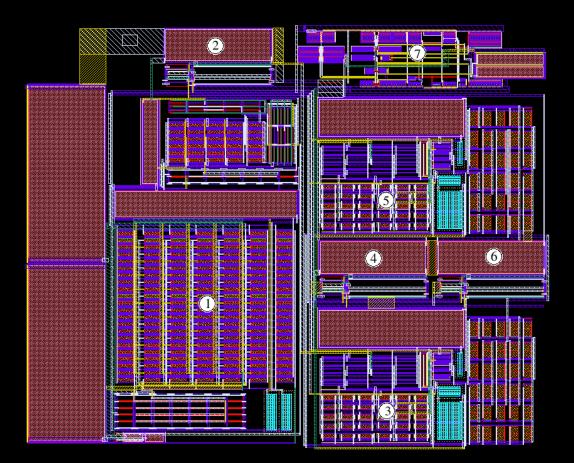

| 6.5          | Layout of the channel using AC coupling circuits. (1) Harrison pream-       |    |

|              | plifier using two stage OTA, (2) first AC coupling block, (3) first filter, |    |

|              | (4) second AC coupling block, (5) second filter, (6) third AC coupling      |    |

|              | block and (7) output buffer                                                 | 75 |

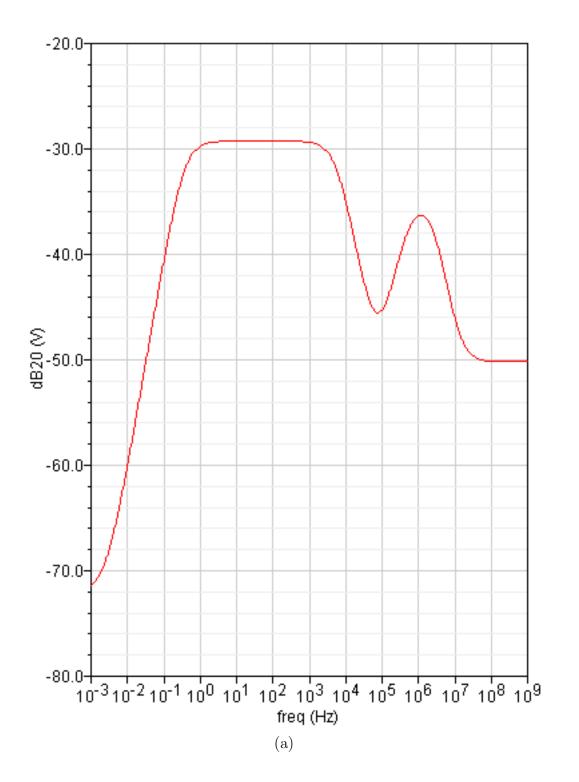

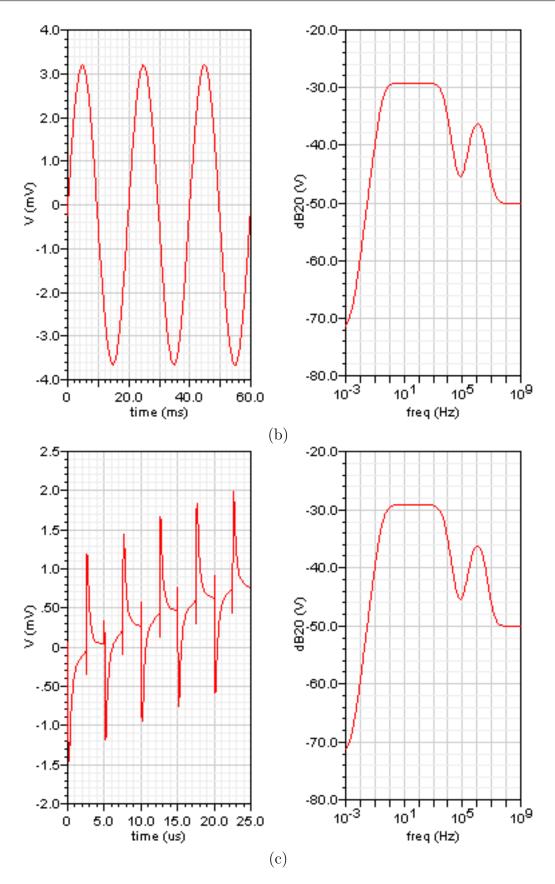

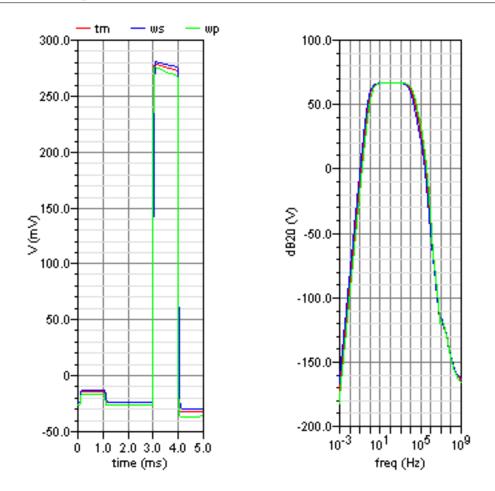

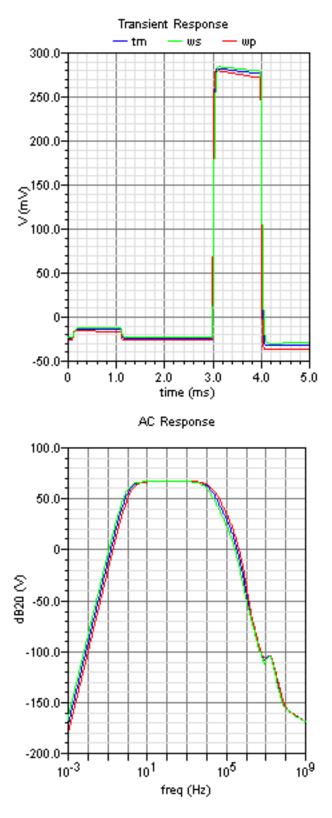

| 6.6          | Transient and AC response in worst cases of the second channel layout       | 76 |

| 6.7          | Layout of channel using standard preamplifier configuration. (1) Har-       |    |

|              | rison preamplifier using single stage OTA with $p$ -MOS inputs and (2)      |    |

|              | output buffer                                                               | 77 |

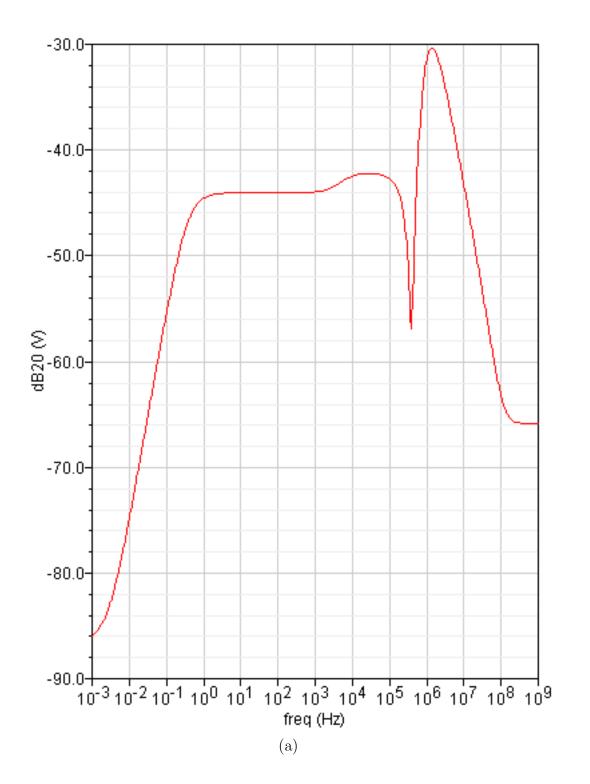

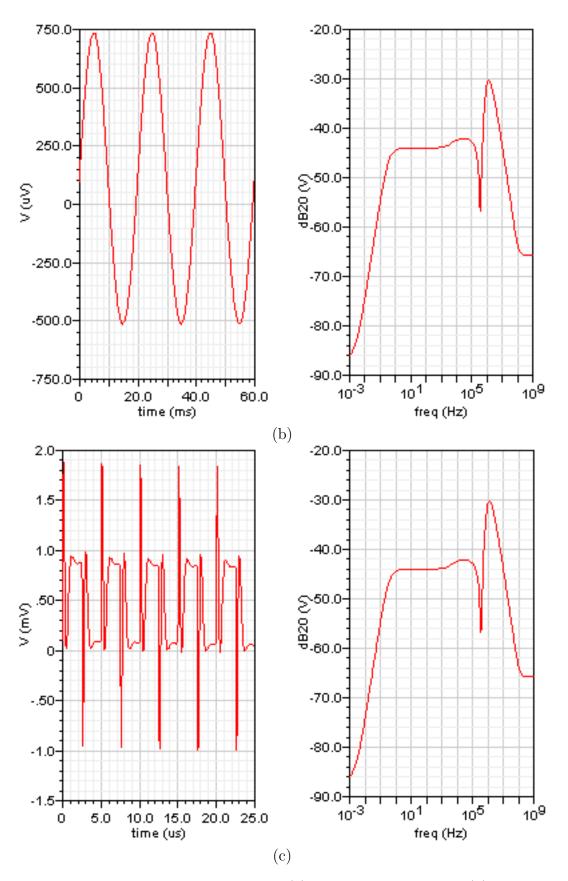

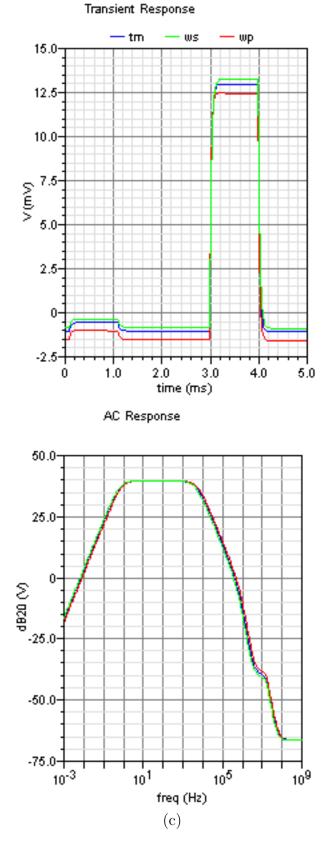

| 6.8          | Worst cases simulations of the complete chip layout. Transient and          |    |

|              | AC responses of (a) the channel using external compensation voltage,        |    |

|              | (b) the AC coupled one and (c) of standard preamplifier                     | 80 |

## List of Tables

| 2.1 | Influence of $A_{VM}^{OTA}$ on the $A_{VM}$ precision $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 11 |

|-----|-----------------------------------------------------------------------------------------------------------------|----|

|     | OTA's MOS dimensions                                                                                            |    |

| 4.1 | $p$ -type symmetrical OTA Harrison preamplifier noise $\ldots \ldots \ldots$                                    | 42 |

| 4.2 | Noise response of the complete channel amplifying $67.83 dB$ in a band-                                         |    |

|     | with $6kHz$ large using a two stage OTA Harrison preamplifier                                                   | 53 |

| 4.3 | Complete channel input referred noise variation with second stage                                               |    |

|     | input transistors dimensions                                                                                    | 56 |

| 5.1 | Low cut frequency dependence on bias current                                                                    | 69 |

| 5.2 | Gain of each stage of the channel using the current controlled AC                                               |    |

|     | coupling circuit                                                                                                | 69 |

| 5.3 | Dependence of the gain on filter input transistors dimensions                                                   | 70 |

| 6.1 | Worst cases analysis results on first channel layout                                                            | 73 |

| 6.2 | Results of temperature analysis on first channel layout                                                         | 74 |

| 6.3 | Worst cases analysis results on second channel layout                                                           | 75 |

| 6.4 | Results of temperature analysis on second channel layout                                                        | 76 |

# Chapter 1 Introduction

In order to characterize electrical signals from neurons, it is necessary to monitor their action potentials, which are variation of the transmembrane potential due to the flux of ions between cell's cytoplasm and external medium.

Results from this characterization find several applications in pharmaceutical screening, biochemical agents monitoring, drug detection, etc.

In this chapter the reader can find in the first part a short explanation of neurons electrical activity, followed by a description of cultured cell recording methods, focusing on diamond microelectrode array.

The second part of the chapter contains a list of electronic requirements for this application and a description of the chosen Front End architecture.

#### 1.1 Neurons and biosensors

#### 1.1.1 Neuron's structure

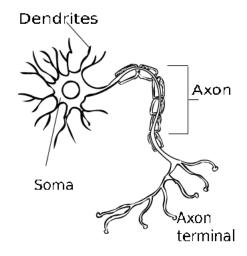

Neurons are cells capable of processing and transmitting informations through electrical pulses.

They are distinguished by their function in the nervous system and by the way they transmit signals. However the main structure is the same for all types (Fig. 1.1).

Neuron's main components are:

- **soma** the cell body where most protein synthesis occurs. It ranges from  $4\mu m$  to  $25\mu m$ ;

- **dendrites** branching fibers extending from the cell body, specialized in receiving incoming signals;

- **axon** which has the function of transmitting action potentials to the dendrites of another neuron;

- **axon terminal** placed at the end of the axon, its task is to electrically and chemically communicate with target neurons.

Figure 1.1: Neuron main structure

#### 1.1.2 Neuron's electrical activity

#### Cellular membrane

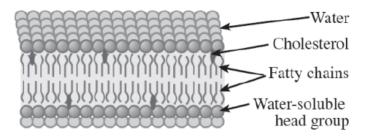

Neural electrical activity is due to the flux of ions through a semipermeable bilayer membrane that covers the neuron itself.

The cellular membrane is composed by a double layer of molecules with fatty hydrophobic tails and charged hydrophilic heads. Layers are disposed as shown in Fig. 1.2.

Figure 1.2: Double layer cellular membrane structure [2]

Fatty chains ( $\sim 7nm$  thick) have the role of electrically insulating the external medium from the cytoplasm preventing ions, charged and uncharged molecules from passively diffusing from one region to the other and allowing the cell to control this flux through transmembrane proteins placed on the membrane. There are proteins that pump ions against their electrochemical gradient and others that form a channel through which ions can move along their electrochemical gradient.

#### **Resting potential**

With resting potential is meant the electrical field that rise between intracellular and extracellular surfaces because of the ions movements in equilibrium state. At resting potential there are relatively more  $Na^+$  ions outside of the neuron and more  $K^+$  ions inside of it. The major contribution to the resting potential is given by  $K^+$  ions and it assumes the typical value of -70mV (negative charge inside the cell relative to the outside).

#### Action potential

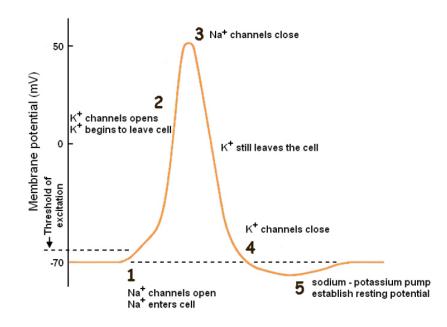

Figure 1.3: Action potential progress

Action potential carries out in five steps (Fig. 1.3).

- Stimulation If transmembrane potential reaches about -50mV, sodium channels are opened for a short period allowing the flux of  $Na^+$  ions into the cell and causing the membrane potential to become positive.

- **Depolarization ("Rising phase")** At some positive membrane potential the  $K^+$  channels are opened too, therefore  $K^+$  ions can flow outside of the neuron.

- **Peak** When +50mV potential is reached  $Na^+$  channels close stopping the inflow of positive charges.

- **Repolarization ("Falling phase")** Since  $K^+$  channels are still open, the membrane potential begin to decrease.

- **Undershoot** When the resting potential is reached,  $K^+$  channels close. Equilibrium ion transport starts again and the cell is ready for the next action potential.

The entire membrane doesn't depolarize at once, depolarization starts in one area and spreads by diffusion to contiguous regions. The process of depolarization and repolarization takes about 0.5ms-1.5ms.

#### 1.1.3 Recording methods

Testing on cultured cells, that means *in vitro*, rather than on *in vivo* cells is more suitable in order to study their behavior and activity. In this section some cultured cell recording method will be exposed.

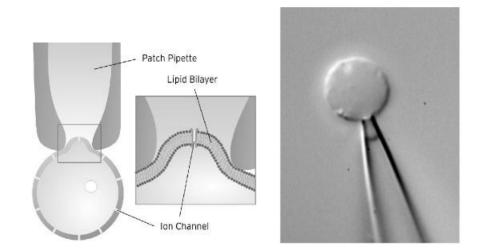

#### Patch clamping

Figure 1.4: Patch clamping

This is an invasive method that consist on patching the tip of a glass electrolytefilled pipette of about  $1\mu m$  diameter to the membrane of a cell, calmping it to a preset voltage and measuring the resulting current (Fig. 1.4).

The advantage is the possibility to record directly action potentials of about 100mV wide and to study individual ion channels. As a drawback, it has a mechanically fragile connection which makes long term recording difficult.

#### Microelectrode

This is a non-invasive solution which estimates the transmembrane potential variation measuring the ion concentration change in extracellular medium surrounding the cell.

Two electrodes  $10\mu m$  large are placed, the first near the cellular membrane and the second far from it, as a reference electrode.

Advantages are given by the possibility of monitoring and stimulating the electrochemical activity of several cells independently and simultaneously for a long time, but signals recorded are on the order of  $100\mu V$  against 100mV of patch clamping.

It's simple to implement a microelectrode array (MEA), That is an arrangement of several electrodes (typically 60 placed at a distance of some hundreds micrometers). This solution allows recording and stimulation of more sites in parallel, moreover the sample can be placed directly on the recording area.

Typical detection distances are lower than  $100\mu m$ .

The impedance of a flat, round titanium nitride electrode ranges from  $30\Omega$  and

$400k\Omega$ . The smaller the electrode diameter and interelectrode distance, the higher the spacial resolution. However, small electrode results in higher noise: the average noise level of  $30\mu m$  microelectrode is lower than  $10\mu V$ , while for a  $15\mu m$  diameter microelectrode it's lower than  $15\mu V$ .

#### Diamond microelectrode

A new material for microelecrode arrays, still in testing phase, is given by diamond. Diamond has a bandgap of about 5.5eV and is considered an insulator, but, with its surface hydrogenated, it becomes conductive. Hydrogenating diamond, dangling bonds on the surface are saturated by hydrogen atoms creating hole accumulation layers in the bandgap that act as acceptors (Fig. 1.5).

Figure 1.5: pure and hydrogenated diamond (001) surfaces

Moreover, when exposed to atmosphere, a thin water layer forms on the surface acting as an acceptor surface for the diamond exchanging electrons with hydrogen terminations.

The result is an areal hole density of  $\rho_{surface} \approx 10^{13} cm^{-2}$  and a superficial sheet resistance of  $R_{\Box} \approx 10^4 \Omega/\Box$  at room temperature.

Diamond is preferred to conventional electrode materials because of some favorable properties.

First of all it is biocompatible, having an inert surface that assure a long term stability with weak adsorption of polar molecules.

Furthermore, having a transmittance grater than 50% in the visible wavelength region upon 500nm, it can be considered optically transparent. This property allows first to position the cell on the microelectrodes through a microscope, and second to record optical signals of cells by using fluorescent dyes. Besides it gives the possibility of modulating its surface characteristics, such as resistivity, with oxygen or hydrogen terminations.

#### Experimental setup

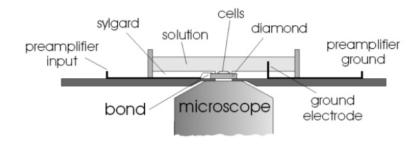

Figure 1.6: Diamond macroelectrode experimental setup

For the testing measurements a diamond microelectrode of  $3mm^2$  was used. The borders of the macroelectrodes are fixed to a high resistivity printed circuit board. A microscope positioned under the macroelectrode allows to see the cells immersed in the electrolyte medium and directly coupled with the macroelectrode. In order to insulate the electrolyte from conductors, bond wires and interconnections a sylgard passivation layer is used. The preamplifier input signal is taken through a gold wire of  $20\mu m$  diameter connected to diamond with a silver paste, while ground electrode is connected to a silver chloride reference electrode immersed in the cultured media.

It is possible to measure the diamond electrode noise level, and it is expected being lower than the one of metallic electrodes ( $\leq 5\mu V$ ). To amplify the signal without increasing the noise floor and to prevent from amplification of the relatively small extracellular signals, a low noise, high input impedance preamplifier is required.

Extracellular signals are  $10^3$  times smaller than transmembrane potentials. Signal amplitude and wave shape depends on many factors, such as the diameter of the neuron, the proximity of the electrode to the neuron, the angle between the electrode surface and the neuron, the portion of the neuron to which the electrode is closest. There are small regions of close adhesion (< 15nm) between membrane and electrode, while other regions are more loosely coupled and separation reaches 100nm. Thanks to low pass filtering properties of the extracellular medium, the more the neuron-electrode distance increases, the more the extracellular signal amplitude decreases; than, neurons placed beyond 140nm from the electrode are indistinguishable from noise. In this regard, high spatial resolution of the electrode and close interface between electrode and cell are very important to obtain a good signal-to-noise ratio.

#### **1.2** AFE basic requirements

AFE basic requirements are imposed by the characteristics of the signal coming from the sensor:

- Amplitude:  $150\mu V$

- Frequency domain: 10Hz-3kHz

- Biological noise:  $10\mu Vrms$

- DC component:  $\pm 50mV$

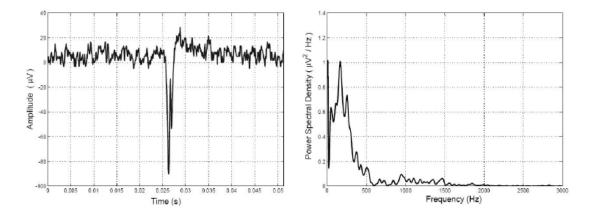

Figure 1.7: Time and frequency domain analysis of neuron spontaneous electrophysiological activity [3]

First important feature of the preamplifier is the frequency band. It has to cut the DC component without cutting the signal. A typical band is between  $f_L \approx 10 Hz$  and  $f_H \approx 10 kHz$ .

Moreover the differential input must have a high input resistance in order to have a negligible voltage drop on the microelectrode ( $R_{electrode} \leq 400 K\Omega$ ). Low power consumption is required too not to damage by heating biological tissues and to have many recording channels on the same chip in a small silicon area. Furthermore, most important features are low noise and high gain (to minimize following stages noise contribution) [1].

# Chapter 2 Front End Architecture

This chapter deals with the description of the chosen Front End Architecture for neural signal recording coming from diamond MEA biosensors together with the reasons for this choice.

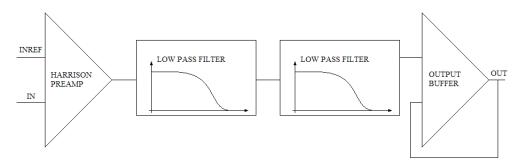

A block diagram of single channel is shown in fig. 2.1.

Figure 2.1: Block diagram of a single channel

#### 2.1 Harrison preamplifier

As exposed above, mainly features of the preamplifier stage are low noise, low power consumption, high gain and offset rejection with a frequency band of  $\sim 10 Hz$ -10 kHz.

Low power consumption requirement derives from the necessity of fully implanting large quantities of them in a small area. Since power dissipation should not exceed a few hundreds mW, for a 1000-electrode system, this results in a maximum power dissipation much less than 1mW per amplifier.

With Harrison's feedback network [4] (Fig. 2.2), the preamplifier transfer function is:

$$A_{VM}(s) = \frac{A_{V0}^{OTA}(sC_1R)}{(A_{V0}^{OTA}+1)(sC_2R+1) + sC_1R}$$

where  $A_{V0}^{OTA}$  is the OTA open loop gain.

If  $A_{V0}^{OTA}$  is assumed infinite, the mid band gain tends to the ratio  $C_1/C_2$ . The amplifier has been designed for a gain of 100, setting  $C_1$  to 20pF and  $C_2$  to 200fF. Both  $C_1$  and  $C_2$  were designed as poly-poly capacitors for maximum linearity.

Figure 2.2: Schematic of Harrison's bandpass preamplifier

The low cutoff frequency  $f_L$  is given by  $1/(2\pi RC_2)$ , while the high one is  $f_H = g_m^{OTA}/(2\pi A_V C_L)$ . To set  $f_L \approx 10 Hz$ , the product  $RC_2$  must be  $\approx 10^{-2}$ . This means that, using a large resistor (than a MOS-bipolar pseudoresistor), capacitor can be small enough to occupy a not too large silicon area.

Moreover, in the case where  $C_1$ ,  $C_L \gg C_2$  the bandwidth is approximately  $g_m/(A_{VM}C_L)$ , where  $g_m$  is the transconductance of the OTA and  $C_L$  is 13pF compensation capacitor.

#### 2.1.1 MOS-bipolar pseudoresistor

The peculiarity of this circuit consists in the use of a MOS-bipolar pseudoresistor element to amplify low frequency signals down to the mHz range while rejecting DC offsets. With negative  $V_{GS}$ , each device functions as a diode-connected pMOS

Figure 2.3: MOS-bipolar pseudoresistor

transistor, while with positive  $V_{GS}$ , the parasitic source-well-drain p-n-p bipolar junction transistor (BJT) is activated, and the device acts as a diode-connected BJT (Fig. 2.4).

For small voltages across this device, its incremental resistance  $r_{inc}$  is extremely high: for  $|V_{GS}| < 0.2V$ ,  $\frac{dV}{dI} > 10^{11}\Omega$  has been measured. A large change in the input

Figure 2.4: MOS-bipolar pseudoresistor working

causes a large voltage across the MOS-bipolar elements, reducing their incremental resistance and giving fast settling time.

Another design uses diode-connected nMOS transistors as pseudoresistors to achieve an equivalent resistance of grater than  $10^{10}\Omega$ , though it is not stated whether a body-source connection is used to create a diode-connected bipolar transistor.

Figure 2.5: I-V relationship and incremental resistance of single MOS-bipolar element

Using two MOS-bipolar devices in series it is possible to reduce distortion for large output signals.

#### 2.1.2 Low-noise, high gain and low-power OTA design

As told before, the ideal gain of preamplifier is:

$$A_{VM}^{ideal} = \lim_{A_{V0}^{OTA} \to +\infty} A_{VM} = \lim_{A_{V0}^{OTA} \to +\infty} \frac{A_{V0}^{OTA}(sC_1R)}{(A_{V0}^{OTA} + 1)(sC_2R + 1) + sC_1R} = \frac{C_1}{C_2} \quad (2.1)$$

Actually  $A_{VM}$  differs from the ideal value  $A_{VM}^{ideal}$  because of the finite value of  $A_{V0}^{OTA}$ . The error on the total gain is:

$$err(A_{VM}) = \frac{A_{VM}^{ideal} - A_{VM}}{A_{VM}^{ideal}}$$

(2.2)

In the bandwith of interest  $R \approx 10^{12} \Omega$ , than Equation 2.1 can be rewritten as:

$$A_{VM} \approx \frac{A_{V0}^{OTA} C_1}{(A_{V0}^{OTA} + 1)C_2 + C_1}$$

(2.3)

Than, using definition 2.2, the gain error results:

$$err(A_{VM}) \approx \frac{\frac{A_{V0}^{OTA}C_1}{(A_{V0}^{OTA}+1)C_2+C_1} - \frac{C_1}{C_2}}{\frac{C_1}{C_2}} = \frac{A_{V0}^{OTA}C_2}{(A_{V0}^{OTA}+1)C_2+C_1} - 1$$

(2.4)

In table 2.1 errors for different values of  $A_{VM}^{OTA}$  are reported (using  $C_1 = 20pF$  and  $C_2 = 200fF$ ).

| $A_{V0}^{OTA}[V/V]$ | $err(A_{VM})[\%]$ |

|---------------------|-------------------|

| $10^{2}$            | -50               |

| $10^{3}$            | -9.1              |

| $10^{4}$            | -0.99             |

| $10^{5}$            | -0.10             |

Table 2.1: Influence of  $A_{VM}^{OTA}$  on the  $A_{VM}$  precision

The typical extracellular neural background noise is of about 5-10  $\mu Vrms$  over the bandwidth, therefore, in order to avoid increasing the noise floor, the preamplifier *rms* noise must be at least a factor two smaller. It means that in the choice of OTA architecture the noise is the most critical parameter since a gain of 10<sup>4</sup> is easily achieved by most CMOS OTA architectures [4].

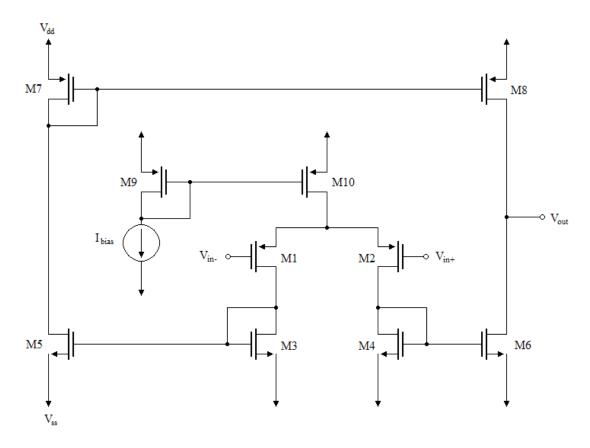

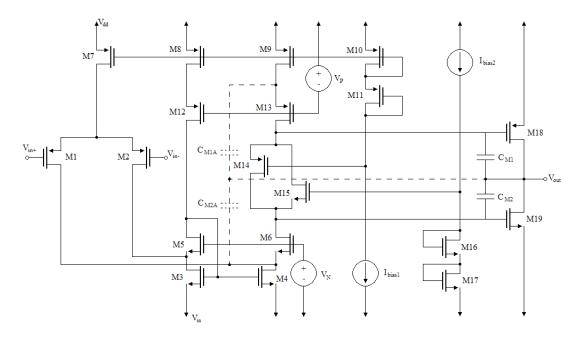

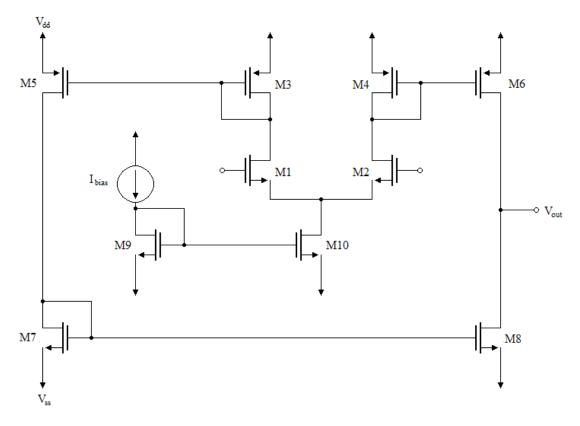

As a solution, symmetrical OTA has been chosen (Fig 2.6) [5].

In Fig. 2.6 a pMOS input stage configuration is shown. In M10 flows current mirrored by M9. This current symmetrically splits in M1 and M2 and is mirrored by M3 and M4 respectively in M5 and M6. Finally the same current of M6 is mirrored in M8 by M7.

Equation 2.5 reports the total input referred noise:

$$V_{irn}^2 = 2V_{n1}^2 + \frac{2V_{n3}^2 + 2V_{n6}^2 + 2V_{n8}^2}{g_{m1}^2 r_{0,1}^2}$$

(2.5)

where transistors M1-M2, M3-M4, M5-M6 and M7-M8 are matched in pairs. The contribution given by thermal noise is:

$$V_{irn,th}^2 = \left[\frac{16k_bT}{3g_{m1}}\left(1 + 2\frac{g_{m3}}{g_{m1}} + \frac{g_{m7}}{g_{m1}}\right)\right]\Delta f$$

(2.6)

Figure 2.6: Schematic of OTA used in Harrison preamplifier

Sizing devices such that  $g_{m3}$ ,  $g_{m7} \ll g_{m1}$  the noise contributions of devices M3-M8 can be minimized. This can be accomplished by making  $(W/L)_3$ ,  $(W/L)_7 \ll (W/L)_1$ . Moreover, to minimize flicker noise, M1 and M2 are set with a high (W/L) ratio.

Nevertheless,  $g_{m3}$  and  $g_{m7}$  cannot be arbitrarily decreased without danger of instability. If the total capacitance seen by the gate of M3 (or M4) is  $C_3$ , than the OTA has two poles at  $\omega_p = g_{m3}/C_3$ . Similarly there is a pole at  $g_{m7}/C_7$  caused by the pMOS mirror. To ensure stability, these pole frequencies must be several times greater than the dominant pole  $\omega_D = g_{m1}C_L$ . As a trade off,  $C_L$  cannot be too large, area limitations and bandwith requirements have to be considered.

On the other hand, the input referred noise of the bioamplifier can be related to the OTA input referred noise by:

$$V_{irn,amp}^2 = \left(\frac{C_1 + C_2 + C_{in}}{C_1}\right)V_{irn}^2 \tag{2.7}$$

where  $C_{in}$  is the OTA input capacitance. Than, as M1 and M2 are made larger,  $C_{in}$  increases and consequently the noise becomes higher.

In table 2.2 are reported the values which were chosen after some simulations.

The OTA open loop gain is given by the product of the OTA transconductance  $(g_m^{OTA})$  with the output resistance  $(R_{out})$ :

$$g_m^{OTA} = \frac{g_{m1}}{g_{m3}} g_{m6} \tag{2.8}$$

| MOS     | W/L                  |

|---------|----------------------|

| M1, M2  | $1000 \mu m/2 \mu m$ |

| M3, M4  | $2\mu m/20\mu m$     |

| M5, M6  | $2\mu m/20\mu m$     |

| M7, M8  | $6\mu m/20\mu m$     |

| M9, M10 | $20\mu m/20\mu m$    |

Table 2.2: OTA's MOS dimensions

$$R_{out} = \frac{1}{g_{ds6} + g_{ds8}} \tag{2.9}$$

$$A_v^{OTA} = g_m^{OTA} R_{out} \tag{2.10}$$

#### 2.2 Filter stage

[1] Harrison preamplifier is followed by a two filter stage which amplifies the signal once again in the bandwidth of interest and increases the slope of the transfer function after the cut off frequency, producing a clearer cut of the signal components with a frequency greater than the one desired.

The input signal of the filter comes from the preamplifier. Since the maximum amplitude of peak-to-peak neural signal is nearly  $V_{pp} = 150 \mu V$  and the preamplifier gain is  $\approx 100$ , the maximum peak-to-peak value of filter input signal results of about 15mV. This means that the filter stage have to amplify without distortions signals smaller than 15mV, this results in a large output swing requirement.

Moreover, the filter stage should exhibit a low pass behavior with a cut off frequency nearly of 10kHz, with the possibility of externally tuning this value.

It has been decided to implement the filter stage as two single pole OP-AMP filters in non inverting configuration in cascade.

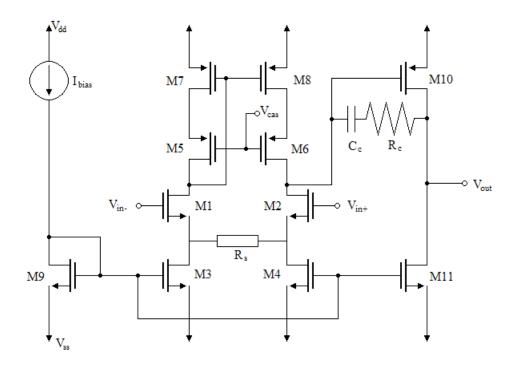

In Fig. 2.7 is shown the OP-AMP architecture chosen for the filter.

It is a two stage differential input single ended amplifier with Miller compensation.

#### 2.2.1 First OP-AMP stage

The first stage is composed by a differential pair with NMOS input transistors (M1, M2) with degeneration resistance  $R_s$ , a cascoded current mirror load (M5, M6, M7, M8) and current source transistors (M3, M4) which mirror the  $I_{bias}$  current. The use of wide swing cascode increases the output resistance, also reducing the systematic mismatch between the currents that flow in the differential branches. Cascode transistors are biased with  $V_{cas}$ , which has to satisfy the following conditions in order to keep M5 and M6 in saturation region:

Figure 2.7: Schematic of filter OP-AMP

$$V_{dd} - V_{DS8sat} > V_{cas} + V_{GS6}$$

$$V_{cas} + V_{GS6} - V_{DS6sat} > V_{out1}^{DC} + S_{swing}$$

$$\Rightarrow V_{out1}^{DC} + S_{swing} - V_{GS6} + V_{DS6sat} < V_{cas} < V_{dd} - V_{DS8sat} - V_{GS6}$$

(2.11)

where  $V_{out1}^{DC}$  and  $S_{swing}$  are the DC voltage level and the signal swing at the output of the first stage.

After some simulations  $V_{cas} = 2.0V$  was chosen.output buffer

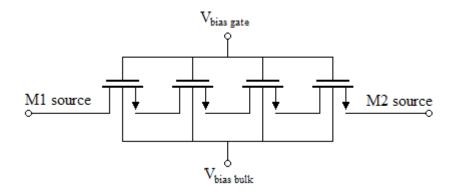

The source degeneration resistance  $R_s$  is composed by four NMOS transistors connected in series as shown in Fig. 2.8

Figure 2.8: Source degeneration resistance scheme

All transistor gates are biased by  $V_{biasgate}$ , with their bulks connected to the negative supply.

The value of  $R_s$  is given by the sum of the resistance of each transistor:

$$R_s = \sum_{transistor M_i} \frac{1}{g_{ds_i}} \approx 1M\Omega \tag{2.12}$$

By changing the value of  $R_s$  it is possible to tune the cut off frequency of the filter stage. This could be desirable to serve different applications once the circuit has been fabricated. Decreasing the value of  $V_{biasgate}$  the channel conductance  $g_{ds}$  of the four transistors that compose the degeneration resistance is decreased, leading to higher values of  $R_s$  and lower values of cut off frequency.

Load resistance value is given by the cascode equivalent resistance:

$$R_d = (g_{m6} + g_{mb6})r_{o8}r_{o6} + r_{o8} + r_{o6} \approx 500M\Omega$$

(2.13)

finally, first stage gain is:

$$A_{V1} = \frac{g_{m2}r_{o2}R_d}{R_d + \frac{R_s}{2} + r_{o2} + (g_{m2} + g_{mb2})\frac{R_s}{2}r_{o2}} \approx 500$$

(2.14)

#### 2.2.2 Second OP-AMP stage

The second stage is a PMOS (M10) common source with NMOS (M11) active load, which gain is given by:

$$A_{V2} = g_{m10}(r_{o10}//r_{o11}) = g_{m10} \frac{1}{g_{ds10} + g_{ds11}} \approx 500$$

(2.15)

than total open loop gain results  $\approx 2500$ .

#### 2.2.3 Miller compensation

Miller compensation has the role to increase the phase margin through  $C_c = 5pF$  capacitance regulating the unity gain frequency:

$$G_{meq} = \frac{g_{m2}}{1 + (g_{m2} + g_{mb2})\frac{R_s}{2}}$$

(2.16)

$$f_{UG} = \frac{G_{meq}}{2\pi C_c} \tag{2.17}$$

Besides the  $R_c$  compensation resistance regulates the transfer function zero:

$$z_1 = -\frac{1}{R_c C_c - C_c / g_{m10}} \tag{2.18}$$

To avoid instability issues, the zero must be pushed to  $\infty$ , than:

$$R_c = \frac{1}{g_{m10}}$$

(2.19)

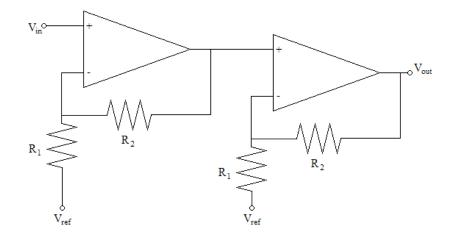

#### 2.2.4 Two filters in cascade

Figure 2.9: Schematic of filter stage

Each OP-AMP is used in non inverting condition and the closed loop gain is:

$$A_V^{closedloop} = \frac{A_V^{openloop}}{1 + A_V^{openloop} \frac{R_1}{R_1 + R_2}}$$

(2.20)

$$\lim_{\substack{A_V^{openloop} \to \infty}} A_V^{closedloop} = 1 + \frac{R_2}{R_1}$$

(2.21)

In order to haw a total gain of 25, each filter must have a gain of 5 and  $R_2$  must be four time greater than  $R_1$ .

$R_1 = 100k\Omega$  and  $R_2 = 400k\Omega$  have been chosen.

#### 2.2.5 Channel-to-channel mismatch

To work correctly, the circuit has to balance the current in the branches of the differential pair creating an output offset:

$$G_{meq} = \frac{\delta I_{branch}}{\delta V_{out1}} \Rightarrow \Delta I_{branch} = \Delta V_{out1} G_{meq}$$

(2.22)

Mismatch between circuit components affects the circuit DC working point and the current symmetry in the branches. For example, a mismatch between mirror transistors leads to different mirrored current values in the different branches of the circuit, a mismatch in the input transistor is responsible for the broken symmetry if the differential pair, and a mismatch in the feedback resistors causes a variation of the OP-AMP closed loop gain.

In a multichannel recording system, there may be differences between the different channel DC output levels because of transistor mismatches, and, if the DC output level is too far from the reference value, the output linear range decreases.

To decrease the channel-to-channel difference mismatches have to be reduced. With this target following solutions have been adopted during OP-AMP design:

- increase the length of PMOS load transistors in order to increase the cascode resistance and consequently the gain of the first stage: with high gain value, the effects of mismatch are compensated with little variation of the output DC level.

- increasing the length of NMOS current source transistors to reduce the mismatch effects in the current mirrored in the two branches of differential pair

- increasing length of NMOS input transistors to reduce mismatch on  $g_m$  values.

- splitting the transistors gates, making more accurate the transistors size in the chip fabrication process.

Increasing  $G_{meq}$  means to reduce the output offset. Nevertheless, to hold steady the unity gain frequency, the compensation capacitance has to be increased. This involves the use of a larger silicon area.

To avoid this, a 5pF capacitance and an offset compensation system have been used.

Figure 2.10: Filter stage offset compensation system

In Fig 2.10 a scheme of a possible offset compensation system is shown. The DC voltages  $V_{offset}$  represent the offset o the circuit, while  $V_{compensation}$  is a DC reference voltage which could vary the DC output level of the filter stage changing the DC level of the negative input of the first OP-AMP.

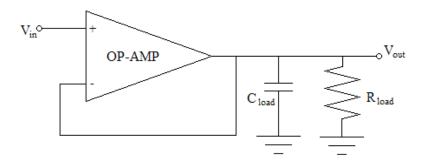

#### 2.3 Output buffer

[1] The role of the unity gain output buffer is to interface the AFE to the recording hardware.

After the filter stage the gain reached is  $\approx 2500$ , which is sufficiently high for our purpose, so the output buffer is not required to amplify further on.

The maximum input signal of the filter stage is 15mV large, this means that the maximum signal in input to the buffer reaches  $15mV \cdot 25V/V = 375mV$ . This

implies that the buffer linear output range must be at least of 375mV.

Of course it is also required a cut off frequency higher than 10kHz.

For the implementation of the output buffer a standard configuration in class AB with two stages and Miller compensation has been chosen (Fig 2.11).

Figure 2.11: Schematic of output buffer OP-AMP

The output buffer is connected to the oscilloscope with a load resistance of  $50\Omega$  and a load capacitance of 20pF (Fig 2.12).

Figure 2.12: Output buffer scheme

If a supply voltage between 0V and 3.3V is used, the DC output level is  $\approx 1.65V$ , this means that a current of 33mA will flow in the load resistance. To avoid this large current flow at the output, there are two possible solutions:

- using a high load resistance of about  $1M\Omega$  in order to have a current flow of few  $\mu A$

- using a dual power supply with  $\pm 1.65V$  in order to have a DC output level of  $\approx V$

# Chapter 3 Layout and packaging

[6] In the last 20 years analog CMOS circuits have evolved towards increasingly small dimensions. While device scaling has enhanced transistors speed, it has also led to unwanted interactions between different sections of integrated circuit as well as nonidealities in the layout and packaging, limiting speed and precision of such systems and influencing heavily their functioning.

#### 3.1 Design rules

To prevent such troubles some design rules have been set concerning *n*-well and polysilicon geometries,  $n^+$  and  $p^-$  implants, interlayer contact windows and metal layers.

#### 3.1.1 Minimum allowable rules

These are a set of rules which ensures the proper fabrication of devices despite tolerances in each step of processing.

#### Minimum width

This value is set both by lithography and processing capabilities of the technology. In general, the thicker a layer (the smaller technology), the greater its minimum allowable width.

#### Minimum spacing

To prevent geometries built on the same or on different masks to be shorted, they have to be separated by a minimum space.

#### Minimum enclosure

Each active area, such as *n*-wells and  $p^+$  implants, must be surrounded by a proper implant geometry with enough margin to guarantee that the device is contained by these geometries despite tolerances.

#### Minimum extension

Some geometries must extend beyond the edge of others by a minimum value. This is the case of the gate polysilicon beyond the active area to ensure proper transistor action at the edge.

#### 3.1.2 Maximum allowable rules

Some maximum allowable rules have been dictated too, e.g. a major metal width for longest wires to prevent *litoff* problems or rules related to the *antenna effect* described in next section.

#### Antenna effect

The antenna effect is an effect that can potentially cause reliability problems during the manufacture of MOS integrated circuits. Since the gate dielectric is so thin, only a few molecules thick, a big worry is breakdown of the this layer. This can happen if the net somehow acquires a voltage higher than the normal operating voltage of the chip. During the construction of the chip, the oxide may not be protected by any diffusion.

Suppose the gate of a small MOSFET is tied to a *metal* 1 interconnect having a large area (Fig 3.1(a)).

Figure 3.1: (a) Layout susceptible to antenna effect. (b) Discontinuity in *metal 1* layer to avoid antenna effect

During the etching of *metal 1*, the metal acts as an "antenna" collecting ions and rising potential. It is than possible than gate voltage of the MOS device increases so much that the gate oxide breaks down irreversibly during fabrication.

The antenna effect may occur for any large piece of conductive material tied to the gate of a transistor including polysilicon itself. For that reason such geometry areas are limited by design rules. Antenna rules are normally expressed as an allowable ratio of metal area to gate area. If large areas can't be avoided, than a discontinuity is created (Fig. 3.1(b)) so that when *metal 1* is being etched the large area is not connected to the gate.

#### **3.2** Analog layout techniques

While design rules aim to guarantee the functioning of devices in IC, these techniques are meant to minimize effects such as crosstalks, mismatches, noise, etc.

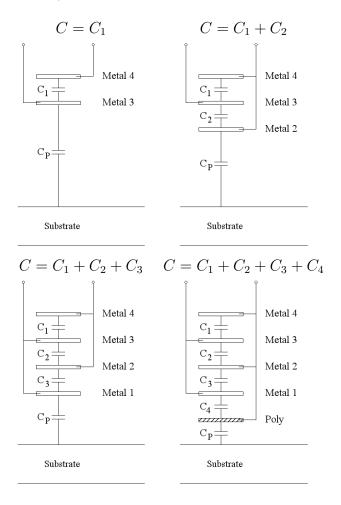

#### 3.2.1 Multifinger transistors

While for wide transistor a folded structure, as shown in Fig. 3.2(a), can be used in order to minimize both the source/drain junction area and the gate resistance, for very wide devices such a solution may prove inadequate. That's the reason for using a multiple fingers structure (Fig. 3.2(b)).

Moreover, in low noise applications, the gate resistance must be one-fifth or one-tenth of  $1/g_m$ .

Figure 3.2: (a) Simple folded transistor. (b) Multifinger structure of a MOSFET

Decomposing the transistor into more parallel fingers takes to the trade-off between reducing the gate resistance (i.e. minimizing the gate resistance noise) and increasing the capacitance associated with the perimeter of source/drain areas (i.e. degrading the circuit high-frequency performance).

An example is shown in Fig. 3.3.

With three fingers the total perimeter of source/drain area is equal to 2(2E + 2W/3) = 4E + 4W/3, whereas in five fingers structure it is given by 3(2E + 2W/5) = 6E + 6W/5. In general, for an unspecific number of fingers N, the source/drain perimeter capacitance is:

$$C_P = \frac{N+1}{2} (2E + \frac{2W}{N}) C_u = [(N+1)E + \frac{N+1}{N}W] C_u$$

(3.1)

Where  $C_u$  is the capacitance per perimeter unit.

Therefore the number of fingers multiplied by E must by much less than W as to minimize the source/drain perimeter capacitance contribution.

Figure 3.3: Layout of a transistor using (a) three fingers, (b) five fingers

A compromise may be reached by contacting the gate on both ends to reduce its resistance without increasing the number of fingers.

Figure 3.4: Layout of a transistor with many fingers

For transistors having a large number of fingers, the structure may modified as shown in Fig. 3.4 avoiding long uncomfortable geometries in the layout of overall circuit.

#### 3.2.2 Symmetry

Symmetry is a very important item especially in the design of differential circuits, in which asymmetries introduce input referred offsets limiting the minimum signal level that can be detected. A symmetric layout also yields to the suppression of common-mode noise and even-order nonlinearity.

For example, in the design of a pair (Fig. 3.5(a)) disparate solutions may be adopted. If the two transistors are laid out with different orientations as in Fig 3.5(b), the matching greatly suffers because of the variable behavior along different axes of many steps in lithography and wafer processing. Thus some more adequate solutions are provided by geometries in Fig. 3.5(c) and (d)

Figure 3.5: (a) Differential pair. (b) An example of an asymmetric layout and (c), (d) two symmetric layouts of the differential pair

Another issue that must be taken into account is the gate shadowing effect. Since during source/drain implantation the wafer is tilted by about 7° to avoid channeling, the gate polysilicon shadows a narrow strip in the source or drain region which receives less implantation than the other, creating a small asymmetry between source and drain side diffusions (Fig. 3.6).

Figure 3.6: Gate shadowing effect

In order to reduce effects due to this kind of asymmetries, dummy structures are used (Fig. 3.7). They reproduce the same environment around the working devices.

Furthermore, if the geometry to be laid out requires a large area occupation (that's the case of large transistors composing a differential pair), appreciable mismatches due to gradients along the axes may arise. To reduce the error, a "commoncentroid" configuration is used limiting the first order effects of gradients along both

Figure 3.7: Addition of dummy devices to improve symmetry

axes (Fig. 3.8). However, the routing of interconnects in this kind of layouts is quite difficult, often leading to systematic asymmetries and to the introduction of parasitic capacitances between wires and from wires to ground.

Figure 3.8: (a) Effect of gradient on a differential pair. (b) Common centroid layout

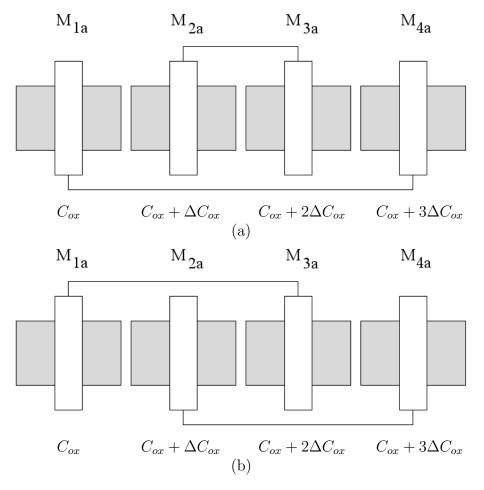

Another solution to this issue which is not affected by routing difficulties is provided by the one-dimensional cross coupling. Let's consider Fig. 3.9 and let us assume that, for example, the gate oxide capacitance varies by  $\Delta C_{ox}$  from each half transistor to the next. In the first configuration it results:

$$I_{DS1a} + I_{DS4a} = \frac{1}{2} \mu_n (C_{ox} + C_{ox} + 3\Delta C_{ox}) \frac{W}{L} (V_{GS} - V_{th})^2$$

$$I_{DS2a} + I_{DS3a} = \frac{1}{2} \mu_n (C_{ox} + \Delta C_{ox} + C_{ox} + 2\Delta C_{ox}) \frac{W}{L} (V_{GS} - V_{th})^2$$

(3.2)

This configuration than cancels the effect of the gradient, while the same does not happens in the second configuration, where:

$$I_{DS1b} + I_{DS3b} = \frac{1}{2}\mu_n (C_{ox} + C_{ox} + 2\Delta C_{ox}) \frac{W}{L} (V_{GS} - V_{th})^2$$

$$I_{DS2b} + I_{DS4a} = \frac{1}{2}\mu_n (C_{ox} + \Delta C_{ox} + C_{ox} + 3\Delta C_{ox}) \frac{W}{L} (V_{GS} - V_{th})^2$$

(3.3)

Figure 3.9: One-dimensional cross coupling

#### 3.2.3 Reference distribution

In analog systems, the distribution across the chip of bandgap reference generators which bias the various building blocks gives rise to a number of issues.

Consider for example Fig. 3.10(a) where current  $I_{REF}$  is mirrored in current sources  $M_1$ - $M_n$  which bias the different building blocks. If the matching between  $I_1$ - $I_n$  is critical and if transistors  $M_1$ - $M_n$  are located far from  $M_{REF}$ , than the voltage drop along the ground line must be taken into account. to prevent such problems, the reference can be distributed in the current domain rather than in the voltage one, as shown in Fig. 3.10(b). the idea is to route the reference current in the neighborhood of he interested building block and to perform the mirroring locally.

This solution ameliorate the match between references, however further errors are introduced by the mismatch between  $I_{REF1}$  and  $I_{REF1}$  and between  $M_{REF1}$  and  $M_{REF1}$ .

Figure 3.10: (a) Distribution of a reference voltage for current mirror biasing. (b) Distribution of current to reduce the effect of interconnect resistance

Finally, the scaling of currents demands careful choice of device dimensions and layout. Since the transistor channel length is a poorly controlled quantity, due to the side diffusion of source/drain regions, to ensure the maximum match, the length of transistor must be equaland the current must be scaled by proper choice of widths.

#### 3.2.4 Passive devices

In this section problems related to the integration of resistors, capacitors and diodes are discussed. Main issues are area occupation, linearity, process variation, precision, etc.

#### Resistors

An important feature of integrated resistors is the sheet resistance  $R_{\Box}$ , which depends on temperature, expressed by the temperature coefficient, and process.

Polysilicon resistors using a silicide block are characterized by high linearity and low capacitance to the substrate. Since their linearity depends on their dimensions, applying symmetry rules described for MOS devices layout, it is possible to obtain resistors which exhibit relatively small mismatches.

In order to improve the matching, large value resistors are usually laid out as the parallel of shorter units, which structure is preferable to the serpentine topology because of the absence of corners (Fig. 3.11).

Figure 3.11: (a) Layout of large resistor. (b) Serpentine topology

The temperature coefficient varies with the doping type and level, typical values are  $+0.1\%/^{\circ}$ C and  $-0.1\%/^{\circ}$ C for  $p^{+}$  and  $n^{+}$  doping respectively. The sheet resistance variation with process is usually less than  $\pm 20\%$ .

In technologies lacking a silicide block mask, resistors may be implemented with *n*-well, source /drain  $p^- n^+$  material, silicided polysilicon or metal, with  $R_{\Box}$  decreasing in this order.

Typically, *n*-well resistors display a temperature coefficient of  $+(0.2 - 0.5)\%/^{\circ}$ C, while their sheet resistance is of about  $1k\Omega/\Box$ , but subject to large variations with process ( $\approx \pm 40\%$ ). Moreover, since, with the depth of several microns, *n*-well regions exhibit width dependent diffusion at the edges,  $R_{\Box}$  also decreases with the width of the resistor. However the most serious problem is given by the dependence of  $R_{\Box}$  upon *n*-well-substrate voltage difference, which causes non-linearity andpoor definition of resistor value.

The  $p^+$  and  $n^+$  source/drain regions exhibit a sheet resistance of  $3 - 5\Omega/\Box$ , thus they are suitable only for low value resistors. Despite they exhibit a higher linearity

with respect to *n*-well resistors, their variation with process may reach 50% and the junctions between these areas and the bulk introduces substantial capacitance and voltage dependence and their variation with process may reach 50%.

Silicided polysilicon has the same sheet resistance of  $p^+$  and  $n^+$  source/drain regions, but suffers from less capacitance to the substrate. These resistors are particularly suitable in applications in which the absolute value of  $R_{\Box}$  is not critical, since their variation with process is as high as 60% to 70%.

Its temperature coefficient varies between  $0.2\%/^{\circ}C$  and  $0.4\%/^{\circ}C$ .

Finally, a very low resistor value may be provided by a metal layer, which temperature coefficient for alluminium is  $0.3\%/^{\circ}$ C. However, if the width of the metal resistor is small, the match suffers.

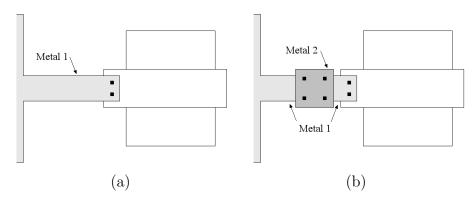

#### Capacitors

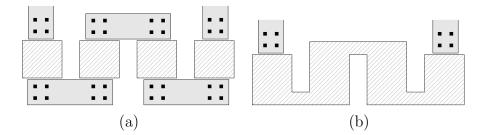

High density linear capacitors are made using polysilicon over diffusion, polysilicon over polysilicon or polysilicon over metal, with a layer of oxide between the two plates. The first structure is largely used owing to its simplicity, while others exhibit higher linearity. If it is not possible to use such structures, available conductive layers are used (Fig. 3.12).

Figure 3.12: Capacitors made using allowable conductive layers

The choice of the topology is driven by area constraint and by the ratio of the bottom-plate parasitic capacitance to the inter-plate one,  $C_P/C$ . The capacitance of consecutive metal layers is of  $35 - 40 a F/\mu m^2$ , while the one between *metal 1* and polysilicon is as high as  $60 a F/\mu m^2$ , leading to a higher density. Nonetheless, the ratio  $C_P/C$  increases from 0.2 - 0.25 for the structure in Fig. 3.12(a) to 0.5 in Fig. 3.12(d). Moreover, since the interlayer capacitance value is poorly controlled, these topologies may experience process variations as high as 20%, while the gate oxide capacitance is controlled by less than 5% error.

Besides, a MOS transistor with source and drain tied together can be used as a capacitance as well if the gate-source potential is sufficiently high to establish an inversion layer, but this voltage dependence limits the linearity of this structure.

As for MOS and resistor devices, capacitors used in high precision applications have to be laid out following the rules described, such as using dummy structures, avoiding gradients, etc. However capacitors are quite more sensitive to wiring parasitic capacitance due to interconnections.

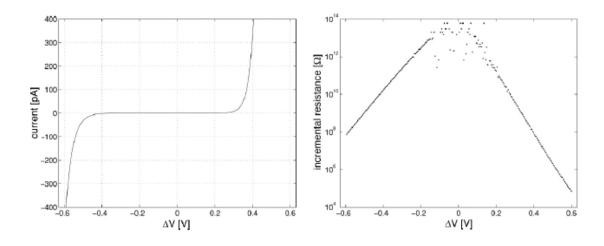

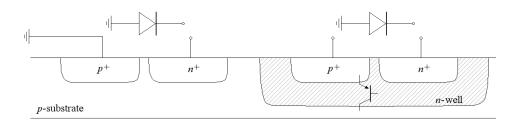

#### Diodes

As shown in Fig. 3.13, two types of p-n junctions can be fabricated, in the p-substrate or in a n-well. The former must be used in reversed bias, than is useful only as a varactor (voltage-dependent capacitor).

The second has some problems too if forward biased because of a parasitic bipolar pnp transistor composed by the  $p^+$  region, the *n*-well and the *p*-substrate. than this structure must not be viewed as a merely two-terminal floating diode.

Figure 3.13: Diodes in CMOS technology

### 3.2.5 Interconnects

Modern CMOS technology offers five metal layers. This introduces a number of parasitic capacitors between the different levels of metal and fringe capacitance of wires, which may degrade the speed of the circuit. Furthermore, the capacitance between the wires produces unwanted coupling of signals. In order to reduce crosstalk, two solutions can be adopted. The use of differential signals, which convert the coupling into common-mode disturbance. Otherwise sensitive signals can be shielded placing ground lines on the two sides of the signal line as exemplified in Fig. 3.14(a), forcing most of electric field lines emanating form the noisy lines to terminate on ground rather than on the signal, at the cost of more complex wiring and greater capacitance between the signal and ground. Note that this solutions proves more effective than just increasing the space between the different lines as in Fig. 3.14(b).

Figure 3.14: (a) Shielding sensitive signals by additional ground lines. (b) Allowing greater space between lines to reduce coupling

Another important issue is the resistance of interconnects. In low noise applications, thermal noise introduced by long interconnects may become remarkable. Moreover vias and contacts also suffer from high resistance.

The design of power and ground busses requires a particular attention too. In large chips, the voltage drop across the busses may become significant, affecting the functioning of different circuits supplied by them.Moreover, electromigration forces a minimum line width to ensure long term reliability. In order to reduce electromigration and busses resistance, it is possible to connect more metal layers in parallel.

#### **3.2.6** Pads and ESD protection

Once the chip has been fabricated, it needs to be interfaced with the external environment. At this scope, bond wires are connected to large pads placed on the perimeter of the chip and connected to the corresponding nodes in the circuit. The pad dimensions and structure are dictated by the reliability issues and by tolerances in the bonding process.

The area of the pads must be minimized in order to reduce the parasitic capacitance of the pad to the substrate and to minimize the total dye area.

Since a pad made of simply a square of top metal may suffer of lit-off issues, a structure composed by two topmost metal layers connected to each other by many small vias on the perimeter is used. Of course, this structure suffers from a larger capacitance to the substrate.

The interface between the IC and the external world also entails the problem of electrostatic discharge (ESD). This effect occurs when an external object having a high potential touches the connections of the circuit. Since the capacitance seen at each input or output is quite small, the ESD produces a large voltage, possibly damaging the devices fabricated on the chip. As a result of the ESD, two possible damages can affect MOS devices. First, the gate oxide may break down if the electric field exceeds roughly  $10^7 V/cm$  (e.g. 10V for an oxide  $100 \stackrel{A}{\circ}$  thick). Second, the source/drain junction diodes may melt if a large current in forward or reverse bias flows.

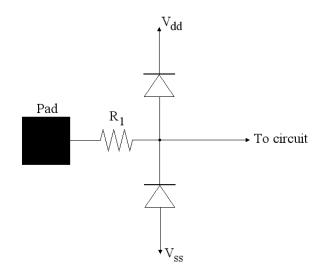

To alleviate this risk, CMOS circuits incorporate EDS protection devices, like the one illustrated in Fig. 3.15. Such device clamps the external discharge to ground or  $V_{dd}$  limiting the potential applied to the circuit. Resistor  $R_1$  is necessary to avoid damage to  $D_1$  and  $D_2$  due to large currents that would otherwise flow from the external source.

Figure 3.15: Simple EDS protection circuit

Obviously, the use of EDS protection circuits involves some problems. The devices introduce substantial capacitance from the node to ground and  $V_{dd}$ , degrading the speed and the matching of impedances at the input and output ports of the circuit. Since the devices must be large enough so as the chip sustains a large EDS without damage, their capacitance may reach several picofarads. Moreover,  $R_1$ introduces thermal noise which may become significant.

The capacitance introduced by ESD devices may couple noise on  $V_{dd}$  and ground lines to the input of the circuit, corrupting the signal.

If not properly designed, ESD structures may lead to latch-up in CMOS circuits when electrostatic discharge occurs.

## 3.3 Substrate coupling

Most modern CMOS use a heavily-doped  $p^+$  substrate to minimize latchup susceptibility. However, the low resistivity of the substrate created unwanted paths between various devices in the circuit, thereby corrupting sensitive signals. In order to reduce the effects of this phenomenon, called substrate coupling or substrate noise, the use of differential operation is suggested, making the circuit less sensitive to common-mode noise. Also, op amps using a PMOS differential input are preferred

because the well of the transistor can be tied to their common source, reducing the effect of substrate noise.

In circuits fabricated on lightly-doped substates, guard rings can be employed to isolate the sensitive sections. A guard ring may be simply a continuous ring made of substrate ties that surrounds the circuit, providing a low-impedance path to ground for the charge carriers produced in the substrate.

## 3.4 Packaging

Finally, integrated circuits are packaged. In simple dual-in-line package, the die is mounted in the center cavity and bonded to the pads on the perimeter of the cavity. These pads are the tip of each trace that ends in each package pin. Such a structure exhibits several parasitics, e.g. bond wire self-inductance, trace self-inductance, trace-to-ground capacitance, trace-to-trace mutual inductance and trace-to-trace capacitance.

While, owing to both circuit innovations and device scaling, the speed and accuracy of integrated circuits have steadily increased, the performance of packages, especially for low-cost applications, has not improved significantly. This limitation originates from the unscalable nature of packages and the environment in which they are used. As a result, packaging continue to limit the achievable performance of today's high-performance ICs.

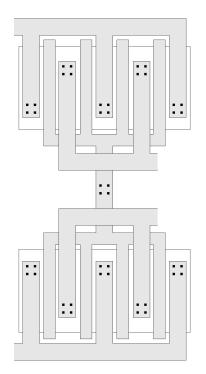

# Chapter 4 Preamplifier layout

Once the layout of the circuit was designed, a certain number of simulations were performed in order to ensure the right functioning.

Generally a first simulation of the layout in comparison with the result of the schematic simulation is performed. If both views give a consistent result, a second simulation is performed considering the parasitic capacitances of the extracted view. As a third step, worst cases and Montecarlo simulations are run.

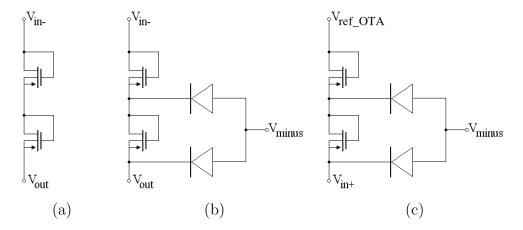

## 4.1 Parasitic diodes

The first block to simulate is the Harrison preamplifier, which is also the most critical one.

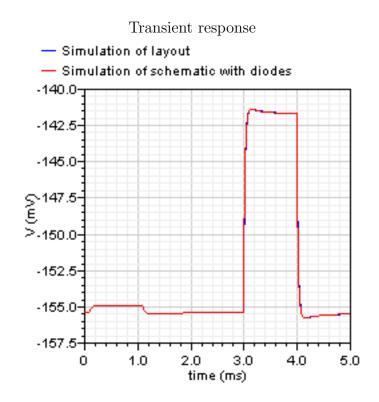

A first simulation is shown in Fig. 4.1. It was performed biasing the circuit between -1.65V and 1.65V, than the output DC voltage is supposed to adjust at 0V. However the result highlights the presence of a noteworthy output offset (-155.458mV), together with an instability in the transient analysis.

Looking at the extracted view, these effects seem to be due to the presence of parasitic *n*-well-*p*-substrate diodes in the feedback network MOS-bipolar pseudore-sistors (Fig. 4.2).

In fact, introducing the parasitic diodes in the MOS-bipolar pseudoresistors and simulating the schematic, the result obtained is the same as the previous (Fig. 4.3).

To study this phenomenon, the schematic was simulated with the parasite diodes first only on the feedback pseudoresistor and than only on the other.

The first simulation (Fig. 4.4(a)) gave a great positive output offset of  $\approx 380 mV$  and transient instability.

On the other hand, the second simulation (Fig. 4.4(b)) resulted in a negative output offset of  $\approx -530mV$ , without any instability effect. This means that the instability is due to the diodes on the feedback pseudoresistor. The total output offset agrees with the partial ones (380mV - 530mV = -150mV) and is the consequence of an asymmetry in the OTA's input transistors caused by the diodes.

As a test, we tried to turn the pseudoresistor at the positive input as it was in [4]. A negative output offset of  $\approx -380mV$  was found, which cancels out the one found in the first simulation. Than in this configuration the problem of the offset is solved, probably thanks to a higher symmetry, since both OTA's inputs see the gate

Transient response

Figure 4.1: Harrison preamplifier layout transient simulation

Figure 4.2: (a) Ideal scheme of MOS-bipolar pseudoresistor. (b), (c) Presence of parasitic n-well diodes in the feedback network MOS-bipolar pseudoresistors

Figure 4.3: Introduction of parasitic diodes in the schematic transient simulation

of the MOS-bipolar pseudoresistor, while in configuration 4.4(b) there's a current flowing through the diode in the positive input. This current throws off balance the inputs, than the OTA finds a new equilibrium introducing an output offset.

Figure 4.4: Simulation of schematic with parasitic diodes on the feedback pseudoresistor (a) and on the pseudoresistor at the positive input (b)

Figure 4.5: Simulation with reversed pseudoresistor

Reducing the output offset, also the stability improves. To understand why, let's consider the model of the feedback MOS-bipolar pseudoresistor depicted in Fig. 4.6:

Figure 4.6: feedback MOS-bipolar pseudoresistor model

where  $V_{in-}$  is the DC tension level present in the circuit on the negative input, and  $V_{out}$  reproduces the output of the preamplifier when an input signal is applied.