Università degli Studi di Torino Facoltà di Scienze M.F.N. Corso di Laurea in Fisica

Tesi di laurea

# Analysis and Design of a Fast Binary Front-End Chip for the COMPASS Experiment at CERN

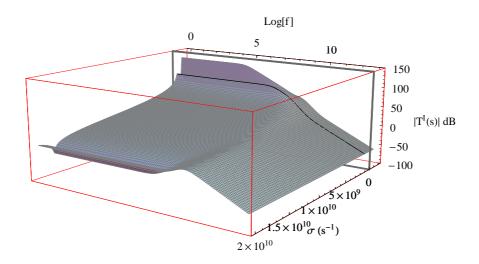

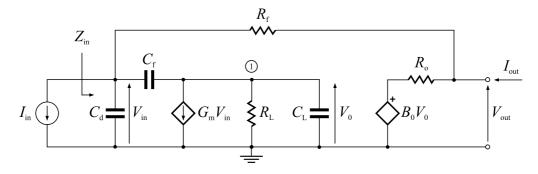

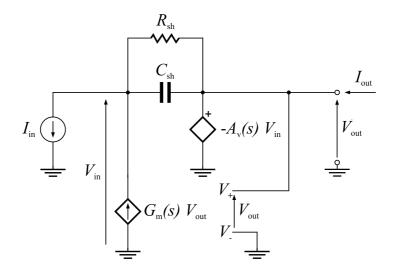

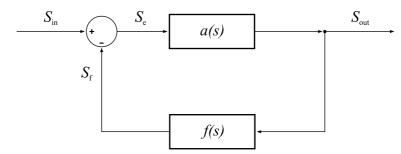

Relatore: dott. Angelo Rivetti Co-relatore: dr. ing. Antonino Grasso

Candidato: Paolo Delaurenti

Anno accademico 2005-2006

# Contents

| Preface  |                                                    |                  |                                                |      |  |  |  |  |  |  |  |

|----------|----------------------------------------------------|------------------|------------------------------------------------|------|--|--|--|--|--|--|--|

| 1        | Introduction                                       |                  |                                                |      |  |  |  |  |  |  |  |

|          | 1.1                                                | The C            | COMPASS Experiment                             | . 1  |  |  |  |  |  |  |  |

|          |                                                    | 1.1.1            | The COMPASS Spectrometer                       | . 2  |  |  |  |  |  |  |  |

|          |                                                    | 1.1.2            | The COMPASS RICH Detectors                     | . 4  |  |  |  |  |  |  |  |

|          | 1.2                                                | Chere            | nkov Radiation                                 | . 6  |  |  |  |  |  |  |  |

|          | 1.3                                                |                  |                                                |      |  |  |  |  |  |  |  |

|          |                                                    | 1.3.1            | Channel Photomultipliers                       | . 11 |  |  |  |  |  |  |  |

|          | 1.4                                                | Front-           | End Electronics for the COMPASS RICH Detectors | 12   |  |  |  |  |  |  |  |

|          |                                                    | 1.4.1            | The MAD                                        | . 12 |  |  |  |  |  |  |  |

|          |                                                    | 1.4.2            | The CMAD                                       | . 13 |  |  |  |  |  |  |  |

| <b>2</b> | The Basics of Front-End Circuits                   |                  |                                                |      |  |  |  |  |  |  |  |

|          | 2.1                                                | First S          | Stage Behavior                                 | 15   |  |  |  |  |  |  |  |

|          |                                                    | 2.1.1            | Collecting Charge                              | 15   |  |  |  |  |  |  |  |

|          |                                                    | 2.1.2            | Resetting Device                               | . 18 |  |  |  |  |  |  |  |

|          | 2.2                                                | The Second Stage |                                                |      |  |  |  |  |  |  |  |

|          | 2.3                                                | The F            | ull Circuit                                    | . 22 |  |  |  |  |  |  |  |

| 3        | Modelling and Analysis of the CMAD Architecture 25 |                  |                                                |      |  |  |  |  |  |  |  |

|          | 3.1                                                | First S          | Stage Analysis                                 | 25   |  |  |  |  |  |  |  |

|          |                                                    | 3.1.1            | The CSA Model and Behavior                     | 25   |  |  |  |  |  |  |  |

|          |                                                    | 3.1.2            | Resetting Device                               | . 28 |  |  |  |  |  |  |  |

|          |                                                    | 3.1.3            | Pole Splitting                                 | . 34 |  |  |  |  |  |  |  |

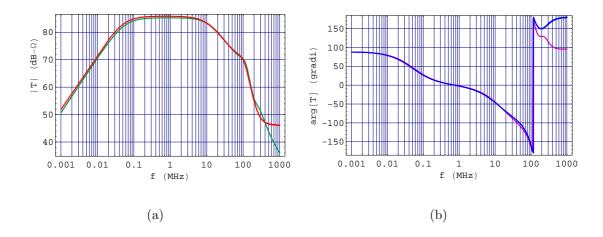

|          |                                                    | 3.1.4            | Frequency Analysis of the First Stage          | 38   |  |  |  |  |  |  |  |

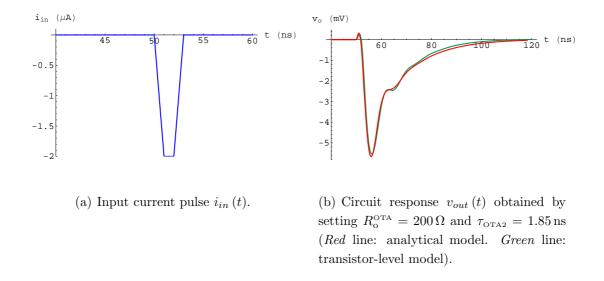

|          |                                                    | 3.1.5            | Pulse Response                                 |      |  |  |  |  |  |  |  |

#### CONTENTS

|          |                                                    | 3.1.6                                 | The Actual Circuit and the Parameter Estimate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 54  |  |  |  |

|----------|----------------------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

|          | 3.2                                                | Second Stage Analysis                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |  |  |  |

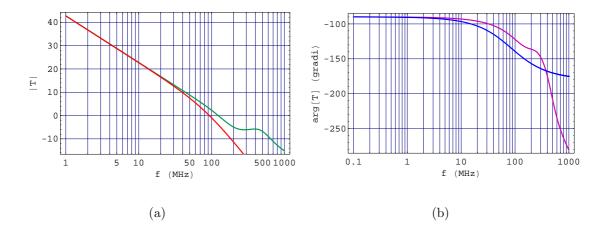

|          |                                                    | 3.2.1                                 | Frequency Analysis of the Second Stage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 58  |  |  |  |

|          |                                                    | 3.2.2                                 | Pulse Response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 65  |  |  |  |

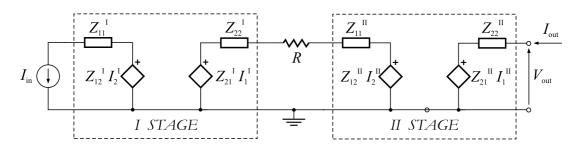

|          | 3.3                                                | Analysis of the Complete Amplifier    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |  |  |  |

|          |                                                    | 3.3.1                                 | Two-Port Representation of the First Stage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 75  |  |  |  |

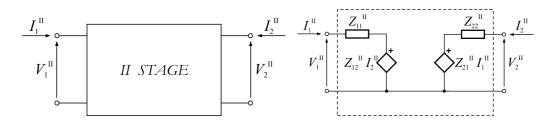

|          |                                                    | 3.3.2                                 | Two-Port Representation of the Second Stage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 76  |  |  |  |

|          |                                                    | 3.3.3                                 | Two-Port Representation of the Full Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 77  |  |  |  |

|          |                                                    | 3.3.4                                 | Frequency Analysis of the Full Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 80  |  |  |  |

|          |                                                    | 3.3.5                                 | Pulse Response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 80  |  |  |  |

| 4        | Mo                                                 | delling                               | g the Non-Linear Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 87  |  |  |  |

|          | 4.1                                                | Analy                                 | sis of the Full Circuit in the Time Domain $\ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 87  |  |  |  |

|          |                                                    | 4.1.1                                 | Time Domain Analysis of the Circuit without the Buffer $\ . \ .$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 87  |  |  |  |

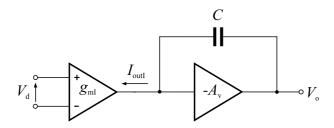

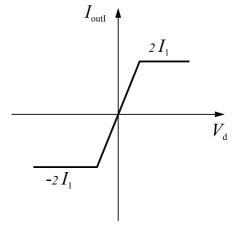

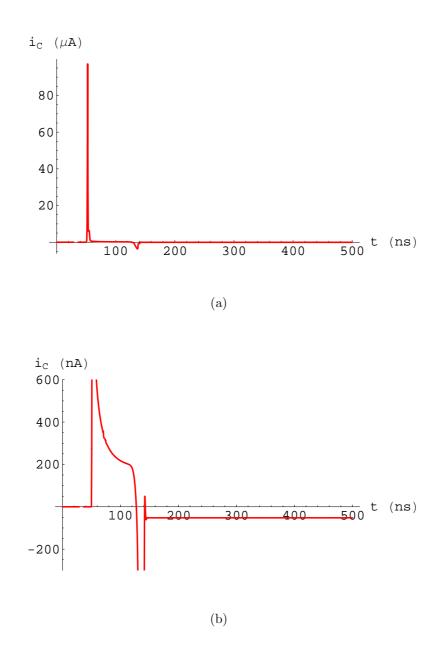

|          |                                                    | 4.1.2                                 | Modelling the Non-Linear Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 88  |  |  |  |

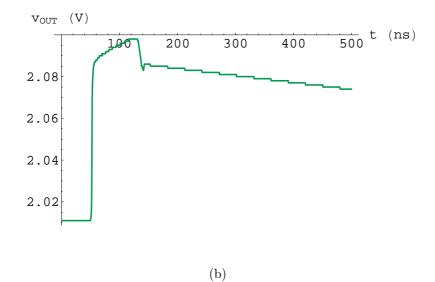

|          |                                                    | 4.1.3                                 | Time Domain Analysis of the Circuit with the Buffer $\ldots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 92  |  |  |  |

|          | 4.2                                                | outer Simulations of the Full Circuit | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |  |  |  |

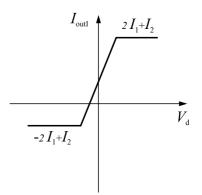

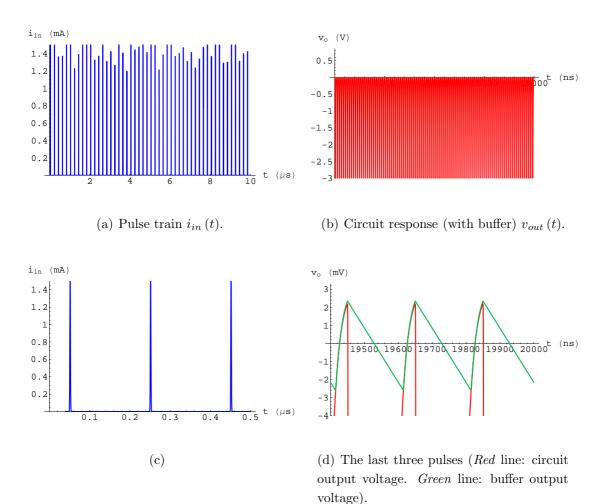

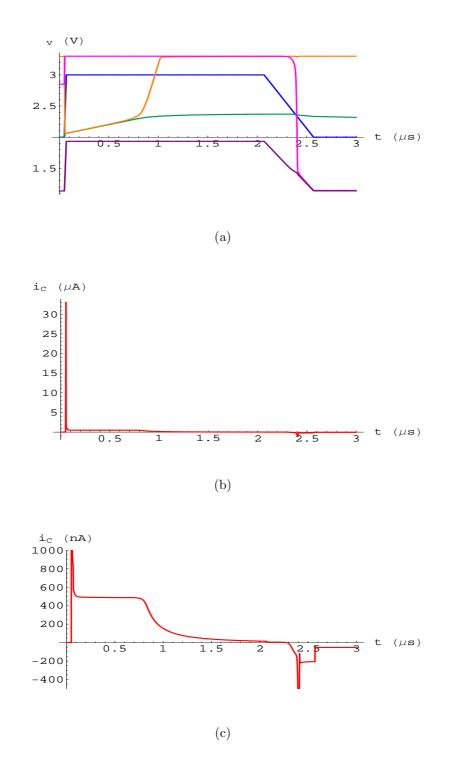

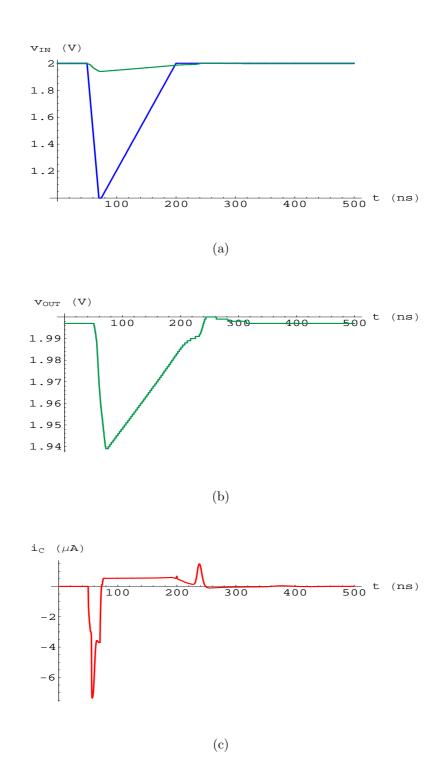

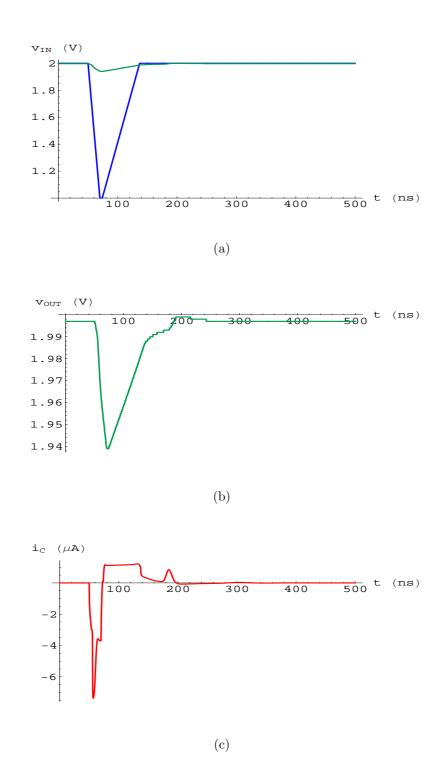

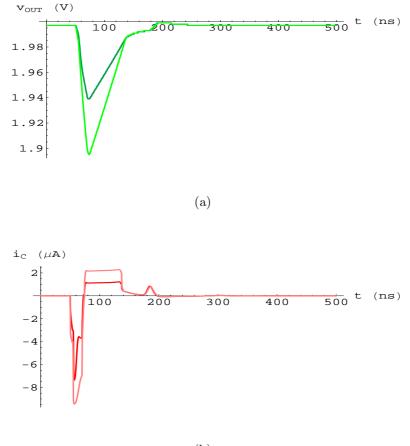

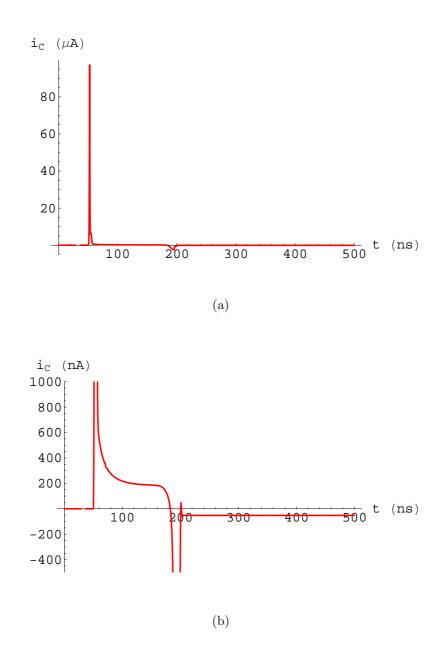

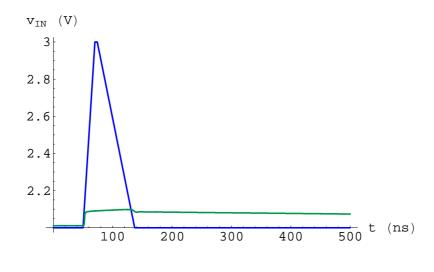

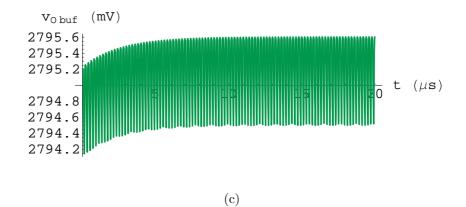

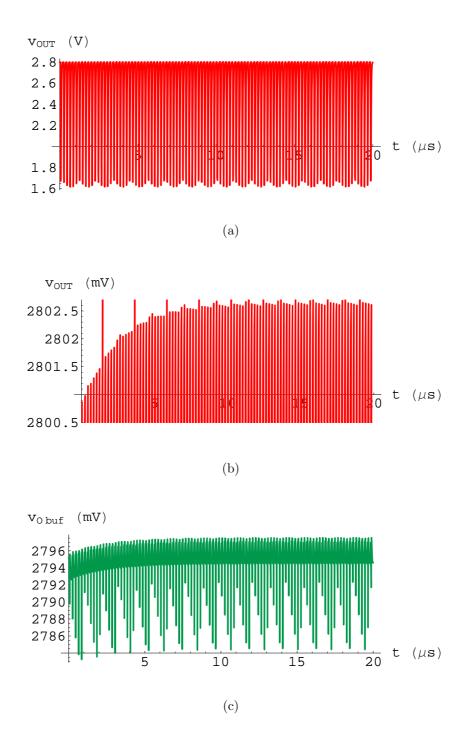

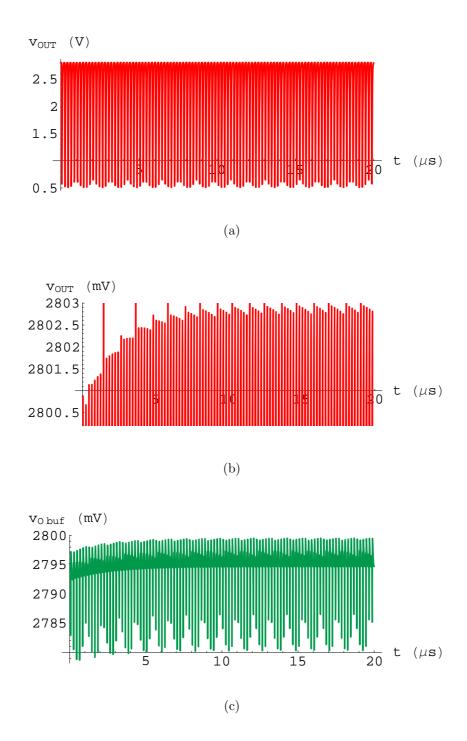

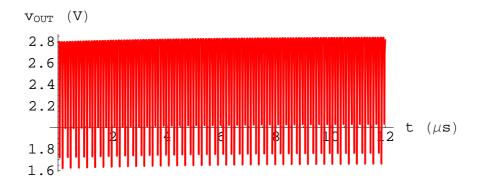

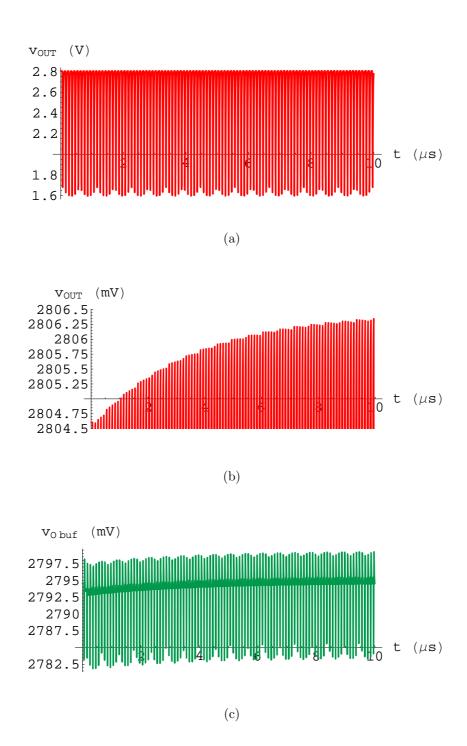

|          |                                                    | 4.2.1                                 | Slew-Rate Symmetrically Limited Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 95  |  |  |  |

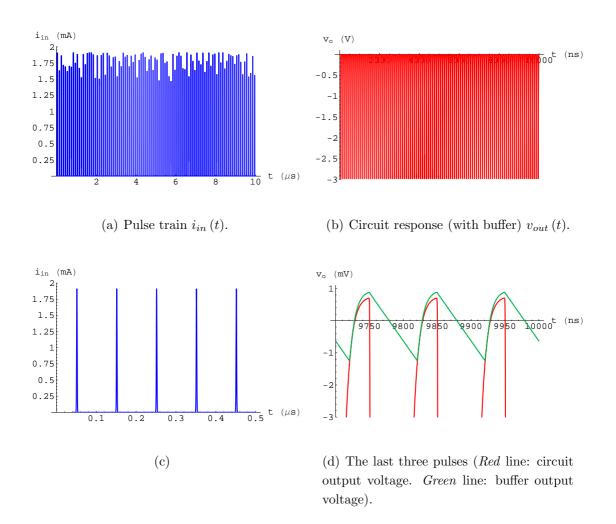

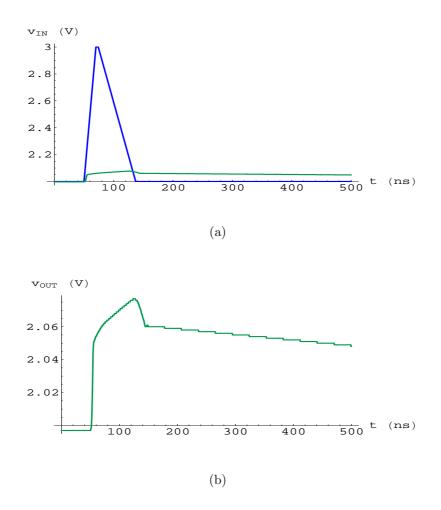

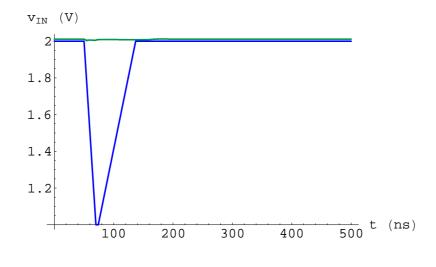

|          |                                                    | 4.2.2                                 | Slew-Rate Asymmetrically Limited Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 96  |  |  |  |

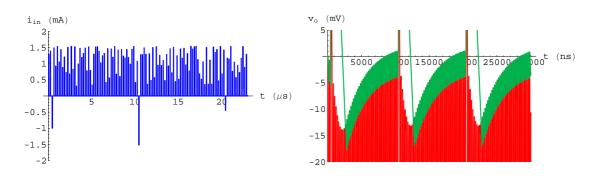

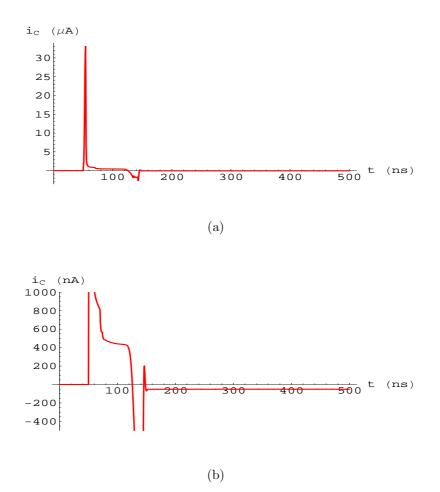

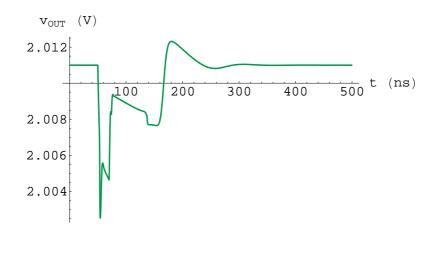

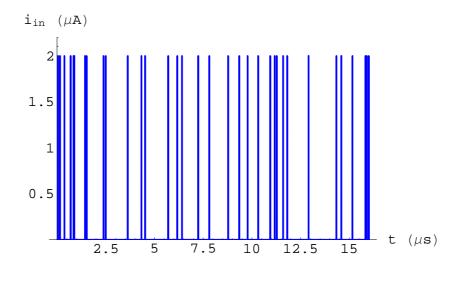

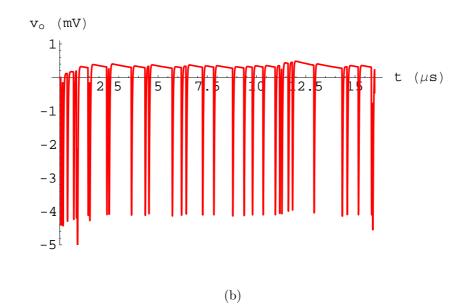

|          |                                                    | 4.2.3                                 | Circuit Response to Bipolar Incoming Pulses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 99  |  |  |  |

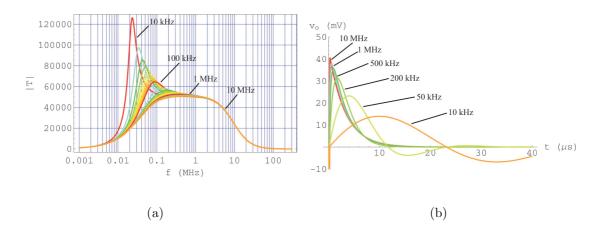

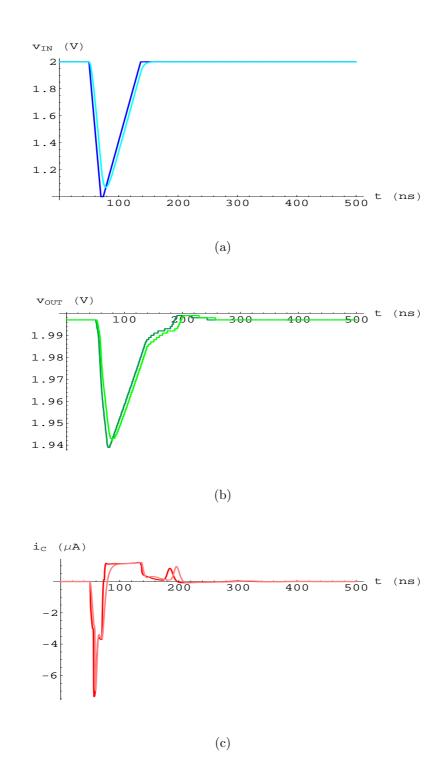

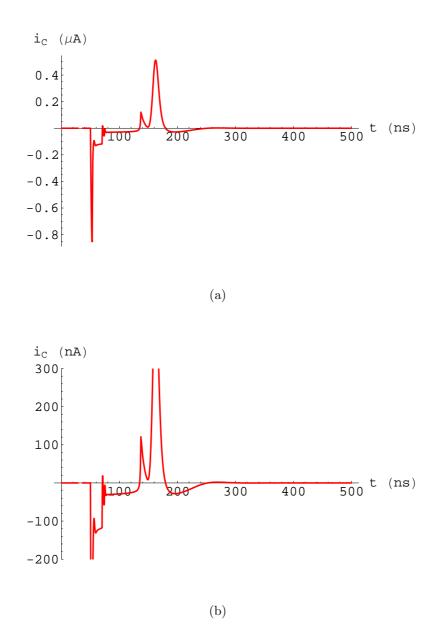

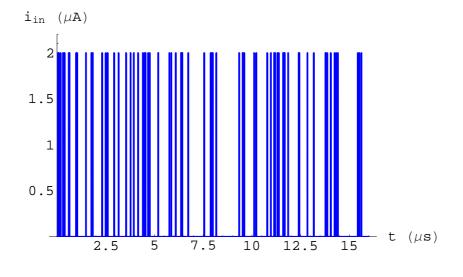

|          |                                                    | 4.2.4                                 | The Buffer Bandwidth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 100 |  |  |  |

| <b>5</b> | The Non-Linear Buffer: Transistor-Level Design and |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |  |  |  |

|          | $\mathbf{SPI}$                                     | PICE Simulations 10                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |  |  |  |

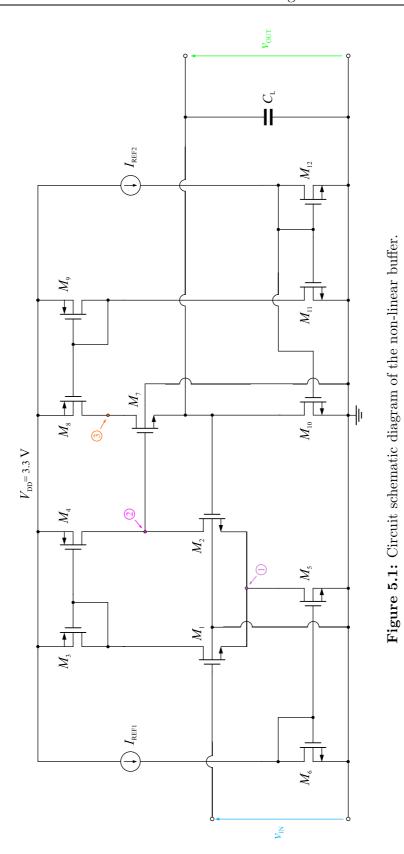

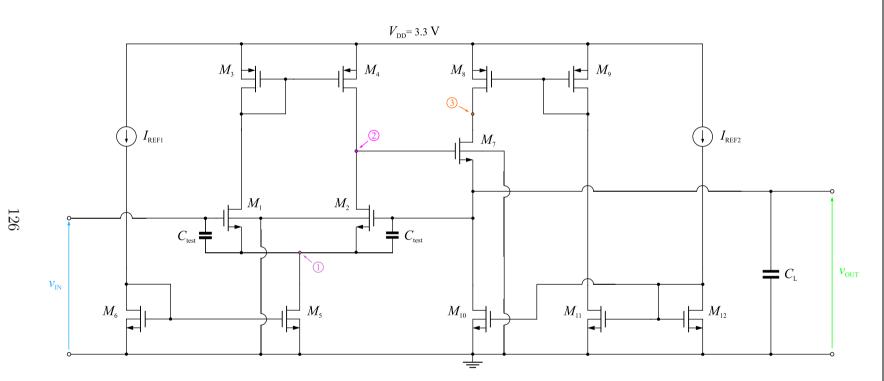

|          | 5.1                                                | The N                                 | Non-Linear Buffer Basic Circuit         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . <t< td=""><td>103</td></t<> | 103 |  |  |  |

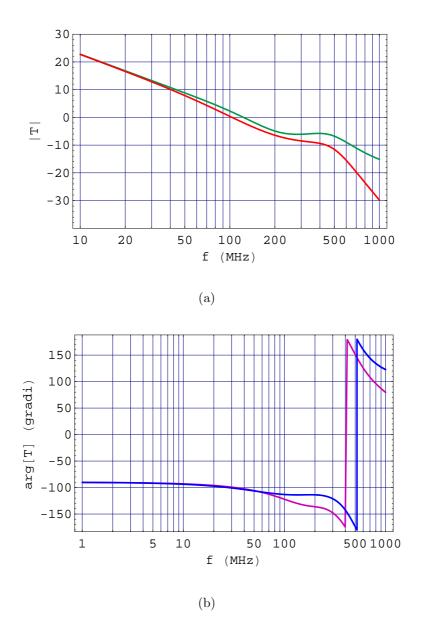

|          | 5.2                                                | Large                                 | -Signal Behavior of the Buffer Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 105 |  |  |  |

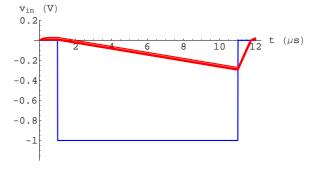

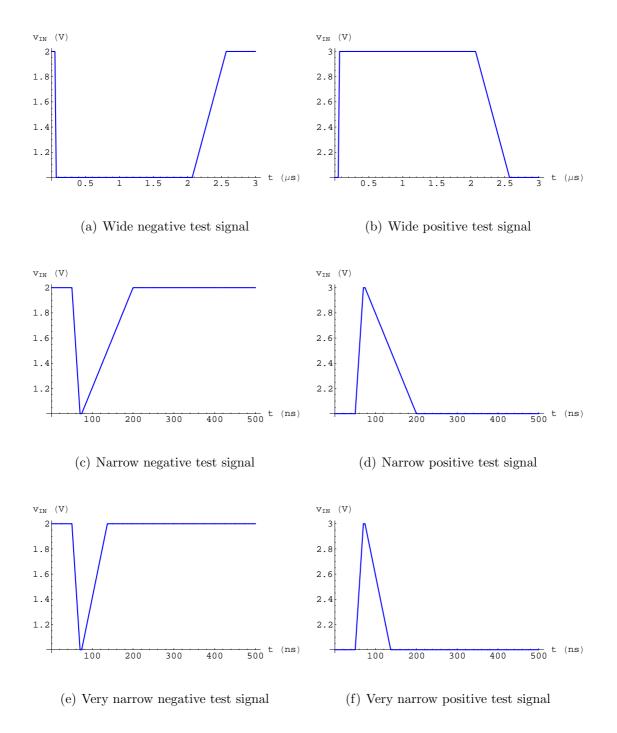

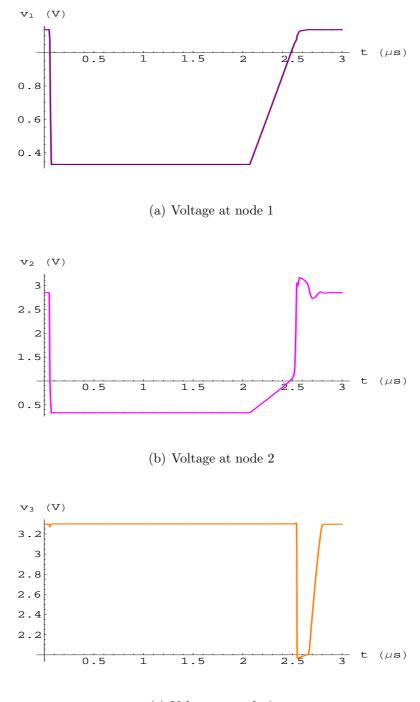

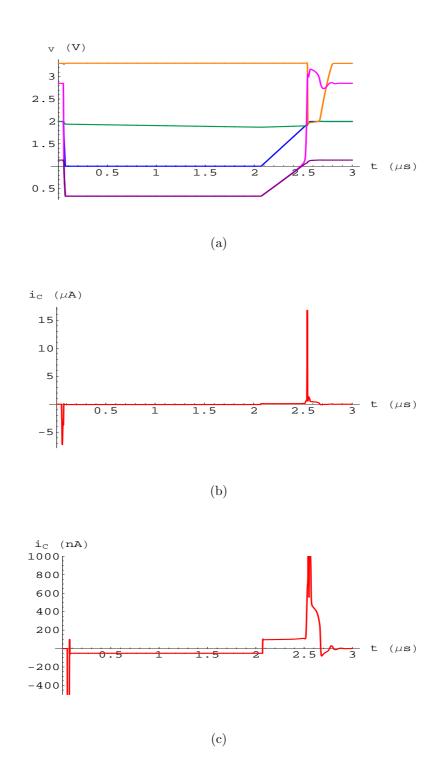

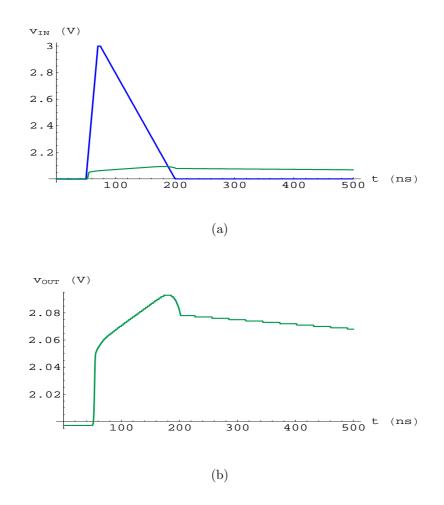

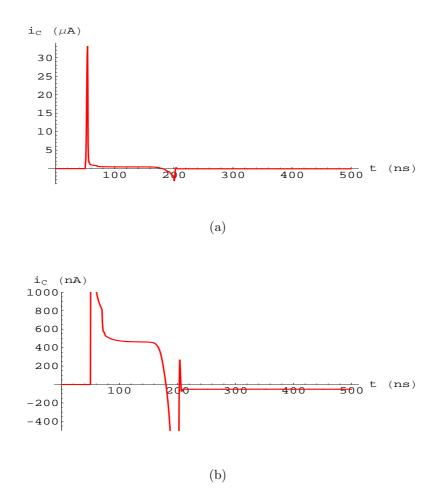

|          |                                                    | 5.2.1                                 | Circuit Response to a Wide Test Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 107 |  |  |  |

|          |                                                    | 5.2.2                                 | Circuit Response to a Narrow Test Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 113 |  |  |  |

|          |                                                    | 5.2.3                                 | Circuit Response to a Very Narrow Test Signal $\hfill \ldots \ldots \ldots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 119 |  |  |  |

|          |                                                    | 5.2.4                                 | Reducing the Capacitive Feedthrough                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 120 |  |  |  |

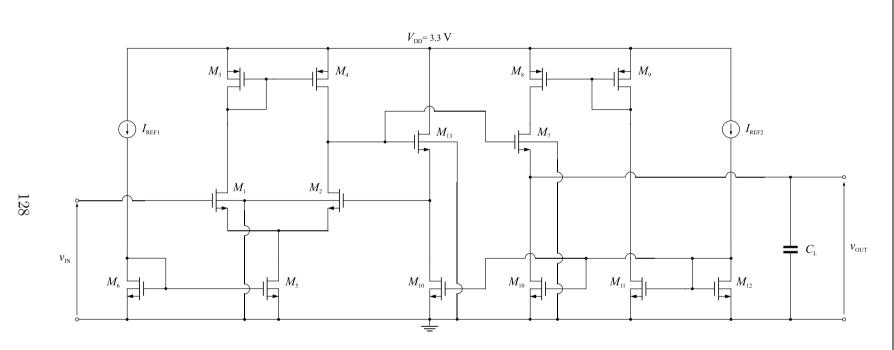

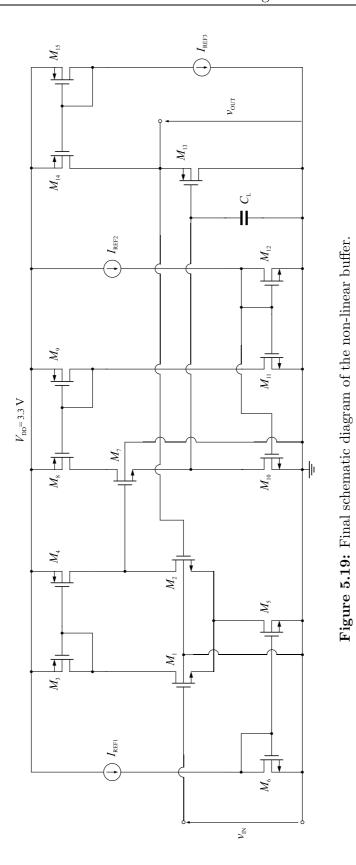

|          | 5.3                                                | The Non-Linear Buffer Final Circuit   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |  |  |  |

|          | 5.4                                                | Large                                 | -Signal Behavior of the New Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 130 |  |  |  |

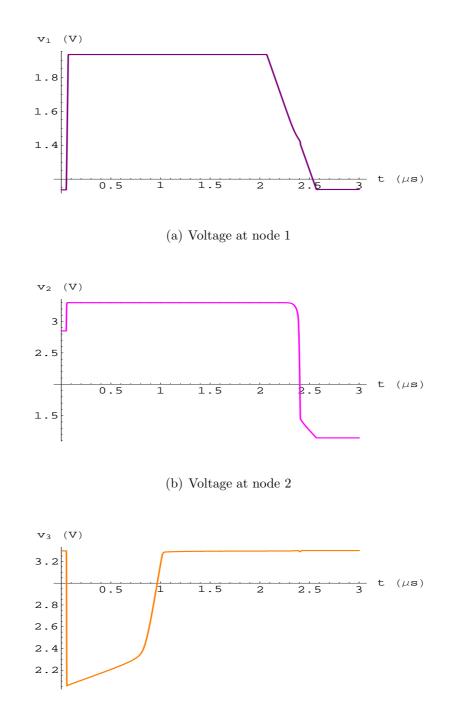

|          |                                                    | 5.4.1                                 | Circuit Response to a Wide Test Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 130 |  |  |  |

|          |                                                    | 5.4.2                                 | Circuit Response to a Narrow Test Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 134 |  |  |  |

|          |                                                    | 5.4.3                                 | Circuit Response to a Very Narrow Test Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 136 |  |  |  |

#### CONTENTS

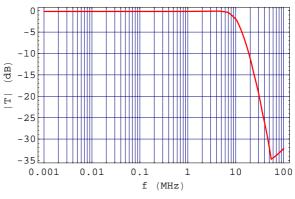

|                                                       | 5.4.4                        | Frequency Response of the New Circuit                                                                        | 142                                                 |  |  |  |

|-------------------------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|--|--|

| Design and Simulation of the Full Front-End Amplifier |                              |                                                                                                              |                                                     |  |  |  |

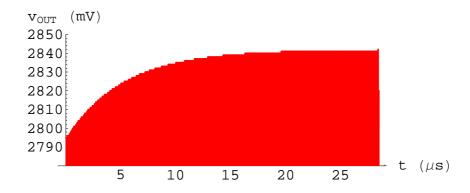

| 6.1                                                   | Behav                        | rior of the Slow Circuit                                                                                     | 146                                                 |  |  |  |

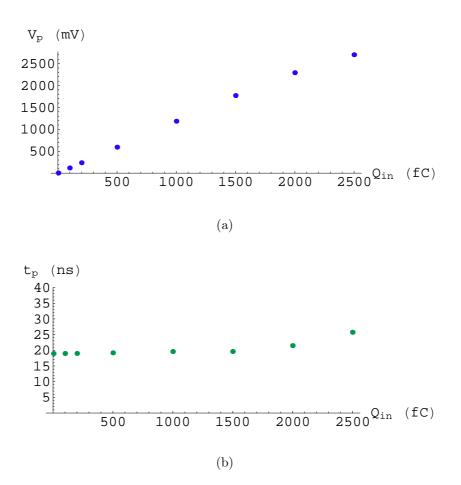

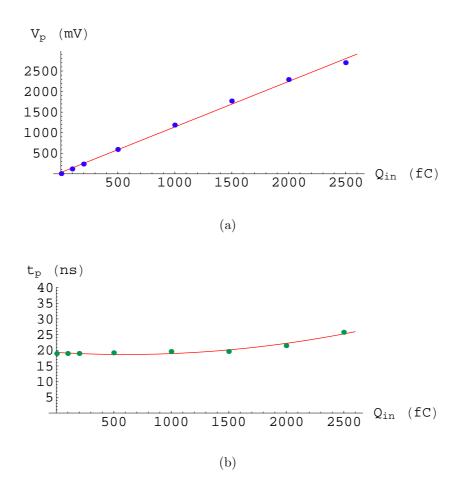

|                                                       | 6.1.1                        | Characterisation of the Single Output Pulse                                                                  | 147                                                 |  |  |  |

|                                                       | 6.1.2                        | The Shape of the Single Output Pulse                                                                         | 151                                                 |  |  |  |

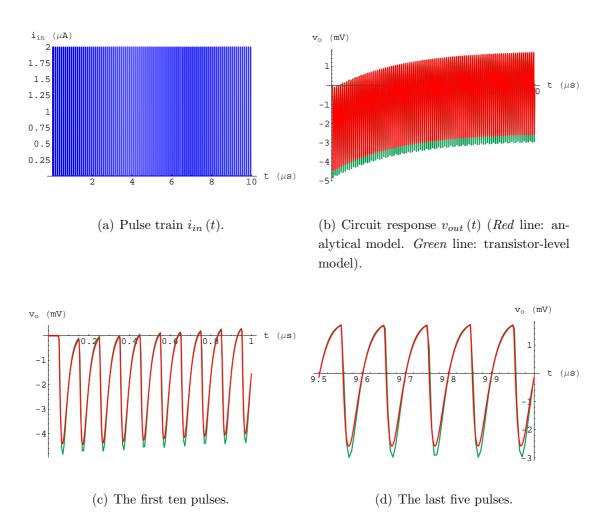

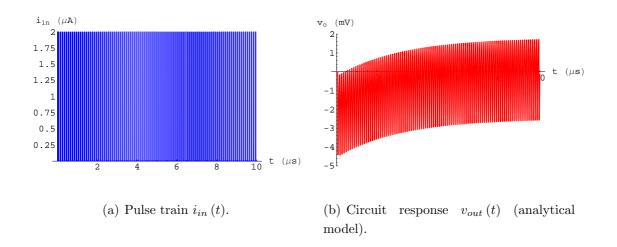

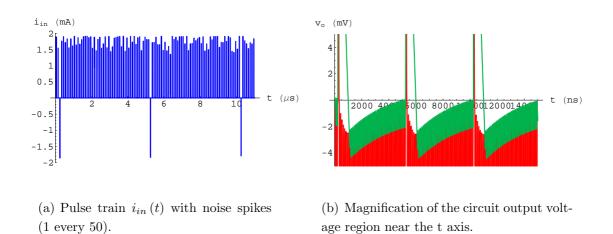

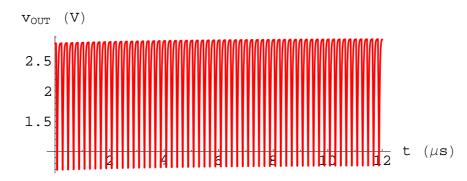

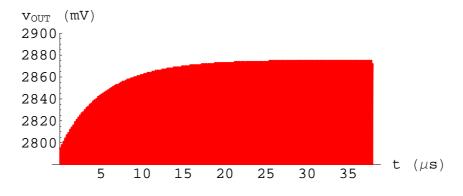

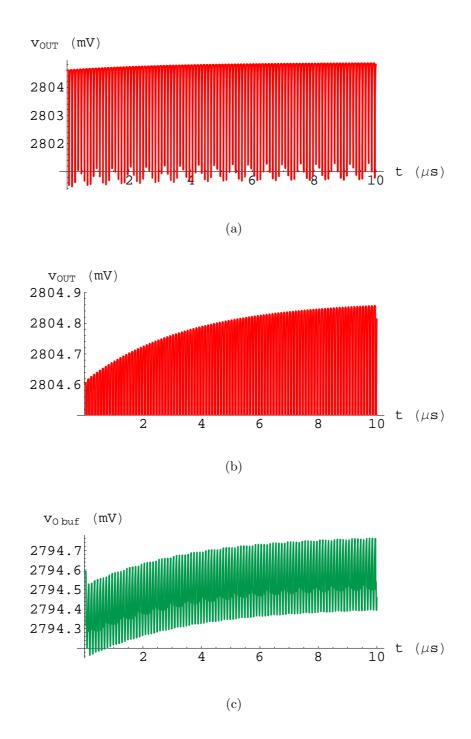

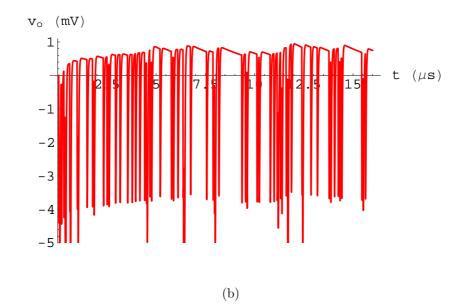

|                                                       | 6.1.3                        | The Circuit Response to a Pulse Train                                                                        | 152                                                 |  |  |  |

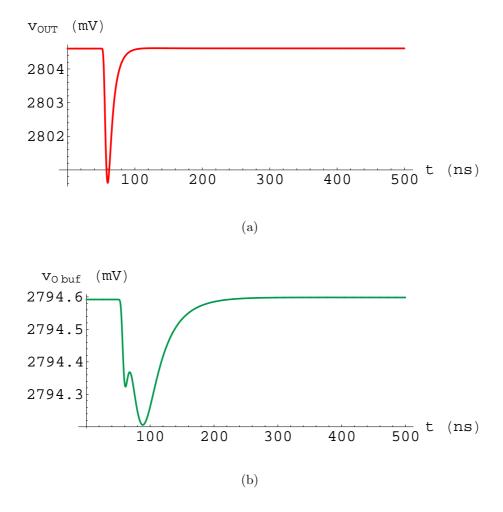

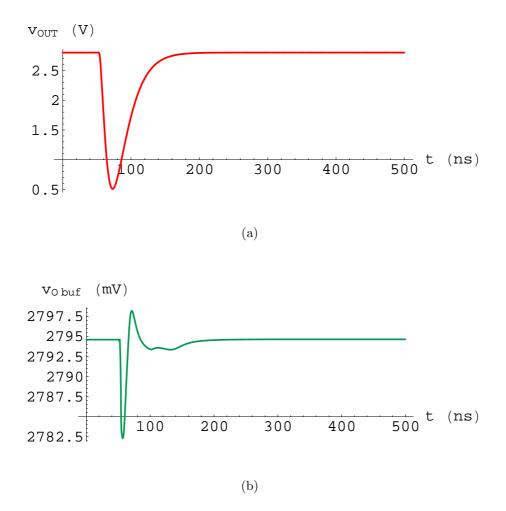

| 6.2                                                   | Behavior of the Fast Circuit |                                                                                                              | 157                                                 |  |  |  |

|                                                       | 6.2.1                        | The Shape of the Single Output Pulse                                                                         | 157                                                 |  |  |  |

|                                                       | 6.2.2                        | The Circuit Response to a Pulse Train                                                                        | 158                                                 |  |  |  |

| 6.3                                                   | Baseli                       | ne Fluctuations                                                                                              | 163                                                 |  |  |  |

| onclu                                                 | isions                       |                                                                                                              | 167                                                 |  |  |  |

| Bibliography                                          |                              |                                                                                                              |                                                     |  |  |  |

|                                                       | 6.1<br>6.2<br>6.3            | Design an<br>6.1 Behav<br>6.1.1<br>6.1.2<br>6.1.3<br>6.2 Behav<br>6.2.1<br>6.2.2<br>6.3 Baseli<br>onclusions | <ul> <li>6.1 Behavior of the Slow Circuit</li></ul> |  |  |  |

### Preface

The topic of this thesis is the design of the final version of the integrated circuit CMAD developed for the COMPASS experiment at CERN.

The project has been carried out at the VLSI Laboratory of the INFN of Turin.

As a first step, the limitations of an existing prototype of the circuit have been identified in order to improve the circuit performance especially from the counting rate point of view.

In fact a higher counting rate is one of the major requirements for the new frontend circuit and the improvement of the counting rate capability is a demanding specification.

Thus to obtain an understanding of the factors affecting the circuit response, a thorough study of the existing architecture has been carried out and an accurate mathematical model has been analytically derived.

The blocks critical for the circuit performance have been pointed out and a new design of these blocks has been achieved.

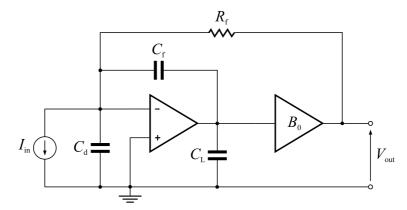

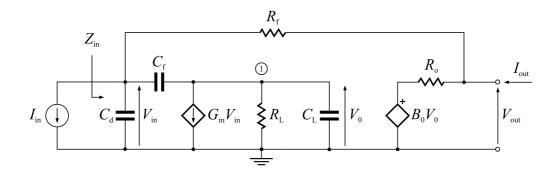

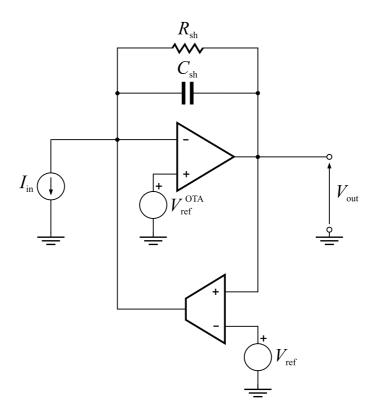

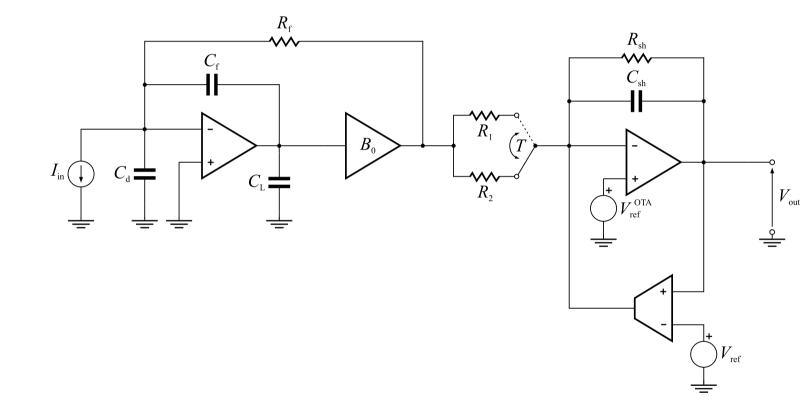

In particular the BLH (baseline holder) block has been modelled and redesigned and the design and the optimisation of the whole analog chain consisting of the preamplifier, the pulse shaper and the BLH (buffer + transconductor block) have been accomplished.

An outline of each chapter will be presented now in order to give a general idea of the thesis structure and the specific topics covered throughout this work.

Chapter 1 contains an overview of the COMPASS experiment for which the frontend chip is designed. A brief description of the COMPASS spectrometer behavior as well as the RICH particle detectors is given. The basics of Cherenkov effect, the fundamental principle that the RICH detectors are founded on, are also covered. The general behavior of the PMTs is presented. Finally a comparison between the main features and performance of the new front-end circuit and those of the old one is performed.

- Chapter 2 deals with the general characteristics of front-end circuits. The main purpose of this chapter is to give an insight into the architecture and the behavior of the stages making up a detector readout system, namely a CSA and a pulse shaper. Thus, the analysis performed is fairly qualitative and it is founded on a set of general relationships allowing an approximate understanding of the circuit behavior.

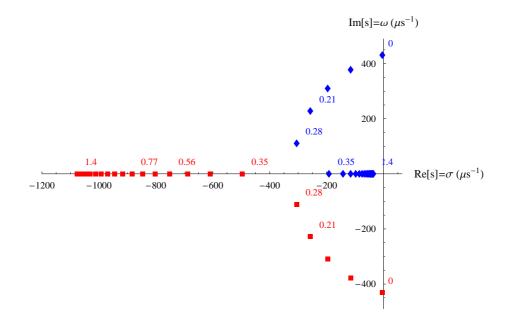

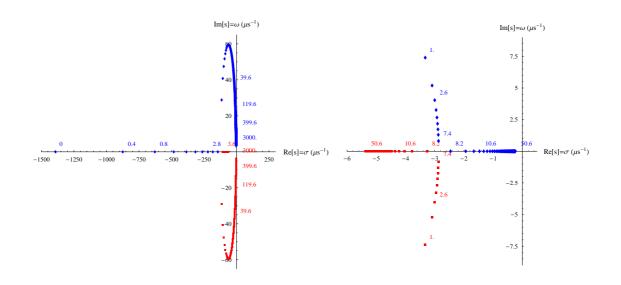

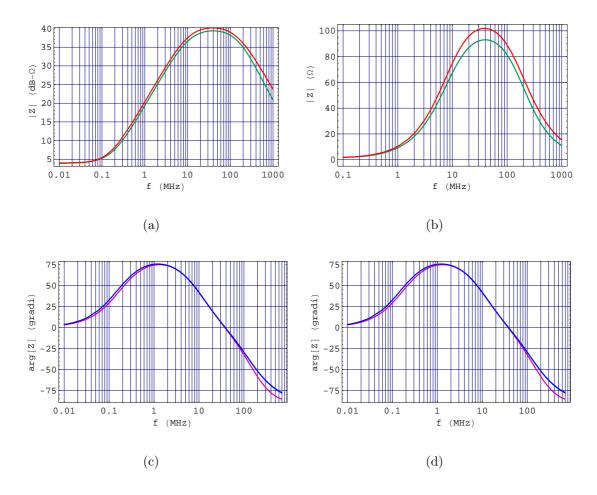

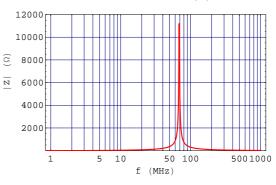

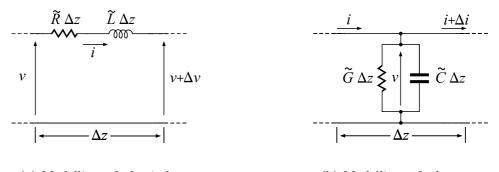

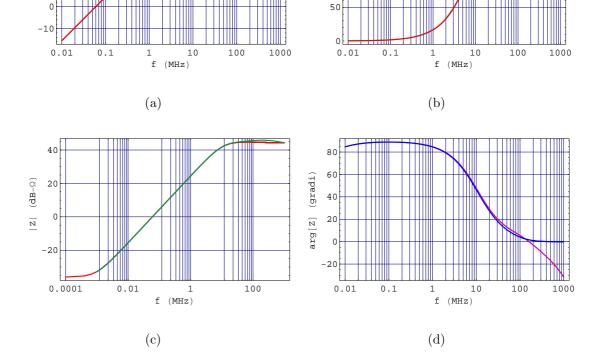

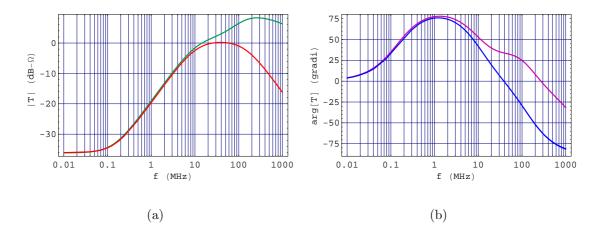

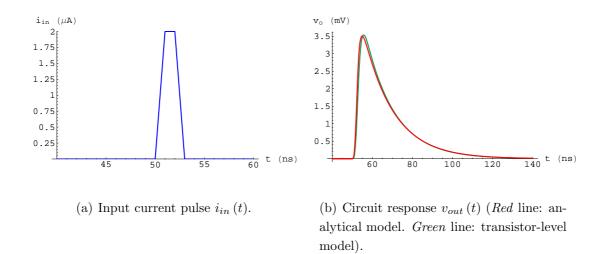

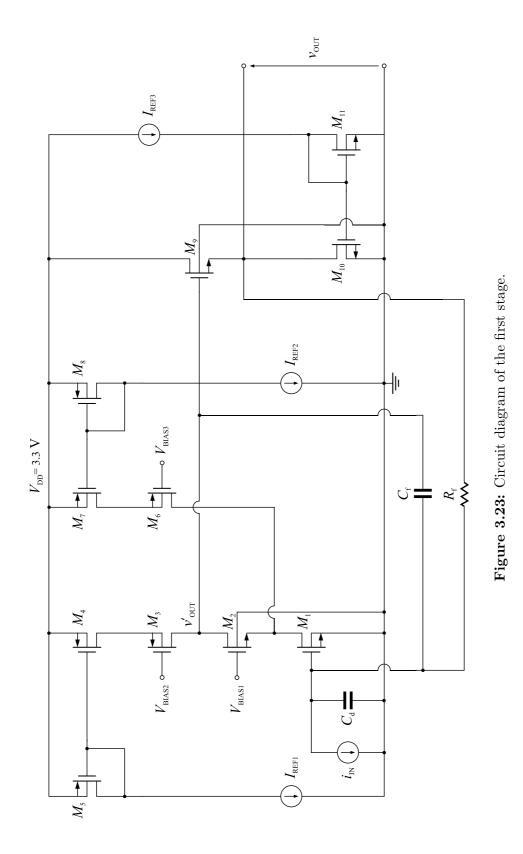

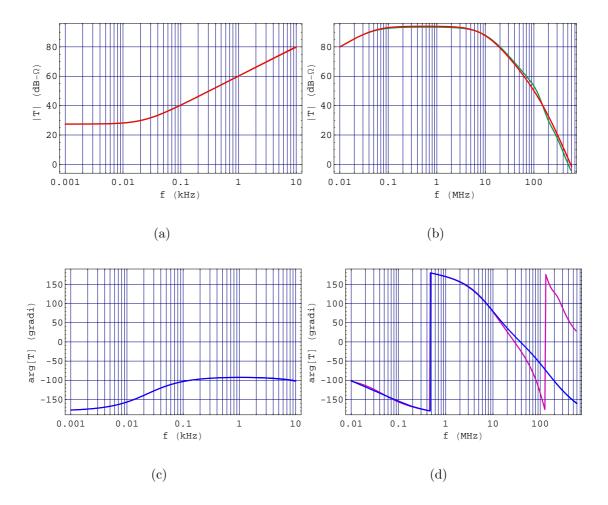

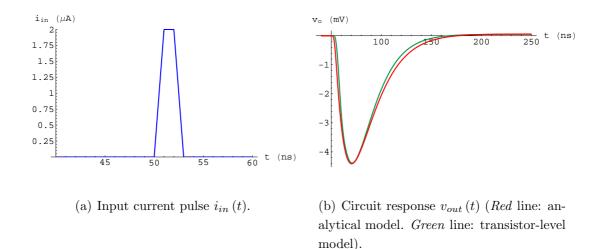

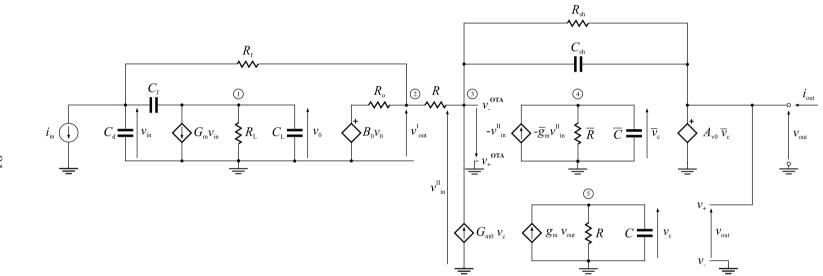

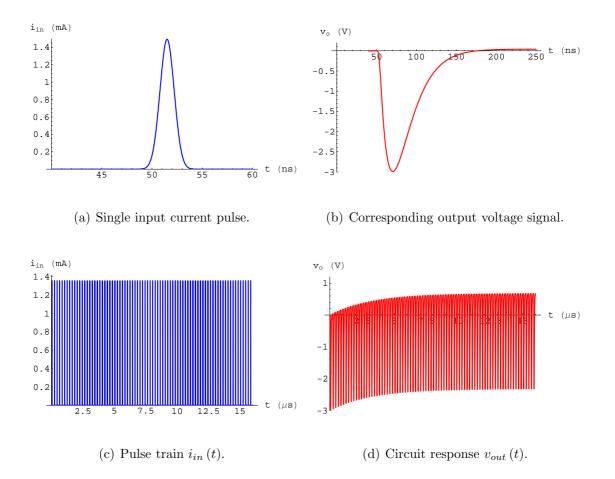

- Chapter 3 contains a detailed analysis of the first two stages of our detector readout system. The models used for representing the main characteristics of each of the circuit building blocks are presented. The small-signal transfer function as well as the input and output impedance of each stage are analytically derived in the frequency domain and described. The time-domain pulse response of each stage is also given graphically and discussed. Moreover, a lot of other graphical outputs are presented in order to check the accuracy of the results obtained through our models.

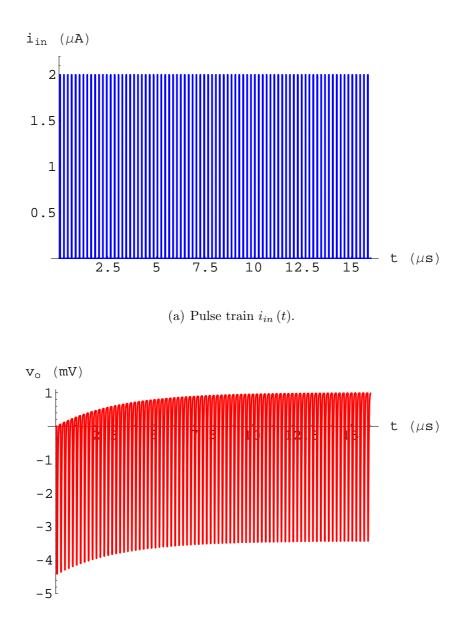

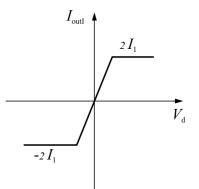

- Chapter 4 deals with the modelling and analysis of the slew-rate limited non-linear buffer making up (together with a transconductor block) the BLH (baseline holder). The BLH is a particularly important block because it provides the circuit output baseline stabilisation both at low frequency and at a high counting rate. Furthermore all the computer simulations performed to set important design parameters are given.

- Chapter 5 is concerned with the design of the non-linear buffer modelled in chapter 4. Several SPICE simulations of the actual circuit are performed in order to check it works properly especially when processing large and fast signals. A detailed analysis of the large-signal buffer basic circuit is carried out to identify circuit limitations and drawbacks. An alternative circuit for solving these problems is presented and analysed.

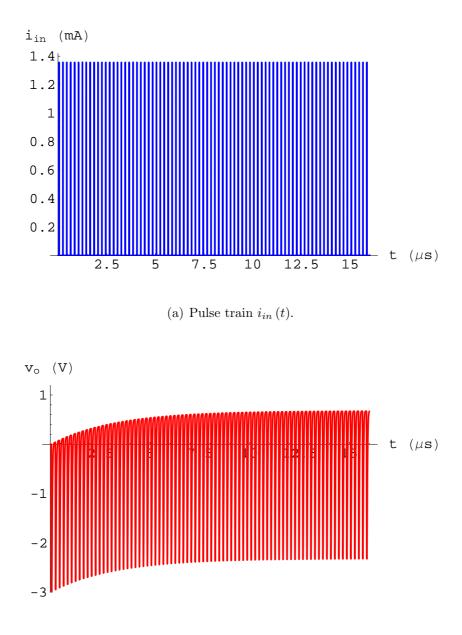

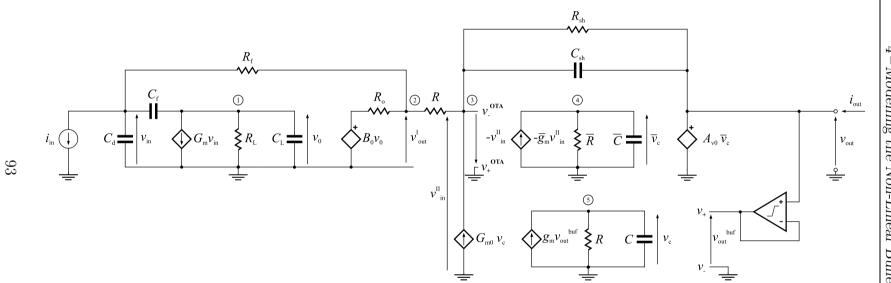

- **Chapter 6** deals with the single-pulse characterisation and the actual-circuit response to various sequences of pulses to show the efficient baseline stabilisation occurring for fast and large signals and performed by the new BLH block. The performance of a circuit version producing narrower output pulses and thus able to provide a higher counting rate is discussed.

Finally, we add that all the calculations presented throughout this thesis have been performed by using *Mathematica*, a general computer software system and language. In fact, although SPICE simulations could be performed to obtain the same numerical results, *Mathematica*'s symbolic computation capabilities allowed us to obtain symbolic relationships which proved to be very useful in understanding the circuit behavior. In fact the circuits considered are simple enough to allow an analytical approach.

# Chapter 1 Introduction

The topics covered in this thesis concern the front-end electronics of particle detectors. The purpose of such a detector is the acquisition of data allowing us to collect information about the energies and trajectories of subatomic particles.

In particular, the circuit studied throughout the thesis will be used for a specific high-energy physics experiment called COMPASS (Common Muon Proton Apparatus for Structure and Spectroscopy) taking place at CERN in Geneva.

#### 1.1 The COMPASS Experiment

The COMPASS experiment is a fixed target experiment at the CERN Super Proton Synchrotron (SPS). The purpose of this experiment is the study of hadron structure and spectroscopy with high intensity muon and hadron beams.

The physics programme includes measurements of semi-inclusive and inclusive polarized deep inelastic scattering, charm production, search for exotics in high quark spectroscopy and Primakov reactions. One of the main goals of the experiment is the measurement of the contribution of the gluon spins to the angular momentum of the nucleon.

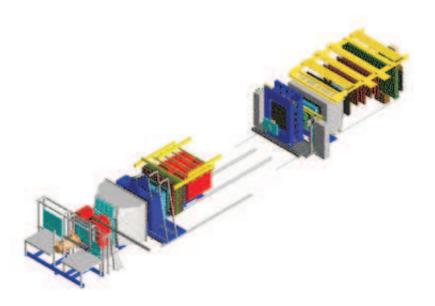

The COMPASS experiment was constructed in 1998-2000 and was commissioned during a technical run in 2001. The experiment set-up is made up of two spectrometers, a large-angle spectrometer followed by a small-angle spectrometer both provided with a gas RICH detector (RICH-1 and RICH-2) for hadron identification. A three-dimensional view of the COMPASS spectrometer is shown in Fig. 1.1.

The first physics run took place in 2002 and continued until the end of 2004.

Figure 1.1: Three-dimensional view of the COMPASS spectrometer at CERN.

After a year shutdown in 2005, data taking should continue in 2006. Nearly 240 physicists from 12 countries and 28 institutions are working on COMPASS.

One of the main new features of COMPASS with respect to previous experiments is its powerful data acquisition. The read-out architecture is based on custom electronics and operated with a 40 MHz clock. A trigger rate of 5 kHz was used for the muon experiments but the real DAQ capabilities will be exploited by the hadron beam experiments, even if the full rate of 50-100 kHz can be only used with a very efficient event reduction.

The total amount of data recorded in 2002 is very large and amounts to 9 billion events or 260 TByte.

#### 1.1.1 The COMPASS Spectrometer

To obtain a general understanding of the concept and performance of the COMPASS spectrometer, which is at the heart of the COMPASS experiment, we will give a brief description of its behavior.

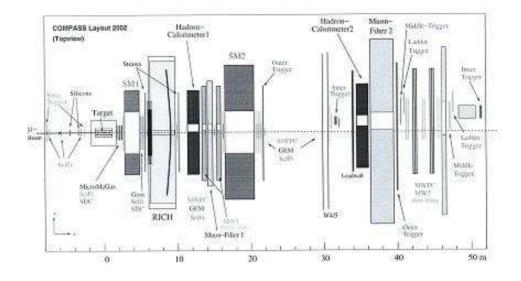

A schematic view of the COMPASS spectrometer is shown in Fig. 1.2. The spectrometer is made up of two stages, the large-angle spectrometer (LAS) covering an aperture of  $\pm 180$  mrad and the small-angle spectrometer (SAS) detecting particles within the inner  $\pm 30$  mrad.

Both sections comprise tracking and particle identification detectors grouped around the spectrometer dipole magnets SM1 and SM2 which provide field integrals of 1 and 4.4 Tm. Tracking in the beam region is provided by scintillating fibre and silicon detectors and in the intermediate region by MicroMeGas (Micro Mesh Gaseous structure) and Gem (Gaseous Electron Multiplier) detectors. Large area outer tracking is covered by drift chambers, multi-wire proportional chambers and straw tubes. Both LAS and SAS comprise a hadron calorimeter.

Figure 1.2: Top view of the COMPASS spectrometer in 2002.

The muon beam has a large momentum spread and a considerable size and hence a measurement of each single incoming particle is essential. The momentum is measured by four scintillator hodoscopes. Upstream of the target the beam particle trajectory is determined by a scintillating fibre hodoscope consisting of seven layers of fibres and read out by multi-anode photomultiplier tubes. The association of track and momentum is based on the time correlation.

The polarised target system consists of a superconducting target solenoid providing a field of 2.5 T and an additional dipole which can provide a transverse magnetic field. The incoming muon beam traverses two 60 cm long target cells containing oppositely longitudinally polarised deuterons. Finally it should be pointed out that the central apparatus for particle identification is the RICH-1 in the LAS. Before giving some additional information about the RICH-1, it is useful to recall that a RICH (Ring Imaging CHerenkov) detector is a particle detector that can determine the velocity v of a particle by an indirect measurement of the Cherenkov angle  $\theta_c$ , namely the angle between the emitted Cherenkov radiation and the particle path (a more detailed explanation of Cherenkov radiation will be given later).

In a RICH detector a cone of Cherenkov light is produced when a high speed particle traverses a suitable medium, often called radiator, with a velocity greater than the speed of light in that medium.

This light cone is detected on a position sensitive planar photon detector, which allows reconstructing a ring or disc, whose radius is a measure for the Cherenkov emission angle.

Both focusing and proximity-focusing detectors are in use. In a focusing RICH detector the photons are collected by a spherical mirror with focal length f and focused onto the photon detector placed at the focal plane. The result is a circle with a radius  $r = f \theta_c$ , independent of the emission point along the particle track. This scheme is suitable for low refractive index radiators, i.e. gases, due to the larger radiator length needed to create enough photons.

In the more compact proximity-focusing design a thin radiator volume emits a cone of Cherenkov light which traverses a small distance – the proximity gap – and is detected on the photon detector plane. The image is a ring of light whose radius is defined by the Cherenkov emission angle and the proximity gap. The ring thickness is determined by the thickness of the radiator.

#### 1.1.2 The COMPASS RICH Detectors

As mentioned previously the COMPASS spectrometer used in the muon program is a two stage spectrometer.

Hadrons produced in DIS (Deep Inelastic Scattering) are detected in the first stage and scattered muons in the second stage.

Two RICH detectors termed RICH-1 and RICH-2 are at the heart of the two stages respectively.

The RICH-1 is the fundamental tool for particle identification. Thus we will try to summarise the most important technical aspects characterising its behavior. The fundamental requirements for RICH-1 design related to the general design of the experiment are:

- ► the capability to separate  $\pi$  and K with momenta up to ~ 60 GeV/c in a high-intensity environment

- ▶ the full acceptance of the LAS (horizontal:  $\pm 250 \text{ mrad}$ ; vertical:  $\pm 200 \text{ mrad}$ )

- ▶ the minimisation of the total amount of material, to preserve the tracking resolution of the SAS as well as the energy resolution of the downstream electromagnetic and hadronic calorimeters

- ▶ the capability to register and handle high data fluxes.

An artistic view of COMPASS RICH-1 is shown in Fig. 1.3 which displays the position of some important detector components such as the mirror wall and the photon detector and also allows us to realise the real size of the whole device.

From a qualitative point of view the RICH 1 is a gas RICH with a 3 meter-long  $C_4 F_{10}$  radiator at atmospheric pressure, mantained at the temperature of 25°C.

The mirror set-up consists of spherical mirrors having a radius of 6.6 m and segmented in 120 hexagonal pieces covering a total area greater than  $20 \text{ m}^2$  forming two spherical surfaces with different centres of curvature.

**Figure 1.3:** Artistic view of COM-PASS RICH-1.

This solution allows the focalisation of the Cherenkov photons onto two sets of photon detectors placed above and below the acceptance region.

The photon detectors are equipped with CsI photocathodes for a total active surface of  $5.3 \,\mathrm{m}^2$ .

The pixel segmentation of the photocathodes (pixel size:  $8 \times 8 \text{ mm}^2$ ) results in approximately 80 000 channels equipped with analog read-out electronics.

In addition to the information stated above on the main design parameters, we can add that the gas radiator must be as pure as possible in order to limit the contamination from impurity able to absorb UV photons. The goal is water vapour and oxygen traces smaller than 5ppm.

For the vessel, leakages  $< 10^{-2}$  mbar l/s as well as nonpolluting materials are required. Moreover the vessel must be thermalised to reduce the refractive index dispersion and designed to be the support for the mirror wall as well as the photon detector.

Thus, the gas purity, the rigidity and the stability required to guarantee the relative alignment of mirrors and photon detector have been important design criteria.

For the mirrors the main requests concern good performance in the UV region, surface shape and amount of material. In practice a good reflectance in the far UV region is obtained by using a reflective coating of Al (80 nm) protected by a layer of Mg  $F_2$  (30 nm).

The local deviation from the spherical shape must not exceed 0.2 mrad and the radius deviation from its nominal value must be in the order of 0.5 % for each single mirror.

The RICH-2 installed in the second stage is used for particle identification in the high energy region, namely up to 120 GeV.

The structure of RICH-2 is similar to RICH-1. The thickness of the radiator gas is 8 m. The radiator gas is a mixture of 50%  $C_2 F_6$  and 50% Ne. The photon-detector is the same type as that of RICH-1 and it has 23 K cathode pads.

#### 1.2 Cherenkov Radiation

As mentioned in the previous section the Cherenkov effect is the fundamental principle that the RICH detectors are founded on.

It is known that the speed of light *in vacuum* is a universal constant c whereas the speed of light in a material may be significantly less than c (e.g. the speed of light in water is 0.75 c).

Cherenkov radiation results when a charged particle, most commonly an electron, exceeds the speed of light in a dielectric medium through which it passes.

Moreover, the velocity of light that must be exceeded is the phase velocity rather than the group velocity.

The phase velocity can be altered dramatically by employing a periodic medium or a complex periodic medium, such as a photonic crystal. In that case a variety of anomalous Cherenkov effects, such as radiation in a backward direction, can be observed (let us recall that ordinary Cherenkov radiation forms an acute angle with the particle velocity).

As a charged particle travels, it disrupts the local electromagnetic field in its medium. Electrons in the atoms of the medium will be displaced and polarized by the passing EM field of the charged particle.

Photons are emitted as the insulator electrons restore themselves to equilibrium after the disruption has passed (in a conductor, the EM disruption can be restored without emitting a photon).

In normal circumstances, these photons destructively interfere with each other and no radiation is detected. However, when the disruption travels faster than the photons themselves, the photons constructively interfere with and intensify the observed radiation.

A common analogy is the sonic boom of a supersonic aircraft. The sound waves generated by the supersonic body do not move fast enough to get out of the way of the body itself. Hence, the waves stack up and form a shock front.

Similarly, a speed boat generates a large bow shock because it travels faster than waves can move on the surface of the water.

can move on the surface of the water. In the same way, a charged particle generates a photonic shockwave as it travels through

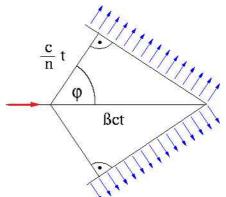

**Figure 1.4:** The geometry of the Cherenkov radiation.

an insulator faster than the speed of light in that medium.

It should also be pointed out that Cherenkov radiation is entirely unrelated to the *bremsstrahlung*, which is emitted by the moving electron itself when it collides with atomic nuclei in the medium.

In contrast, the Cherenkov effect involves radiation emitted by the medium under the action of the field of the particle moving in it.

The distinction between the two types of radiation appears with particular clarity when the particle has a very large mass since *bremsstrahlung* disappears whereas Cherenkov radiation is unaffected.

Figure 1.4 shows graphically what we stated above. The red arrow represents the charged particle moving in the medium whereas the blue arrows represent the photons emitted after the particle has passed.

From the figure it is apparent that this radiation is only observed at a particular angle called Cherenkov angle  $\varphi$ , with respect to the track of the particle.

This angle represents the position in which waves from arbitrary points over the particle track are coherent and combine to form a plane wave front.

If the velocity of the particle is  $v = \beta c$  where c is the velocity of light *in vacuum* and c/n is the velocity of the Cherenkov light in the medium, then by taking into account only geometrical considerations we can write the Cherenkov angle as

$$\cos\varphi = \frac{\frac{c}{n\left(\lambda\right)}\Delta t}{\beta c \,\Delta t}\tag{1.1}$$

from which

$$\cos\varphi = \frac{1}{\beta n\left(\lambda\right)} \tag{1.2}$$

where n is the refractive index of the medium and  $\Delta t$  is the time interval considered in Fig. 1.4.

Let us now consider equation (1.2) in order to analyse some particular implication, namely:

- ▷ for a medium of a given refractive index n, there is a threshold velocity  $\beta_{\min} = 1/n$ , below which no radiation takes place. At this critical velocity the direction of radiation coincides with that of the particle. Thus the process can be used in the construction of threshold detectors in which Cherenkov radiation is only emitted if the particle has velocity greater than c/n.

- ▷ For an ultra-relativistic particle, for which  $\beta = 1$ , there is a maximum angle of emission given by  $\cos \varphi = 1/n$ .

- ▷ The radiation occurs in the visible and near visible regions of the spectrum, for which n > 1. A real medium is always dispersive, so actually radiation is restricted to those frequency bands for which  $n(\omega) > 1/\beta$ . In the x-ray region it is always  $n(\omega) < 1$  and radiation is forbidden. Thus, emission in the x-ray region is impossible because n is less than unity and the equation  $\cos \varphi = 1/n$  cannot be satisfied.

There are two further conditions to be fulfilled to achieve coherence. First, the length l of the track of the particle in the medium should be large compared with the wavelength of the radiation in question, otherwise diffraction effects will become dominant. Secondly, the velocity of the particle must be constant during its passage through the medium, or, to be more specific, the differences in the times for the particle to traverse successive distances  $\lambda$  should be small compared with the period  $\lambda/c$  of the emitted light.

#### **1.3** Photomultiplier Tubes

Since the signal to be read out by the front-end electronics comes from photomultiplier tubes, it is interesting to obtain an insight into the main features of these devices.

The photomultiplier tubes (PMTs) are used for light detecting of very weak signals. They are photoemissive devices in which the absorption of a photon results in the emission of an electron.

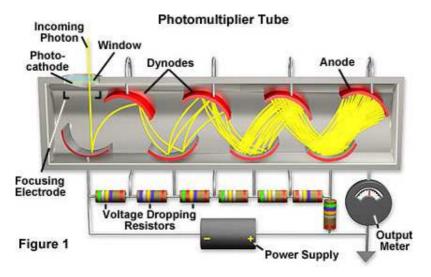

Figure 1.5: Three-dimensional schematic representation of a conventional PMT.

These detectors work by amplifying the electrons generated by a photocathode exposed to a photon flux. A three-dimensional schematic representation of such a device is shown in Fig. 1.5.

Photomultipliers acquire light through a glass or quartz window that covers a photosensitive surface, called the photocathode, which then releases electrons that are multiplied by electrodes known as metal channel dynodes.

At the end of the dynode chain there is an anode or collection electrode. Over a very large range, the current flowing from the anode to ground is directly proportional to the photoelectron flux generated by the photocathode.

The spectral response, quantum efficiency, sensitivity, and dark current of a photomultiplier tube are determined by the composition of the photocathode.

The best photocathodes capable of responding to visible light are less than 30% quantum efficient, meaning that 70% of the photons impacting on the photocathode do not produce a photoelectron and are therefore not detected.

Photocathode thickness is an important variable that must be monitored to ensure the proper response from absorbed photons.

If the photocathode is too thick, more photons will be absorbed but fewer electrons will be emitted from the back surface, but if it is too thin, too many photons will pass through without being absorbed.

The electrons emitted by the photocathode are accelerated toward the dynode chain, which may contain up to 14 elements.

Focusing electrodes are usually present to ensure that photoelectrons emitted near the edges of the photocathode are likely to land on the first dynode.

Upon impacting the first dynode, a photoelectron will invoke the release of additional electrons that are accelerated toward the next dynode, and so on.

The surface composition and geometry of the dynodes determines their ability to serve as electron multipliers. Because the gain varies

Figure 1.6: Dynode number versus PMT gain.

with the voltage across the dynodes and the total number of dynodes, electron gains of 10 million are possible if 12–14 dynode stages are employed, as shown in Fig. 1.6.

Photomultipliers produce a signal even in the absence of light due to the dark current arising from thermal emissions of electrons from the photocathode, leakage current between dynodes, as well as stray high-energy radiation.

Electronic noise also contributes to the dark current and is often included in the dark-current value.

#### **1.3.1** Channel Photomultipliers

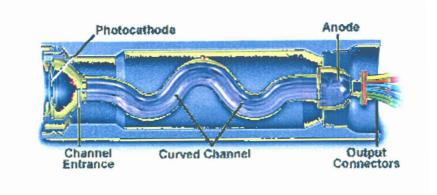

Channel photomultipliers represent a new design that incorporates a detector having a semitransparent photocathode deposited onto the inner surface of the entrance window.

Photoelectrons released by the photocathode enter a narrow and curved semiconductive channel that performs the same functions as a classical dynode chain.

Each time an electron impacts the inner wall of the channel, multiple secondary electrons are emitted. These ejected photoelectrons have trajectories angled at the next bend in the channel wall (simulating a dynode chain), which in turn emits a larger quantity of electrons angled at the next bend in the channel.

The effect occurs repeatedly, leading to an avalanche effect with a gain exceeding 100 million.

Figure 1.7: Three-dimensional schematic representation of a channel PMT.

Thus, the channel photomultiplier is a design that eliminates the hundreds of elements necessary to construct a conventional dynode chain.

The advantages of this design are lower dark current (pA range), increased sensitivity, wider bandwidth, and an extended dynamic range. The monolithic structure provides a fairly high efficiency. Secondary emission of electrons occurs identically on any portion of the photomultiplier sidewalls, thus optimizing performance.

Because photomultipliers do not store charge and respond to changes in input light fluxes within a few nanoseconds, they can be used for the detection and recording of extremely fast events.

Finally, the signal to noise ratio is very high in scientific grade photomultipliers because the dark current is extremely low (it can be further reduced by cooling).

#### **1.4** Front-End Electronics for the RICH

In this section we will consider the main reasons which have led to the development of a new design for the detector front-end circuit.

In fact, these new requirements have motivated the modelling and the analysis performed throughout this thesis on the front-end circuit, to give the basis for the improvement of the circuit performance, especially at a high counting rate.

An overview of the old circuit, called MAD, will be presented as well as a brief description of the features of the new circuit.

#### 1.4.1 The MAD

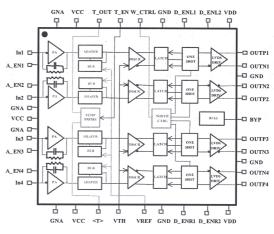

The MAD is a full custom ASIC in which the analog front-end electronics for the muon chambers of CMS barrel has been integrated.

This chip has been realised in  $0.8 \,\mu\text{m}$ BiCMOS technology and provides 4 identical chains of amplification, discrimination and cable driving circuitry.

It also integrates a flexible channel enabling/disabling feature and a temperature probe.

Figure 1.8 shows the block diagram of the MAD.

By inspecting the figure we are able to identify the four identical analog chains mentioned above.

Figure 1.8: Block diagram of the MAD.

Each chain consists of a charge preamplifier (PA) followed by a pulse shaper with its baseline restorer (BLR), a latched discriminator (DISCR + LATCH) comparing the analog output of the shaper with an external reference voltage value (VTH) and issuing a standard logic signal, a programmable one-shot stretching the output logic pulses and finally an output stage able to drive long twisted pair cables with LVDS compatible levels (LVDS DRIV).

As far as the channel output section operation is concerned, we can add that the buffered output of the discriminator is capacitively coupled to the one-shot and that the discriminator differential output, when active, stores the comparator status in the latch producing a non retriggerable pulse whose width is inversely proportional to the current sunk from the W\_CTRL pin, shared by all the channels.

The ASIC also includes some control and monitoring features, namely

- ▷ each channel can be disabled at the shaper input resulting in little crosstalk to neighbours,

- ▷ a fast enable/disable feature allows the simulation of tracks perpendicular to the detector,

- ▷ an absolute temperature probe is able to detect electronics failures and monitor environmental changes.

#### 1.4.2 The CMAD

The new readout front-end circuit will be used in the COMPASS RICH upgrade to read out the signals coming from multi-anode photomultiplier tubes.

There are several important reasons which suggested the changes that characterise the new project and now some of them will be dealt with briefly here to obtain a general idea of the new circuit features.

From the fabrication process point of view the MAD was realized in  $0.8 \,\mu\text{m}$ BiCMOS technology whereas the CMAD is realised in  $0.35 \,\mu\text{m}$  CMOS technology. The key point here is that the  $0.8 \,\mu\text{m}$  BiCMOS technology is obsolete and new samples of the circuit can no longer be produced in such a technology.

Also the modularity of the circuit is enhanced since the new circuit is provided with eight channels whereas the old one had only four channels.

Another important new requirement for the circuit is the gain value.

The MAD was designed to give a gain of 4 mV/fC while the CMAD allows us to choose between two gain values, the old value of 4 mV/fC, for compatibility with the old circuit, and the new value of 1.1 mV/fC, optimised for COMPASS.

In fact the signals coming from the new detector will not be as weak as those the old circuit had been conceived for. For this reason the new circuit has been designed to give a gain value smaller than the preceding one.

Finally, another demanding design specification concerns the maximum counting rate.

The new circuit is able to work correctly up to 5 MHz and an enhanced version of this circuit, capable of working properly up to a rate in the order of 10 MHz, has already been designed.

On the other hand the old circuit allowed a maximum counting rate approximately equal to 2 MHz.

### Chapter 2

### The Basics of Front-End Circuits

Signals delivered by particle detectors are normally fairly weak.

The first element of the electronics acquisition chain is therefore a front-end amplifier whose task is to amplify and filter the incoming signal.

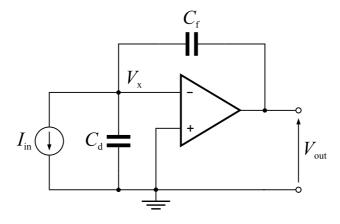

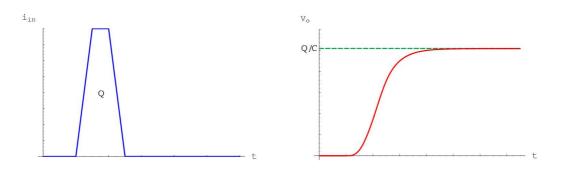

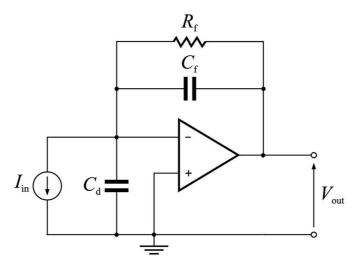

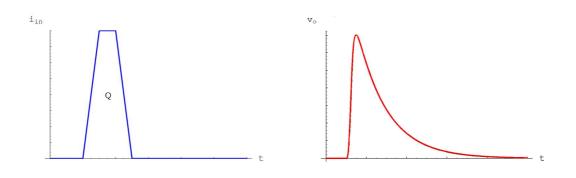

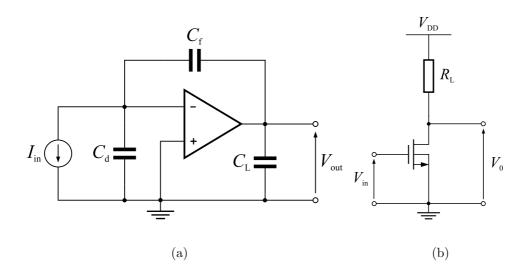

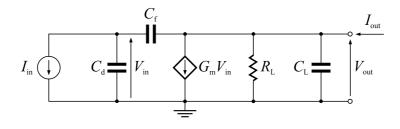

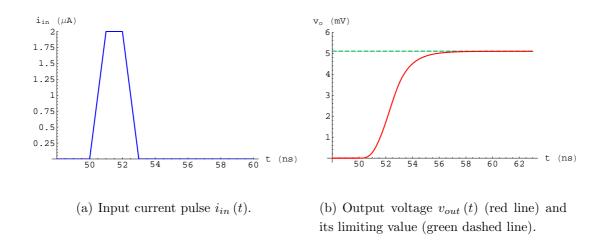

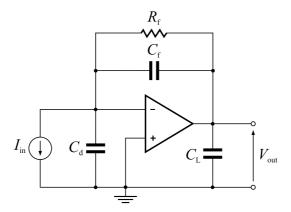

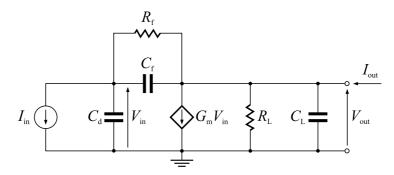

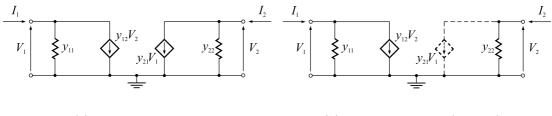

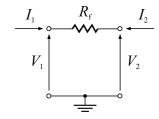

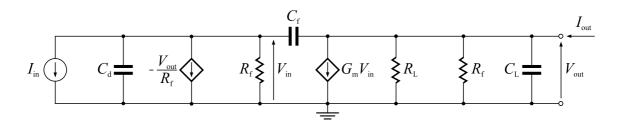

In this chapter we will perform a general analysis of the stages making up a typical front-end amplifier, namely a CSA and a pulse shaper.

The purpose of this preliminary analysis is to obtain a general understanding of the behavior of these blocks.

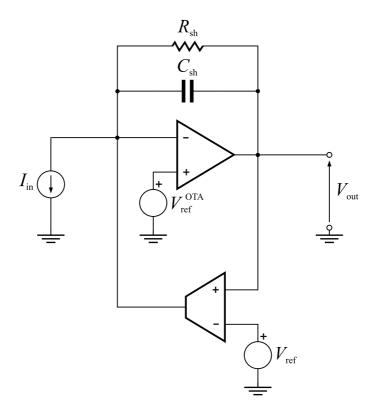

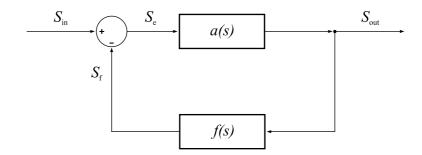

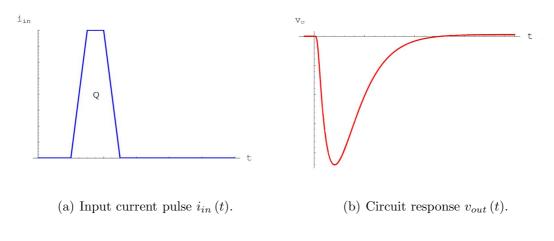

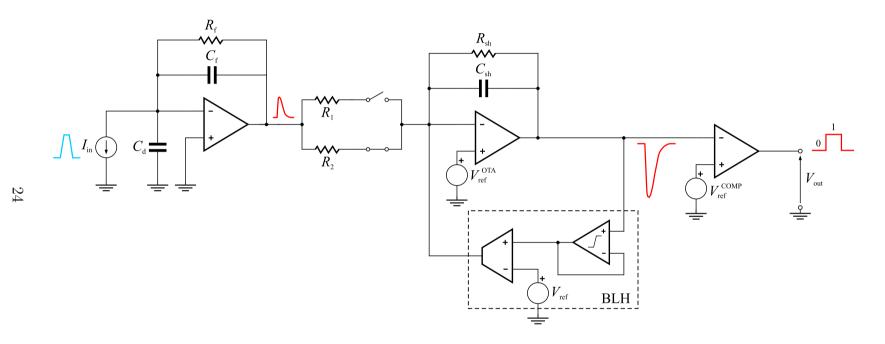

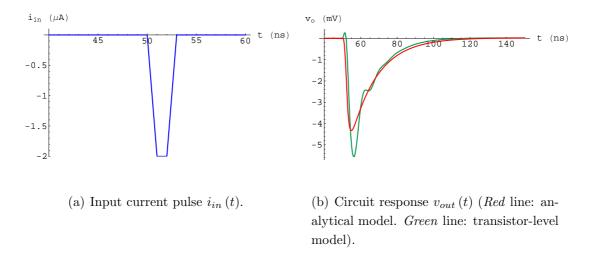

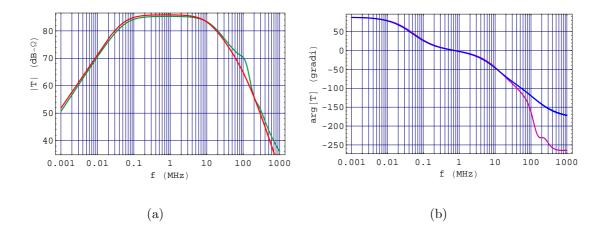

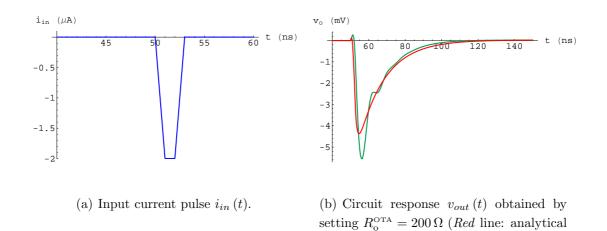

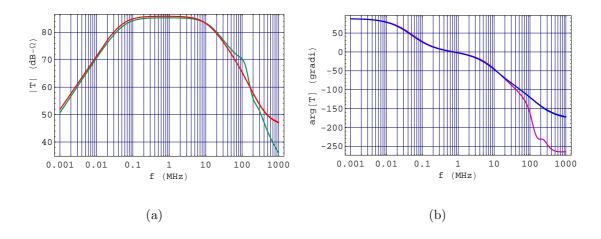

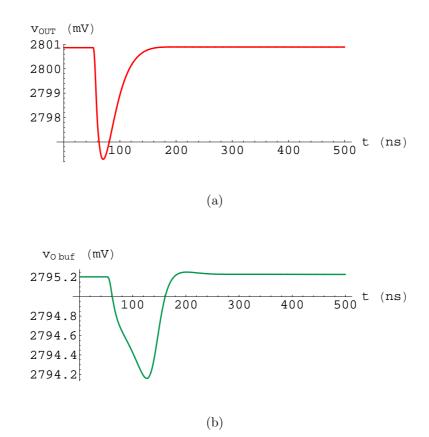

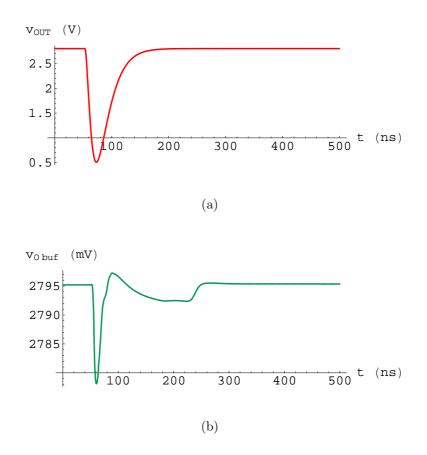

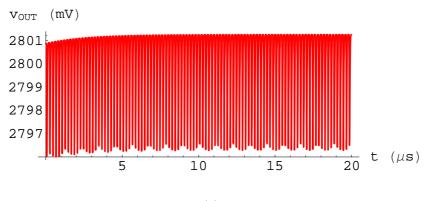

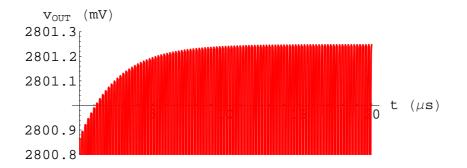

The small-signal behavior of these stages will be dealt with in detail in the following chapters by performing a detailed analysis of their small-signal equivalent circuits.