## Università degli Studi di Torino

Dipartimento di Fisica Corso di Laurea Magistrale in Fisica delle Tecnologie Avanzate

## Analog Front-end Design in Deep Sub-micron CMOS Technology for Timing application in Pixel Detectors

Candidato: Lorenzo Piccolo Relatore: Angelo Rivetti

Controrelatore: Michela Greco

a.a. 2016-2017

# Contents

| A        | bstra                                       | nct    |                                                                                     | iv |  |  |

|----------|---------------------------------------------|--------|-------------------------------------------------------------------------------------|----|--|--|

| 1        | 4D Tracking Detector for HL-HEP Experiments |        |                                                                                     |    |  |  |

|          | 1.1                                         | HL-LI  | HC Upgrade                                                                          | 1  |  |  |

|          | 1.2                                         | The T  | TIMESPOT Project                                                                    | 4  |  |  |

|          |                                             | 1.2.1  | TIMESPOT Radiation Sensors                                                          | 7  |  |  |

|          | 1.3                                         | Electr | ronics for Timing                                                                   | 12 |  |  |

|          |                                             | 1.3.1  | Timing Metrics                                                                      |    |  |  |

|          |                                             | 1.3.2  | Overview on Timing Architectures                                                    | 15 |  |  |

| <b>2</b> | Deep Sub-Micron CMOS Electronics            |        |                                                                                     |    |  |  |

|          | 2.1                                         | MOSI   | FET Properties                                                                      | 23 |  |  |

|          |                                             | 2.1.1  | Electrical Characteristics and Working Regions                                      | 25 |  |  |

|          |                                             | 2.1.2  | Small Signal Parameters                                                             | 32 |  |  |

|          |                                             | 2.1.3  | MOSFET Noise                                                                        | 35 |  |  |

|          |                                             | 2.1.4  | Mismatch in <i>MOSFETs</i>                                                          | 37 |  |  |

|          | 2.2                                         | CMO    | S Fabrication Process and Design $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 39 |  |  |

|          |                                             | 2.2.1  | CMOS technologies                                                                   | 40 |  |  |

|          |                                             | 2.2.2  | Manufacturing Process                                                               | 41 |  |  |

|          |                                             | 2.2.3  | Design Cycle                                                                        | 43 |  |  |

|          | 2.3                                         | Scalin | g to the 28nm Technology node                                                       | 45 |  |  |

|          |                                             | 2.3.1  | Scaling                                                                             | 45 |  |  |

|          |                                             | 2.3.2  | High-k dielectric with Metal Gate                                                   | 47 |  |  |

|          |                                             | 2.3.3  | Channel Strain                                                                      | 49 |  |  |

|          |                                             | 2.3.4  | Resolution Enhancement Techniques (RET)                                             | 49 |  |  |

|          |                                             | 2.3.5  | Impact of Scaling on Analog Circuits                                                | 51 |  |  |

|          | 2.4                                         | Basic  | CMOS Analog structures                                                              | 52 |  |  |

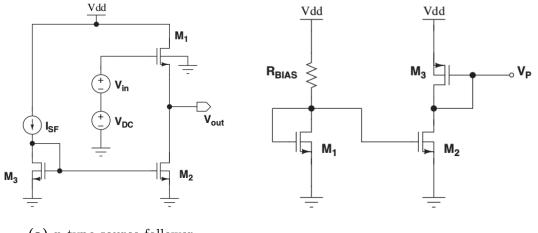

|          |                                             | 2.4.1  | Buffers and Circuit Biasing                                                         | 53 |  |  |

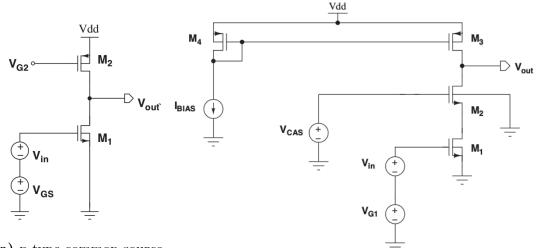

|    |                        | 2.4.2                               | Single Ended Amplification Stages                                        | . 54 |  |  |  |

|----|------------------------|-------------------------------------|--------------------------------------------------------------------------|------|--|--|--|

|    |                        | 2.4.3                               | Differential Amplification Stages                                        | . 58 |  |  |  |

| 3  | Front-End Architecture |                                     |                                                                          |      |  |  |  |

|    | 3.1                    | Overv                               | iew                                                                      | . 62 |  |  |  |

|    | 3.2                    |                                     | e Sensitive Amplifier                                                    |      |  |  |  |

|    |                        | 3.2.1                               | Core Amplifier                                                           |      |  |  |  |

|    |                        | 3.2.2                               | Krummenacher Filter                                                      |      |  |  |  |

|    | 3.3                    | Leadir                              | ng Edge Discriminator                                                    | . 75 |  |  |  |

|    |                        | 3.3.1                               | Amplification Stages                                                     | . 75 |  |  |  |

|    |                        | 3.3.2                               | Offset Correction                                                        |      |  |  |  |

| 4  | Simulation Results     |                                     |                                                                          |      |  |  |  |

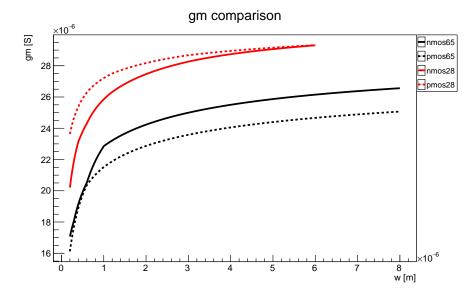

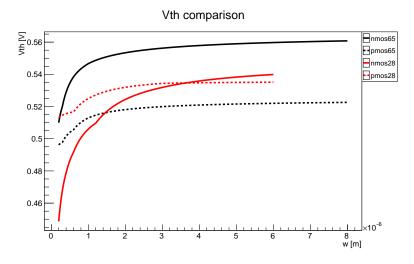

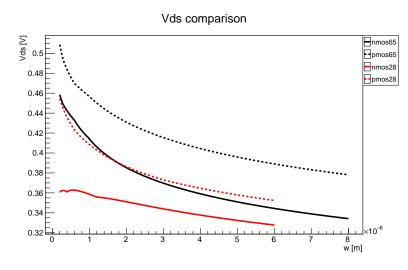

|    | 4.1                    | Comp                                | arative Technology Tests                                                 | . 84 |  |  |  |

|    | 4.2                    |                                     | Tests                                                                    |      |  |  |  |

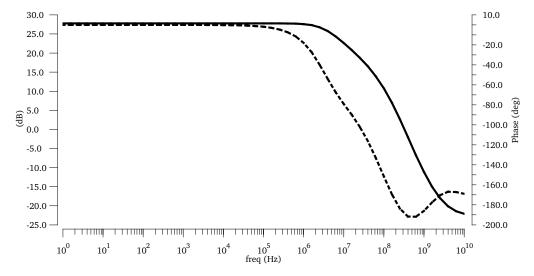

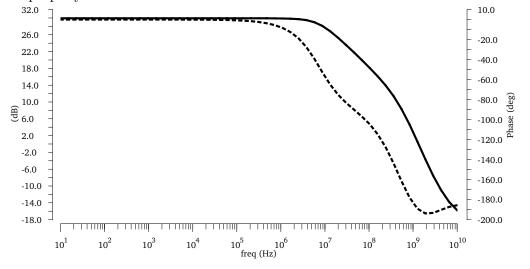

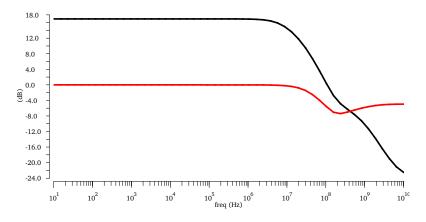

|    |                        | 4.2.1                               | Core Amplifier Transfer Function                                         |      |  |  |  |

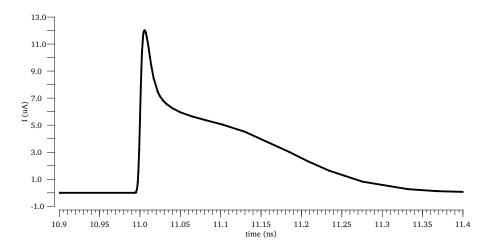

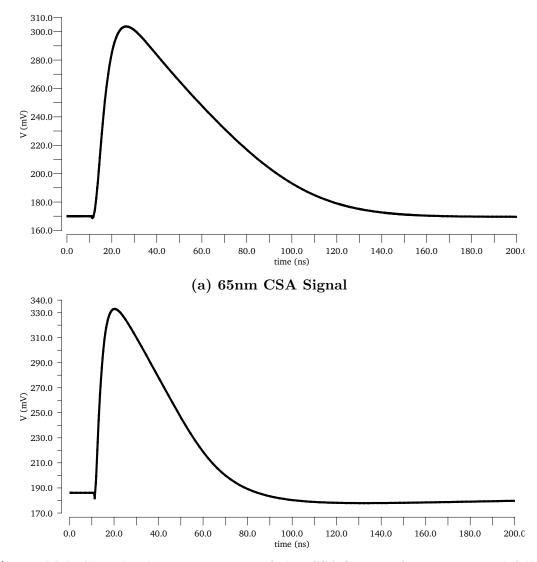

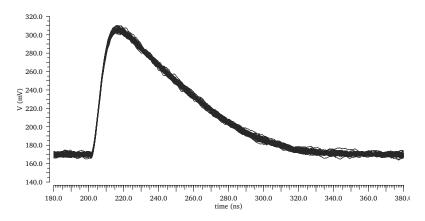

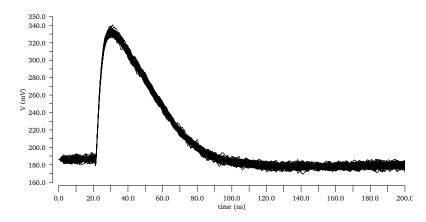

|    |                        | 4.2.2                               | CSA Signal Characteristics                                               |      |  |  |  |

|    | 4.3                    | .3 Leading Edge discriminator Tests |                                                                          | . 91 |  |  |  |

|    | 4.4                    |                                     | $g$ Tests $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ |      |  |  |  |

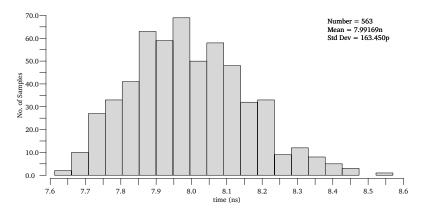

|    |                        | 4.4.1                               | Noise Contribution                                                       |      |  |  |  |

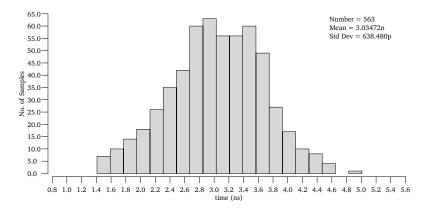

|    |                        | 4.4.2                               | Signal Variation Contribution                                            | . 96 |  |  |  |

|    |                        | 4.4.3                               | Mismatch Contributions                                                   |      |  |  |  |

|    |                        | 4.4.4                               | Time Walk                                                                | . 99 |  |  |  |

|    |                        | 4.4.5                               | Process Variations Contributions                                         |      |  |  |  |

| Co | Conclusions            |                                     |                                                                          |      |  |  |  |

| Bi | Bibliography           |                                     |                                                                          |      |  |  |  |

High Luminosities (HL) upgrades planned at the Large Hadron Collider (LHC) will pose strict requirements for High Energy Physics (HEP) experiments. Future vertex detector systems need to combine pixel dimensions of  $100\mu m \times 100\mu m$  or smaller with time resolution below 100ps in order to obtain satisfying tracking performance and prevent event pile-up. Moreover these detectors will have to sustain radiation doses of  $10^{17} MeV/cm^2n_{eq}$  in magnitude.

In this work an analog CMOS front-end architecture for pixel detectors which satisfies these requirements is proposed. This front-end will be part of TIMESPOT project, a national initiative by INFN. The project aims to develop an integrated solution for a tracking detector that meets HL HEP requirements; therefore sensors, front-end ASIC and back end electronics will be developed as part of it. As a consequence of this, the studied analog front-end design must take into account the need to be interfaced with other system's blocks.

To achieve this, the work was done in coordination with other TIMESPOT working groups. For the scope of this thesis, such coordinate effort was done mainly with sensors developing groups.

Pixel detectors electronics pose many design challenges: low power consumption, high signal-to-noise-ratio, radiation hardness and small chip area. Furthermore the timing requirement of 100ps resolution demands robust design against process variations.

The target pixel pitch was chosen to be  $55\mu m \times 55\mu m$  so, to integrate all required features, a 28nm technology node was chosen for the front-end electronics. In order to efficiently design the front-end in this advanced deep sub-micron technology, characterization studies where done beforehand.

The work was carried out using industry standard tools and methodologies for design, simulation and layout of CMOS integrated circuits. Technologies libraries provided by manufacturer were employed in circuits simulation and process variation impact evaluation.

The thesis initially introduces HL-LHC challenges, the TIMESPOT project and its sensors in chapter 1, electronics techniques and architectures for timing are also illustrated. Chapter 2 illustrates the most important characteristics of these technologies by the means of electronics mathematical models and technologies details with a particular interest in deep sub-micron CMOS technologies. Chapter 3 illustrates the designed architecture and discuss the various optimizations adopted in this work. In the end, in chapter 4, both results on a preliminary design in 65nm and the final 28nm version are presented and compared. In these analysis particular attention is paid to timing performance.

## Chapter 1

# 4D Tracking Detector for HL-HEP Experiments

The studied front-end architecture with timing measure is part of the *TIMESPOT* project, its goal is to produce a 4D tracking system for *High Luminosity* (*HL*) accelerator experiments. In this chapter firstly, in section 1.1, motivations and requirements of *HL* experiments are briefly illustrated, with a particular focus on *HL-LHC* expansion. Then the *TIMESPOT* project is presented in 1.2, explaining its organization, systemic approach and the role of the front-end electronics in it. In 1.2.1 the work in progress realization of the two 3D sensor considered in *TIMESPOT* are presented due to the strict connection between their design and the front-end one. Finally in 1.3 timing metrics and architectures are presented, their feasibility in respect of the desired front-end is also discussed.

## 1.1 HL-LHC Upgrade

*CERN* (Conseil Européen pour la Recherche Nucléaire) is the world leader organization in *HEP* (*High Energy Physics*), this is the result of an international collaboration including countries from *ERA* (*European Research Area*), US, Japan and many others.

Its collider, the *LHC* (*Large Hadron Collider*) in Geneva, enabled experiments to obtain remarkable results on the verificating of the standard model, like Highs boson discovery in 2012. It provided to 10000 *LHC* users (7000 scientists and engineers among them) proton-proton collisions of 7 TeV of energy in centre-of-mass. Through the years this energy was increased reaching 8 TeV in centre-of-mass in 2013.

The future interest of *CERN* is to go beyond the standard model that is to verify

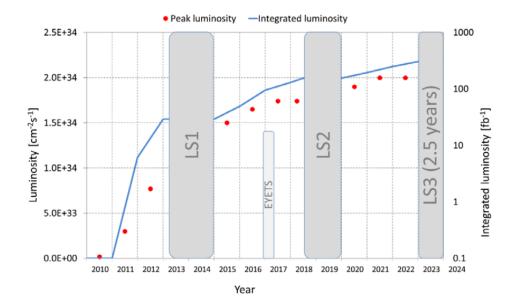

Figure 1.1: Planned LHC luminosity upgrades thorough the next years, taken from [1]

or disprove supersimmetric theories or search to acquire proof on the existence of dark matter. In order to fulfill these goals a major upgrade is needed: an increase of the luminosity, and thus of the collisions by a factor of five beyond its design value. For this reason the upgrade project of LHC is called HL-LHC (High Luminosity-LHC) [1].

With the usual upgrade programs, running the accelerator will become marginal due to statistical error: 10 years of data acquisition would be required only to have the statistical error. For this reason *HL-LHC* would pose the ambitious goal of achieving a 3000  $fb^{-1}$  of integrated luminosity in a dozen of years, all at the nominal energy of 13-14 TeV in centre-of-mass, which corresponds to  $\times 10$  of the design integrated luminosity value. But, in order to reach 3000  $fb^{-1}$  with a 50% margin in effective data acquisition in full operation, the peak luminosity needs to be pushed to  $7\div 7.5\times 10^{34}cm^{-2}s^{-1}$ . The upgrade program of the next years is presented in fig.1.1.

Reaching this goal would mean to fully exploit the *LHC* facility, it requires  $300 \div 350 \ fb^{-1}$  per year, which corresponds to a peak luminosity of  $5 \times 10^{34} cm^{-2} s^{-1}$ . The project started in 2010 and it entered in the nominal energy regime in 2015, with a luminosity of  $1 \times 10^{34} cm^{-2} s^{-1}$  (40  $fb^{-1}$  per year). The timetable foresees the end of the R&D in 2025 and it will have to assure high efficiency in operation until 2035. The first upgrade of the luminosity is planned for 2022 and it aims to double the 2015 value. Experiments need to be upgraded in the mean time in order

to be ready for HL-LHC, the upgrade will range from the experiments structure to sensors, data acquisition, process and electronics.

The development of electronics for *LHC* experiments started thirty years ago and it has enabled the growth of the research field both in capacity and expertise. LHC has demanded through the years the development of many *ASICs* (*Application Specific Integrated Circuits*) with deep sub-micron *CMOS* technology (detailed in 2.2) as the baseline. *CMOS* offers good digital and analog performance and radiation hardness exceeding the requirements of the time (100 kGrey of total ionizing dose (*TID*) and  $10^{14} MeV n_{eq} cm^{-2}$ ). This technology enabled the building of the readout of high density sensor systems with low power consumption and with short connections to the sensor.

The biggest challenge for the new electronics comes from the high event rate [2]: the total foreseen pileup (number of events per bunch crossing) in the detectors will grow from 27 to 200 (the initial design value was 19). Since the bunches cross every 25ns, the expected hit rate on the inner most sensor layer will go from the present  $200MHzcm^{-2}$  to  $3GHzcm^{-2}$ , leading to an average rate of 75KHz for a pixel of  $(50 \times 50)\mu m^2$  area. To prevent signals pile-up and provide a good particle tracking, timing informations are required. To assure good background rejection timing resolution needs to be under 1ns, this can be provided by triggers signals generated by electromagnetic calorimeters, which feature sub-200 ps resolution. The expected trigger rate will be of 1MHz, requiring a data bandwidth of  $1.25 \ Gbits^{-1}cm^{-2}$ . This performance could be met by processing the trigger matching close to the front-end in order to reduce latency and by increasing the buffers in order to accommodate it. This high precision timing standard is supported also by advancement in the sensors side: new 3D-Sensors features high radiation hardness and fast and reliable signals.

New possibilities both for integrating more features and for introducing timing measure capability on pixel area are opened by the adoption of new scaled technologies below 130nm and 65nm. This new technology comes with some drawbacks and challenges: the typical scaling Dennard scaling method which consists in scaling by a certain factor both voltages and transistor size has reached its limit (discussed in 2.3). This can be seen by observing the scaling in supply voltages from 1.2V to 0.7V despite a minimum feature shrinking from 130nm to 14nm: with usual scaling methods the supply voltage would have been scaled to 130 mV instead. In order keep on the trend of a 0.7x geometrical scaling every two years many new solutions have been employed resulting in more complications in *ASIC* design.

In any case, higher densities will allow designers to make more features in pixel

Figure 1.2: Conceptual representation of 4D tracking, taken from [3]

device front-end like digital calibration circuit for analog parts or ToT (*Time over Threshold*) measures for both timing correction and charge extraction. In terms of timing performance, the time measure resolution could be brought to sub-100ps by using *All Digital TDC (Time to Digital Converters)*, taking advantage of the good scalability of digital circuits. There are already examples of *TDCs* with 20ps resolution and 1mW of power consumption at  $1M_{smaple}s^{-1}$  in 130 nm, new technologies could open the possibility of integrating one of them per pixel.

The critical factor in the adoption of all this new technologies is the *NRE costs* (*Non Recurrent Engineering*) associated with the masks (more on the manufacturing process in 2.2.2), right now 28 nm processes are becoming cost effective and will represent the target technologies for electronics for pixel sensor detectors.

## 1.2 The TIMESPOT Project

The TIMESPOT (*TIME and SPace real-time Operating Tracker*) project by INFN aims to overcome the *HL-LHC* challenges with a systemic approach, it proposes to research and develop a demonstration prototype of a complete 4D tracking system with  $(55 \times 55) \mu m^2$  space resolution and at least 100 ps time resolution [3].

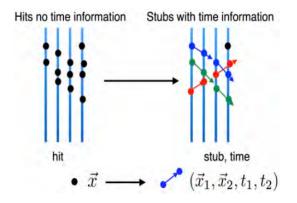

The 200 event pileup in future HL experiments is expected to increase the probability of ghost-tracks (from spurious hits) from 1.6% to 40%, thus damaging total tracking efficiency which is expected to reduce from 99% to 96%. For this reason high granularity and time resolution are essential to restore the tracking efficiency: the tracking algorithm will exploit *stubs*, namely timing track at detector level (illustrated in fig.1.2). This process is essential for background rejection, but in order to make it effective both sensor and front-end would need to be fast and precise, while the tracking system needs to receive and process  $Tbs^{-1}$  of data. For these reasons the proposed solution is conceived as a system: every block needs to be optimized in conjunction with the others.

The system will be composed of:

- A high speed, high granularity and rad-hard 3D solid-state pixel sensor. The pixel pitch would be of  $(55 \times 55) \mu m^2$  with resolution inferior to 100 ps. Two variants would be investigated: a silicon 3D sensors and diamond based one. Details on these sensors are presented in 1.2.1.

- A 28 nm CMOS front-end with timing measure capability. A dedicated analog chain will be designed for each sensor, considering the fluctuations that this step will add to signal, its design must be done in interplay with the ones of the sensors. Ideally every pixel will have its own 100 ps TDC. Every pixel will even integrate the digitization and eventual digital signal processing circuits.

- A real-time 4D tracking board: it will use a custom parallel track processor based on pattern matching with stored pre-calculated events in order to avoid combinatorial means. The board could implement this using FPGAs. An associative memory banks layer could be used as a first step producing a veto condition that will reduce the data bandwidth that needs to be processed. The process needs to be in real-time in compared to the 40 MHz bunch-crossing and it must be able to process 1  $Tbs^{-1}$  of data.

To reflect this characteristic, the project is divided in 6 work packages (WP) across 10 INFN centers, it aims to develop in conjunction this 4D tracking system:

(WP1) 3D silicon sensor design and characterization

(WP2) 3D diamond sensor design and characterization

(WP3) front-end design with timing capability

(WP4&5) high speed read-out boards for real-time tracks reconstruction

(WP6) assembly of a working small telescope prototype called *Timespotter*, featuring at least 4 fully equipped tracking layers, high speed data tracking and real-time processing.

The research and development of the various elementary blocks will start as an optimization process of consolidated technologies, where the final goal is to produce

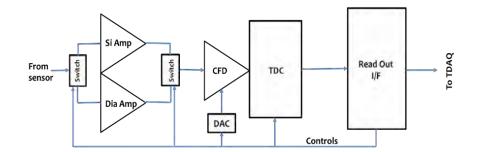

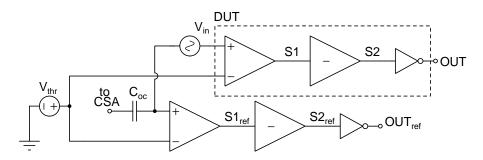

Figure 1.3: Block-diagram representation of the tentative front-end architecture, taken from [3]

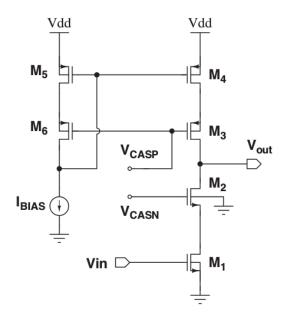

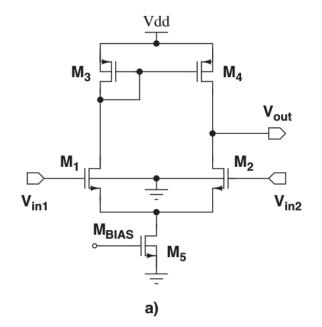

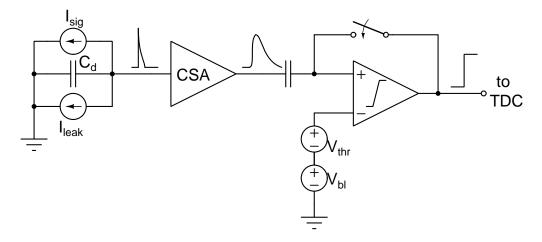

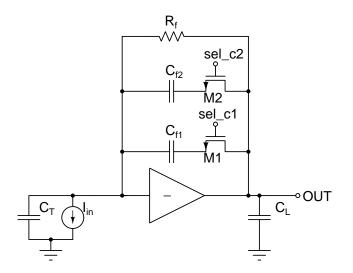

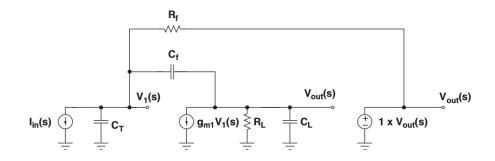

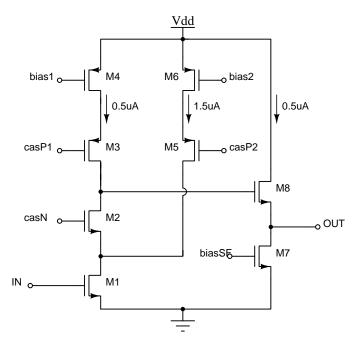

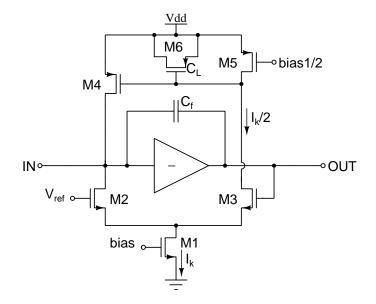

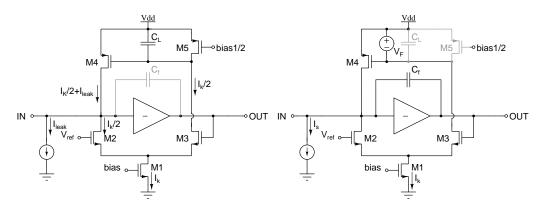

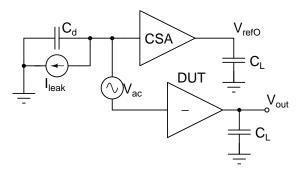

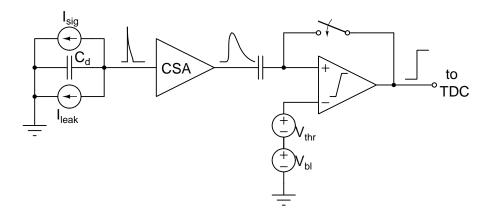

a scale down prototype to demonstrate the feasibility of the system. The prototype will be scaled down in the number of channels but not in its features: it will be a complete tracking system. The first phase of the research will be focused on the first three WP and it will produce and study both the two type of sensors and essential elementary blocks of the front-end. This preliminary work will end in 2018 with the individual test, characterizations and debugging of these blocks. In the second phase in 2019 a fairly large pixel matrix, fully integrated, bonded with the sensor will be studied. A tentative architecture of the first part of the front-end is represented in fig.1.3. The first amplification stage could be exclusive for the two sensors due to their intrinsic differences (sensor capacitance, SNR, signal amplitude). The plan is to integrate both core amplifiers on pixel. Two Architectures were investigated: a fast but noisy amplifier-shaper architecture or a slower but with less noise Charge Sensitive Amplifier (CSA) architecture. The discrimination stage, essential to produce the digital signals triggering the timing measure, must be compact while not degrading the performance because of time-walk: a Constant Fraction Discriminator (CFD) is a possibility along with a Leading Edge Discriminator with ToTcorrection (details in 1.3). Finally an All Digital TDC will digitize the timing difference between the signal and the reference LHC bunch-cross clock with at least 100 ps LSB. The digital architecture is selected due to its optimal scaling to modern digital-oriented technologies. In case integrating a per pixel TDC will results unfeasible, the possibility of shared TDCs among 4 or 8 adjacent pixels will be explored. Assuming a natural scaling of a previous 130nm synthesis-able 200 ps architecture the area occupation could be of  $(20 \times 30) \mu m^2$ . In the end all this blocks will reside in the  $(55 \times 55) \mu m^2$  pixel area.

The subject of this work is the very first analog part of this front-end, these structures are among the one that will be manufactured and individually tested within the end of 2018 in a test chip. The selected amplifier architecture is the CSA one, as for the discriminator a compact leading edge one is initially studied in order to evaluate the discrimination performance, the impact of time-walk and the feasibility of ToT correction. This architecture will be discussed in chapter 3.

The implementation of a front-end with per-pixel sub-100 ps timing measure capability represents a novelty in *HEP* experiments: the best results in timing performance are represented by: the *TDCpix* for the *NA62 Giga Tracker* which features a  $300\mu m$  pitch with 150 ps resolution obtained by multiplexing one 75 ps *TDC* for 1800 channels (not tailored for *HL*) in a 130nm technology node; and by *Timepix3*, developed at *CERN*, with a pitch of  $55\mu m$ , 1ns resolution with one *TDC* per 8 channels, in 130 nm.

### 1.2.1 TIMESPOT Radiation Sensors

Radiation sensors convert part of the energy deposited by an incident particle in an electrical signal. In the case of considered family of detectors, the signal is a current pulse whose integrated charge is the one created inside the bulk of a semiconductor thorough ionization. The development of the current signal is due to the induction on a metallic electrode caused by the motion of the mobile charge carriers created during ionization, namely electrons and holes. This is the drifting motion under the effect of the electrical field imposed by a bias voltage applied to a biasing electrode. The instantaneous current  $I_k$  induced on an electrode by a charge q can be expressed using the *Ramo Theorem* [4]:

$$I_k = -q\vec{v_d} \cdot \vec{E_w}(\vec{x}) \tag{1.1}$$

Where  $\vec{E_w}(\vec{x})$  is called *weighting field* and it corresponds to the field generated by setting the potential of the specific electrode to 1 and the one of all others to 0. This field defines only how the charge couples with the electrode and it depends only on the geometry of the system. Charge velocity, and thus its trajectory, depends on the actual electrical field  $\vec{E}$  thorough the *drift velocity*  $v_d$ :

$$v_d = \mu E \tag{1.2}$$

Where  $\mu$  is the carrier mobility. This is true in case of velocity saturation: electrical field needs to be sufficiently intense to satisfy this condition (typical values exceed  $10^4 V cm^{-1}$ ). It should be noted that  $\frac{\vec{E}(\vec{x})}{|E(\vec{x})|} = \vec{E_w}(\vec{x})$  only in two-electrodes systems. Both type of carries contribute to the total current in the same direction since both

their charges are opposite in sign but at the same time they will drift in opposite directions. The duration of the signal is the one required to collect all the carriers inside the metallic electrodes: once inside the metal volume, the total charge induced by them equals zero.

The first consequence of this fact is that the shape of the current pulse depends on the shape of the charge development inside the volume: electrons and holes contribution will last as long as they reach the respective electrode which is given by their distance from them and their drift velocity (note that electrons and holes have different mobility). This constitutes an uncertainty on the timing of the signal.

There are other sources of fluctuation of the signal: the number of pairs crated during the particle interaction, the possibility of carriers trapping due to impurities on the material and the delta-ray effect (production of a secondary electron far from the primary interaction which can itself ionize the material).

One last cause of uncertainty is the eventual presence of low-field zones which makes the velocity saturation condition no more true.

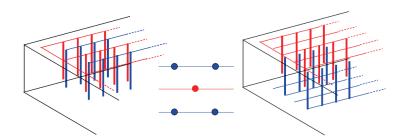

The adoption of 3D sensors for timing detectors is driven by their capability to mitigate most of these effects and thus to produce more reproducible signals: standard 2D sensors present the electrodes arranged on the surface of the material, while in the 3D ones they penetrate inside the bulk volume. This sensor geometry, compared to the flat one, makes it possible to put the electrodes close to each other (inter-electrodes distances  $< 70 \mu m$ ) without reducing the sensitive area, preserving the sensor efficiency and improving the charge development. With depth  $> 200 \mu m$ more electron-hole pairs can be created, thus increasing the signal strength. Furthermore the shorter electrodes distance allows to reach the desired electrical field strength with a smaller bias voltage.

In terms of signals reproducibility, electrodes proximity brings many advantages:

- for perpendicularly incident particles the absolute signals length variation for the opposite extreme cases (adjacent to the electrode of one polarity versus the other) is reduced.

- the inter-electrodes distance  $(L_e)$  could be made small compared to the carriers mean free path due to trapping, reducing the overall trapping probability.

- $-L_e$  can be even made shorter than the delta-ray creation distance, eliminating the contribution from this effect

The higher presence of low-field zones due to border effect caused by the tips of the electrodes (usually column like shaped) is the main disadvantage in terms of time

resolution of 3D sensors. The current pulses from these cases presents a long decay tail. However this contribution can be minimized acting on the electrodes geometry: reducing the relative low-field volume making the charge formation in that zone less frequent or making the field variations less prominent in order to make the timing difference lower.

Another advantage of 3D sensors which makes them preferred solution for HL experiments is their intrinsic radiation hardness: the principal radiation damage is the creation of defects inside the crystal which act as traps, both the lower required bias voltage and the short inter-electrodes distances mitigate the contributions.

However 3D sensors present generally more capacitance since electrodes and the sensible area forms a capacitor with small distance between plates. As a consequence, the sensor-amplifier system becomes slower and with a smaller SNR.

As a consequence of these aspects, in order to obtain the desired resolution of 100 ps, front-end and sensor must be optimized together: solutions for the sensor signals fluctuation can introduce a problem for the analog signal processing on the very first-end, trade-offs between the two part must be considered. As detailed in chapter 4, in order to tackle this need, simulations during design phase of the frontend were performed on signals derived from simulations of the sensors, enabling, when necessary, work in progress adjustment to both blocks.

In the following sections characteristics of both 3D sensors realization investigated for *TIMESPOT* project are detailed.

#### Silicon 3D Sensor

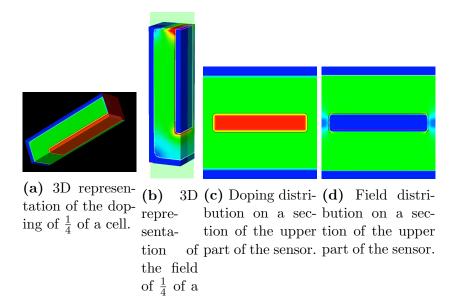

The silicon based sensor will be designed by INFN Trento [5]. Its dimension are  $(55 \times 55 \times 100)\mu m^3$  with a trench shaped  $(6 \times 45 \times 75)\mu m^3$  central signal electrode and  $6\mu m$  wide bias electrodes, parallel to the signals ones, which separates the cells along one axes (presented in fig.1.4a and fig.1.4c). The substrate is  $p^{--}$  doped (weakly doped with acceptors), while the signal electrodes are  $n^{++}$  (highly doped with donors) and the bias ones are  $p^{++}$  (highly doped with acceptors). At the bottom of cells  $3\mu m p^{++}$  layer. The bulk silicon is  $p^{--}$  due to its radiation-resistance properties.

Many geometries were tested, the selected one features the most uniform field obtained (represented in fig.1.4b and fig.1.4d): there is a low filed area along two adjacent  $n^{++}$  electrodes which correspond to the 1.5% of the area of a section of the electrode (fig.1.4d); another low-field is at the bottom of the cell under the tip of the electrode(fig.1.4b), this accounts for the 10% of the total 3D volume.

The manufacturing process used consists in etching the silicon bulk with Deep

**Figure 1.4:** 3D silicon sensor dimensions. The doping is represented from  $red(n^{++})$  tu  $blue(p^{++})$ . The field is modulus is represented with blue to green for low field to high field values, biased with 100V.

cell.

Reactive Ion Etching (DRIE) and then doping the holes with desired atoms. These holes are then filled with polysilicon in order to create the ohmic contacts, this process is the one limiting the smallest electrode that can be produced: filling reliably these holes become difficult the smaller their section. At the same time making electrodes excessively large will reduce the active area, reducing the efficiency. To use this process a support wafer is needed: a  $SiO_2$  layer is used and than removed with a further step. On this back surface the bottom  $p^{++}$  doping is realized: since the bias electrodes passes through the whole bulk layer reaching the previously removed  $SiO_2$  layer, the bias voltage can be directly applied to the newly formed  $p^{++}$ layer. Attention has been kept to the distance between the  $p^{++}$  layer and the  $n^{++}$ electrodes since a too thinner ones cause low sensor break-down voltages.

The sensor thickness, and thus the electrodes length, is limited by two factors: the sensor capacitance  $C_d$  increases with the electrodes depth and the poly filling becomes less reliable. In any case due to the shape of this sensor resembling the one of a parallel plate capacitor its  $C_d$  is fairly large:  $\sim 100 fF$  (including the front-end connections).

The front-end connection will be made my bump bonding directly on the top surface of the sensor.

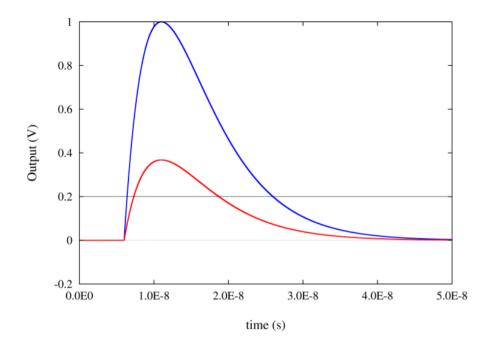

Simulations of this sensor were performed by INFN Cagliari, providing informa-

Figure 1.5: Schematic representation of the electrodes positions in the diamond sensor for both one and two-sided variations, taken from [6]

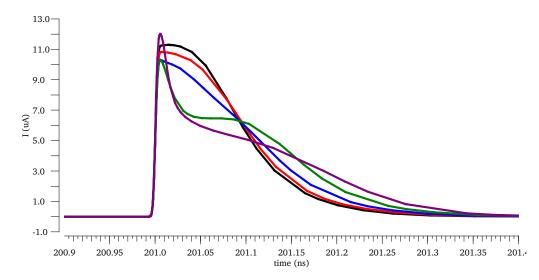

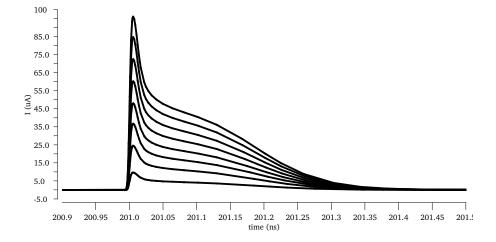

tion on field distribution and on the expected signal. The simulation set up was: bias voltage set to 100V and uniform 1.2 fC linear charge development perpendicular to the top surface. The expected signals are expected to have a current peak of  $\sim 10\mu A$  and duration < 300 ps. There are plans for future analysis on different angles of incidence and non uniform charge distributions calculated with a radiation-mater interaction software (GEANT4 from *CERN*).

#### Diamond 3D Sensor

The 3D diamond sensor is designed by INFN Firenze [6][7] and modelled and characterized by INFN Perugia.

It consists in graphite electrodes inside a CVD (*Chemical Vapor Deposition*) made polycrystalline diamond. The bulk is made with hetertoepitaxial growth on top of iridium, it is a low cost solution enabling the formation of samples with a  $(2 \times 2)cm^2$  area and 500  $\mu m$  thickness.

The columns shaped electrodes are made by direct graphitization of the diamond using pulsed laser along the beam focus, a technique originally used for optical application. To trigger the transformation process, the laser energy density per pulse must exceed  $5Jcm^{-2}$ . Columns shaped electrodes with a diameter of 9 to 10  $\mu m$  can be produced. Two different lasers were employed: a 8ns Nd:YAG, the other 30fs Ti:sapphire. Different results are met depending on the laser used: ns one has low collection efficiency but low resistivity, while the fs one has higher resistivity ( $60k\Omega$  versus  $4k\Omega$ ). Raman spectroscopy suggests the presence of sp3 bonds on the electrodes surface as an explanation of ns low efficiency. Multiple steps gratifications can be employed to enhance the electrodes properties, but it is time consuming.

The diamond is naturally a good material in terms of radiation hardness, and it seems to improve after irradiation. It even presents high uniformity, and is polarized with 100V bias. The resulting signal is weaker than the one of silicon detectors, bu the sensor presents better SNR and lower capacitance.

The fabrication technique allows to freely trace 3D structures, the one proposed is formed of hexagonal combs in which the center and vertex electrodes are oppositely polarized (fig.1.5). This creates an interdigitated structure in which the electrodes can be connected to the surface by creating paths to the surface. Connection can be made on either of two top and bottom surfaces opening the possibilities for one or two-sided sensors, however the actual bonding mechanism with silicon is yet to be decided: the two solutions are direct diamond-silicon connection using the laser or metallic bump bonding.

### **1.3** Electronics for Timing

A timing measure is a value proportional to a timing interval, in most of cases this is the time elapsed between a reference event and the measured one. This section will present the main methods used to extract a timing measure from an electrical signal in order to convert them in a digital number. First, in 1.3.1, some useful timing metrics used in electronics are presented. In 1.3.2 some electronics architectures are illustrated, their feasibility in the context of *CMOS* technology for pixel sensors is also discussed.

### **1.3.1** Timing Metrics

#### Single Sample

The time information can be taken from sampling the signal in a predefined condition of its value. A typical condition is a threshold crossing in a certain direction. The absolute time information is the elapsed time from a well defined event, which can be measured in the same way. Good reference signal must be periodic, stable and will allow a precise measurement of the condition event. An example which is often found in electronics is using a steep rectangular-shaped digital signal with a certain periodicity, where the crossing of a certain value of its steep rising or falling edge is used as the time reference.

The simplest example of method which provides the extraction of timing event from an analog signal is the *Leading Edge Discriminator*. With this method a digital pulse is produced with its value (ideally) instantaneously transitioning on the first threshold crossing of the signal. Threshold value and the direction of its crossing must be decided based on the signal characteristics like polarity, base line value and noise. As for the noise, the statistics of the signal must be even taken into account: in order to avoid false crossing-event the threshold must be put at level far from the noise one. In case of normal distributed noise, the threshold must be kept at a level which makes the rate of spurious crossing-event below the desired value. In any case the noise is superimposed to the signal, thus for real signals with finite non-instantaneous rising times, the signal leading edge will be disturbed creating the so called *jitter* ( $\sigma_t$ ). Approximating linearly the rising profile, with a peak value  $V_p$  and rising time  $t_r$ :

$$\frac{dV}{dt} \sim \frac{V_p}{t_r} \tag{1.3}$$

And considering a noise voltage amplitude  $\sigma_V$ , the jitter can be computed as:

$$\sigma_t = \frac{\sigma_V}{\frac{dV}{dt}} = \frac{t_r \sigma_V}{V} = \frac{t_r}{SNR}$$

(1.4)

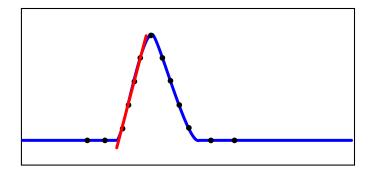

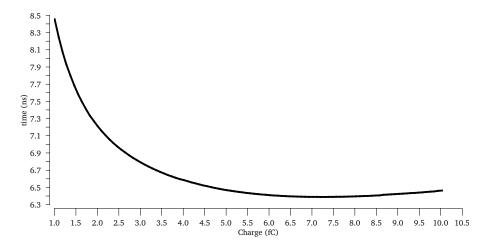

When the desired event to be measured is the starting of the development of the signal on the base line, the threshold cannot be positioned close to the baseline due to noise triggering. Selecting the threshold to an higher value may not be an applicable solution because of signal nature: if the slope is not constant for every signal the delay time between this event and variation from the baseline will not be constant to. In case of the signal presenting constant rise time (typical of bandwidth constrained amplifiers often used in particle detectors as the *charge sensitive amplifiers*) but variable peak values, the threshold is crossed at a different time in respect to the amplitude of the signal. This undesired effect is called *time-walk* and is depicted in fig.1.6. Calling m the ratio between the amplitude of two signals:

$$t_c = \frac{V_{thr}}{d_t V} = \frac{V_{thr} \cdot t_r}{V_p} \Rightarrow V_{p2} = mV_{p1} \Rightarrow t_{c2} = \frac{t_{c1}}{m}$$

(1.5)

As it can be noted, the time-walk has an hyperbolic relation with the amplitude increase.

With these signals of this type, the jitter is related to the amplifier bandwidth (BW), in fact knowing that  $BW \propto \frac{1}{t_r}$  and  $SNR \propto \frac{1}{\sqrt{BW}}$ :

$$\sigma_t \propto \frac{1}{\sqrt{BW}} \tag{1.6}$$

The time-walk constitutes a systematic error which, in case of it being relevant in magnitude, it must be accounted and corrected. If the signals amplitude is known

Figure 1.6: Example of time-walk on a signal with constant rising and falling times.

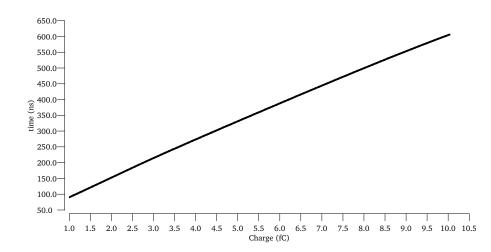

from other measures it will identify the time-walk contribution on the time measure. A method which, under certain assumptions on the signals shape, can uniquely identify the signal amplitude exploiting another time measure is the *Time over Threshold (ToT)* corrections. The ToT is the time in which the signals stays above (or below depending on its polarity) the threshold: two crossing events measures of opposite direction are needed. This value can be used to correct the time-walk only in the case the relation between  $V_p$  and ToT is known and unique. Assuming (as in the case of the proposed amplifier detailed in 3.2) that both the rising and falling time are constant, the relation between amplitude and ToT can be found. If threshold level is in a constant slope region in both crossing times the relation is expected to be linear.

#### Multiple Samples

The desired timing information of a signal can be extracted by sampling the slope of the signal at different times, if the shape of signal is known. Fig.1.7 depict this method. The advantage of this approach is that, for an infinite number of samples, it tends to cancel the random contribution of noise. Since the noise contribution to every sample is independent, sampling the signal N times will reduce the previously

Figure 1.7: Example of multiple samples take on a signal

obtained relation by:

$$\sigma_t = \frac{t_r}{SNR} \frac{1}{\sqrt{N}} \tag{1.7}$$

This can be expressed by the sampling frequency  $f_s = \frac{1}{t_s}$  knowing that the number of samples into the rising edge of the signal equals  $N = \frac{t_r}{t_s}$ :

$$\sigma_t = \frac{1}{SNR} \sqrt{\frac{0.35}{BW \cdot f_s}} = \frac{1}{SNR} \sqrt{\frac{1}{3 \cdot f_{-3dB} \cdot f_s}}$$

(1.8)

Where BW is the bandwidth of the amplifier, therefore oversampling is needed to reduce significantly the jitter.

Although, in order to obtain a high sampling frequency and measure, the signal value both a high frequency ADC is needed. This circuits takes large chip areas and will be really power hungry operating at the velocity requested for the application: the signal can't be made too long in order to avoid pile-up due to high event-rate. It results, from these considerations, that oversampling the signal is not a solution for timing pixel detectors for high luminosity HEP experiments.

#### **1.3.2** Overview on Timing Architectures

In this section various architectures, which can be employed in this specific case, are briefly illustrated. This is a block-diagram level description and not a practical CMOS realizations. First the two main candidates as discriminators are discussed, then an overview on various *Time to Digital Converter (TDC)* is presented.

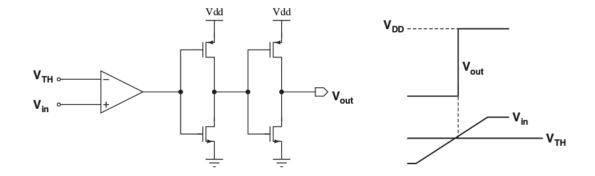

#### Leading Edge Discriminator

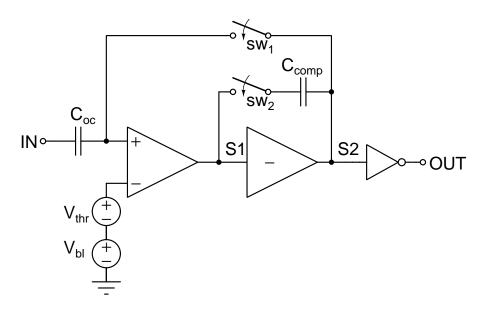

The intended operation of this circuit is discussed in the previous section. Fig.1.8 illustrates the block scheme of the simplest architecture and its ideal response. The depicted ideal behavior is compromised by the limited gain and bandwidth of the amplification stage: in fact only with infinite gain and BW a zero rising time for the output signal can be obtained. With a finite gain, the output signal slope will retain some information of the input one, making the delay time dependent on the signal slope in the proximity of the threshold. The BW limitation will, in case of infinite gain, make the delay time equal to the slew-rate of the amplification stage.

A leading edge discriminator is generally composed by a differential high gain amplification stage that sens the threshold crossing and amplifies resulting in a steep signal. It is then followed by a digital buffer which produces the desired digital signal.

The amplification stage can be composed of many lower gain stages for two principal reasons:

- Making a single high gain differential stage in CMOS is impractical, so a two stage configuration with a single ended high gain stage can be the preferred solution.

- Generally, in CMOS technologies, making a high stage gain will reduce its bandwidth creating a gain-bandwidth trade off. This situation can be avoided by making many low gain stages, sized so that the BW will be little compromised, but obtaining the same total gain. Therefore this method is used to obtain fast discriminators.

It must be said that fast discriminators, due to the big number of requested stages, tend to be large an power consuming. So they are not an option for the desired front-end.

In any case, this simple type of discriminator is used as a basic building block for more complex ones.

#### **Constant Fraction Discriminator**

As the name suggests, Constant Fraction Discriminator (CFD) is a discriminator which produces a signal when a threshold relative to the signal peak is crossed. What the user can do is to change value of this fraction of the total signal. The direct application of this discriminator is to prevent time-walk.

In order to make the process work, the assumption of a signal approximated to a triangle-shaped one, with constant rising and falling times in the entire signals fam-

Figure 1.8: Concept of leading edge discriminator and ideal signal response, taken from [8]

Figure 1.9: Concept of CFD, taken from [8]

Figure 1.10: Ideal signal response and quantization error of a TDC, taken from [8]

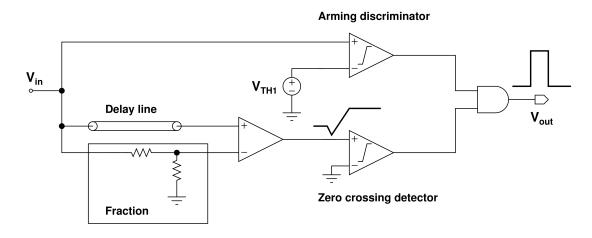

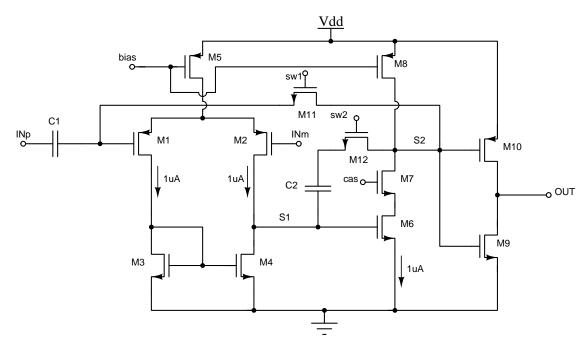

ily, must be hold. Practically, the constant fraction is realized by firstly producing a bipolar signal from the input one: the signal is delayed and then subtracted with an attenuated version of itself:

$$out(t) = in(t-d) - f \cdot in(t) \tag{1.9}$$

Where d is the amount of which the signal is delayed and f is the attenuation factor. The zero crossing point of this signal happens when a certain fraction of the signal is reached, for every signal, so a zero crossing discriminator is used to trigger the condition. An arming discriminator is then used to vetoing the noise-trigger from this last discriminator. Fig.1.9 illustrates this architecture.

The fraction can be implemented with a simple resistive partitioner. As for the delay, it can be realized with passive filtered line [9]. Although a passive implementation is difficult to implement with deep-submicron CMOS technologies due to their limited voltage headroom (discussed in 2.3.5) the big area occupation of capacitors and resistors.

Figure 1.11: Concept of an Analog TDC using the voltage across a capacitor charged by constant current source as TAC, taken from [8]

#### Time To Digital Converter (TDC)

*TDCs* are a family of electronics device which directly digitize a timing interval. The input signal can be structured as a time displacement between two well defined steep signals, or a single rectangular signal which holds a certain state (ad example a voltage value) for the time period that will be measured.

Since a TDC is a digital converter it will produce a set of discrete values which the minimum one (represented by its LSB) defines the best resolution achievable by the system. The absolute timing value that corresponds to the LSB depends on the mechanism used to discretize the timing interval, the various TDC architectures differentiate one to the others on the base of it. As for the number of bits used, they are not upper limited, but they are usually constrained by circuit complexity, area usage, time required to complete the measurement and power consumption. For this reason the resolution can be expressed (for linear converters) by the largest timing interval measurable (range  $T_r$ ) divided by  $2^{N_b}$ , where  $N_b$  is the number of bits. In fig.1.10 the ideal signal response of a TDC with its quantization error is presented.

However non-linearities in the conversion procedure can reduce the resolution within the range. For this reason the average resolution of the TDC can be expressed by using its effective number of bits  $(ENOB \leq N_b)$ . This number is reduced as well by the sensibility to the noise of the conversion. The non linearity of a system is usually represented by the Differential Non-Linearity (DNL):

$$DNL = \max_{1 < i < 2^{N_b}} \left[ \frac{t(i) - t(i-1)}{t_{LSB}} \right]$$

(1.10)

Where  $t_{LSB}$  is the ideal minimum time step. The DNL is usually presented in units of LSB. So, in order to create a high resolution TDC, a fast, linear and low noise sensitive technique needs to be exploited.

Figure 1.12: Example of gated ring oscillator, taken from [8]

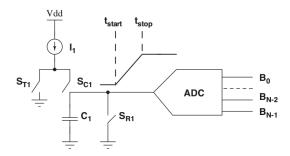

There is a grate variety of TDC architecture, but mainly they are divided in two groups: Analog TDC and All Digital TDC. Devices of the first category digitize a time difference which was previously converted in an analog (voltage or current) signal with a TAC (Time to Analog Converter), and the digitized with an ADC. Fig.1.11 shows an example of an Analog TDC: when the start signal arrives,  $S_{C1}$  is opened and  $S_{T1}$  is closed, in this way  $I_1$  starts charging  $C_1$ ; when the stop signal arrives the ADC starts converting the voltage; when the conversion is completed  $C_1$  is discharged using  $S_{R1}$ . Resolution and conversion time depend on the ADC properties constituting the two major drawbacks of this family of TDCs.

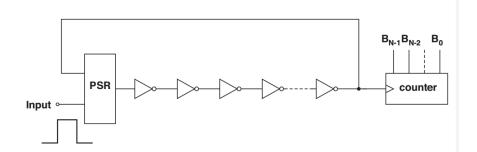

The second TDCs category is the so called *Fully Digital TDC (FD-TDC)*, this type of TDCs directly digitize the time interval. A first idea could consists in simply counting a high frequency clock, but this approach has its shortcoming: even though  $\sim 10GHz$  clocks can be reliably generated, distributing reliably on a multichannel chip could be cumbersome and will dissipate a lot of power.

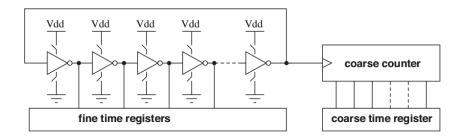

For these reasons a simple approach is to generate a clock in loco using a *Ring* Oscillator (an oscillating circuit formed by an odd number of inverters), and using its frequency as a coarse counter, while the change of state of its inverters will trigger the sampling of the status of the signal to be measured. The ring oscillator can be "gated" (making it oscillating when desired) in order to save power, the gate oscillator concept is shown in fig.1.12. These types of TDC are generally called RO-TDC, and their resolution is limited by the minimum delay inverter that can be produced in the selected technology.

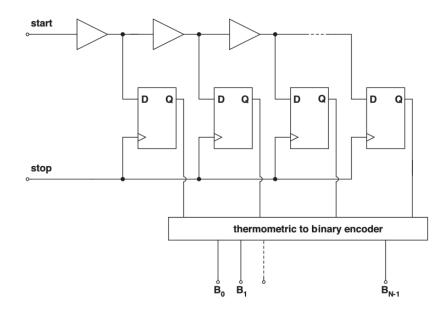

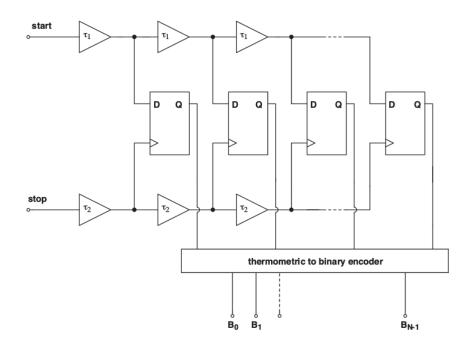

Another approach is the one of the DL-TDCs (showed in fig.1.13), based on delay lines. The simplest topology uses two rising (or two falling) edges of a signal which was previously at 0. The start signal is then delayed using voltage buffers, the stop signal is then used as the dynamic signal of DFF based registers which samples the delay line status. When the stop signal rising edge comes before the

Figure 1.13: Delay line based TDC, taken from [8]

start one, a 0 state is sampled and the measure ends. The start and stop signals must be re-setted to 0 afterward.

In this way the range depends on the length of the line resulting in a waste of chip area, in order to prevent this the delay line can be looped, counting the number of the elapsed loop will provide a coarse counter. Another modification of this topology enables to obtain an inferiori resolution to the minimum gate delay: with the *Vernier* topology (fig.1.14 both signals can be delayed by a different amount resulting in a resolution equal to the difference of the two delay times.

A last topology is the one based on *Pulse Shrinking* (fig.1.15). As the name suggests, the signal is progressively time shriked and used as dynamic signal of a DFF to the point its duration becomes so small that no more can be detected. Even this topology can be looped as the previous one.

Everyone of these topologies can be combined with a *Time Amplifier*, which stretches the timing difference between two signals, this enables to obtain high resolution using low resolution topologies at the expanse of linearity and conversion time. Two or more architectures with different resolution can be putted in stages: the less precise would take a coarse measurement, while the time difference between its measure and the signal can be measured by the more precise stage.

Figure 1.14: Vernier TDC, taken from [8]

Figure 1.15: Pulse Shrinking TDC, taken from [8]

## Chapter 2

# Deep Sub-Micron *CMOS* Electronics

This chapter aims to introduce key the aspects of analog *CMOS* electronics through its: operation, manufacturing process and design. These concepts will be later used to describe and discuss this work.

Section 2.1 is a brief recap on basic electrical characteristics of *MOSFET*'s in the designed front-ed: this is far from a complete treatise on the subject but is meant to introduce concepts to be used later.

In section 2.2 a number of technical aspects of CMOS including its manufacturing and design are illustrated. Section 2.3 focuses on the scaling to the 28nm node; the consequences on circuits design is also discussed.

The end of the chapter, section 2.4, is dedicated to an overview of various *CMOS* structures used in the actual front-end, including their mathematical small signal models.

## 2.1 MOSFET Properties

Metal Oxide Semiconductor Field Effect Transistors (MOSFET) are one of the most used and produced electronics devices in modern electronics. Their physical working principles are well known and will not be explained in this work [8], instead this section will include a brief presentation and discussion that aims to establish common terminology.

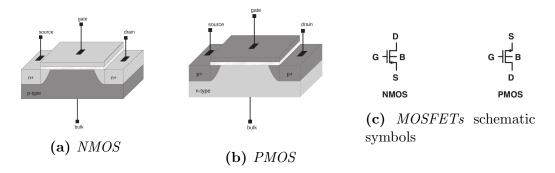

A *MOS* transistor is a device in which the current flowing in the *channel* between it's two terminals named *drain* (*D*) and *source* (*S*) is controlled by the voltage applied to its *gate* terminal (G) referred to the S terminal ( $V_{GS}$ ). There are two types of

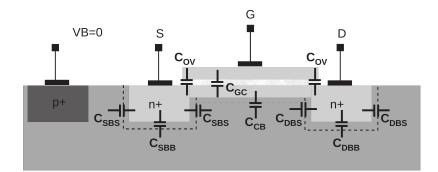

Figure 2.1: Taken from [8]

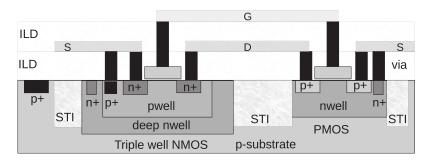

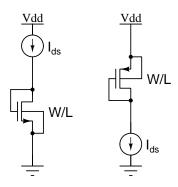

MOS transistors depending on the relation between the controlling voltage and the channel conductance, in fig.2.1c the schematic symbols for both are illustrated. In a *N*-type MOSFET (NMOS) the channel transconductance increases increasing  $V_{GS}$ , in a *P*-type MOSFET (PMOS) it increases with a negative gate-source voltage.

In fig:2.1a a representation of an NMOS device is presented. Here we can see that in NMOS the transistor bulk is made of silicon doped with acceptor atoms (called p doping, with a concentration of  $N_A \sim 10^{16} cm^{-3}$ ). On this substrate two regions highly doped with donors ( $n^+$  doping, with  $N_D \sim 10^{19} cm^{-3}$ ) which forms the drain and source of the NMOS are implanted. The channel is the zone between the two diffusions and it is insulated from the gate with an insulator usually made of silicon dioxide (SiO<sub>2</sub>). The gate itself is made of polysilicon: a ploycristalline state of silicon, selected due to its chemical affinity to SiO<sub>2</sub>. This part is also doped  $n^+$ . A fourth contact is placed on the bulk (B) in order to control its voltage.

When  $V_{GS} < 0$  the holes present inside the p-type bulk starts to migrate underneath the insulator in order to mirror the charge in the gate.

In this condition no current can flow since they form two reverse-biased junctions with the *bulk* (accumulation region). When  $V_{GS}$  raises the holes are repelled from the *channel* leaving only the fixed acceptor ions which cannot contribute to the current. When a certain threshold voltage  $(V_{th})$  is reached, an electrons layer (*inversion layer*) forms inside the channel, this charges can now drift under the effect the field imposed by  $V_{DS}$  creating the *drain source* current  $(I_{DS})$ . The same but reversed reasoning applies for the *PMOS*: the differences are that the channel carriers are holes instead of electrons and that  $V_{th}$  is negative, a representation of this transistor can be found in fig.2.1b.

MOSFET electrical characteristics are modelled on the basis of its geometrical structure and the physical properties of the materials. In particular the two main physical parameters that affect the MOSFET operation are the carriers mobility

$(\mu_n \sim 1500 cm^2/V \cdot s \text{ and } \mu_p \sim 500 cm^2/V \cdot s$ , for electrons and holes in intrinsic silicon) and the *insulator dielectric constant* ( $\varepsilon_{ox} = 3.45 \cdot 10^{-2} fF/nm$  in case of  $SiO_2$ ). The most important geometrical parameters are related to the *channel* extension (width W and length L) and the *insulator thickness* ( $t_{ox}$ , typically few nanometres). It should be noted that with L will be indicated *effective length* of the *channel*, this is the length of the insulator layer minus the portions of the diffusions that extend underneath it.

Some of this parameters are technology dependent:  $\mu_n$  and  $\mu_p$  depend on the concentration of dopants on silicon,  $\varepsilon_{ox}$  depends on the selected insulating material and  $t_{ox}$  is chosen by the manufacturer in order to avoid leakage current through the insulator.

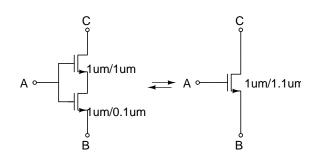

W and L, instead, can be tuned by the designer, although their values are bounded to be inside the maximum and minimum values ranges provided by the manufacturer. Of this rules the *minimum channel length*  $L_{min}$  is the one defining the technology node; the shorter this parameter is the more advanced is the technology as it allows the integration of more transistors on the same chip area.

The last aspect of the technology that must be taken into account is the fact that the *MOSFET* behavior depends on the voltages applied across its terminal; this identifies a number of working regions with their characteristics.

Through out the section electrical characteristics, small signal parameters and sources of noise of MOS transistors will be presented.

### 2.1.1 Electrical Characteristics and Working Regions

From an electrical point of view, the MOSFET operation can be divided in three main regions based on its  $I_{DS}$  current.

When  $V_{GS} - V_{th} \leq 0$  the device is in *depletion*: there are no free charge carriers on the channel thus no current can flow between D and S.

When  $V_{GS} - V_{th} > 0$  and  $V_{DS} \leq V_{GS} - V_{th}$  the device is in *linear region*: the transistor works as a voltage controlled linear resistor.

Increasing  $V_{DS}$  moves the transistor in *saturation*: here, since the maximum current is limited, the transistor operates as a voltage controlled current source. Moreover there are three sub regions based on the level of inversion of the channel: *strong*, *moderate* and *weak inversion*.

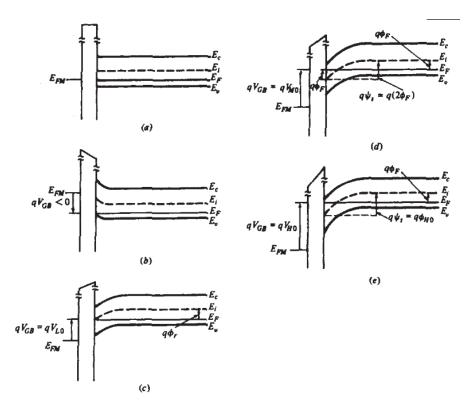

A bands diagram of the gate-insulator-channel system sowing the bands bending for different bias conditions is presented in fig.2.2.

The relation for MOSFET capacitance and  $V_{th}$  are presented in first place in order

Figure 2.2: Band diagrams showing bands banding of NMOS in various bias conditions: (a)flat-band (b)accumulation (c)weak inversion (d)moderate inversion (e)strong inversion. The three materials are respectively the ones of gate-insulator-substrate (with metallic gate).  $E_c$ ,  $E_v$ ,  $E_i$  and  $E_F$  are the energy levels of conduction band, valence band, intrinsic silicon Fermi level and the junction Fermi level. It can be noted how, from accumulation to strong inversion, the Fermi level is moved from the valence band to the conduction one. In case of a polysilicon gate, the band bending will occur even inside it. Taken from [10]

to evaluate  $I_{DS}$  relations for all the operating regions.

#### Gate Capacitance

An important quantity used in further calculations is the capacitance per unit area  $(C_{ox})$  of the insulator layer. In a first approximation it can be calculated as the capacitance of parallel plate capacitor:

$$C_{ox} = \frac{\varepsilon_{ox}}{t_{ox}} \tag{2.1}$$

Figure 2.3: graphical representation of *MOSFET* capacitances, taken from [8]

The first useful characteristics derived from this quantity is the *gate-channel* capacitance, calculated using the same approximation:

$$C_{GG} = C_{ox} WL \tag{2.2}$$

Using this value, a first evaluation of the capacitance between the *gate* and the *drain* or *source* terminals can be calculated as:

$$C_{GS} = C_{GD} = \frac{C_{GG}}{2} \tag{2.3}$$

This capacitances are the one slowing down the *MOSFET* therefore limiting the bandwidth of its transfer function. For a more precise evaluation on the *MOSFET* capacitances, more effects need to be accounted: for every junction inside the transistor creates a parallel face plain capacitor, the thickness of this parasitic element depends on the extension of its depletion region: it varies dynamically with the bias. Fig.2.3 represents the other parasitics capacitances.

#### Threshold Voltage

As previously discussed this is the voltage required to form the *channel* inside the transistor. The value of this parameter depends on the device's physical properties and on the potential applied to the *bulk* terminal. For a first evaluation its value with *bulk* and *source* at the same potential is presented:

$$V_{th0} = V_{fb} + 2\phi_F + \frac{1}{C_{ox}}\sqrt{2\varepsilon_{Si}qN_A 2\phi_F}$$

(2.4)

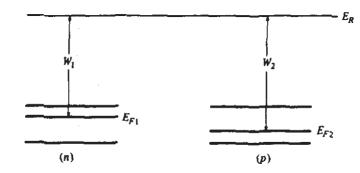

Figure 2.4: Band diagrams for the work functions of both *NMOS* and *PMOS*, taken from [10]

Where the term  $2\phi_F$  is the voltage required to neutralized the unloaded *bulk*: its value depends on the *Fermi potential* of the substrate <sup>1</sup>, therefore  $V_{th}$  depends on the temperature. The last term accounts for the voltage generated by the exposed charge of the depletion region of temporarily created junction between the electrons *channel* and the *p bulk*.

$V_{fb}$  is called *flat-band voltage*. It is the voltage required to avoid the bending of the bands inside the materials and therefore needed to obtain a uniform charge distribution. This condition of flat-band is depicted in 2.2(a),  $V_{fb}$  follows the relation:

$$V_{fb} = \phi_G - \phi_B - \frac{Q_{ox}}{C_{ox}} \tag{2.6}$$

Where  $\phi_B$  and  $\phi_G$  are the *contact potentials*<sup>2</sup> of the *bulk* and *gate* at the given temperature. In order to neutralize the device, the total contact potential of the *gate*-insulator-*bulk* structure has to be overcome. The contact potential of a layered structure like this one depends only on the external materials.

An alternative view on the subject is by the means of the *work functions*<sup>3</sup> of the materials [10]: the energy bands bending is explained by the lineup of the *Fermi levels* of the materials at the interface. Therefore the *contact potential* of the junction

$$\phi_F = \frac{E_F - E_i}{q} \tag{2.5}$$

<sup>&</sup>lt;sup>1</sup>The *Fermi potential* of extrinsic silicon is the difference between its *Fermi Level*( $E_F$ ) and the one of intrinsic silicon( $E_i$ ), expressed as a voltage:

Where q is the electron's charge. It is approximately -0.56V for n-doped silicon and 0.56 for p-doped one.

$<sup>^{2}</sup>Contact potential$ : the potential that arises at the ends of a junction between two materials

<sup>&</sup>lt;sup>3</sup> Work function: the energy required to move an electron from the *Fermi level* to the vacuum level, namely the energy required to remove an electron from the material.

can be put in relation with the materials work functions  $(W_1, W_2)$ :

$$\phi_{12} = \frac{W_2 - W_1}{q} \tag{2.7}$$

The band diagrams in fig.2.4 represents this relation for *MOSFETs*.

Another voltage that needs to be neutralized is the one given by trapped charges inside the insulator. This can be accounted for using the concentration per unit area of this charges  $(Q_{ox})$  and  $C_{ox}$ .

Finally, when a voltage is applied between *source* and *bulk*  $(V_{SB})$ , the so called *bulk effect* arises. The voltage between the contacts and the *bulk* reverse biases the *channel-bulk* junction widening the depletion region and therefore the exposed charge that needs to be neutralized. The complete expression for the *threshold voltage* is:

$$V_{th} = V_{th0} + \gamma \left(\sqrt{2\phi_F + V_{SB}} - \sqrt{2\phi_F}\right)$$

(2.8)

Where  $\gamma$  is the *bulk effect coefficient* that represents the device's sensitivity to the bulk effect:

$$\gamma = \frac{\sqrt{2\varepsilon_{Si}qN_A}}{C_{ox}} \tag{2.9}$$

Linear Region  $(V_{GS} - V_{th} > 0 \land V_{DS} \leq V_{GS} - V_{th})$

The characteristic of the MOSFET in this region is the following:

$$I_{DS|l} = \mu_n C_{ox} \left(\frac{W}{L}\right) \left[ (V_{GS} - V_{th}) V_{DS} - \frac{V_{DS}^2}{2} \right]$$

(2.10)

As it can be noted from the equation,  $I_{DS}$  behaves as a resistor for small values of  $V_{DS}$ . Intuitively, the value of the resistance can be interpreted as the one of a conductor: growing linearly with its length and decreasing with its area, hence the  $\left(\frac{W}{L}\right)$  term.

A non liner quadratic behavior is met for high  $V_{DS}$  values, this is attributed to the non uniformity of the *channel* caused by  $V_{DS}$  imposed field.

#### Saturation: Strong Inversion $(V_{GS} - V_{th} > 0 \land V_{DS} > V_{GS} - V_{th})$

In the case in which  $V_{DS}$  assumes a large value compared to  $V_{th}$ , the carriers in the *channel* can no more sustain the *linear region* trend for  $I_{DS}$ . The current value almost saturates, therefore the MOS behaves as a voltage controlled current source.

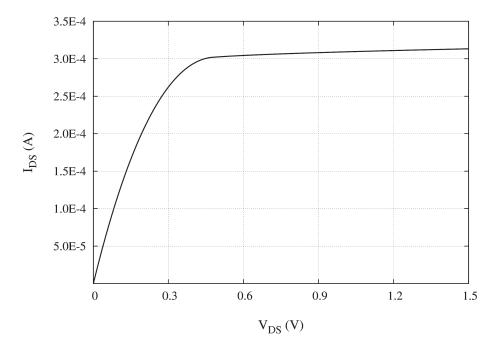

Figure 2.5:  $I_{DS}$  characteristics from liner region to saturation, taken from [8]

This characteristics is useful in analog circuits, but it must be considered in the design of circuits measures that keep the transistor in saturation.

The complete relation for  $I_{DS}$  in strong inversion is:

$$I_{DS|s} = \frac{1}{2} \mu_n C_{ox} \left(\frac{W}{L}\right) (V_{GS} - V_{th})^2 (1 + \lambda V_{DS})$$

(2.11)

The last part of the equation describes the *channel length modulation effect*: due to the *pinch-off* of the channel caused by external field of  $V_{DS}$ , the *effective length* of the channel decreases giving a weak dependence to  $I_{DS}$  on  $V_{DS}$ .

$\lambda$  is the channel length modulation effect parameter and it relates the relative channel shortening with  $V_{DS}$ :

$$\lambda V_{DS} = \left(\frac{\Delta L}{L}\right) \tag{2.12}$$

This parameter defines the device's sensitivity to this effect. It must be noted that its bigger for devices with shorter *channels*, so it is not a technology defined parameter.

| level of inversion | $I_{DS}$                                                                                                            |        |

|--------------------|---------------------------------------------------------------------------------------------------------------------|--------|

| strong             | $\frac{1}{2}\mu_n C_{ox}\left(\frac{W}{nL}\right)\left(V_{GS}-V_{th}\right)^2$                                      | (2.14) |

| moderate           | $2n\mu_n C_{ox}\left(\frac{W}{L}\right)\phi_T^2 \left[ln\left(1+e^{\frac{V_{GS}-V_{th}}{2n\phi_T}}\right)\right]^2$ | (2.15) |

| weak               | $2n\mu_n C_{ox}\left(\frac{W}{L}\right)\phi_T^2 e^{\frac{V_{GS}-V_{th}}{n\phi_T}}$                                  | (2.16) |

Table 2.1: EKV models for  $I_{DS}$

Saturation: Weak and Moderate Inversion  $(V_{GS} \sim V_{th} \land V_{DS} > V_{GS})$

Even for  $V_{GS} < V_{th}$  there is a residual  $I_{DS}$  inside the channel before the *depletion* point, the strong inversion relation previously illustrated does not consider this fact as it depends only on the overvoltage. The correct trend for this operating region called *weak inversion* is exponential in relation to  $V_{GS}$ :

$$I_{DS|w} = \mu_n C_{ox} \left( n - 1 \right) \left( \frac{W}{L} \right) \phi_T^2 e^{\frac{V_{GS} - V_{th}}{n\phi_T}} \left( 1 - e^{-\frac{V_{DS}}{\phi_T}} \right)$$

(2.13)

In this condition, the charge inside the *channel* can not be no more calculated with the parallel plate capacitor approximation. That is because the *channel* region is not completely inverted, but it presents a depletion layer (with its associated capacitance) between the *channel* and the *bulk*. The (n - 1) term is the ratio between this capacitance and the one of the oxide layer; for its role in the equation, n is called *slope factor*.

The *bulk effect* contribution is provided by the explicit value of  $V_{th}$ .

Lastly, a third region of inversion is considered in between the *weak* and *strong* one: the *moderate inversion*. Both the two previous relations can't provide an adequate  $I_{DS}$  relation for the intermediate region of inversion and, moreover, the transition between the two regimes is not continuous. For these reasons the *moderate inversion relation* is obtained as an interpolation between the two characteristics and is presented in eq.(2.15).

A recap on the different  $I_{DS}$  is presented in tab.2.1, these are a set of *bulk* references models called *EKV model*, widely used in the field.

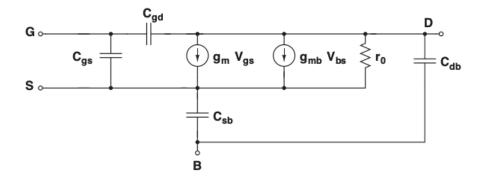

Figure 2.6: small signal equivalent of a NMOS transistor, taken from [8]

#### 2.1.2 Small Signal Parameters

In order to study analytically electronic circuits, complex non-linear elements as transistors are usually linearized around the operation point. In this way, an equivalent circuit with ideal elements can be substituted to it, making the solution of the nodal equation simpler. This approach is called the *small signal equivalent* analysis of the circuit. For an electrical parameter  $f(\vec{x})$  a *small signal parameter*  $f_{sm,i}$  can be evaluated for every dependant variable  $x_i$  of its function at a certain operating point  $\vec{x}^*$ . The parameter can be obtained as the first order coefficient of the partial Taylor expansion of the function:

$$\Delta f(\vec{x}) = \left(\frac{\partial f(\vec{x}^*)}{\partial x_i}\right) \Delta x_i$$

=  $f_{sm,i}(\vec{x}^*) \Delta x_i$  (2.17)

It must be noted that this approximation holds as long as the signal is a small variation from the operating point and the signal must not move the transistor from one operating region to another. For example, a typical request is to keep all transistors in the circuit in *saturation* for all expected signals.

In fig.2.6 the schematic of the small signal model of a *NMOS* transistor, with the main capacitances affecting the circuit, is presented.

#### Gate Transconductance

This parameter represents the conductance of the equivalent ideal current source placed between D and S of a transistor in *saturation*, it's called *transconductance* because its value is voltage controlled by  $V_{GS}$ . It's trivial to use a *MOSFET* in this configuration as the core gain element for a *transconductance amplifier*. Its expression varies on the basis of inversion level. For *strong inversion*, by definition:

$$g_{m|s} = \frac{\partial I_{DS|s}}{\partial V_{GS}}$$

$$= \mu_n C_{ox} \left(\frac{W}{L}\right) (V_{GS} - V_{th})$$

$$= \sqrt{2\mu_n C_{ox} \left(\frac{W}{L}\right) I_{DS}}$$

(2.18)

Here we can see its relation to  $\left(\frac{W}{L}\right)$ .

The last relation is particularly useful because the value of  $I_{DS}$  is typically chosen at design time in order to optimize the circuit power consumption versus area occupation: setting L,  $g_m$  grows linearly with the area and  $I_{DS}$ . For the *weak inversion*, instead:

$$g_{m|w} = \frac{\partial I_{DS|w}}{\partial V_{GS}}$$

$$= \frac{I_{DS}}{n\phi_T}$$

(2.19)

As it can be noted  $g_m$  loses its dependence to the transistor aspect ratio in this regime, so it seams that the transistor can be made indefinitely small without compromising its  $g_m$ . However decreasing  $\left(\frac{W}{L}\right)$  will move the transistor in *strong inversion*, regaining its dependence on the aspect ratio.

In order to quantify this situation it is necessary to define bounds for the inversion regions, for this reason the *boundary current* is introduced as the current value in which the strong and weak versions of  $g_m$  provide the same value:

$$\frac{I_{DS|bound}}{n\phi_T} = \sqrt{2\mu_n C_{ox}\left(\frac{W}{L}\right) I_{DS|bound}} \to I_{DS|bound} = 2n\mu_n C_{ox}\left(\frac{W}{L}\right)\phi_T^2 \qquad (2.20)$$

As a reference, it's useful to use a technology dependant parameter as the *technology* boundary current:

$$I_{DS|bound0} = 2n\mu_n C_{ox}\phi_T^2 \tag{2.21}$$

Using the  $I_{DS|bound}$  value, the *inversion coefficient* is introduced as the ratio between

the actual current and the *boundary current*:

$$I_C = \frac{I_{DS}}{2n\mu_n C_{ox}\left(\frac{W}{L}\right)\phi_T^2} \tag{2.22}$$

The inversion region is identified by its value:

$$I_C < 0.1 \leq I_C \leq 10 < I_C$$

weak moderate strong

As stated above, decreasing  $\left(\frac{W}{L}\right)$  for the same  $I_{DS}$ , will move the transistor in *strong* inversion.

Finally  $g_m$  can be expressed in all regions using  $I_C$ :

$$g_m = \frac{I_{DS}}{n\phi_T} \frac{1}{\sqrt{I_C + \frac{1}{2}\sqrt{I_C} + 1}}$$

(2.23)

#### **Bulk Transconductance**

This parameter accounts for the *bulk effect* contribution to  $I_{DS}$ . It is calculated from the explicit dependence of  $V_{th}$  on  $V_{SB}$ :

$$g_{mb} = \frac{\partial I_{DS}}{\partial V_{BS}}$$

$$= \left(\frac{\partial I_{DS}}{\partial V_{th}}\right) \left(\frac{\partial V_{th}}{\partial V_{BS}}\right)$$

$$= \mu_n C_{ox} \left(\frac{W}{L}\right) \left(V_{GS} - V_{th}\right) \frac{\gamma}{2\sqrt{2\phi_F + V_{SB}}}$$

$$= \eta g_{m|s}$$

$$(2.24)$$

$g_{mb}$  results proportional to  $g_m$  by a factor  $\gamma$  (typically  $0.2 \div 0.3$ ).

### **Output Conductance**

The output conductance is results from the *short channel effect* causing the dependence of  $I_{DS}$  from  $V_{DS}$ . The name is due to the lack of dependence of  $g_{ds}$  on

$V_{GS}$ . Its explicit equation is:

$$g_{ds} = \frac{\partial I_{DS}}{\partial V_{DS}}$$

$$= \lambda \mu_n C_{ox} \left(\frac{W}{L}\right) (V_{GS} - V_{th})^2$$

$$= \lambda I_{DS}$$

(2.25)

Due to its linear relation with  $I_{DS}$ , it's more straightforward to represent it as a resistor:

$$r_0 = \frac{1}{g_{ds}}$$

$$\simeq \frac{1}{\lambda I_{DS}}$$

(2.26)

This is called *output resistance* of the *MOSFET*.

## 2.1.3 MOSFET Noise

Electronics noise stands for the statistical, unavoidable fluctuation of the signal. In this section the basic sources of noise in *MOSFET* are illustrated. Noise is studied with a statistical approach due to its random nature. Noise is expected to present a symmetrical distribution around the zero with a certain variance.

A useful quantity is the noise power spectral density (PSD) referred to the input of the circuit which is the distribution in frequency of the average power of a signal, for a generic signal x(t):

$$S_{xx}(f) = \lim_{T \to \infty} \frac{1}{T} |X_T(f)|^2$$

=  $\lim_{T \to \infty} \frac{1}{T} \left| \int_{-\frac{T}{2}}^{\frac{T}{2}} x(t) e^{-j2\pi f t} dt \right|^2$  (2.27)

Where  $X_T(f)$  is the truncated Fourier transform of the signal.

The fact that the noise is in this form and referred to the input, let us compute the influence of the circuit on the output noise density by the mean of a simple multiplication with its squared *transfer function*:

$$S_{yy}(f) = |H(f)|^2 S_{xx}(f)$$

(2.28)

If other independent noise sources are considered, their contributions to the PSD

are simply summed up.

For the sake of brevity the *PSD* will be further indicated with  $v_n^2$  for voltage values and  $i_n^2$  for current ones.

#### Thermal Noise

One of the primary noise sources in electronics is the variation in current density due to thermal agitation of carriers. For a resistor of value R the power distribution of this noise follows the Plank's law for black body radiation in one dimension [11]:

$$v_{nT}^{2} = \frac{4Rhf}{e^{\frac{hf}{k_{B}T}} - 1}$$

$$\simeq 4k_{B}TR$$

(2.29)

Where the approximation follows from the fact that at room temperature the frequency at which the exponential argument becomes unitary is  $\sim 6.25THz$ , so it can be first order approximated in zero.

$$i_{nT}^2 = \frac{4k_B T}{R}$$

(2.30)

This relation is valid for any type of conductor with a certain resistance R, so in the case of the MOSFET we can use the inverse of the transconductance:

$$i_{nT}^2 = 4k_B T \gamma g_m \tag{2.31}$$

$\gamma$  is called *inversion factor* and it takes into account the variation of the mobile charge in the *channel* in the different inversion levels:

$$\gamma = \frac{1}{2} + \frac{1}{6} \frac{I_C}{I_C + 1} \tag{2.32}$$

The noise expected with this relation results too optimistic for short channel devices (under 1.7 $\mu m$  [12]): in this an excess noise correction factor ( $\alpha_w$ ) is introduced to take into account this effect:

$$i_{nT}^2 = 4k_B T \alpha_w \gamma g_m \tag{2.33}$$

This current noise can be seen as an output noise in all the applications which use the MOSFET as a transconductance amplifier; for this reason it may turn useful to convert this quantity as voltage to be used as an input noise source:

$$v_{nT}^2 = 4k_B T \alpha_w \gamma \frac{1}{g_m} \tag{2.34}$$

#### Flicker Noise

This is another important noise source in MOSFETs, it's often called  $\frac{1}{f}$  noise due to its PSD.

This contribution has been explained with two competing models: one ascribes this noise to interactions between carriers and phonons of the silicon lattice, the other one to fluctuation on the number of carriers due to trapping in the  $Si - SiO_2$  interface.

The following relation unifies the two descriptions: