# Università degli Studi di Torino

Facoltà di Scienze Matematiche, Fisiche e Naturali

# Laurea Magistrale in Fisica delle Tecnologie Avanzate $\sim$ MASTER THESIS $\sim$

# LOW POWER FRONT-END ELECTRONICS FOR HYBRID PIXEL DETECTORS

*Candidato:* Olave Elias Jonhatan *Relatore:* Prof. Rivetti Angelo *Controrelatore:* Prof.ssa Greco Michela

Anno Accademico 2012-2013

MASTER DEGREE IN PHYSICS OF ADVANCED TECHNOLOGIES Low Power Front-End Electronics for Hybrid Pixel Detectors <sup>1</sup>

SUPERVISOR: Angelo Rivetti LOCATION: Torino TIME FRAME: Dicember 2013 EMAIL: *olave@to.infn.it*

1 Thesis written with LATEX[1]

A thought is a seed with promise. A dream is a wish with wings.

Dedicated to my family.

# ABSTRACT

$\overline{P}$ ANDA is a planned particle physics experiment at the future international Facility for Antiprotron and Ion Research (FAIR) which is currently being built in Darmstadt. In order to cope with the physics goals of the experiment, the  $\overline{P}ANDA$  detector is based on an asymmetric double spectrometer. In these work the main parts of the detector are described with a particular attention to the MVD, the silicon based high precision vertex detector placed close to the interaction point. The inner layers of the MVD are equipped with hybrid pixels detectors which are based on a modular structure where detector, transmission bus and readout ASIC are connected using bonding techniques. The ASIC developed for the hybrid pixel sensors, called ToPix, uses a commercial deep-submicron CMOS 0.13 µm technology with a power supply of 1.2 V and, based on the Time over Threshold Technique (ToT), allows to obtain from the analog signal generated by a particle hit, the time stamp and the energy loss measurement. In this thesis, the three prototypes until now developed are described together with the experimental results, underlining the problems observed. The test results of the third prototype, ToPix v<sub>3</sub>, show a good performance but with some features to improve, like the tuning system which, due to a non-linear response between the DAC code and the voltage variation obtained, would require a lot of time to tune the threshold of the millions of pixels of the MVD. This work aims to find a solution for this problem analyzing the parts of the front-end involved, as the DAC and the discriminator. The solution should be implemented in the very small silicon area of 13 µm  $\times$  28  $\mu m$  and will be part of a new version of the DAC which would allow to obtain the linear relation required to solve the problem. Three possible solutions are described with the help of the most significant simulation results. The solution selected is described in more detail and the most important simulations performed to check the circuit reliability for different working conditions are illustrated.

A part of this work is also dedicated to study the use of a new CMOS technology with similar feature size which should allow to develop an ASIC with the same performance but at a lower production cost. The study is based on the comparison between the different performances of the discriminator, which has been studied exploring different devices flavours. The most significant simulation results obtained selecting from the large set of simulations performed, are discussed.

# SOMMARIO

PANDA è un esperimento di fisica nucleare che avrà luogo presso la Facility for Antiprotron and Ion Research (FAIR) attualmente in costruzione a Darmstadt. Per raggiungere gli obiettivi dell'esperimento, il detector di PANDA utilizza una struttura a doppio spettrometro asimmetrico. In questa tesi vengono descritte le parti più importanti del detector, focalizzandosi con maggior attenzione sul MVD, il vertex detector ad alta precisione collocato vicino al punto di interazione. Gli strati più interni del MVD utilizzano pixel ibridi basati su una struttura modulare in cui detector, bus di trasmissione e ASIC di readout vengono connessi utilizzando la tecnica del bonding. L'ASIC sviluppato per i pixel ibridi, chiamato ToPix, utilizza la tecnologia commerciale CMOS 0.13 µm alimentata a 1.2 V e, grazie alla tecnica del Time over Threshold (ToT), permette di ottenere dal segnale creato da una particella, l'energia depositata ed il tempo relativo all'urto con il sensore. In questa tesi i tre prototipi di ToPix finora sviluppati sono descritti insieme ai risultati sperimentali, sottolineando gli eventuali problemi riscontrati. Si parte dai risultati del terzo prototipo, ToPix v3, che mostrano un ottimo funzionamento ma con alcune caratteristiche che potrebbero essere migliorate, come il sistema di regolazione della soglia dei pixel che, a causa di un comportamento non lineare tra regolazione del DAC e la variazione di tensione ottenuta, richiede molto tempo per regolare i milioni di canali presenti nel MVD. Questo lavoro punta allo studio delle cause che sono alla base di questo problema, analizzando le parti del front-end coinvolte, come il DAC e il discriminatore, in modo da trovare una soluzione da realizzare in un'area di silicio di 13  $\mu$ m  $\times$  28  $\mu$ m. Sono descritte tre possibili soluzioni del problema insieme all'aiuto dei risultati più significativi. Infine la soluzione finale scelta è descritta con più attenzione, riportando anche la descrizione delle simulazioni più importanti svolte al fine di controllare l'affidabilità del circuito in diverse condizioni di lavoro.

Una parte di questa tesi è poi dedicata allo studio dell'utilizzo di una nuova tecnologia CMOS con una dimensione simile a quella attualmete utilizzata che potrebbe permettere lo sviluppo di un ASIC con le medesime caratteristiche ma ad una costo di produzione inferiore. Lo studio è basato sul confronto tra le caratteristiche del discriminatore ottenute implementandolo con i dipositivi forniti dalle due diverse tecnologie. I risultati più significativi, scelti da una lunga serie di simulazioni svolte, sono riportati al fine di poter fare un confronto sulle due tecnologie analizzate.

# CONTENTS

| 1                                 | The $\overline{P}$ ANDA Experiment |                           |                                               |    |  |

|-----------------------------------|------------------------------------|---------------------------|-----------------------------------------------|----|--|

|                                   | 1.1                                | .1 Introduction           |                                               |    |  |

|                                   | 1.2                                | The S                     | cientific Program                             | 3  |  |

|                                   | 1.3                                | The $\overline{P}$        | ANDA Detector                                 | 6  |  |

|                                   | -                                  | 1.3.1                     | Charged Particle ID system                    | 8  |  |

|                                   |                                    | 1.3.2                     | Tracking System                               | 13 |  |

|                                   |                                    | 1.3.3                     | Calorimetry system                            | 16 |  |

|                                   |                                    | 1.3.4                     | Magnet system                                 | 18 |  |

|                                   |                                    | 1.3.5                     | Beam-Target system                            | 20 |  |

| 2 The PANDA Micro Vertex Detector |                                    |                           |                                               |    |  |

|                                   | 2.1                                | The R                     | Requirements                                  | 22 |  |

|                                   | 2.2                                |                           | riggerless data acquisition system            | 23 |  |

|                                   | 2.3                                |                           | n Sensors                                     | 24 |  |

|                                   |                                    | 2.3.1                     | Hybrid Pixel Detectors                        | 24 |  |

|                                   |                                    | 2.3.2                     | The Double-Sided Silicon Microstrip Detectors | 26 |  |

|                                   | 2.4                                | The N                     | AVD Design                                    | 27 |  |

|                                   |                                    | 2.4.1                     | The sensor Geometry                           | 29 |  |

|                                   |                                    | 2.4.2                     | The Mechanics and the cooling system          | 31 |  |

| 3                                 | The                                | e Front                   | t-End Electronics ASIC                        | 33 |  |

|                                   | 3.1                                | Requi                     | irements of the Readout                       | 34 |  |

|                                   | -                                  | 3.1.1                     | The Readout ASIC                              | 38 |  |

|                                   |                                    | 3.1.2                     | The ASIC operation                            | 42 |  |

|                                   | 3.2                                | The R                     | Readout Architecture                          | 44 |  |

|                                   | 3.3                                | ASIC                      | Prototypes                                    | 46 |  |

|                                   |                                    | 3.3.1                     | ToPix Version 1                               | 46 |  |

|                                   |                                    | 3.3.2                     | ToPix Version 2                               | 52 |  |

|                                   |                                    | 3.3.3                     | ToPix Version 3                               | 56 |  |

| 4                                 | Linear in-pixel DAC                |                           |                                               |    |  |

|                                   | 4.1                                | .1 Design and simulations |                                               |    |  |

|                                   | 4.2                                | The D                     | DAC of ToPix version 3                        | 63 |  |

|                                   | -                                  | 4.2.1                     | The transistor level implementation           | 65 |  |

|                                   |                                    | 4.2.2                     | Simulation results                            | 68 |  |

|    | 4.3          | The threshold voltage tuning                               | 70  |  |  |

|----|--------------|------------------------------------------------------------|-----|--|--|

|    | 4.4          | Idea for the linearization circuit                         | 76  |  |  |

|    |              | 4.4.1 Voltage amplifier model                              | 81  |  |  |

|    |              | 4.4.2 Transconductance amplifier model                     | 87  |  |  |

|    | 4.5          | Post Layout simulations                                    | 94  |  |  |

|    | 4.6          | New DAC for ToPix version 4                                | 99  |  |  |

|    | 4.7          | The voltage threshold linearity in ToPix v4                | 100 |  |  |

|    |              | 4.7.1 Simulation of the tuning system in ToPiX v4          | 106 |  |  |

| 5  | Ар           | ossible new Technology for the hybrid pixel front-end chip | 107 |  |  |

|    | 5.1          | Low power comparators                                      |     |  |  |

|    | 5.2          |                                                            |     |  |  |

|    | 5            | 5.2.1 The transistor level implementation                  |     |  |  |

|    |              | 5.2.2 Simulation results                                   |     |  |  |

|    | 5.3          | The comparator with a new sub-micron technology            | 120 |  |  |

|    |              | 5.3.1 Trip voltage Analysis                                |     |  |  |

|    |              | 5.3.2 Gain analysis                                        | 124 |  |  |

|    |              | 5.3.3 Delay time analysis                                  | 125 |  |  |

|    | 5.4          | Comparison between the technologies                        | 126 |  |  |

| 6  | Con          | clusions                                                   | 127 |  |  |

| bi | bibliography |                                                            |     |  |  |

# 1

# THE $\overline{P}$ ANDA EXPERIMENT

# 1.1 INTRODUCTION

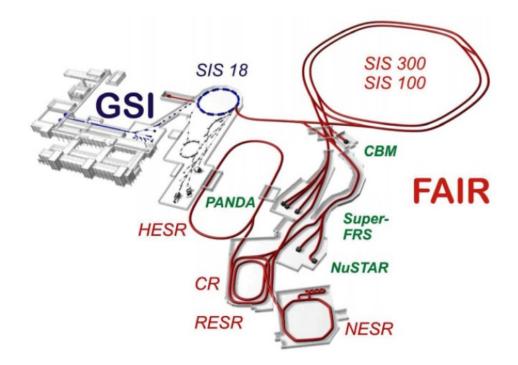

PANDA (antiProton ANnihilation at DAmstadt) will be one of the most important planned experiments at FAIR, the future international Facility for Antiprotron and Ion Research which is currently being built on the area of the GSI, in Darmstadt. For this new facility the present GSI accelerators, once upgraded and together with a new proton linear accelerator, will serve as pre-accelerator and injector for the new complex. An overview of the FAIR facility is given in Figure 1.1.

Figure 1.1: FAIR Facilities Layout. New accelerators and storage rings are highlighted in red while the experimental sites are indicated with green letters [2].

The core of FAIR, a double-ring accelerator (SIS100 heavy ion synchrotron), will be associated with a complex system of cooler and storage rings and experimental setups. This complex system allows to drastically improve the quality of the secondary beams, providing antiprotons and exotic nuclei for several experiments. One of the most important elements of FAIR is the High Storage Ring (HESR), designed to run with antiproton in two operating modes: high resolution mode and high intensity mode. In the high resolution mode, the particle momentum can be varied from 1.5 to 8.9 GeV/c and the resolution  $\delta p/p$  is  $10^{-5}$ , while in the high intensity mode the momentum increases up to 15 GeV/c but at the price of a resolution reduction  $\delta p/p$  to the value of  $10^{-4}$ . During the experiments the antiprotons produced by a primary proton beam will be filled into the HESR and then collide with the fixed target inside the  $\overline{P}ANDA$  Detector [2].

The PANDA experiment is being designed to fully exploit the physics potential arising from the availability of beams of antiprotons or radioactive ions of unprecedented intensities, energies and qualities. In order to cope with this challenge the whole project is characterized by many technological innovations.

# **1.2** THE SCIENTIFIC PROGRAM

FAIR will be constructed to explore the nature of matter and the evolution of the universe. The scientific program ranges in different fields of physics from charmonium spectroscopy to the search for exotic hadrons and the study of nucleon structure, from the study of in-medium modifications of hadron masses to the physics of hypernuclei. Therefore, to make these experiments possible, antiproton beams in the momentum range from 1.5 GeV/c to 15 GeV/c will be provided by the high energy storage ring (HESR) to the  $\overline{P}ANDA$  experiment giving the access to a center of mass energy range from 2.2 GeV/c<sup>2</sup> to 5.5 GeV/c<sup>2</sup> [2] [3].

Nowadays all these studies are carried out mainly at electron machines. These facilities offer the advantage of kinematically clean reactions but at the price of a reduced set of final states and reduced cross-sections that limit the precision data over the full charm spectrum for the future planned experiments. For this reason, the  $\overline{P}ANDA$  experiment will be in the future a unique tool to improve both statistics and precision of existing data and to further explore the physics in the charm quark sector.

The main fields of the hadron physics program are briefly summarized below:

#### • The Hypernuclear Physics:

Single and double  $\Lambda$ -hypernuclei were discovered more than 30 years ago but, in spite of a considerable effort during the last 10 years, only 6 double  $\Lambda$ -hypernuclei are presently known.

A hypernucleus is a nucleus obtained replacing an up or a down quark with a strange quark. In this way a new quantum number is introduced into the nucleus: the strangeness. Thanks to the use of  $\overline{p}$  beams an efficient production of hypernuclei with more than one strange hadron will be possible. In this way with these studies a new chapter of strange physics will be opened for nuclear structure spectroscopy.

# • Open Charm Spectroscopy:

In highly energetic collisions the momentum transfer can be large enough to create hadrons which contain heavier quarks. D mesons are examples of hadrons which contain a light quark  $D^0 = (c\overline{u})$  and they are referred to as open charm.

A large production number of  $D\overline{D}$  meson pairs is expected running the HESR at full luminosity mode and at  $\overline{p}$  momenta larger than 6.4 GeV/c. Thanks to the well-defined production kinematics of D meson pairs and to the high yield would be possible to accomplish with the charmed meson spectroscopy program.

# • Charmonium Spectroscopy:

$\overline{p}p$  annihilations will be used to create charmonium states. In this way the whole energy region below and above the open charm threshold will be probed. This will be very important for a better understanding of QCD. The charmonium spectroscopy will be performed using a  $\overline{p}$  beam with the resonance energy required for the experiment and then performing an energy scan with a fine tuning of the beam momentum. The several thousand of  $\overline{CC}$  states expected per day, obtained by using the detector at full luminosity, will allow fine scans to measure masses with accuracies of the order of 100 keV and widths to 10% or better. In general the precision of these measurements depends only on the accuracy of the determination of the initial  $\overline{p}p$  state energy, thus only on the momentum spread.

# • Gluonic Excitations:

The  $\overline{P}ANDA$  physics program contains also one of the challenges of hadron physics: the search for gluonic excitations. The gluonic hadrons can be divided in two main categories: glueballs and hybrids. Glueballs are for example states where only gluons contribute to the overall quantum numbers while hybrids consist of a valence-quark plus one or more excited gluons which contribute to the overall quantum numbers.

The additional degrees of freedom carried by gluons allow these hybrids and glueballs to have  $J^{PC}$  exotic quantum numbers. In this case, where is possible to exclude mixing effects with nearby  $q\bar{q}$  states, the experimental identification of these particles is easier. The study of the glueballs and hybrids properties, which are determined by the long-distance, is important for understanding the dynamics of low energy QCD and of the structure of the QCD vacuum. The gluonic hadrons mass range will be studied in the first step using the high luminosity modality to observe the candidate states and then using the precision modality to analyze the interesting mass region. The final step consists in a spin-orbit analysis for the determination of the quantum numbers of the observed states.

#### • Hadrons in Nuclear Matter:

Nowadays in other facilities experiments are focused only on the light quark sector, but thanks to the high intensity  $\overline{p}$  beam, up to 15 GeV/c, in  $\overline{P}$ ANDA it will be possible to obtain an extension of the existing experiments to the charm sector, both for hadrons with hidden and open charm.

The study of in-medium modifications of hadrons embedded in hadronic matter is aimed at understanding its partial restoration in a hadronic environment and the nature of hadron masses in the context of spontaneous chiral symmetry breaking in QCD.

Another study which can be made is the measurement of  $J/\psi$  and D meson production cross sections in  $\overline{p}$  annihilation on a series of nuclear targets.

#### The Nucleon Structure:

The recent theoretical framework of GPDs (Generalized Parton Distributions) caused excitement in the field of understanding the nucleon structure. In fact, it has been shown that exclusive  $\overline{p}p$  annihilation into two photons at large *s* and *t* can be described in terms of GPDs. In this context, thanks to the electromagnetic processes,  $\overline{P}ANDA$  will also be able to investigate the structure of the nucleon.

The main electromagnetic processes used in the experiment will be the Deeply Virtual Compton Scattering (DVCS) and the process  $\overline{p} + p \rightarrow e^+ e^-$ . The last one will allow the determination of the electromagnetic form factors of the proton in the time-like region over an extended q<sup>2</sup> region [2][3].

# **1.3** THE $\overline{P}$ ANDA DETECTOR

A complex detector arrangement based on a setup of modular subsystems is necessary in order to achieve the proposed physics goals. Therefore, PANDA is designed as a multi-purpose apparatus following the below requirements:

- High resolution for tracking

- Good particle identification

- Full coverage of the solid angle

- High rate capabilities

- Versatile Readout

- Good event selection

- A triggerless system for the data acquisition

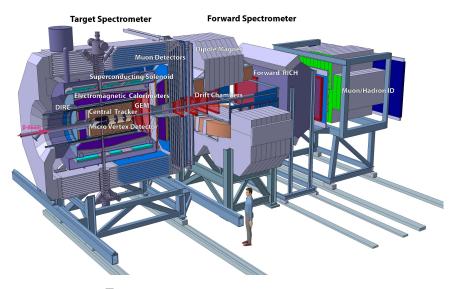

To obtain a good momentum resolution the proposed detector will be arranged as an asymmetric double spectrometer composed by the following two parts:

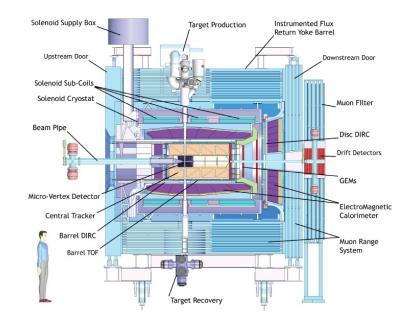

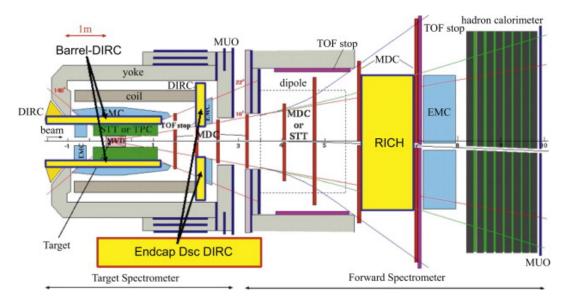

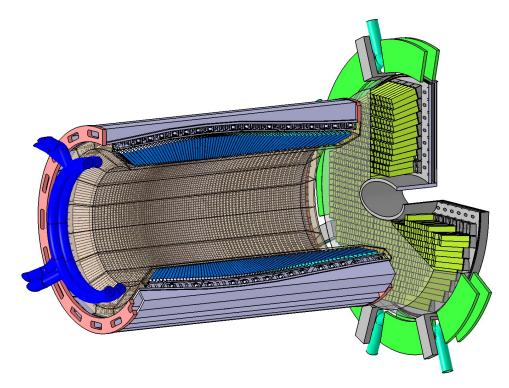

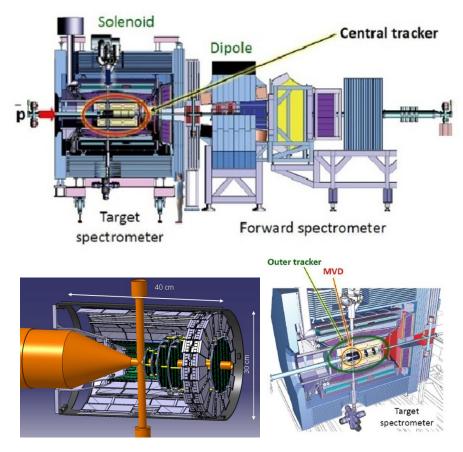

• The Target Spectrometer (TS): This part of the detector surrounds the interaction point where the charge tracks will be measured using a highly homogeneous solenoidal field. The detectors contained in TS will have an onion shell like configuration in the same manner of a collider detector. The pipes for the injection of target material will have to cross the spectrometer perpendicular to the beam pipe. An overview of the TS layout is given in Figure 1.2.

Figure 1.2: Artistic side view of the Target Spectrometer (TS) of PANDA [2].

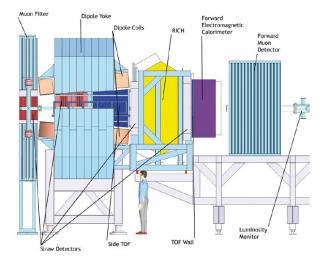

• The Forward Spectrometer (FS): Based on a dipole magnet, the FS will allow the reconstruction of all particles emitted with horizontal and vertical polar angle smaller than 10° and 5°, respectively. Many devices, like the dipole magnet, the Forward RICH, the drift chambers and the Muon/hadron identification systems will compose this part of the detector. The setup of the FS is depicted in Figure 1.3.

Figure 1.3: Artistic side view of the Forward Spectrometer (FS) of PANDA [2].

With the installed setup, a good particle identification with an almost complete solid angle will be combined with excellent mass, momentum and spatial resolution. Moreover, the foreseen triggerless readout will improve the system flexibility. The final  $\overline{P}$ ANDA detector layout contains both Target Spectrometer and Forward Spectrometer, as shown in Figure 1.4.

Figure 1.4: Layout of the PANDA detector consisting of a Target Spectrometer, surrounding the interaction region, and a Forward Spectrometer to detect particles emitted in the forward region [2].

The whole detector contains the fundamental systems, like the charged particle identification system, the tracking system, the target systems and the calorimetry which are compulsory to achieve the experimental purposes of  $\overline{P}ANDA$ . A short description of these systems is given in the following paragraphs.

# 1.3.1 Charged Particle ID system

One of the most important goals to achieve the physics program envisaged, is the identification of charged particles with extreme precision. Therefore, the  $\overline{P}ANDA$  Detector will be equipped with some dedicated particle identification systems inside the target spectrometer and in the forward region around the dipole magnet. The planned configuration will allow to classify the particle species over the whole kinematic range in addition to dE/dx measurements from tracking and information from the electromagnetic calorimetry.

Figure 1.5: Layout of the Identification particles of the PANDA detector. The Čherenkov detectors are indicated in yellow while the Muon Detection System in blue color. The ToF system is indicated in purple color.

The systems, which allow the particle identification, are called PID devices. They are shown in the Figure 1.5 and briefly described below.

# • ČHERENKOV DETECTORS

These detectors are based on the Čherenkov radiation phenomenon which consists of photons that are emitted along a characteristic cone when a charged particle passes through a dielectric.

It is well known that the speed of light in vacuum (c = 300,000 km/s) is the maximum reachable velocity. However, if *n* is the index of refraction the

speed of light in the medium is less than c (v = c/n). It can happen that very fast particles traverse medium with a velocity that is slower than the speed of light in vacuum but faster than the speed of light in that medium. This particle will emit a cone of light called *Čherenkov radiation*. If  $\beta > 1/n$  is the velocity, the radiation will be emitted at an angle  $\theta_c = \arccos(1/\beta n)$  [4]. Thus, combining the velocity information determined from  $\theta_c$  with the momentum information from the tracking detectors, it is possible to determine the particle mass.

Since the momentum particle of this detectors has a strong variation with the polar angle, two different Čerenkov detectors will be employed for particle identification.

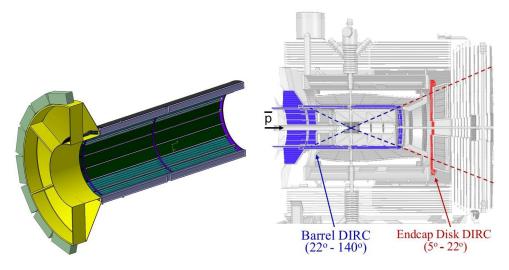

The DIRC detectors, which are based on the principle of Detection of Internally Reflected Čherenkov radiation, will be located in the target spectrometer where relatively slow particles are expected. The DIRC is also used in the BaBar detector but at  $\overline{P}ANDA$ , it is intended to focus the images by lenses onto Micro Channel Plate PhotoMultiplier Tubes (MCP PMTs) which are insensitive to magnet fields [5].

The first DIRC detector is the barrel DIRC which will cover the angular region between  $22^{\circ}$  and  $140^{\circ}$ . It will consist of 1.7 cm thick quartz slabs surrounding the beam line at a radial distance of 45 cm to 54 cm.

Figure 1.6: Layout of the DIRC detector. The blue and the red region represent the barrel DIRC and the end cap disk DIRC, respectively.

The End-Cap DIRC, the second DIRC detector, will be placed as shown in Figure 1.6, directly upstream of the forward end cap calorimeter and it will cover the remaining angular region down to  $5^{\circ}$ . It consists in the same radiator fused silica, but in a shape of a disk of 2 cm thick and 110 cm of radii.

In this configuration the DIRC will provide the  $\pi/K$  separation up to about 4 Gev/c and the distinction between  $\gamma$ 's and relativistic charged particles.

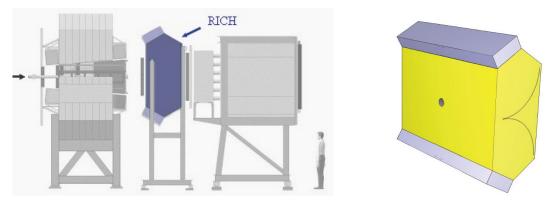

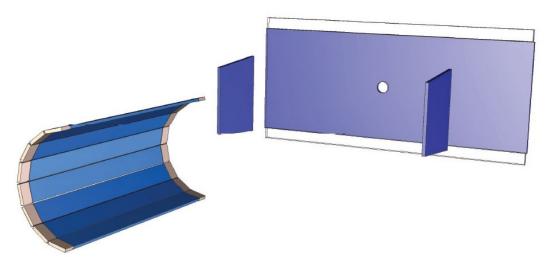

The Ring Imaging Čerenkov detector, or simply RICH, is the third Čherenkov detector and will be used for hadron identification. Like shown in Figure 1.7, it will be placed in the forward direction. The RICH estimates the particles velocity with a high accuracy (0.1%). To reduce the RICH material effect on the electromagnetic calorimeter (ECAL) energy measurement, the sensitive area presents a hole [6].

Figure 1.7: Layout of the RICH detector.

### • MUON DETECTION SYSTEM

This system (MUO) is composed of the instrumentation of the magnet yokes to identify muons. Generally the processes of interest having muons in final states could have small cross sections as compared with the backgrounds. Therefore, a very good muon identification will be necessary to maximize signal to background ratio.

The muon detection will be implemented through the Range tracking System (RS) which is composed of 13 sensitive layers, each with 3 cm thick like shown in Figure 1.5. They alternate with 3 cm thick iron absorber layers, introducing enough material for the absorption of pions in the  $\overline{P}ANDA$  momentum range and angles. Thanks to this configuration it will be possible to distinguish the energy loss processes of muons and pions and therefore obtain a good separation between the background and the primary muons.

The setup is different in the forward and cap because more material is needed due to the higher momenta of the occurring particles. The foreseen setup in this region consists of six detection layers placed around five iron layers of 6 cm each within the downstream door of the return yoke, and a removable muon filter with additional five layers of 6 cm iron. Moreover, rectangular aluminum Mini Drift Tubes (MDT) are foreseen as sensors between the absorber layers.

This system is a good way to detect the muons stopped by the absorber and those which pass through the iron.

# • TIME OF FLIGHT SYSTEM (TOF)

The TOF system will provide the particle identification for slow particles at large polar angles. Since the released energies per particle both at low beam energies and at high beam energies are low, a Time of Flight barrel in the Target Spectrometer is desirable for the particle identification of slow charged particles and for the DIRC detector.

The reaction  $\overline{p} + p \rightarrow \Xi^- + \Xi^+$  is an example of the production of  $\Xi$  which has low momentum energy. Since the value of this cross section is likely four orders of magnitude lower than the one corresponding to the  $\overline{p} + p$  annihilation process, the background suppression plays an important role in the unique identification of hypernuclei. Moreover, the mayor part of  $\Xi^+$  annihilates releasing in most cases two positive kaons. The identification of this kaon via a TOF provides a possibility to tag the production of hyperons.

The Time Of Flight system consists of a scintillating fibers array and a cylindrical scintillator detector, which provides the start and stop time measurement, respectively.

Figure 1.8: Complete layout of the TOF scintillator barrel.

Figure 1.9: Schematic view of the Mini Drift Chamber (brown) enclosed by the Scintillator Barrel (blue).

The TOF scintillator barrel at  $\overline{P}ANDA$ , shown in Figure 1.8, is composed of 2.85  $\times$  2.85 cm<sup>2</sup> tiles of fast scintillator with thickness 0.5 cm mechanically mounted together with the DIRC detector in order to achieve low energy threshold. In total the 5000 tiles foreseen will allow to obtain a time resolution of 100 fs [2][7].

The ToF system foresees also a scintillator wall of 5.6 m wide and 1.4 m tall which will be placed in the forward region at a distance of  $\sim$  7 m downstream the target. The wall will be composed of 60 vertical scintillator strips. In this part of the ToF system a time resolution of 50 ps is expected.

The timing barrel for the trigger of the hypernuclei program will allow to increase the detection probability for  $\overline{\Xi}$  particles by a factor of up to 1000 by detecting the slow kaon decay products. For the DIRC subsystem, the TS-ToF barrel could serve as a time reference to use in addition to the information obtained from the Čherenkov images. Thanks to these information it will be possible to reduce the background and to correct dispersion effects.

The full system is optimized in order to reduce the material budget to a value less than 2% of one radiation length.

Figure 1.10: Layout of the complete identification system.

# 1.3.2 Tracking System

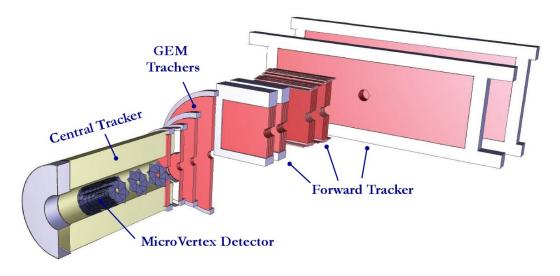

The tracking system will provide a measurement of charged particle trajectories with high spatial resolution over the complete solid angle. To achieve the proposed goals of the experiment four different tracking systems are foreseen inside the Target Spectrometer and in the forward region around the dipole magnet. In Figure 1.11 is shown the complete tracking system of  $\overline{P}ANDA$ .

Figure 1.11: Layout of the Tracking System.

The different subdetectors illustrated in the figure are optimized in order to get an accurate determination of the particle momenta, a high spatial resolution of the primary interaction vertex and the detection of displaced secondary vertices.

A brief description of these subdetectors is given in the following:

• THE MICRO VERTEX DETECTOR (MVD)

The Micro Vertex Detector, or simply MVD, is the silicon based high precision vertex detector for the Target Spectrometer. The MVD is placed in the inner part of the detector close to the interaction point, therefore its design is properly optimized for a maximum acceptance. The detector will detect the secondary decay vertices from charmed and strange hadrons and will also improve the transverse momentum resolution. A complete description of the Micro Vertex Detector will be given in Charter 2.

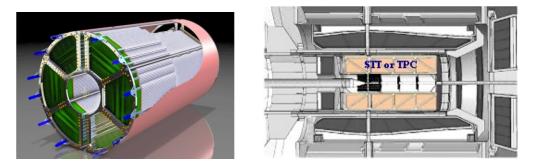

• THE SRAW TUBE TRACKER (STT)

The Straw Tube Tracker (STT), together with the Time Projection Chamber, is a subdetector used for the principal track reconstruction. The STT consists of aluminized mylar tubes called straws. Each straw tube is constructed with a single anode wire in the center that is made of 20  $\mu$ m thick gold plated tungsten and it is filled with a gas mixture. In PANDA the straws will be stiffened by operating them at an overpressure of 1 bar which makes them self-supporting. The detection of the particle which transverses the straw tube will be possible thanks to the ionization effect and to the high voltage of some kV applied between the wire and the tube. With this configuration setup, once the charges are near enough to the wire ( $\sim 50 \mu$ m), an avalanche multiplication takes place with an amplification of 10<sup>4</sup> - 10<sup>5</sup> of the primary charge allowing the readout of the electric signal. Measuring the arrival time of the signal and the charge collected it is possible to evaluate the coordinates and the particle energy lost by ionization, respectively.

Figure 1.12: Schematic view of the Straw Tube Tracker with the position in the Target Spectrometer.

The PANDA Straw Tube Tracker is composed of an ensemble of 150 cm long drift tubes, arranged in planar layers in a hexagonal shape around the MVD like shown in Figure 1.12. In total the layers are 27 of which the 8 central ones are skewed to achieve a good spatial resolution also in z. The basic module used is a planar double-layer of tubes in order to resolve the left-right ambiguity of the track position with respect to the wire. Moreover, the gap to the surrounding detectors will be filled with further individuals straws so that in total there will be 4210 straws around the beam pipe [8].

Concerning the gas choice, an Ar/CO<sub>2</sub> gas mixture (90/10) has been chosen for the  $\overline{P}$ ANDA straw tubes. This mixture is a compromise between a good spatial resolution and the material budget, which must be small to minimize the multiple scattering [3].

### • GAS ELECTRON MULTIPLIER STATIONS (GEM)

The Gas Electron Multiplier (GEM) is a type of gaseous ionization detector used for radiation detection. These detectors are able to collect the electrons released by ionizing radiation guiding them to a region with a large electric field and thereby initiating an electron avalanche. The avalanche is able to produce enough electrons to create a current large enough to be detected by electronics.

The GEM-Trackers are composed of a set of large area planar GEM detectors and will be used as a first forward tracking detector after the central tracker (see Figure 1.13) in other to track the particles emitted at angles below 22° which are not covered fully by the STT.

Figure 1.13: Gas Electron Multiplier Trackers in the Target Spectrometer [3].

In Figure 1.13 the planar GEM detectors used in the target spectrometer are shown. The current implementation includes 3 or 4 GEMS discs depending on the length of the central tracker. Anyway the exact number of planes and also their positions, are yet to be determined based on the simulations studies. Each GEM disc will be equipped with Gaseous micro-pattern detectors based on GEM foils as amplification stages. Moreover, each disc will contain in the middle a double sided read-out pad plane which allows particle track position measurement in four projections.

Thanks to the high number of projections per GEM discs it will be possible to obtain an optimal determination of the particle trajectory position with a resolution better than 100  $\mu$ m.

# • FORWARD TRACKER (FT)

The Forward Tracker (FT) consists of three pairs of planar tracking stations designed for momentum analysis of charged particles which are deflected in the magnetic field. The detector will be placed in front, within and behind the dipole magnet. Each pair will contain two autonomous detectors so that the independent detectors mounted will be 6. The FT covers angular acceptance equal to  $\pm$  10° horizontally and  $\pm$  5° vertically with respect the beam direction.

The same straws used for the central tracker will be employed for the modules which form the detection planes. Every module consists of 32 straws arranged in two layers and has its own preamplifier-discriminator card in order to be autonomous mechanically and electrically. The modules are mounted side by side on a support frame which is employed for two double layers. Moreover, each tracking station consists of four double-layers mounted with a configuration which allows to reconstruct tracks in each pair of tracking stations separately, also in case of multitrack events. Concerning the read-out electronics for the straw detector, it should meet high requirements caused by the high counting rates [3].

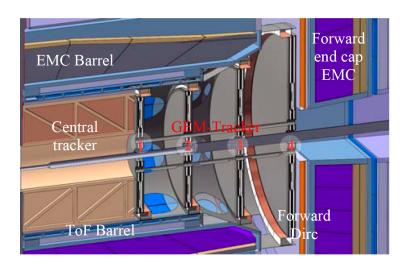

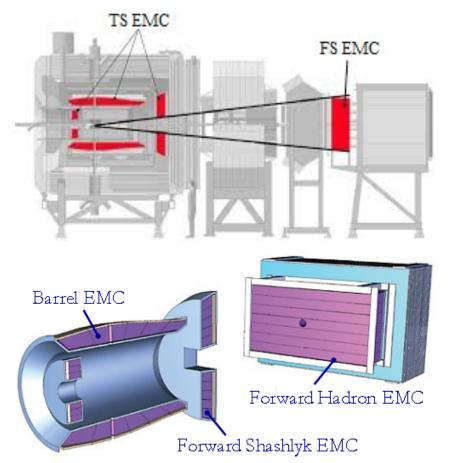

# 1.3.3 Calorimetry system

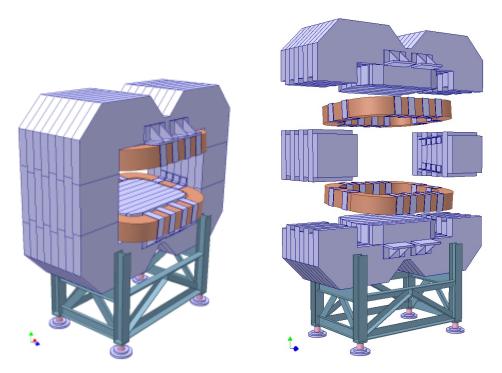

The calorimetry system is composed, as shown in Figure 1.14, of two electromagnetic calorimeters placed in the target spectrometer and a hadron calorimeter in the forward spectrometer used respectively for the detection of photons and for the detection of neutral hadrons.

Figure 1.14: PANDA Detector schematic view. Target spectrometer calorimeter (TS EMC) and forward spectrometer calorimeter (FS EMC) are shown in red.

### • THE BARREL EMC & THE FORWARD EMC

The electromagnetic calorimeter (EMC), due to the high count rates expected, requires a fast scintillator material with a short radiation length and Molière radius. The EMC will provide measurements of photons with accurate energy, position and time with high resolution. Therefore, in order to achieve this sufficient resolution for photon, electron and hadron detection even at intermediates energies, the high density inorganic scintillator chosen was the lead-tungsten (PbWO<sub>4</sub>). This material, the same used at CERN and thus efficiently optimized, will allow a compact setup due to its good energy resolution and fast response.

The barrel EMC, shown in Figure 1.15, will be positioned behind the DIRC barrel inside the solenoid magnet. It has an inner radius of 57 cm and will

Figure 1.15: The Barrel EMC and the Forward EMC [9].

consist in 11,360 tapered crystals with a front size of  $2.1 \times 2.1 \text{ cm}^2$ . Each crystal will be 20 cm long in order to achieve an energy resolution below 2%.

The forward end cap EMC and the backward end cap consist in a planar arrangement of 3,600 tapered crystals and 592 crystals, respectively.

The light yield of the whole system can be increased of about 4 compared to room temperature by cooling the crystals down to - 25 °C. With this configuration the EMC will provide a coverage of 96 % of the full solid angle and will allow a  $\pi/e^-$  discrimination of 10<sup>3</sup> for the momenta above 0.5 GeV/c [9].

# • THE SHASHLYK ELECTROMAGNETIC CALORIMETER

The Shashlyk EMC will be located outside the target region, seven meters from the interaction point beside the dipole magnet. This subdetector will be employed for the detection of photons and electrons with high resolution and efficiency. The system is based on a lead-scintillator sandwiches read out with wavelength shifting fibers (WLS) passing through the block. The geometrical size constraints in the region where this EMC is located are not so strict as well as position resolution requirements thus it is possible to obtain a granularity of 10 cm × 10 cm employing 351 modules arranged in 13 rows and 27 columns. Each module will be 70 cm length, which correspond with a radiation depth of  $20X_0$ , and it will be divided into four channels of 55 mm × 55 mm size in order to achieve a higher spatial resolution. Using this technique an energy resolution of 4 % is expected [10] [9] .

# 1.3.4 Magnet system

The Magnet System of  $\overline{P}ANDA$  is designed to provide an ideal combination of fields. This system, compulsory for the momentum reconstruction and for the particle identification, will be composed of two magnets. A brief description of these devices is given below.

• SOLENOID MAGNET

Positioned in the Target Spectrometer, the solenoid magnet will deliver a homogeneous solenoid field of about 2Tm. The inner diameter of 1.9 m will be left free for the detector placement [6]. In Figure 1.16 is shown the magnet position in the TS.

(a) Solenoid magnet.

(b) Solenoid magnet in the target spectrometer.

Figure 1.16: View of the solenoid magnet (a) and its position in the target spectrometer (b).

In order to satisfy all the requirements for the field, this magnet is designed using a superconducting split coil which has a length of 2.8 m and a laminated yoke for the flux return. This design allows the allocation of the vertical target pipe, like shown in Figure 1.16, without sacrificing the homogenous field. The cryostat will surround all detectors and will serve as their mounting structure. The whole system weights about 300 t and it will be placed in a moveable platform for an easier maintenance.

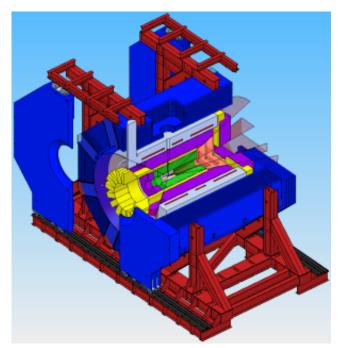

# • DIPOLE MAGNET

The dipole magnet, the central part of the forward spectrometer, is used for reconstruction of charged particle tracks with a good momentum resolution. The dipole covers the entire angular acceptance of the target spectrometer of  $\pm$  10° and  $\pm$  5° in the horizontal and in the vertical direction, respectively. The device will provide a bending power of 2 Tm.

In addition to these devices, also two correcting dipole magnets are foreseen around the  $\overline{P}ANDA$  detector system in order to compensate the beam deflection. The whole system weight is about 220 t and it has an aperture of 1 m  $\times$  3 m. The dipole is designed properly in order to operate fully synchronous with the High Energy Storage Ring (HESR). In Figure 1.17 is shown a view of the dipole magnet of  $\overline{P}ANDA$  [11].

Figure 1.17: View of the dipole Magnet.

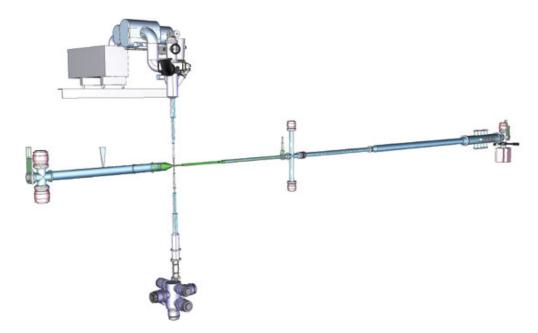

# 1.3.5 Beam-Target system

The Beam-Target system is composed of the devices used for the target production and for the vacuum generation necessary for the region close to the interaction point (IP). Like shown in Figure 1.18, the target and beam pipe cross sections are decreased until an inner diameter of 20 mm close to the IP. The planned materials to use for the innermost parts are mainly beryllium, titanium and suitable alloys.

Figure 1.18: View of the Target system in  $\overline{P}ANDA$ .

The constraints on the material budget and the limited space in the proximity of the IP impose to place the vacuum pumps outside the target spectrometer.

Moreover, depending on the experimental requirements, the target material can be of three different types: the cluster beam target, the pellet beam target and the fiber target. Therefore, the vacuum system will be feasible so that the operation with the different target types will be possible. To prevent the backscattering into the interaction region a dumping system of the target residuals after beam crossing is mandatory.

# 2

# THE PANDA MICRO VERTEX DETECTOR

The Micro Vertex Detector (MVD) is the innermost subsystem of the  $\overline{P}ANDA$  apparatus. Located inside the solenoid magnet of the target spectrometer at 2.5 cm from the interaction point, this silicon tracking device will be used for the identification of the primary and secondary vertices which are important for the study of the weak decay of hadrons with charm or strange content.

Figure 2.1 shows the location of the MVD inside the target spectrometer.

Figure 2.1: The Micro Vertex Detector in the Target Spectrometer [2].

A particular attention will be given to D mesons which are important for the investigation of the charmonium states. The tagging of these particles is achieved through the detection of their charged decay products and, due to their short decay length, it requires a spatial resolution less than 100  $\mu$ m.

The detector will also allow to improve the momentum resolution on all tracks and will provide information for the identification of low momentum particles through dE/dx measurements.

#### **2.1** THE REQUIREMENTS

The MVD is of central importance to cope with all the physics program of the  $\overline{P}ANDA$  experiment, thus a particular attention must be given to its design which must respect some requirements listed below:

#### • Good space resolution:

The decay length ( $c\tau$ ) of D  $_{s}^{\pm}$  mesons is about 150  $\mu$ m thus a spatial resolution of 100  $\mu$ m, or possibly better, is compulsory in the bending plane. Also the spatial resolution in the perpendicular plane to the beam axis is important to obtain a good transverse momentum resolution.

# • Good time resolution:

The time resolution required for the reliability of the detector depends on the expected rate. The detector is designed to work with a maximum interaction rate of  $2 \times 10^{-7}$  events per second and thus a very good time resolution is mandatory to associate unambiguously each track with its parent interaction. The time resolution of the current design is down to 2 ns rms.

#### Adequate radiation hardness:

Due to the position close to the interaction point and to the high rate expected, the radiation hardness is an important parameter to analyze. All the sensors and the electronics components must have an adequate radiation tolerance to guarantee an enough life-time of the detector.

#### • Triggerless read-out scheme:

This is one of the main properties which improve the apparatus flexibility. The triggerless concept implies an event selection based on the physics properties of detected particles, such as reconstructed invariant mass or a detected secondary vertex. To be compliant with the triggerless scheme, the chips should employ a free running architecture, in which all the events above a preset threshold are time-stamped and transmitted off-chip.

#### • Compact geometry:

The detector is located inside the solenoid magnet so that the space available for the detector is restricted and a very compact geometry will be necessary for all the system. The current geometry foresees a diameter of 30 cm and a length of 46 cm in the beam direction.

#### • Material budget:

The use of one additional track point improves a lot the performances of the tracking system, but it means that the particle is crossing another layer of material, loosing energy and making multiple scattering. Thus, in this detector it is really important to reach a correct trade-off between resolution and material budget. Therefore study the amount of material budget present inside the MVD and its influence on particles is mandatory for a correct design of the detector.

## 2.2 THE TRIGGERLESS DATA ACQUISITION SYSTEM

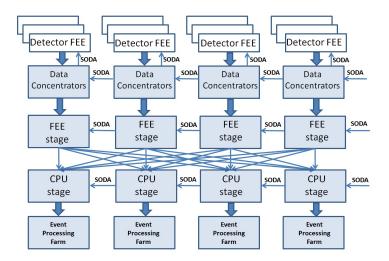

The PANDA experiment will employ a novel data acquisition concept based on triggerless readout. This approach is necessary to manage the average number of  $2 \times 10^7$  antiproton-proton annihilations/s expected during the experiment. In fact, the particular PANDA requirements lead to a new design of the readout chain from the front-end to the data acquisition: the readout will use a DAQ system operating without a hardware trigger signal while the front-end electronics will operate with a continuous data transmission.

The front-end will send the information to the Data Concentrators (DCs) during a given period of time. Then, when the SODA (Synchronization Of Data Acquisition) system sends a common reference time signal to all the DCs, they will combine all the collected data into time stamped messages which will be sent to the DAQ system. The DAQ architecture, depicted in Figure 2.2, has to be able to analyze the data collected and build messages, each with the same time tag to a simple output. At the output, the fragments from all the DCs will be pushed forward into two stage burst merging switching network based on Compute Nodes located in ATCA crates [12].

Using this architecture the concatenated fragments with the same time-stamp tag will be available for physics selection processing.

Figure 2.2: Triggerless system: the DAQ architecture.

# 2.3 SILICON SENSORS

A little general introduction about the silicon detectors is given before the description of the MVD in order to understand the design choices.

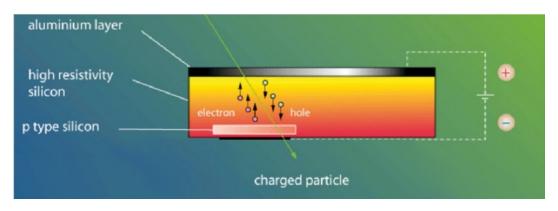

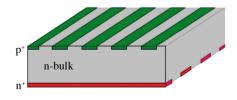

The silicon properties make of this material an optimal stuff for charged particle tracking detectors in high radiation environment under strong magnetic field. The silicon sensor consists in a reversed p-n junction, fully depleted by a high voltage ( $\sim 10^2$  V). As shown in Figure 2.3, when a charged particle crosses this region it loses the part of its energy in the matter which starts the electron hole pairs generation. Thanks to the high mobility of both these charge carriers in silicon, a very fast collection time is possible ( $\sim 10$  ns).

Figure 2.3: P-N junction and the hole pairs generation.

Silicon is successfully employed for tracking detectors because it allows a very high degree of miniaturization with a segmentation density larger of three orders of magnitude than the gaseous detectors. Moreover, not less important, is the very good reproducibility in big quantities limiting the costs. Due to these properties they perfectly meet the requirements imposed on the MVD.

The two different sensors foreseen for the MVD are hybrid pixel detectors and Double Sided Silicon Detectors which are based on different technologies and thus these sensors will be discussed separately in the following paragraphs.

# 2.3.1 *Hybrid Pixel Detectors*

Hybrid pixel detectors, thanks to their good radiation tolerance and their intrinsic good spatial resolution, are an optimal solution for the regions near to the interaction point where the expected rate of particles is very high. The use of this kind of detector in fact, allows to identify particles unambiguously also with high rates but at the price of using a very high number of channels to cover the surface.

The design of systems based on hybrid pixel detectors has been consolidated in LHC experiments like ALICE, ATLAS and CMS, however the  $\overline{P}$ ANDA constraints required the use of a dedicated solution.

In PANDA in fact, it is necessary a triggerless system and so a hardware able to perform a continuous readout. For this reason a front-end ASIC (Application Specific Integrated Circuits), which was developed in a CMOS 0.13  $\mu$ m technology, is used for the readout of the pixel sensors. This custom front-end, called Topix, will be discussed in Chapter 3.

In addition to the triggerless constraint, since the material budget must be reduced, the electronics and sensors must be thinned as much as possible.

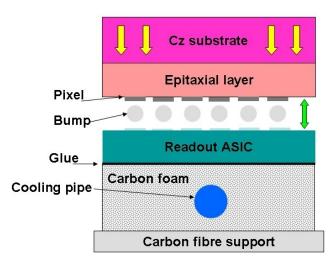

The following figure shows a schematic view of the hybrid pixels used for the Micro Vertex Detector.

Figure 2.4: Hybrid pixels assembly for the  $\overline{P}ANDA$  experiment [2].

The sensor consists of a matrix of reverse biased silicon diodes flip-chip bonded to several readout chips. The diodes are obtained growing an epitaxial silicon layer on a silicon Czochraski substrate which is then almost completely removed. Each cell on the sensor matrix is then, like shown in Figure 2.4, connected by bump bonding technique to the corresponding readout cell of a custom ASIC properly developed in CMOS 0.13  $\mu$ m technology. To make this connection possible the readout cell must fit into the same area as the pixel sensitive element. Then the whole assembly is glued to a carbon foam layer to improve the heat dissipation towards the cooling pipe. The mechanical support is made of a structure of carbon with a suitable shape [2].

After a dedicated R&D effort an elementary cell size of 100  $\mu$ m x 100  $\mu$ m x 100  $\mu$ m x 100  $\mu$ m with a resistivity of 2 k $\Omega$ ·cm has been chosen as the optimal compromise, combining a good space resolution with acceptable performance towards the end of the experiment [13]. After ten years, which is considered the experiment lifetime, for pixels with this geometry is expected a leakage current of 60 nA, that can be tolerated because the charge collection efficiency should still allow the detection of minimum ionizing particles.

Moreover, the power consumption will be reduced thanks to the use of the CMOS  $0.13 \mu m$  technology and thus it will be possible a simplification of the cooling system.

The pixel part of the MVD will contain in total about 10 million independent channels which will give, in addition to the two-dimensional spatial information, also the time and energy loss of every hit.

# 2.3.2 The Double-Sided Silicon Microstrip Detectors

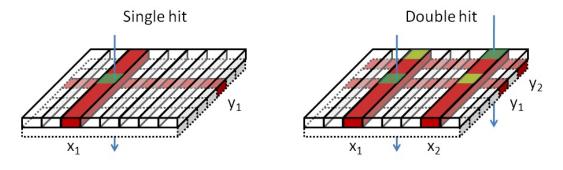

The Double-Sided Silicon Detectors (DSSDs), based on the double sided technology, are produced on FZ wafers. The layout of DSSD foreseen in  $\overline{P}ANDA$  is shown in Figure 2.5. The strips, realized in p<sup>+</sup>type silicon on the front side and in n<sup>+</sup>type silicon on the other side, are arranged in rows and columns in order to obtain a two dimensional information. In the foreseen configuration for this detectors the resolution in one dimension is defined by the strip pitch.

Figure 2.5: Layout of the DSSDs.

Silicon strip detectors have a good spatial resolution and a low material budget, but unfortunately they cannot handle unambiguously very high rates of particle and so they cannot be used where a high rate is expected like the region close the interaction point. This limit is caused by the method employed in the hit identification. In fact, like shown in Figure 2.6, when a single particle hits the sensor the first layer gives the coordinates  $x_1$  and the second layer gives the coordinate  $y_1$ identifying correctly the hit number 1. While when two particles hit the sensor the first layer gives the coordinate  $x_1$  and  $x_2$  and the second layer gives the coordinates  $y_1$  and  $y_2$ . In this case, where the particles arrive simultaneously, is not possible to identify correctly the two hits because also the coordinates  $(x_1, y_2)$  and  $(x_2, y_1)$ could be possible. These two additional hits are called ghost hits.

Figure 2.6: Ghost hit effect with a double hit in DSSDs.

Nevertheless, strips could be efficiently employed in regions with a low hit rate and moreover, make possible the reduction of the number of readout channels reducing also the material budget. In fact, if  $N_{pixel} = \frac{A}{w^2}$  pixels readout channels are required to cover an area A with a spatial resolution w, using  $N_{strip} = 2\sqrt{N_{pixels}}$  strip readout channels, it is possible to cover the same area and with the same resolution [14]. More specific details about the strips used in the MVD will be given in the next paragraph.

# 2.4 THE MVD DESIGN

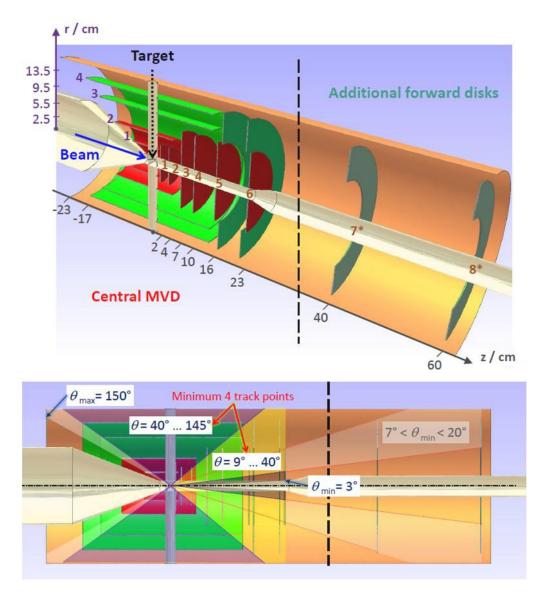

The MVD, located inside the solenoid magnet of the  $\overline{P}ANDA$  target spectrometer, is divided into a barrel and a forward part. A schematic picture of the MVD layers is shown in Figure 2.7.

The detector is composed of four barrel layers and six forward disks arranged perpendicularly to the beam in order to achieve the best acceptance for the forward part. The layer structure is equipped with silicon hybrid pixels detectors or double sided silicon micro strips according to their position and covers a polar angle between  $9^{\circ}$  and  $145^{\circ}$ .

Figure 2.7: Layout of the MVD. The red inner parts use hybrid pixel sensors while the green parts use DSSDs micro-strip. Bottom: Side view along the beam axis illustrating the polar angle coverage. The barrel and the forward part meet at a polar angle of  $\theta$ =40° [2].

The radii of the innermost and the outmost barrel layer are set to 2.5 cm and 13.5 cm respectively while the two intermediate barrel layers are arranged in increasing order. The barrel part covers polar angles between 40° and 150° while the disks in forward direction allow the measurements at small polar angles between 3° and 40°. The innermost disk is located at 2 cm from the interaction point and it has an interspacing of 2 cm to the second disk. These two first disks have the same radii and are located inside the second barrel layer. Located further downstream there are the other four disks which have a bigger radii. The first two of them are positioned inside the third barrel layer while the last two are outside the barrel layers. In addition to the disks, in order to achieve a better acceptance of hyperon cascades, two additional silicon disk layers are considered further downstream at around 40 cm and 60 cm.

Based on the detectors type used in the layers is possible to divide the MVD in two parts: the silicon pixel part and the silicon strip part.

The silicon pixel part of the Micro Vertex Detector is the region highlighted in red in Figure 2.7, and it is composed of the two innermost barrel layers and of the six forward disks. These layers are the most important ones for determining primary and secondary vertices of charm mesons.

In the region where these layers are located a high hit rate is expected thus the detectors must be able to transmit very high data rates due to the untriggered readout. For this part is also required a very high precision and granularity. In addition, since these layers are exposed to relatively high radiation also an adequate radition hardness is mandatory. To cope with all these requirements a hybrid silicon pixel detector appears to be the best solution for this part of the MVD.

Concerning the silicon strip part of the MVD, it is composed of the barrels and the forward disks highlighted in green in Figure 2.7. In these layers is possible to employ the Double-Sided silicon detectors because the hit rate expected is not so high and thus the probability to have ghost hits is low. The use of DSSDs simplifies the readout of a much larger area with significantly fewer channels. In the current MVD design are foreseen 254 strip modules which will be better described in the next paragraph.

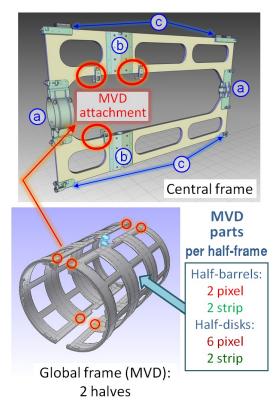

#### 2.4.1 *The sensor Geometry*

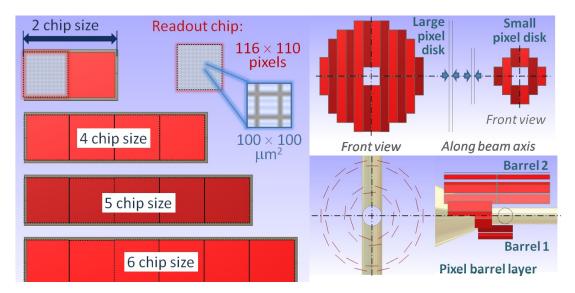

The structure of the MVD is based on a module concept where the silicon sensors represents the lowest level. The detector module is defined as the smallest functional unit which is electronically independent. The schematic layers shown in Figure 2.8 must be approximated by an arrangement of these individual detector modules. The sensor dimensions and the sensor positions chosen for the different parts of the MVD result from an explicit design optimization which takes into account some technical aspects.

The pixel design is based on a quadratic pixel cell size of 100  $\mu$ m × 100  $\mu$ m which is used like elementary unit to make the main module. It contains 116 columns and 110 rows of pixels covering an area of approximately 1.3 cm<sup>2</sup>. This module allows to build the four different pixel sensors shown in Figure 2.8 on the left. All of them have a rectangular shape and the same height but their length is different.

An optimal coverage of both the barrel and the forward regions can be reached by using these modules which are readout respectively by two, four, five and six chips.

Figure 2.8: Left: The pixel sensors employed in the MVD layers. Right: The pixel sensor arrangement in different detector layers.

In the same Figure (on the right) is shown the basic geometry for the pixel sensor arrangement. The forward disks layers consist of an adequate configuration of the four modules described previously. The modules appear aligned in rows with a small interspace along the beam axis. The Figure 2.8 shows also the barrel layers which are composed of a double-ring arrangement of the four modules in order to achieve sufficient radial overlap.

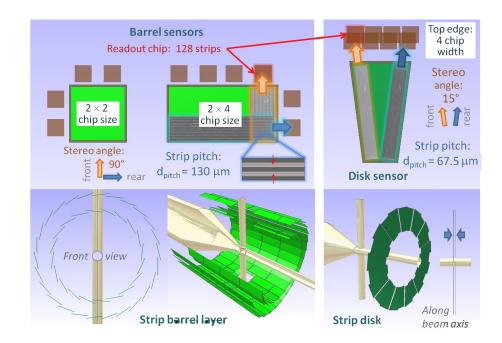

For the silicon strips detectors unlike the pixel detectors, there isn't the constraint due to the readout chip size on the dimension of the sensor segmentation thus the

strip design is more feasible. The basic design of the MVD foresees DSSDs of three different geometries shown in Figure 2.9 and described below:

- Rectangular or squared sensors: Used for the barrel part, these sensors feature a stereo angle of  $90^{\circ}$ . The pitch for these sensors is set to 130  $\mu$ m.

- Trapezoidal sensors: They are used for the peripherical region of the forward disks and feature a stereo angle of  $15^{\circ}$  in order to place the strips parallel to the sensor edge. The pitch chosen for this geometry is 70  $\mu$ m.

Figure 2.9: Sensor geometry for the MVS strip part. Top: The sensor types employed for the MVD. Bottom: The sensor arrangement in the layers. [2]

The complete detector will contain about 10 million pixel channels and 200000 strips. Figure 2.10 and Figure 2.11 list the compilation design parameters for the MVD and the position of the sensors in the different layers.

| Basic parameter                         | Pixel part                                                                       | Strip part                                            |  |

|-----------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------|--|

| Number of super-modules                 | 66                                                                               | 70                                                    |  |

| Number of detector modules              | 176                                                                              | 140                                                   |  |

| Number of sensors                       | 34 (2 chips size)<br>28 (4 chips size)<br>54 (5 chips size)<br>60 (6 chips size) | 172 (rectangular)<br>34 (squared)<br>48 (trapezoidal) |  |

| Total:                                  | 176                                                                              | 254                                                   |  |

| Active silicon area / [m <sup>2</sup> ] | 0.106                                                                            | 0.494                                                 |  |

| Number of front-end chips<br>Total:     | 338 (barrels)<br>472 (disks)<br>810                                              | 940 (barrels)<br>384 (disks)<br>1324                  |  |

| Number of readout channels              | $\approx 10.3\cdot 10^6$                                                         | $\approx 1.7\cdot 10^5$                               |  |

| <b></b>           |                                             |                               |            |               |             |                               |              |                | r              |

|-------------------|---------------------------------------------|-------------------------------|------------|---------------|-------------|-------------------------------|--------------|----------------|----------------|

| Main Sub-layer    | $(r_{\rm def})$                             | $\langle r_{\rm opt} \rangle$ | $r_{\min}$ | $r_{\sf max}$ | $(z_{def})$ | $\langle z_{\rm opt} \rangle$ | $z_{\min}$   | $z_{\max}$     |                |

| layer             |                                             | [mm]                          | [mm]       | [mm]          | [mm]        | [mm]                          | [mm]         | [mm]           | [mm]           |

| Barrel            | Inner ring                                  |                               | 22         | 21.80         | 22.75       | -                             | -            | -39.8          | 9.8            |

| layer 1           | Outer ring                                  | 25                            | 28         | 27.80         | 28.58       |                               |              |                |                |

| Barrel            | Inner ring                                  | 50                            | 47.5       | 47.30         | 47.85       | -                             | -            | -79.8          | 57.8           |

| layer 2           | 2 Outer ring                                |                               | 52.5       | 52.30         | 52.82       |                               |              |                |                |

| Barrel<br>layer 3 |                                             | 95                            | 92         | 89.72         | 96.86       | -                             | -            | -133.8         | 139.0          |

| Barrel<br>layer 4 |                                             | 135                           | 125        | 123.20        | 129.24      | 1.1020                        | 21           | -169.2         | 139.0          |

| Disk              | Sdk 1, front                                |                               | -          | 11 50         | 0.0 5.0     | 20                            | 22           | 19.7           | 19.9           |

| layer 1           | Sdk 1, rear                                 | < 50                          |            | 11.70         | 36.56       | 20                            |              | 24.1           | 24.3           |

| Disk              | isk Sdk 1, front                            | < 50                          | -          | 11.70         | 36.56       | 40                            | 42           | 39.7           | 39.9           |

| layer 2           | Sdk 2, rear                                 | < 50                          |            | 11.70         | 30.50       | 40                            | 42           | 44.1           | 44.3           |

| Disk              | Ldk 1, front                                | < 95                          | -          | 11.70         | 73.96       | 70                            | 72           | 69.7           | 69.9           |

| layer 3           | $\operatorname{Ldk} 1, \operatorname{rear}$ | < 95                          |            | 11.70         | 13.90       | 10                            |              | 74.1           | 74.3           |

| Disk              | Ldk 2, front                                | < 95                          | _          | 11.70         | 73.96       | 100                           | 102          | 99.7           | 99.9           |

| layer 4           | $\operatorname{Ldk} 2, \operatorname{rear}$ | < 30                          |            | 11.70         | 13.90       | 100                           | 102          | 104.1          | 104.3          |

|                   | Ldk 3, front                                | 21                            |            | 11.70         | 73.96       |                               | 150<br>162.5 | 147.7          | 147.9          |

| Disk<br>layer 5   | Ldk 3, rear                                 |                               |            | 11.10         | 10.00       | 160                           |              | 152.1          | 152.3          |

| layer 5           | StripDk 1, L<br>StripDk 1, S                | -                             | -          | 74.33         | 131.15      |                               |              | 160.0<br>165.0 | 160.3<br>165.3 |

|                   | Ldk 4, front                                | -                             | -          | 11.70         | 73.96       | 230                           | 220          | 217.7          | 217.9          |

| Disk              | Ldk 4, rear                                 |                               |            |               |             |                               |              | 222.1          | 222.3          |

| layer 6           | $\operatorname{StripDk} 2, S$               | _                             | _          | 74.33         | 131.15      | 230                           | 207.5        | 204.7          | 205.0          |

|                   | $\operatorname{StripDk} 2, L$               |                               |            | (4.33         | 131.15      |                               | 207.5        | 209.7          | 210.0          |

Figure 2.11: Positions and design parameters of the active sensor volumes within the different detector layers [2].

#### **2.4.2** The Mechanics and the cooling system

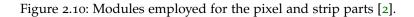

Since the MVD will operate at room temperature of about  $+25^{\circ}$ , both for pixels and strips, an active cooling system is required for a long term stability of the detector. Therefore the cooling pipes, together with other service structures must be brought from outside close to the detector in order to allow the sensor supply and the data transmissions. The limitations given by the stringent boundary conditions are shown in Figure 2.12.

Due to the fixed target setup, the access to the MVD is possible only from the upstream direction. In fact, the downstream region is occupied by the forward spectrometer. Moreover, also the downstream access is limited caused by the conic expansion of the pipe and this leads to inhomogeneities in the material budget distribution. For these reasons the service layout chosen concentrates most of the material where it is less harmful for the physics performance. Moreover, the use of Aluminium-Kapton cables for power supply distribution and signal transmission in addition to a light-mass cooling system allows to keep the average material budget of the full MVD below 8%.

Figure 2.12: Schematic routing for the MVD. The blue and green arrows illustrate the concept used for the barrel and forward region, respectively. With yellow arrows are indicated the probable routing of the additional forward disks which could interfere with the MVD volume.

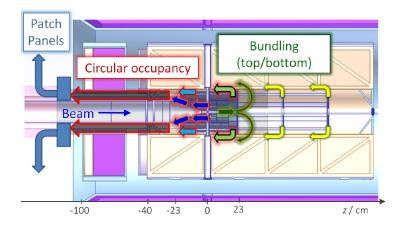

In Figure 2.13 is shown the global support structure which is composed of two half frames mechanically independent. They allow the mounting of all detector half layers and the attachment of the central frame. All the sensors are supported by a light weight carbon fiber structure and the interconnections are realized using low mass flex cables [2][3][15].

Figure 2.13: Detector integration of the MVD. Left: Three-point fixation to the central frame which also provides fixation points for the beam pipe (a), the target pipe (b) and the connection to a rail system (c).

## 3 The front-end electronics ASIC

An Application Specific Integrated Circuit, or simply ASIC, is an Integrated Circuit (IC) customized for a particular application. In recent years several radiation tolerant customized ICs were realized for High Energy Physics (HEP) experiments such as ALICE, ATLAS and CMS at the Large Hadron Collider (LHC) at CERN. However, due to its unique requirements, mainly related to the absence of a trigger signal, for the PANDA experiment it is necessary the development of a specific custom readout ASIC for the hybrid pixel sensors.

The technology employed to develop the ASIC is a commercial deep sub-micron CMOS 0.13 µm which, like all the deep sub-micron technologies with a very thin gate oxide and Shallow Trench Insulation (STI), has the potential to withstand high levels of Total Ionizing Dose (TID) using standard layout techniques [16]. In addition to the good radiation hardness, this technology offers also a much higher integration density respect to other technologies. In order to obtain a robust system, the ASIC is designed in the way that the information is sent out from the device digitally. Therefore the ASIC design is based on a mixed signal approach which foresees analogue signals and digital signals in the same monolithic system.

In this chapter the more important requirements of ToPix and the readout architecture are described. The blocks that form the front-end are presented using a high level description. More specific information about the transistor implementation is given in Chapter 4 and Chapter 5. The ASIC operation, with particular regard to the Time over Threshold (ToT) technique which is used for the digitization, is explained. Moreover at the end of the chapter is foreseen a description of the three prototypes developed until now with a discussion about the results obtained from tests.

More details can be found in the Technical Design Report for the PANDA Micro Vertex Detector [2].

#### 3.1 REQUIREMENTS OF THE READOUT

The proximity of the MVD to the interaction point and the  $\overline{P}ANDA$  radiation environment are two fundamental parameters which are very influential for the pixel readout requirements.

The custom ASIC, especially developed for the PANDA experiment, has to provide position, time stamp and energy loss measurements for every hit. In order to achieve a correct track reconstruction a high granularity, is requested. This requirement leads to minimize the pixel size but with this reduction the perimeter to area ratio increases and consequently also the input capacitance. For this reason many simulations were made to find the optimal trade-off and the results indicate a pixel size of 100  $\mu$ m  $\times$  100  $\mu$ m as the best solution.

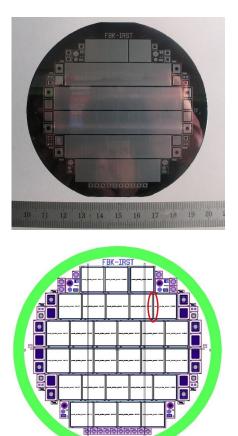

The pixel detector is based on a modular concept as explained in the previous chapter. Figure 3.1 shows the whole wafer employed for the full size prototype sensors. As shown in the figure, the wafer contains an arrangement of 1, 2, 4, 5 and 6 readout chips together with some diagnostic structures. The vertical bars on the modules correspond to two columns with a pixel size of 100  $\mu$ m  $\times$  300  $\mu$ m and they represent the border between two different readout chips.

Figure 3.1: The wafer used for the sensors prototype. In red is indicated the boundary region with larger pixels [17].

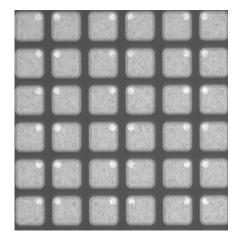

Figure 3.2 is a zoom of the last image where it is possible to observe the pixel sensor arrangement in each module. It is also possible to see at one corner of every pixel the pad used for bump bonding which follows a mirror configuration with respect to the bus serving two pixel columns.

Figure 3.2: Picture of the pixel matrix.

To cover the whole region of the barrel and the disk layers a minimum of 34 wafers, all with the design of Figure 3.1, has to be produced. The number of needed sensors for the different layers of the MVD is briefly summarized in Table 3.1.

| SENSOR NUMBERS |    |            |            |            |       |

|----------------|----|------------|------------|------------|-------|

|                | S2 | <b>S</b> 4 | <b>S</b> 5 | <b>S</b> 6 | Total |

| Barrel 1       | 6  | 8          | 0          | 0          | 14    |

| Barrel 2       | 0  | 0          | 6          | 44         | 50    |

| Disk 1         | 6  | 2          | 0          | 0          | 8     |

| Disk 2         | 6  | 2          | 0          | 0          | 8     |

| Disk 3         | 4  | 4          | 12         | 4          | 24    |

| Disk 4         | 4  | 4          | 12         | 4          | 24    |

| Disk 5         | 4  | 4          | 12         | 4          | 24    |

| Disk 6         | 4  | 4          | 12         | 4          | 24    |

| Total          | 34 | 28         | 54         | 60         | 176   |

Table 3.1: The sensors employed to build the sensitive area of the MVD. The S number corresponds to the number of readout chips contained in the modules employed [2].

Since each hybrid pixel sensor is obtained connecting the pixel sensor to the readout cell via bump bonding technique, the readout cell matrix has to respect the same geometry as the pixel sensor matrix. The pixel matrix is realized using pixels with a size of 100  $\mu$ m  $\times$  100  $\mu$ m which are arranged in a configuration of 110 columns each composed of 116 pixel cells covering a total area of 11.4 mm  $\times$  11.6 mm. Every pixel has to transmit only digital information and therefore time and charge digitization has to be preformed at the pixel level. This impose the use of a mixed signal electronics for the readout system of each pixel.

In the experiment it is foreseen to employ p-in-n epitaxial silicon sensors which have optimal features but in order to have a backup solution, such as the well known n-in-n sensor employed in LHC, the front-end has to be designed to be compatible also with this second polarity.

The sensor chosen has a thickness of 100  $\mu$ m in order to cope with the limited material budget. The average ionization expected in a sensor with this geometry goes from a Minimum Ionizing Particle (MIP) of 1.3 fC up to 50 fC.

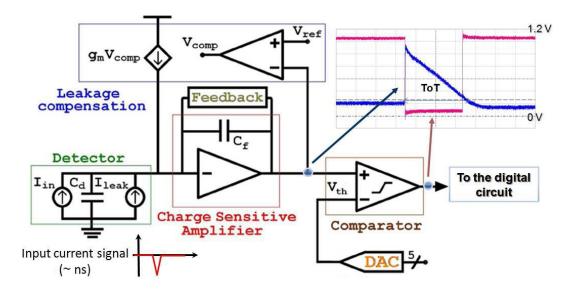

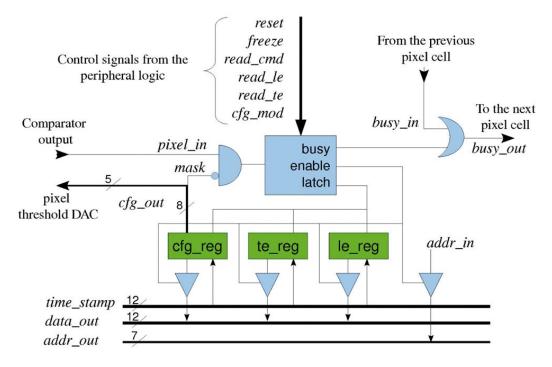

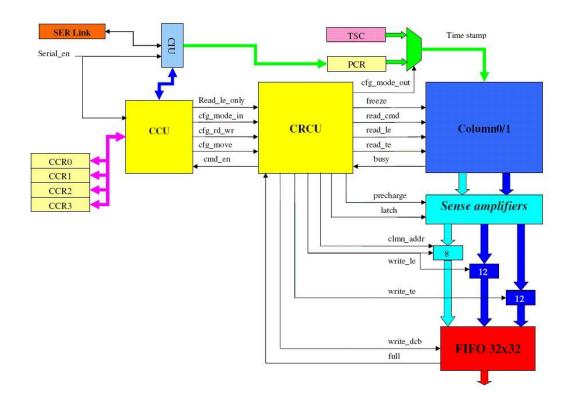

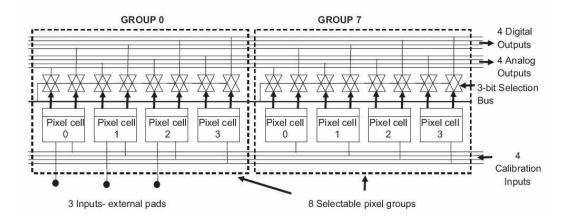

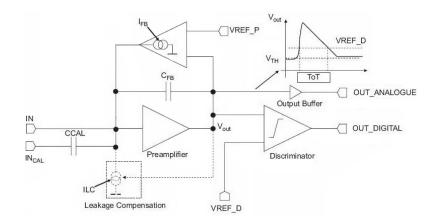

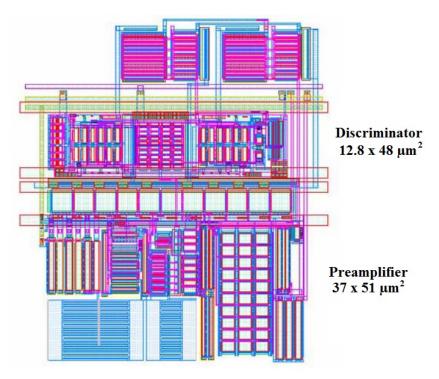

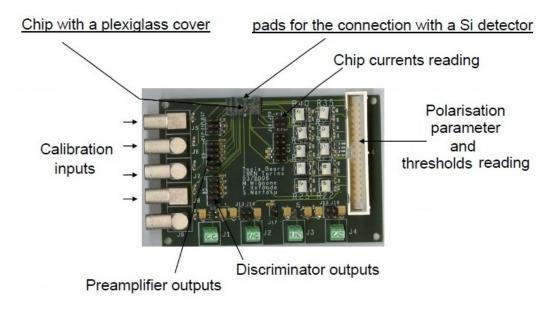

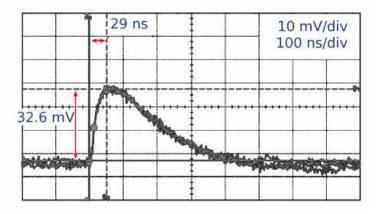

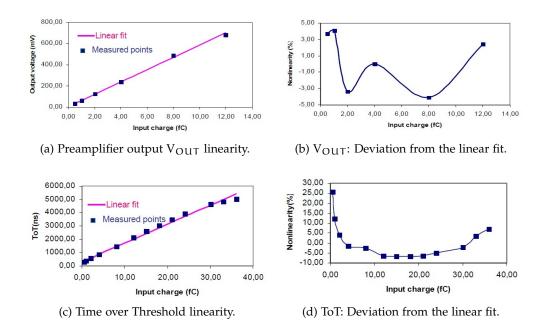

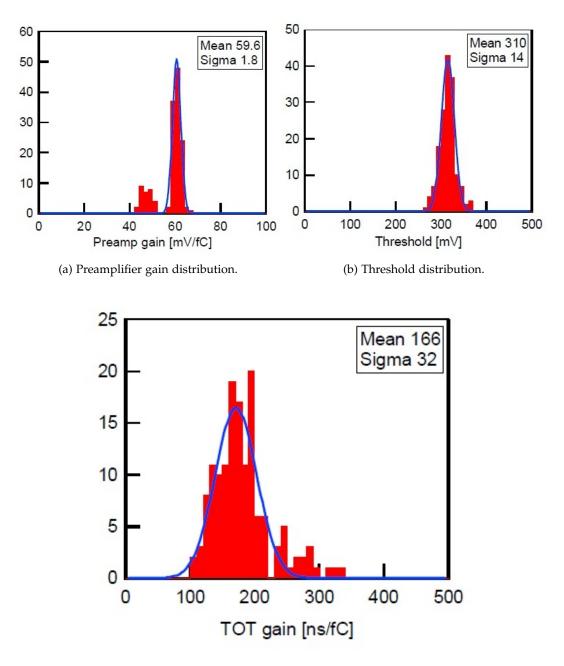

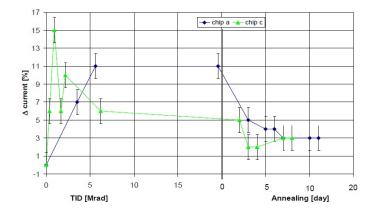

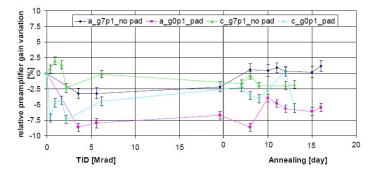

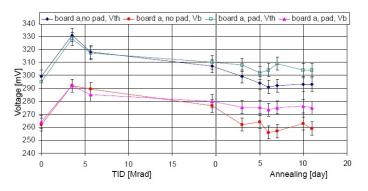

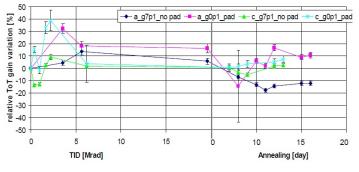

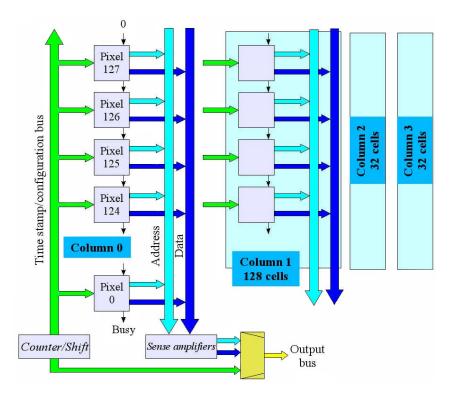

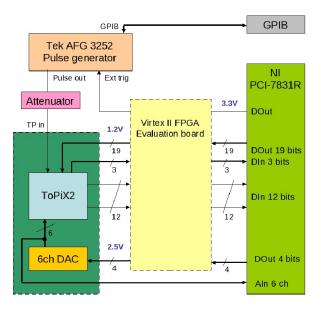

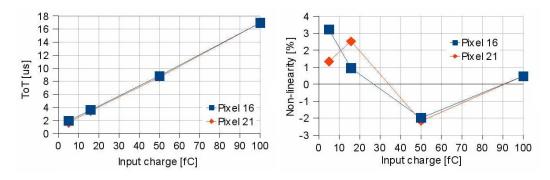

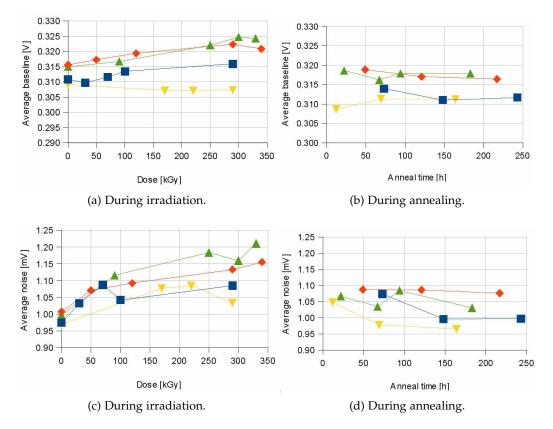

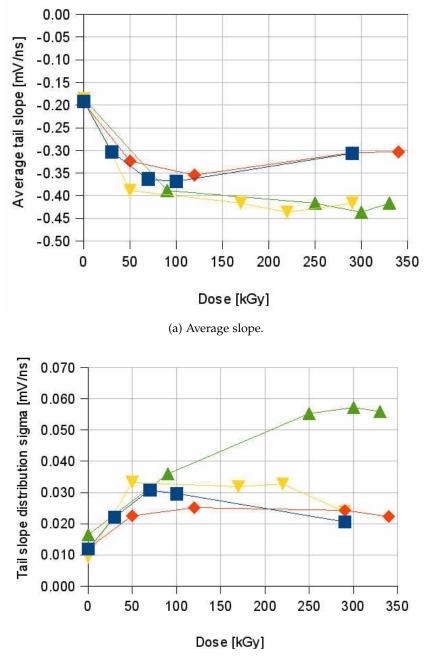

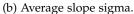

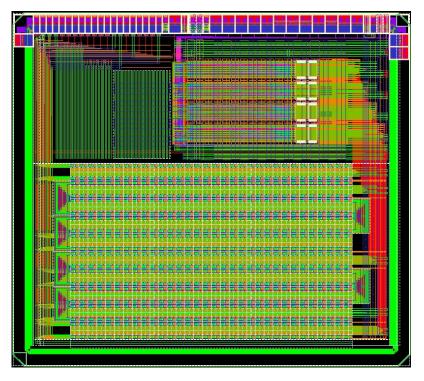

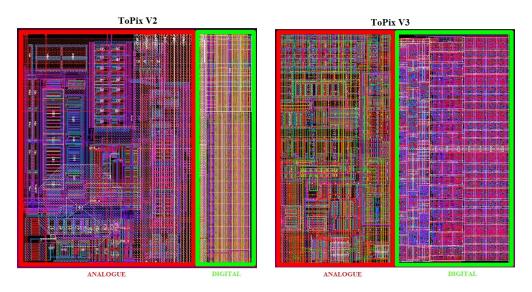

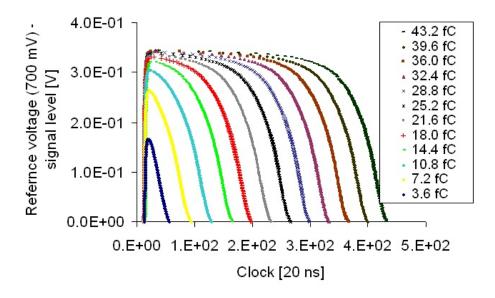

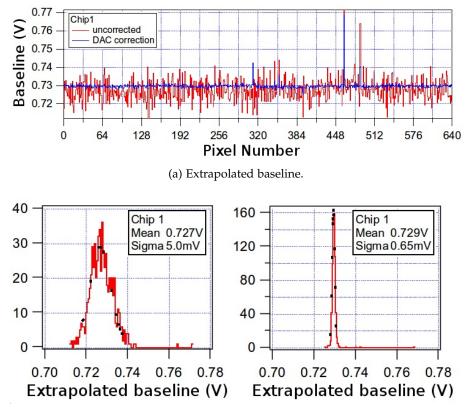

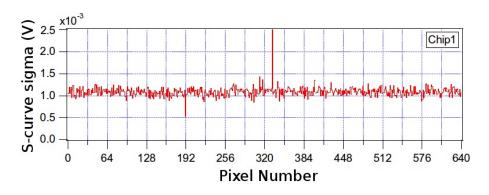

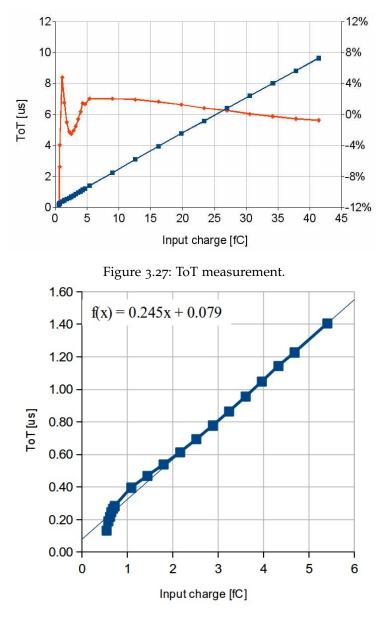

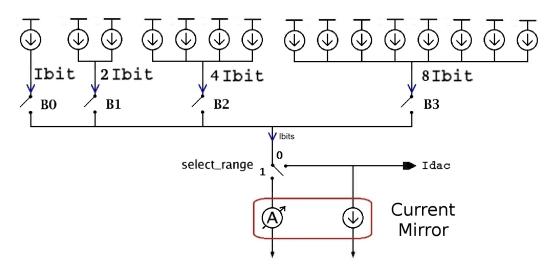

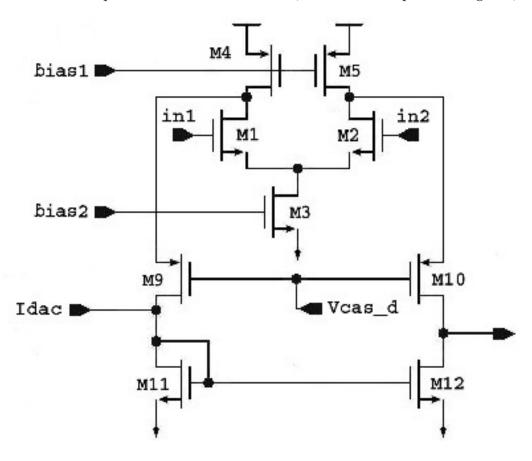

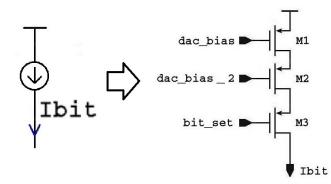

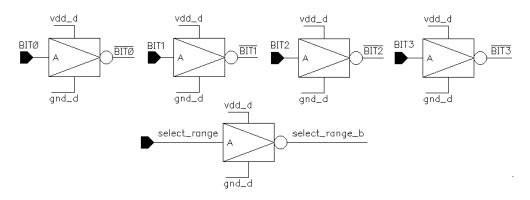

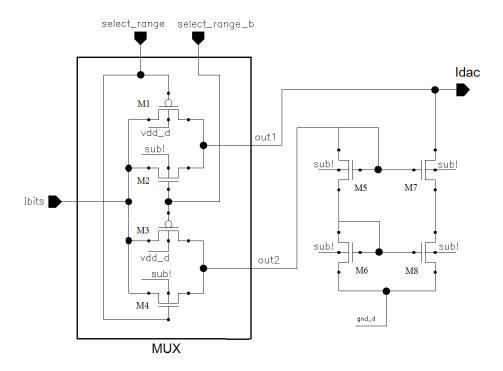

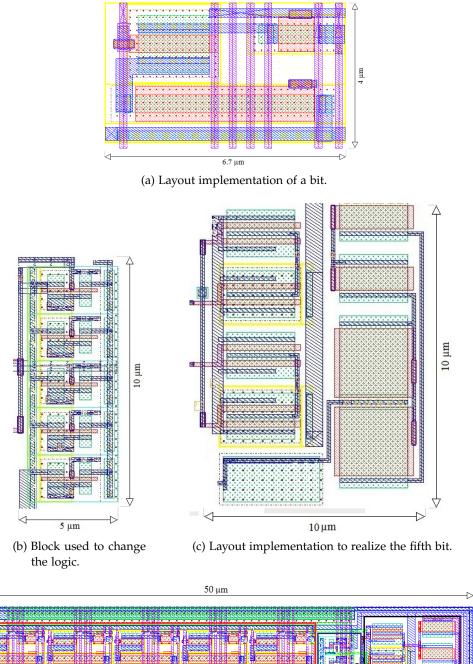

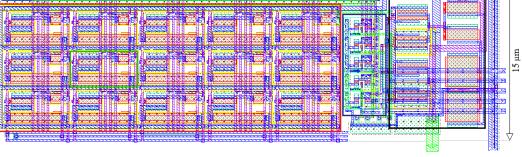

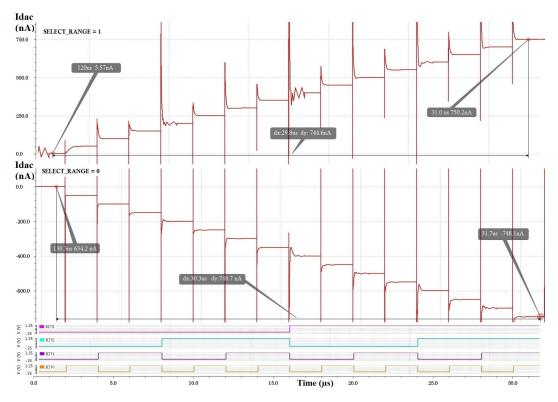

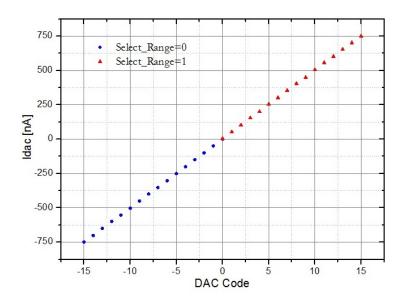

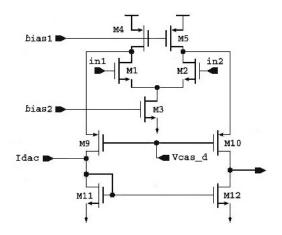

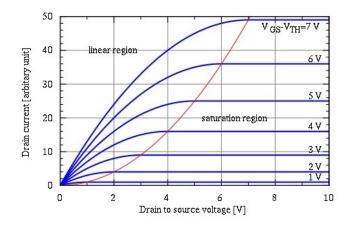

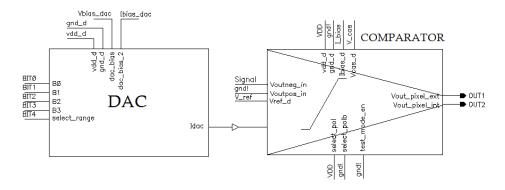

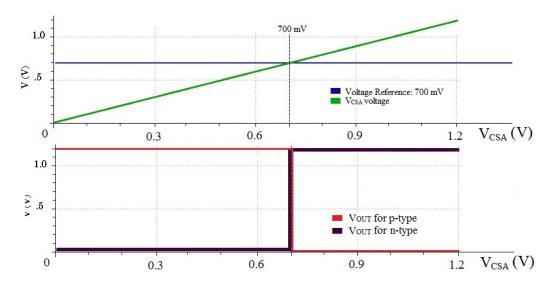

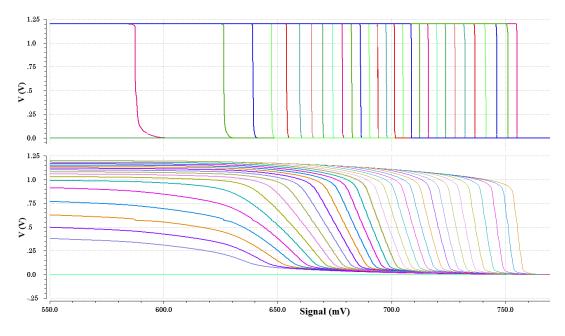

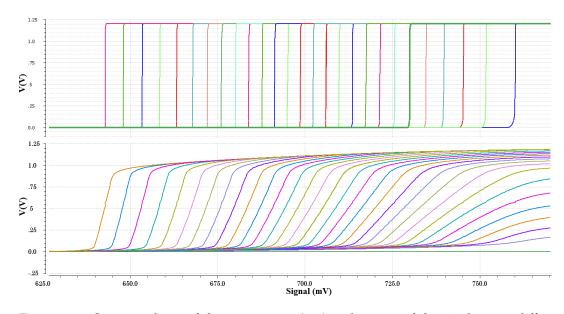

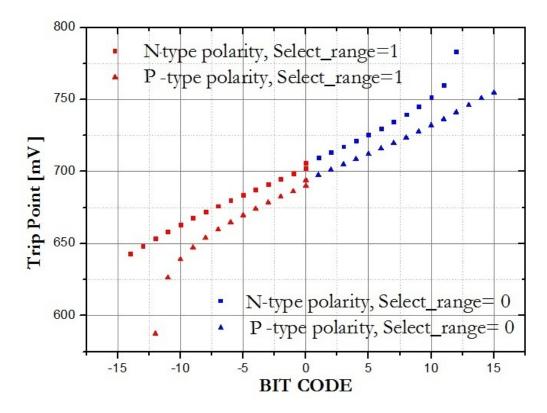

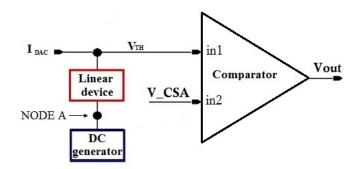

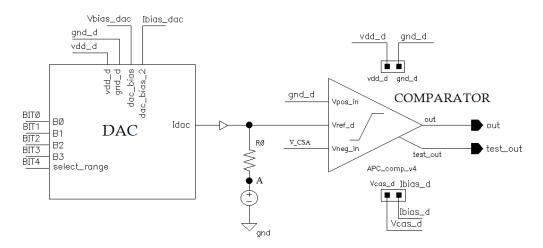

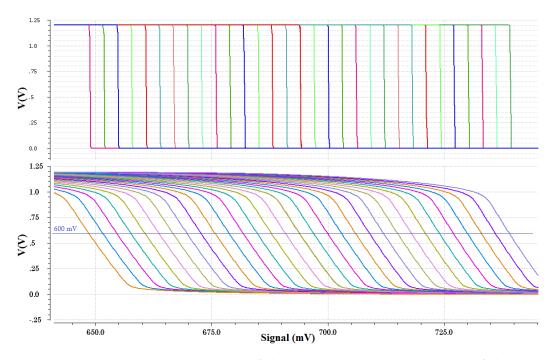

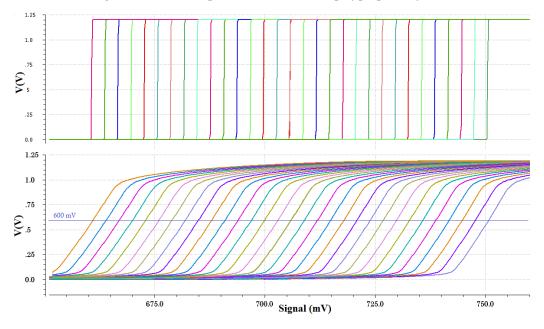

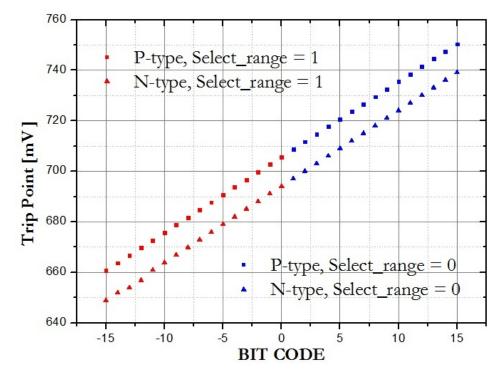

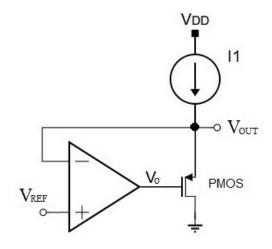

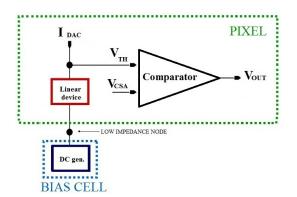

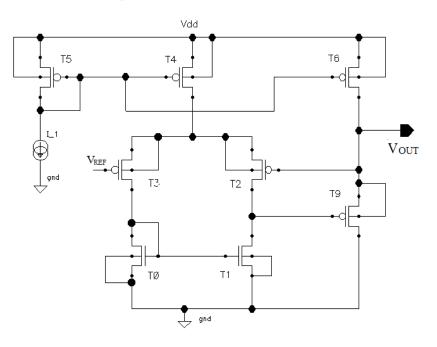

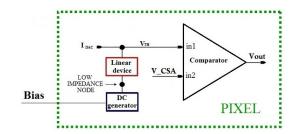

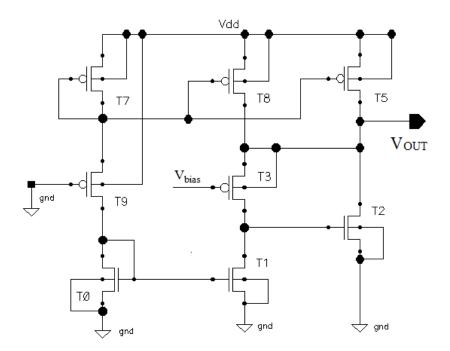

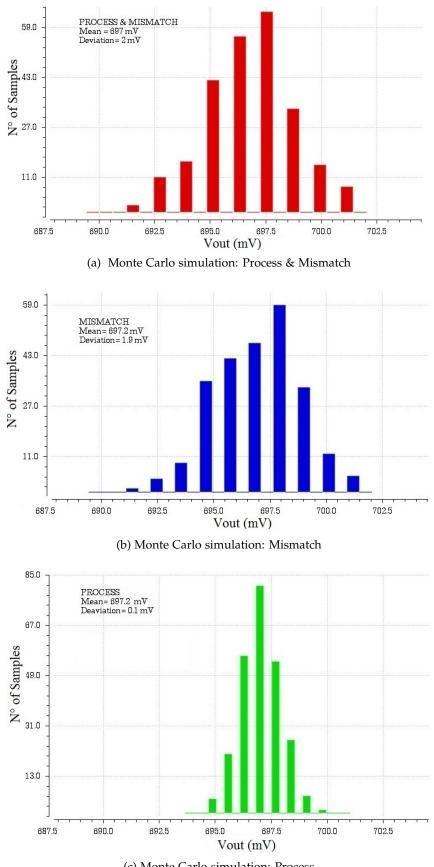

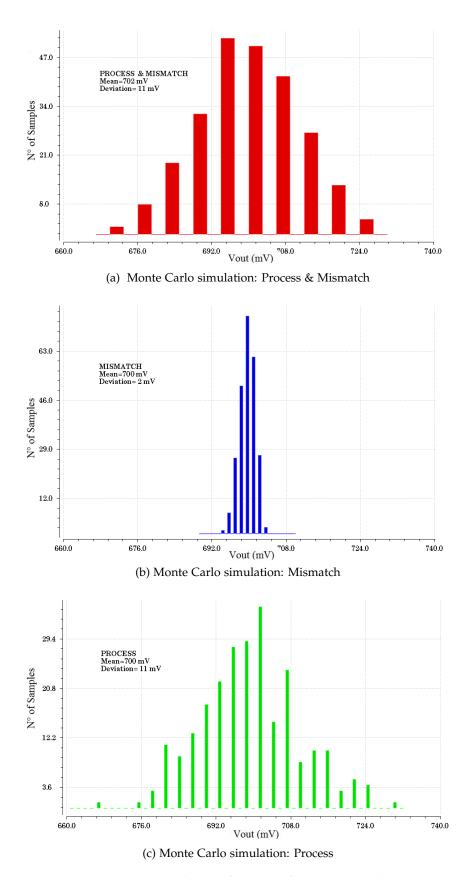

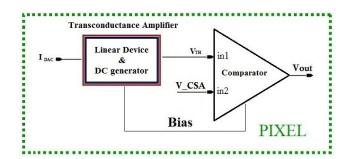

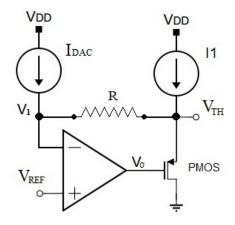

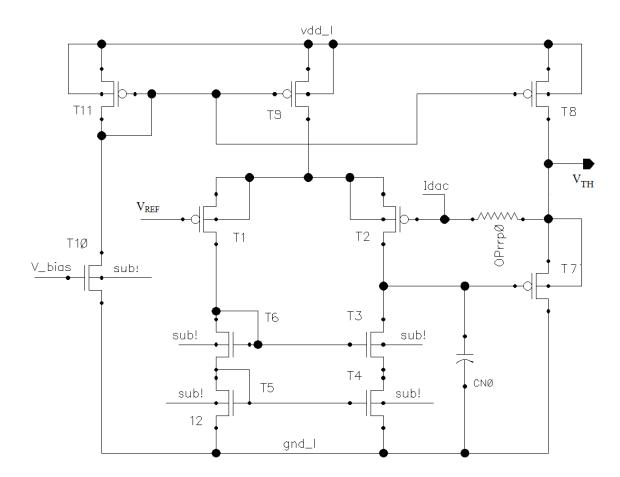

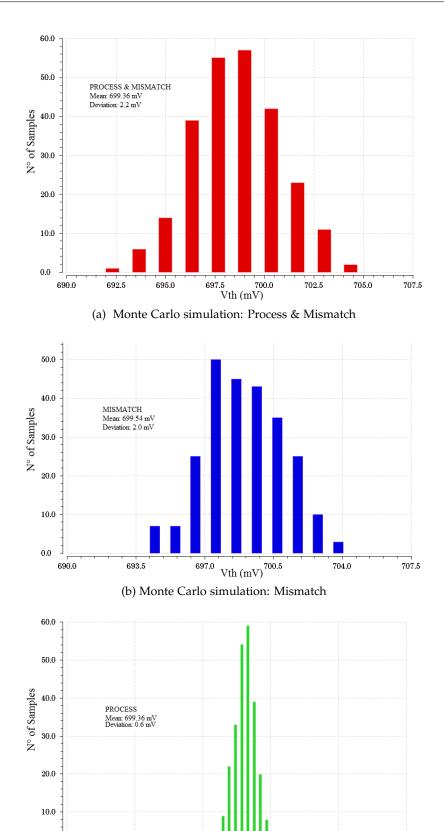

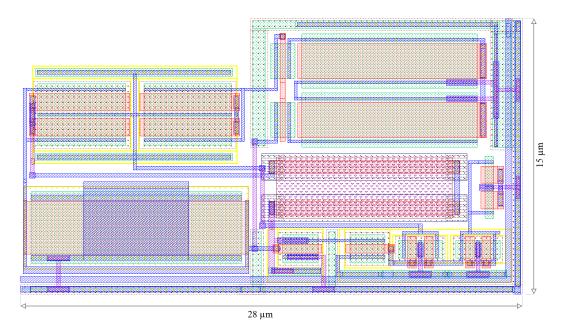

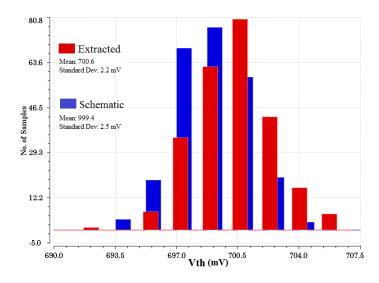

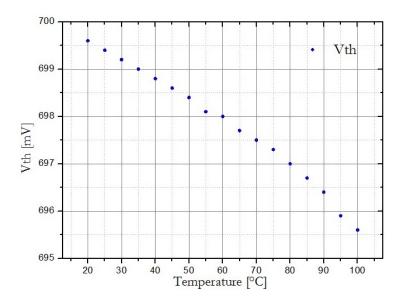

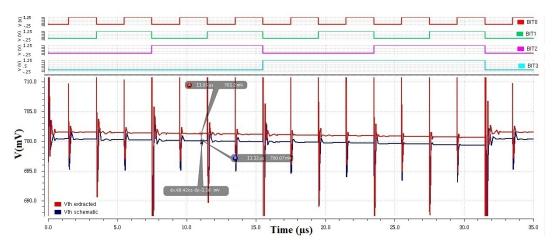

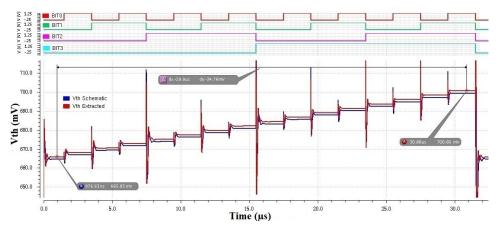

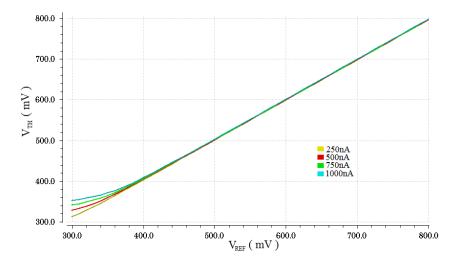

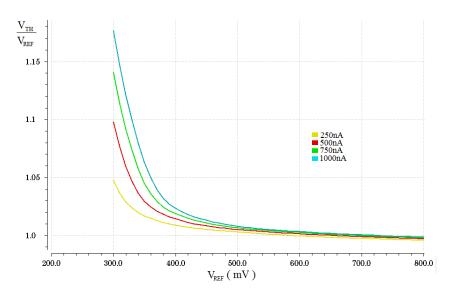

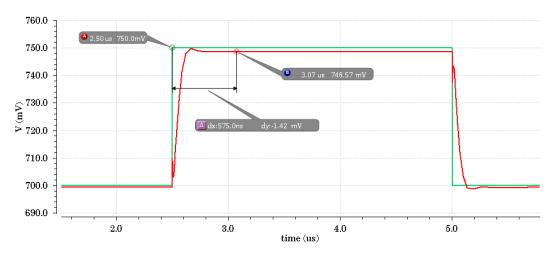

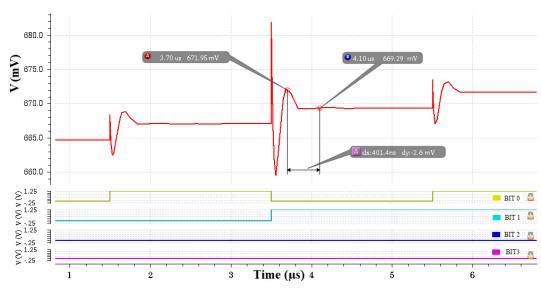

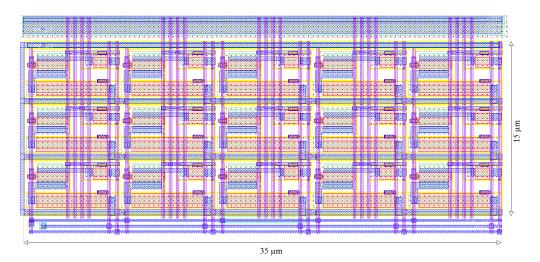

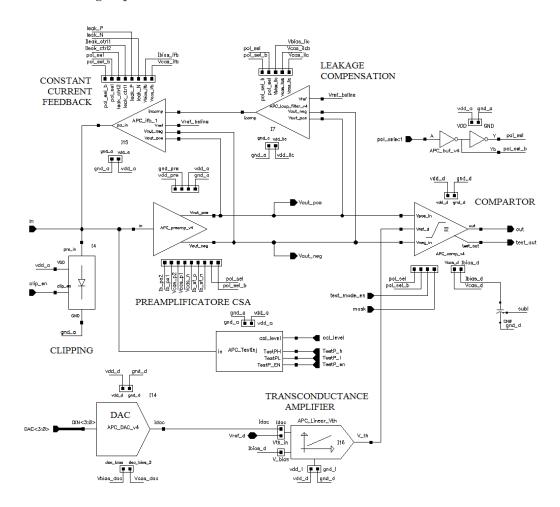

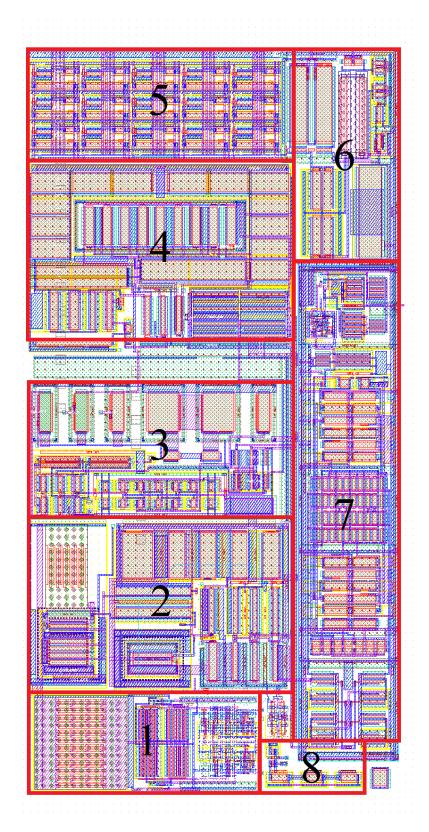

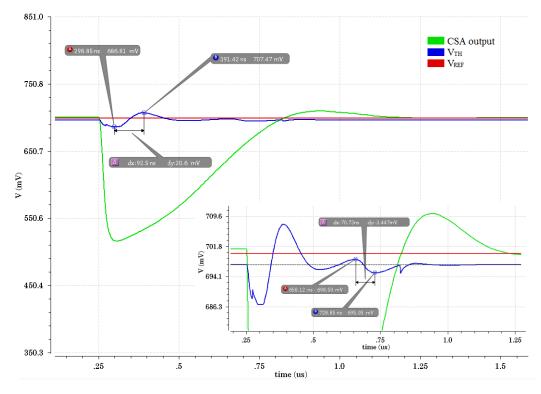

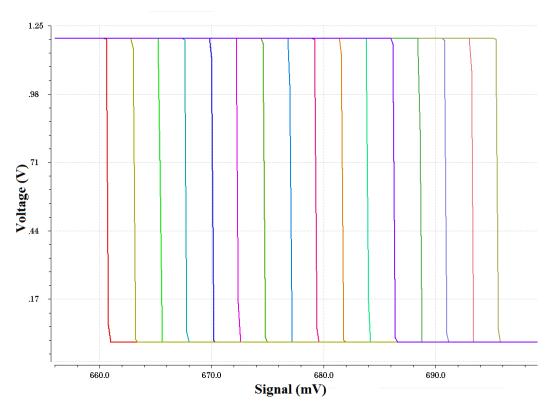

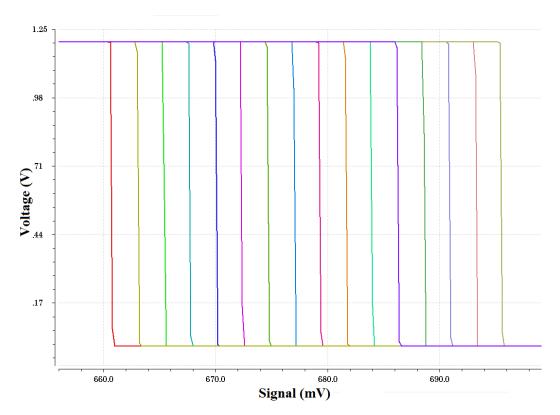

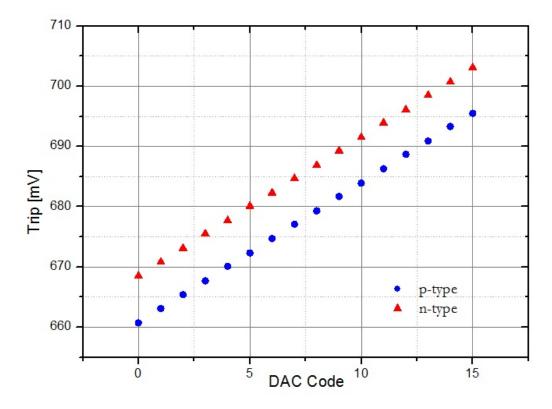

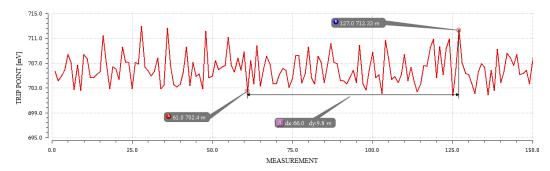

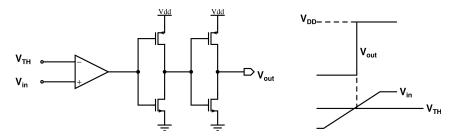

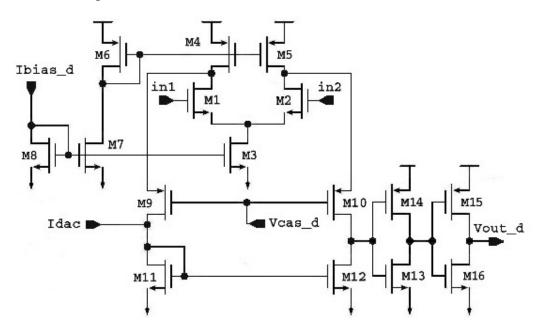

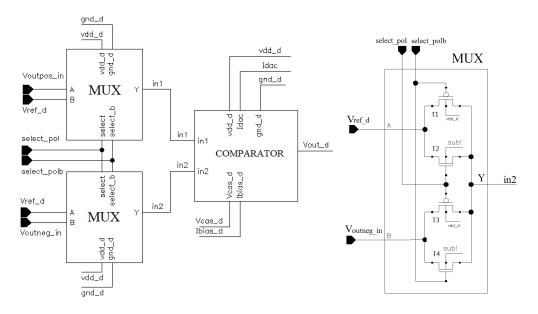

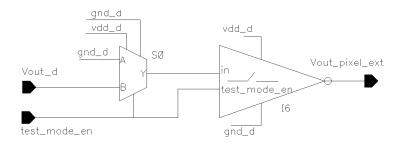

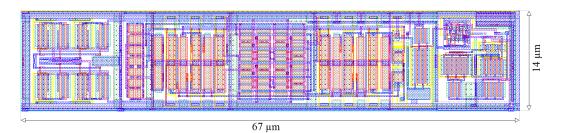

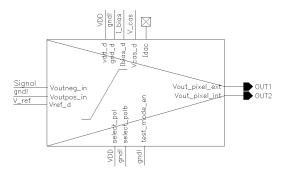

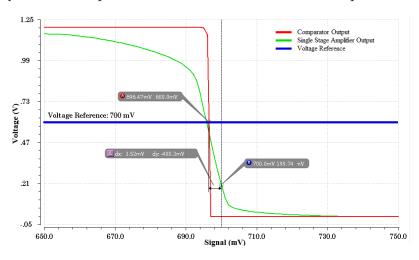

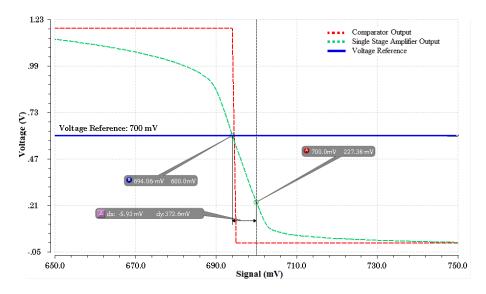

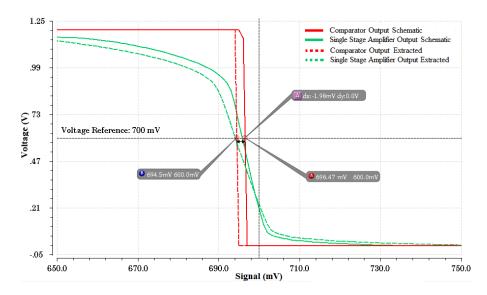

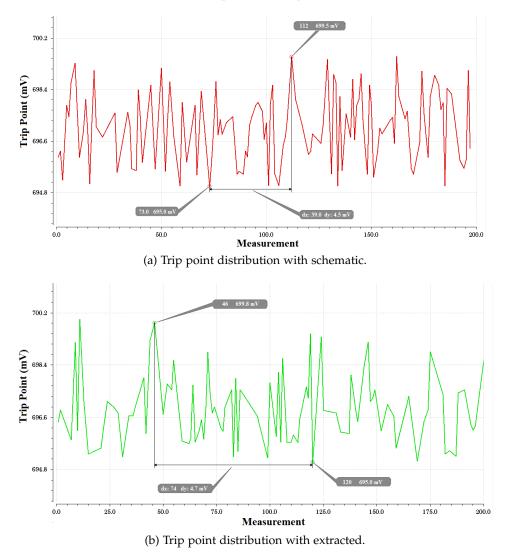

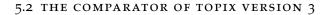

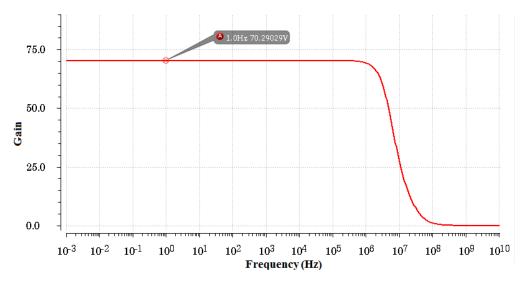

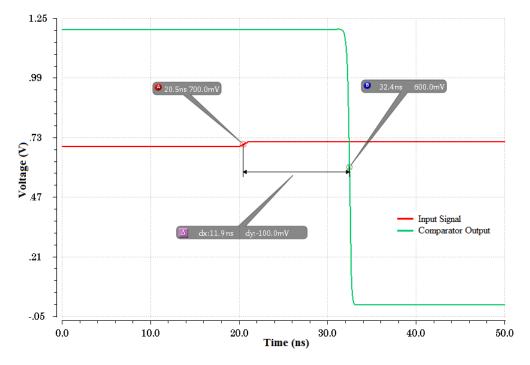

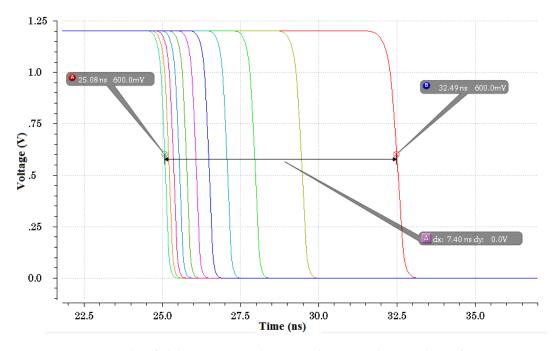

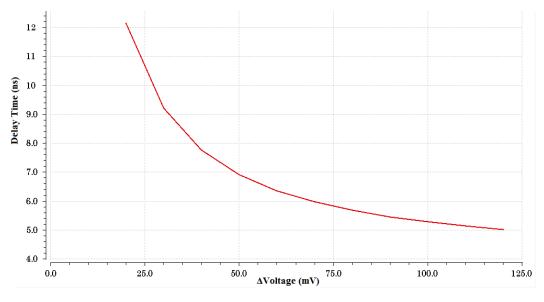

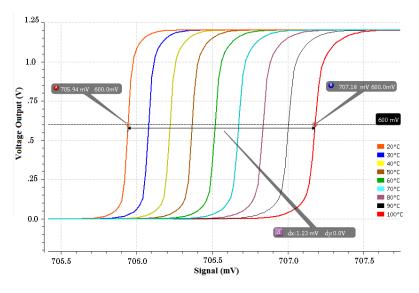

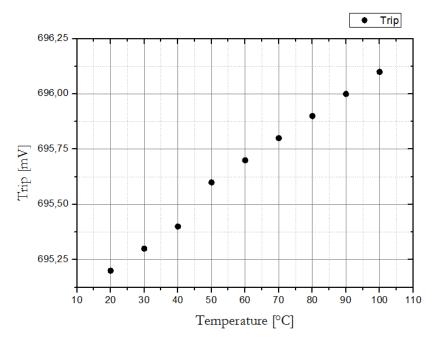

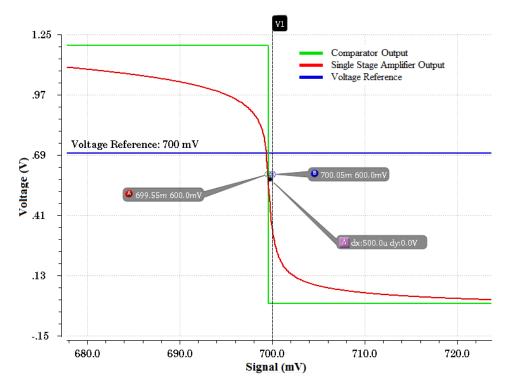

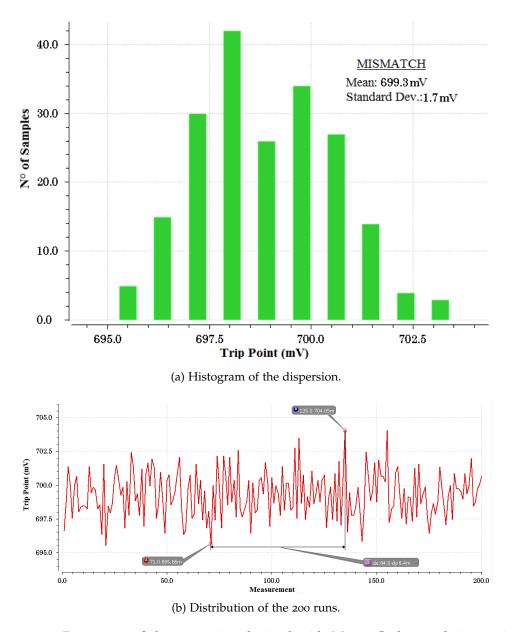

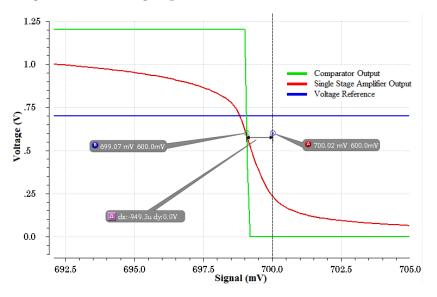

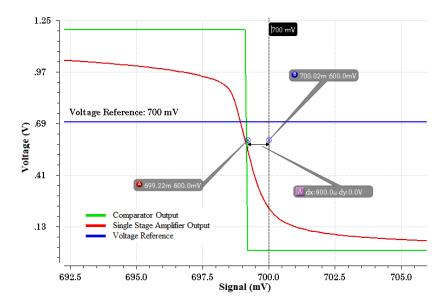

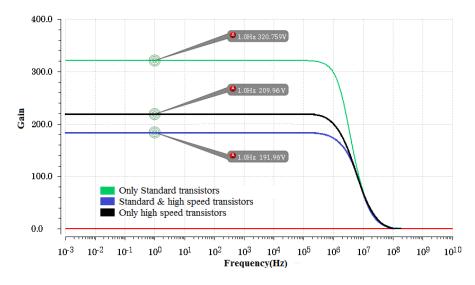

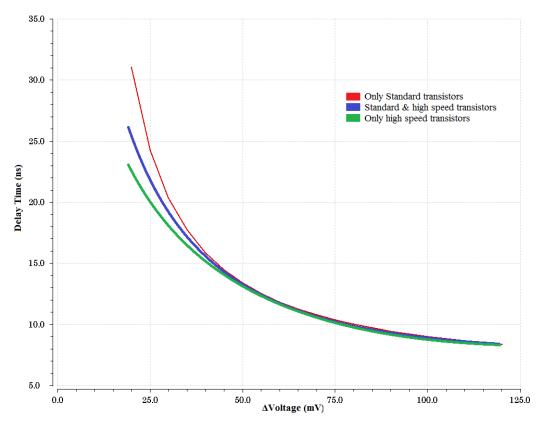

The front-end is designed to tolerate a power density of up to  $W/cm^2$  so that, due to high pixel density of about  $10^4 \text{ cm}^{-2}$ , a limit of  $15 \ \mu\text{W}$  has been put on the power consumption of the analogue pixel cell. Concerning the noise, it is a function of the bias current because, as will be explained later, it is mainly limited by the input transistor thermal noise. An Equivalent Noise Charge (ENC) of ~ 200  $e^-$  has been chosen as a good trade-off between minimum detectable charge and power consumption of the ASIC.