# LOW POWER FRONT-END ELECTRONICS FOR HYBRID PIXEL DETECTORS

~ Master Degree in Physics of Advanced Technologies ~

#### **SUPERVISOR**

Prof. Angelo Rivetti

#### <u>CANDIDATE</u>

Olave Elias Jonhatan

# **CONTEXT**

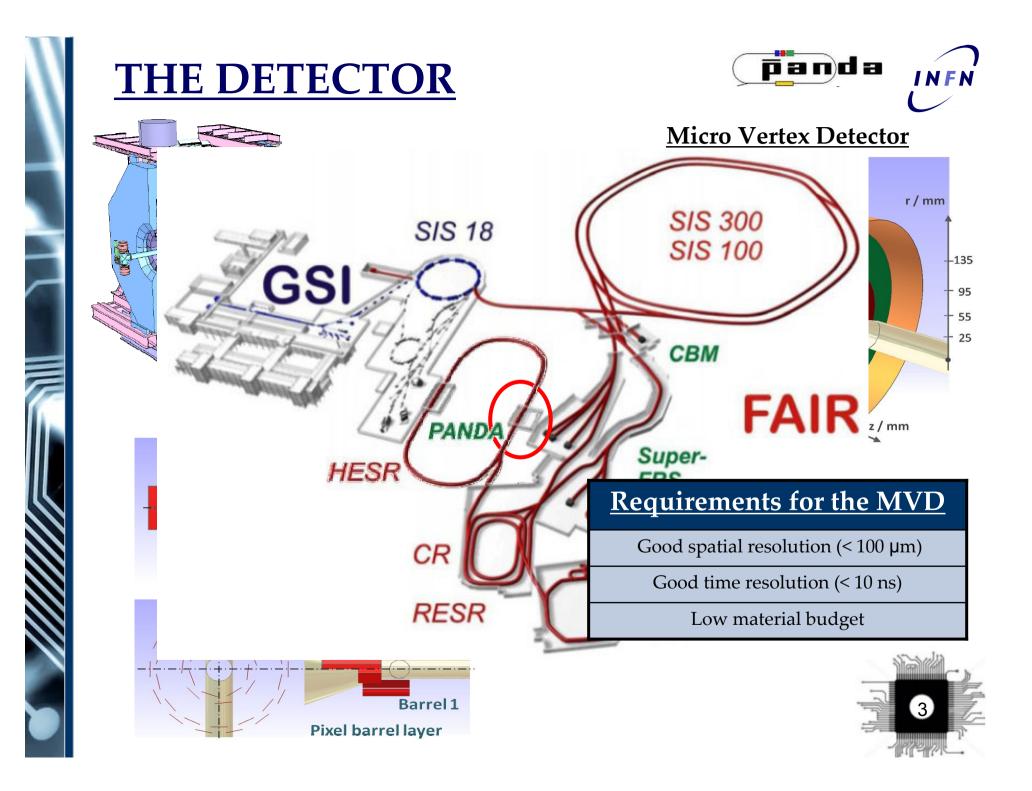

**Developement for the panda Detector**

# **WORK TOPIC**

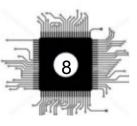

**Design of a new Digital to Analog Converter for the ASIC**

Study of a new technology for the ASIC

# **HYBRID PIXEL DETECTORS**

#### **ASIC Requirements**

| Measurements                | Hit position<br>Energy loss<br>Time |

|-----------------------------|-------------------------------------|

| Pixel Size                  | 100 μm x 100 μm                     |

| Time/charge<br>digitization | At pixel level                      |

| ASIC Size                   | Fixed by the pixel size             |

| Input Polarity              | Selectable                          |

| Trigger                     | Self triggering                     |

| <b>Power Consumption</b>    | < 20 µw                             |

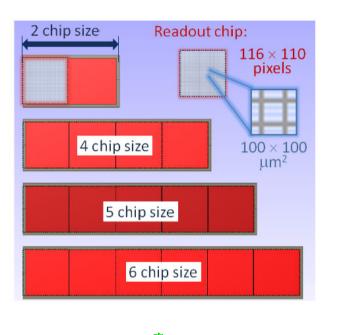

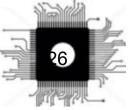

116 rows 110 cols

More channels are required

The compact design allow to optain a very good resolution also with high rates

Thinned silicon Cz substrate Epitaxial silicon layer Bump bonding Readout chip Carbon foam Carbon fiber Cooling system

The system allows a good correction

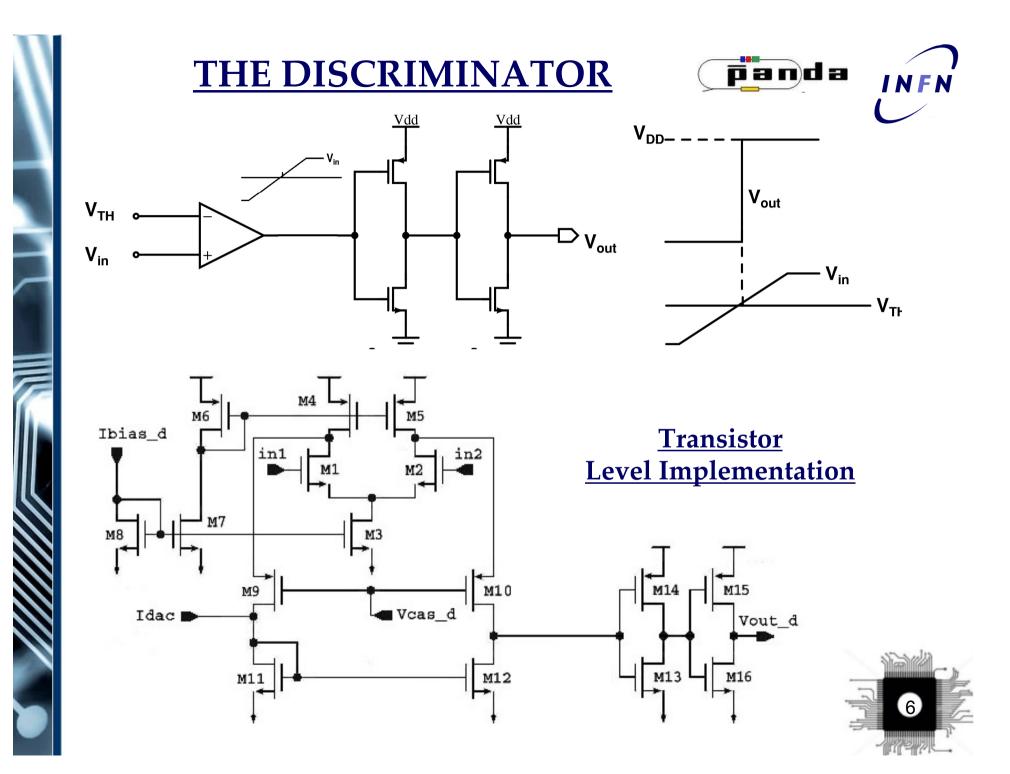

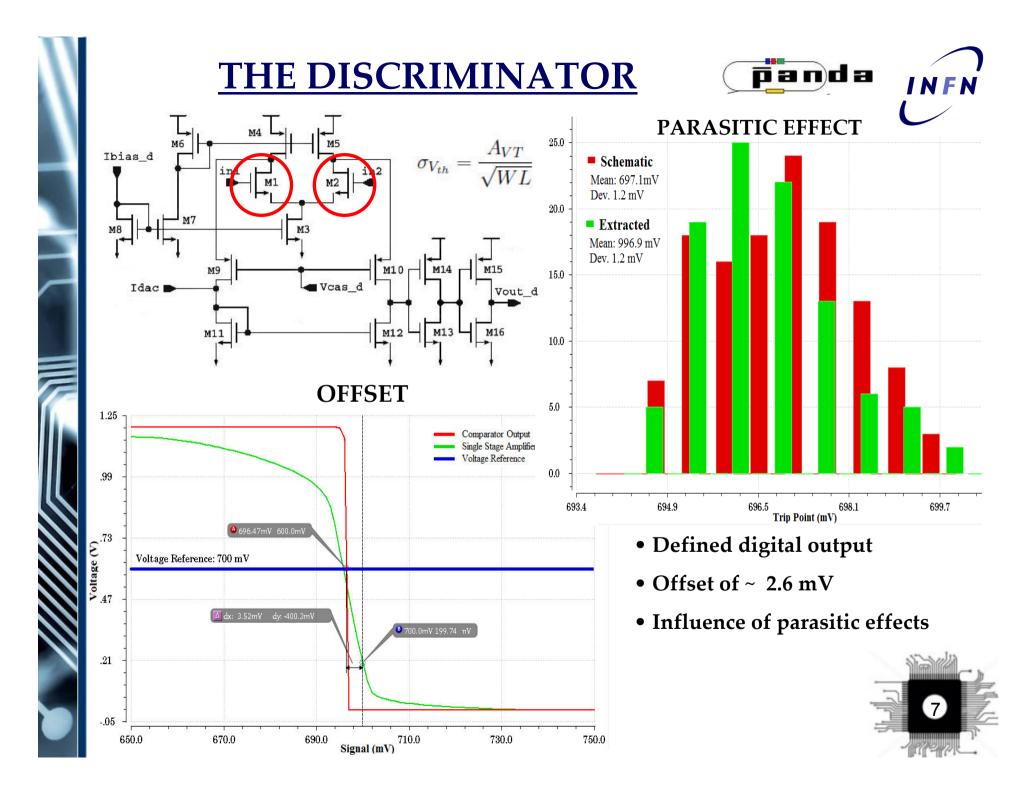

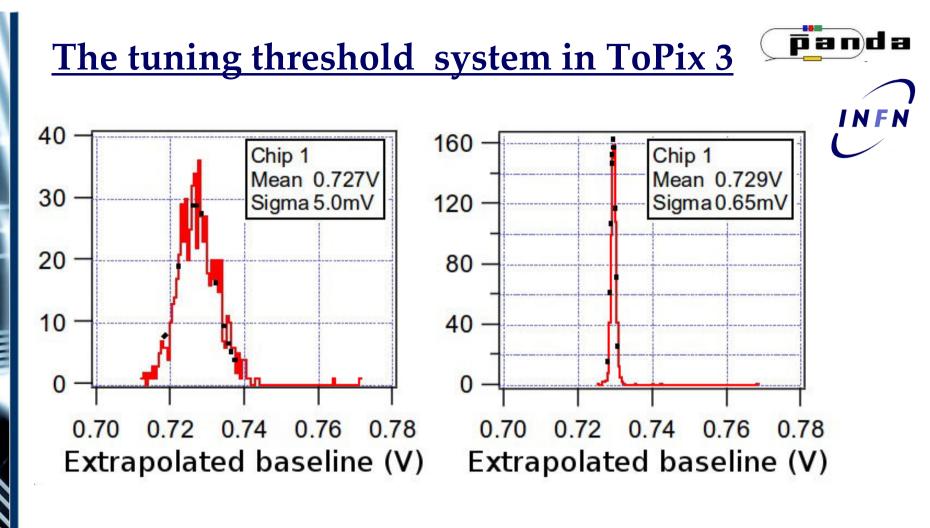

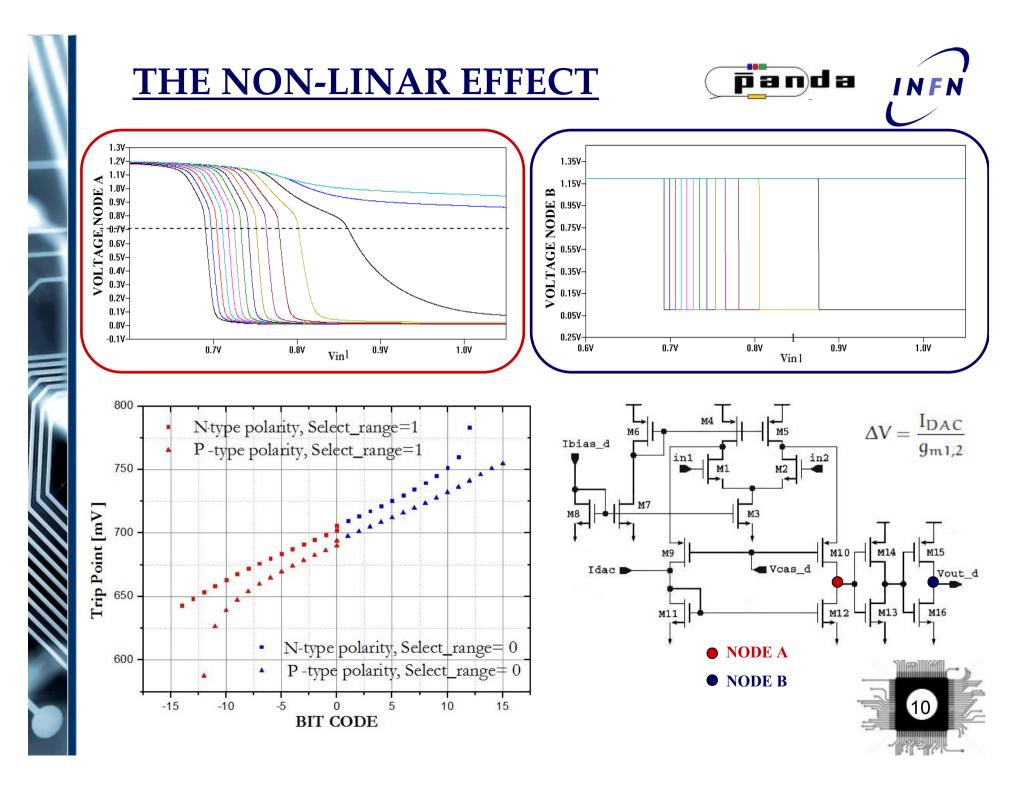

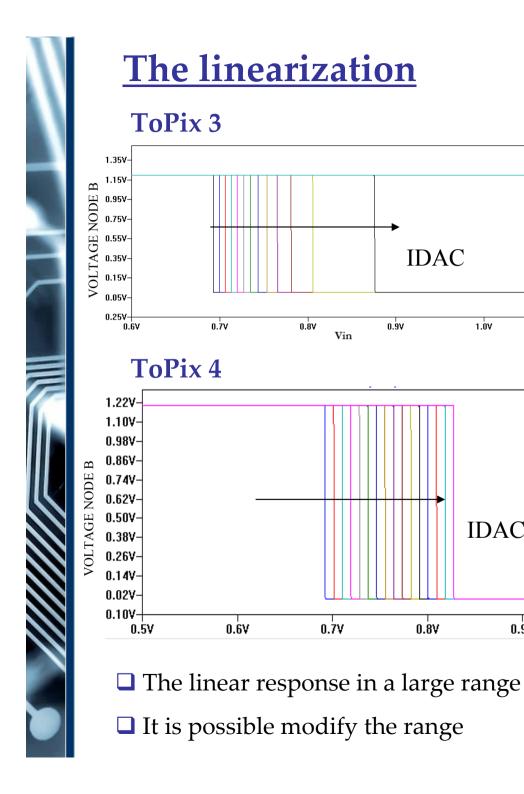

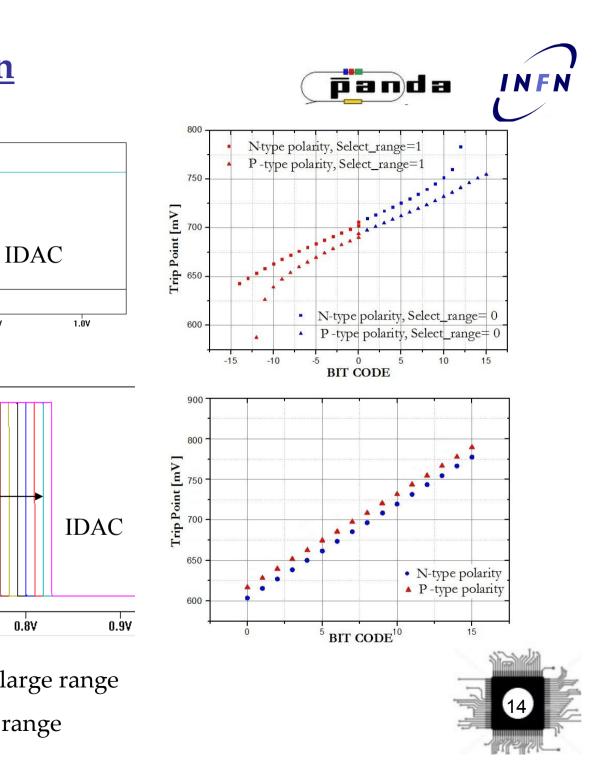

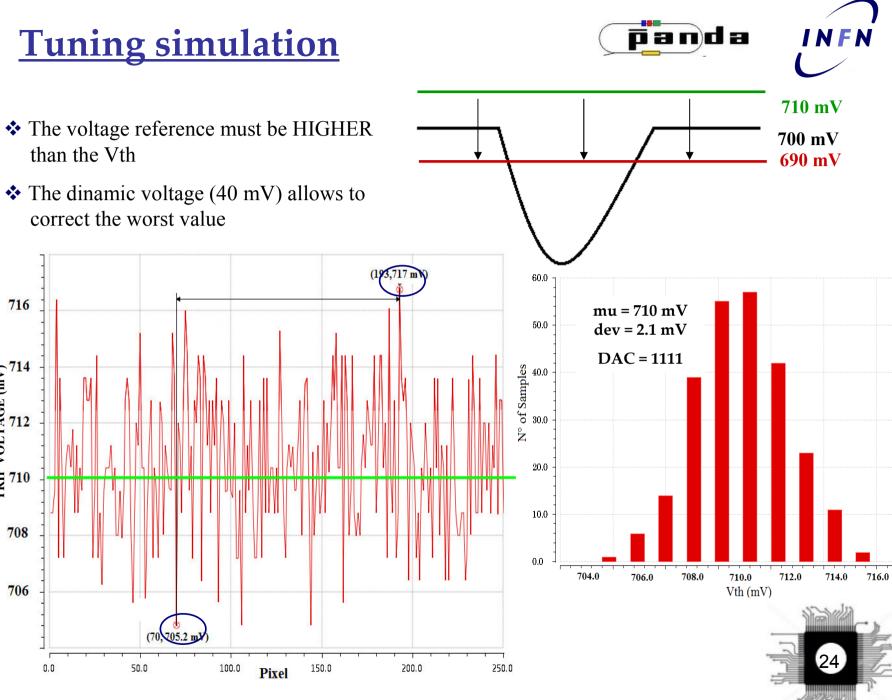

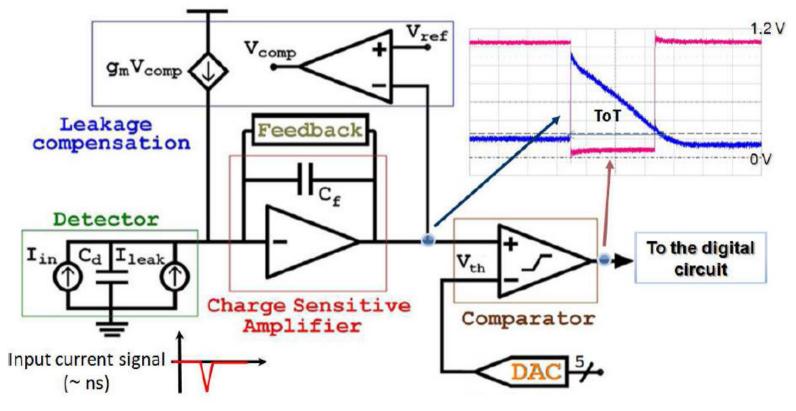

Due to a non-linear response the tuning procedure appears cumbersome

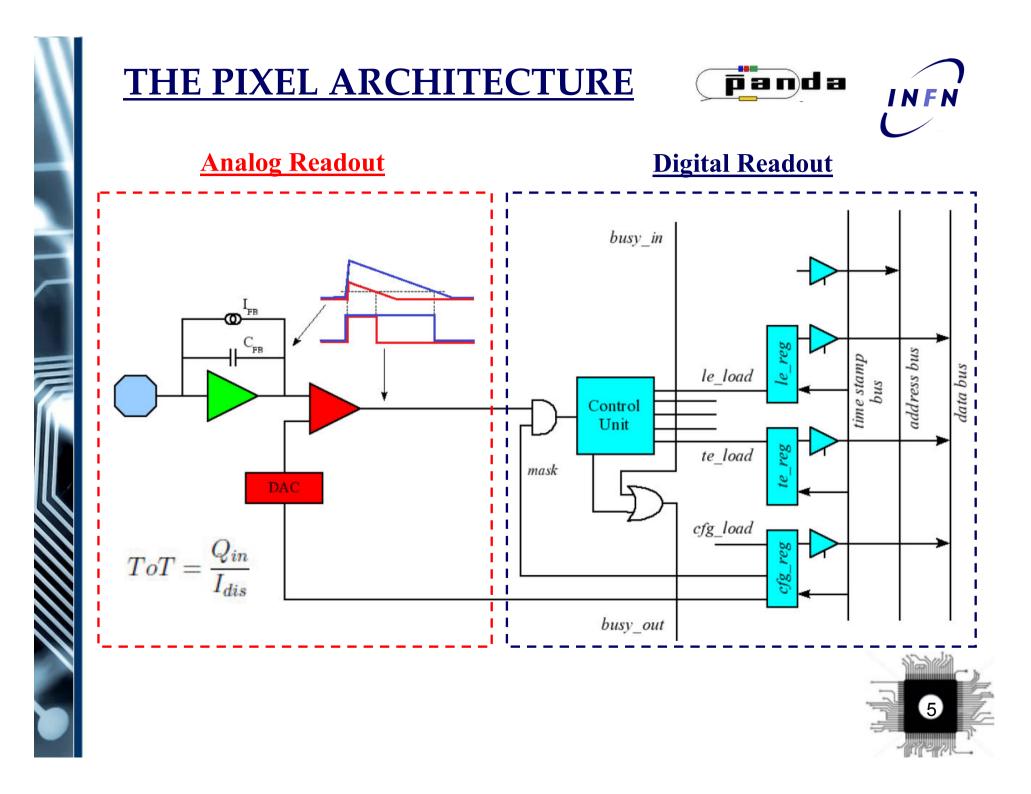

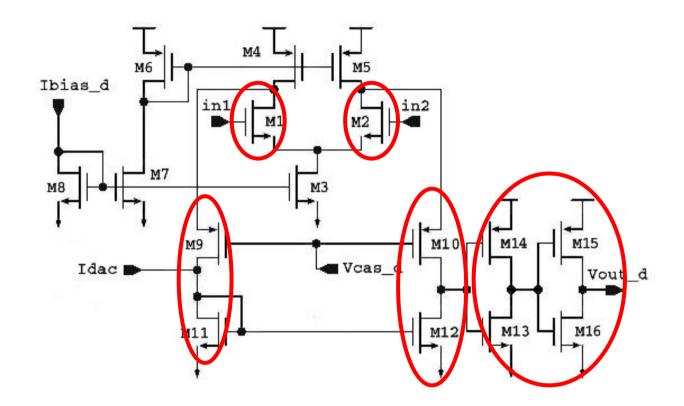

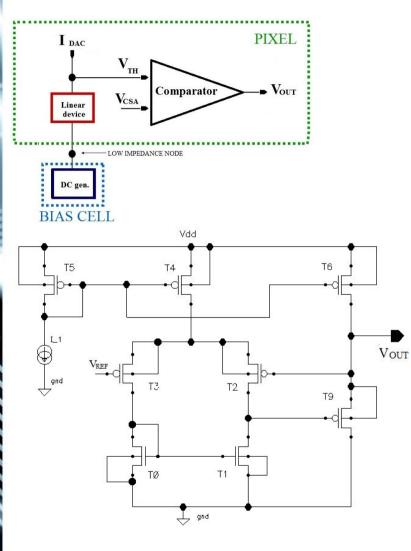

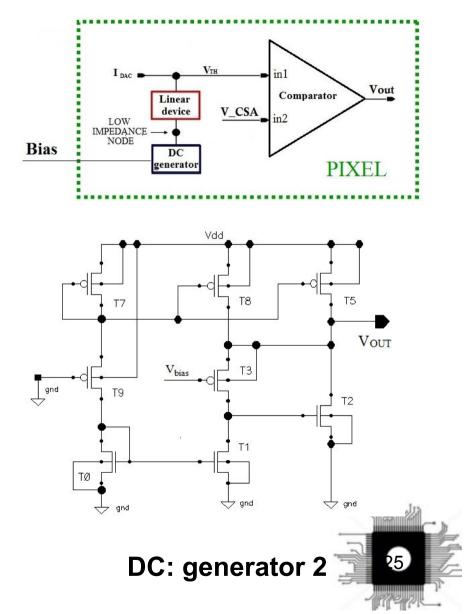

The devices involved are: COMPARATOR & DAC

Some trade-offs are necessary to fit the circuit in the available area.

0.9V

Vin

0.77

# **Results**

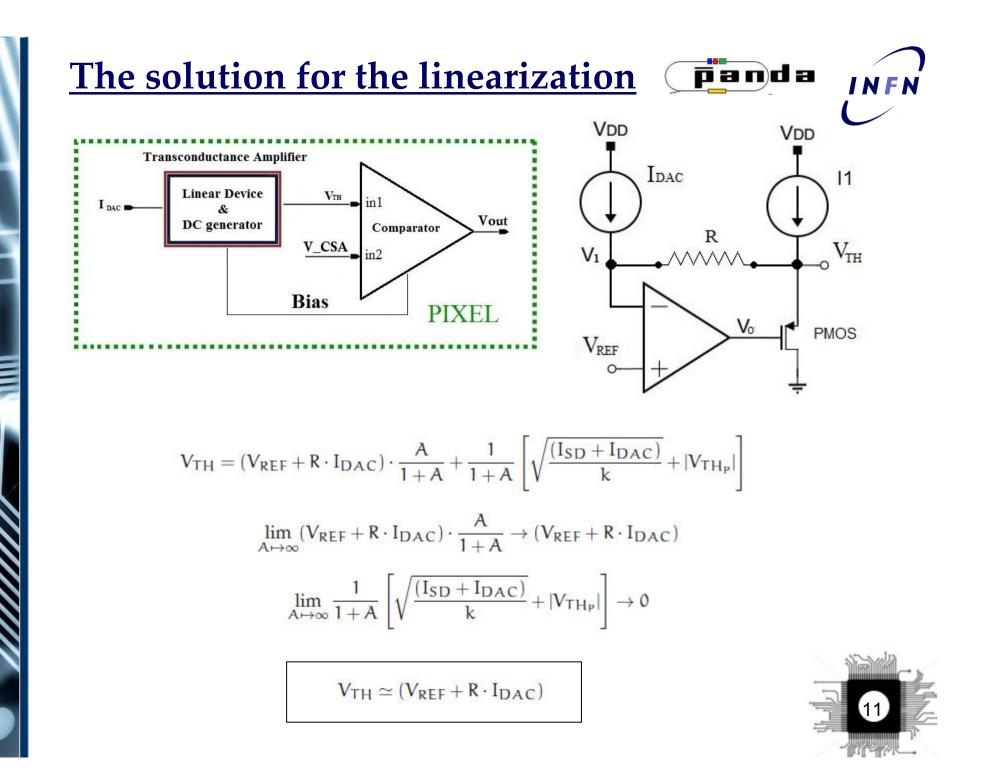

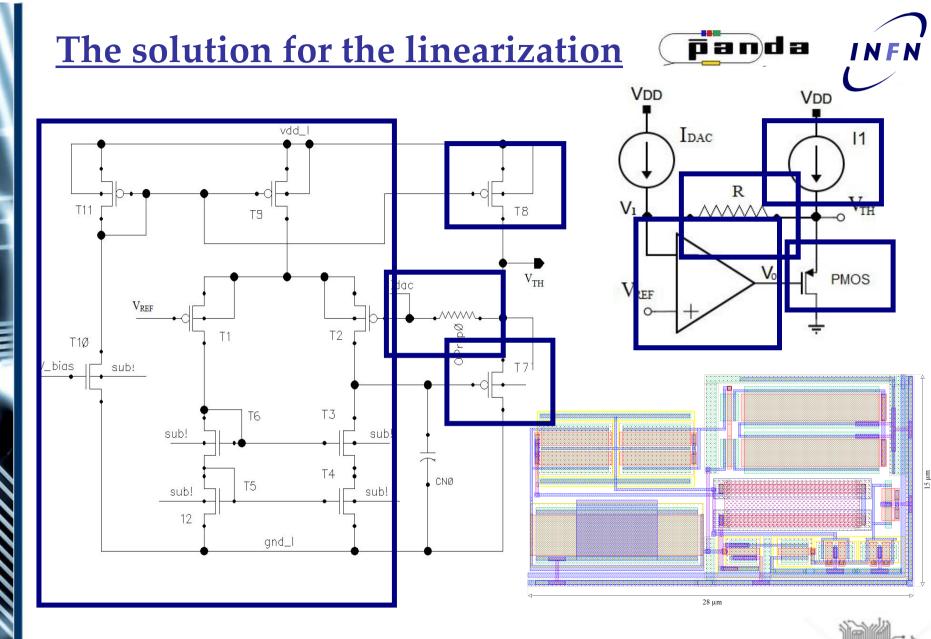

V<sub>TH</sub>

Comparator

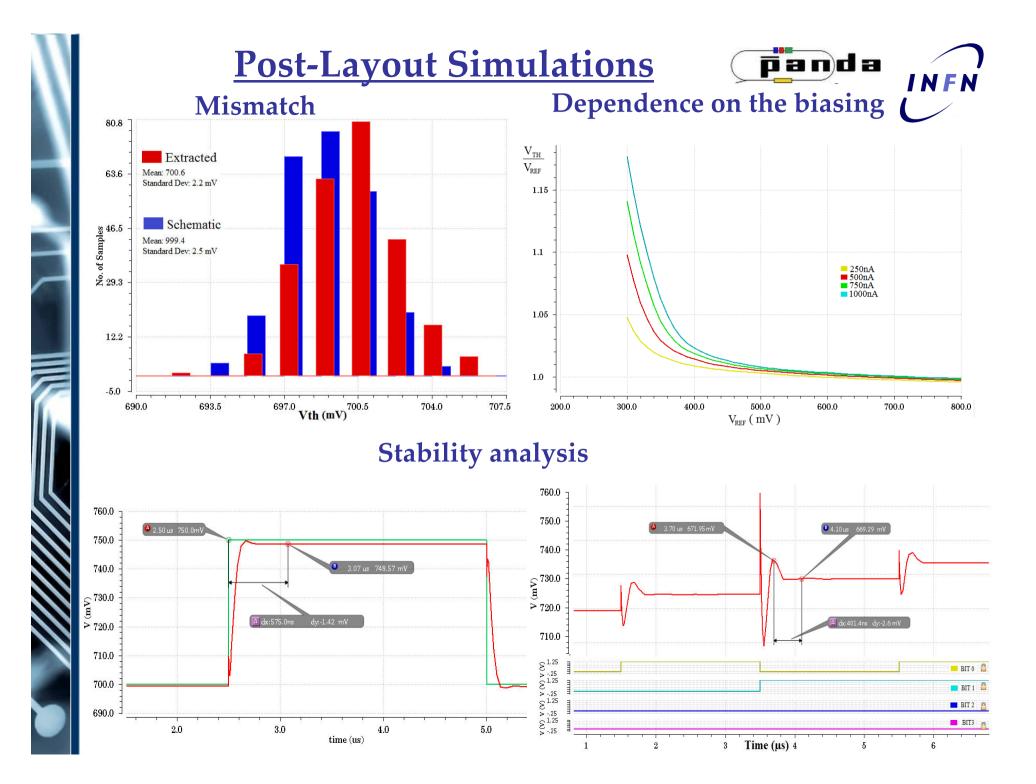

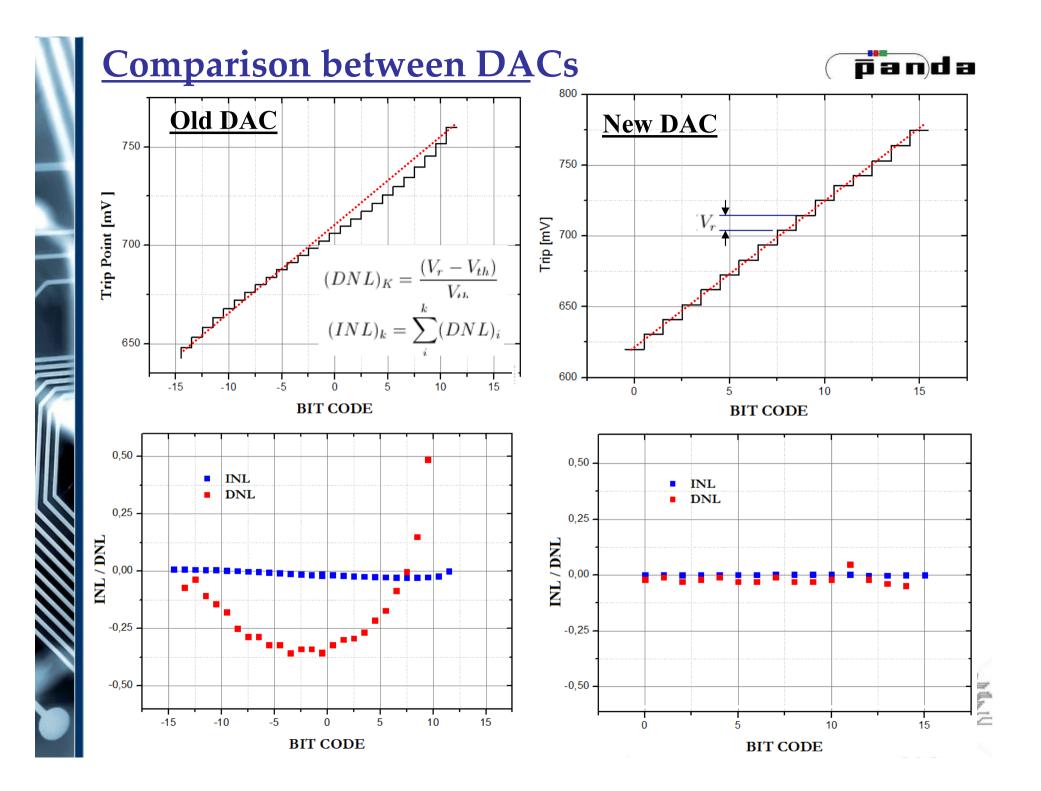

|                   | Mean value<br>MISMATCH | Dev.<br>Stand | Low<br>impedance<br>node | Homogeneity in<br>different pixels | External bias | DAC protection |

|-------------------|------------------------|---------------|--------------------------|------------------------------------|---------------|----------------|

| Solution A        | 700 mV 🛛 🗸             | 1 mV 🗸        | ✓                        | X                                  | X             | X              |

| Solution B        | 700 mV 🛛 🗸             | 1.8 mV 🗸      | <ul> <li>✓</li> </ul>    | <ul><li>✓</li></ul>                | X             | X              |

| Final<br>solution | 697 mV 🛛 💙             | 1.9 mV 🗸      | <ul> <li>✓</li> </ul>    | $\checkmark$                       | <b>v</b>      | $\checkmark$   |

PIXEL

- Vout

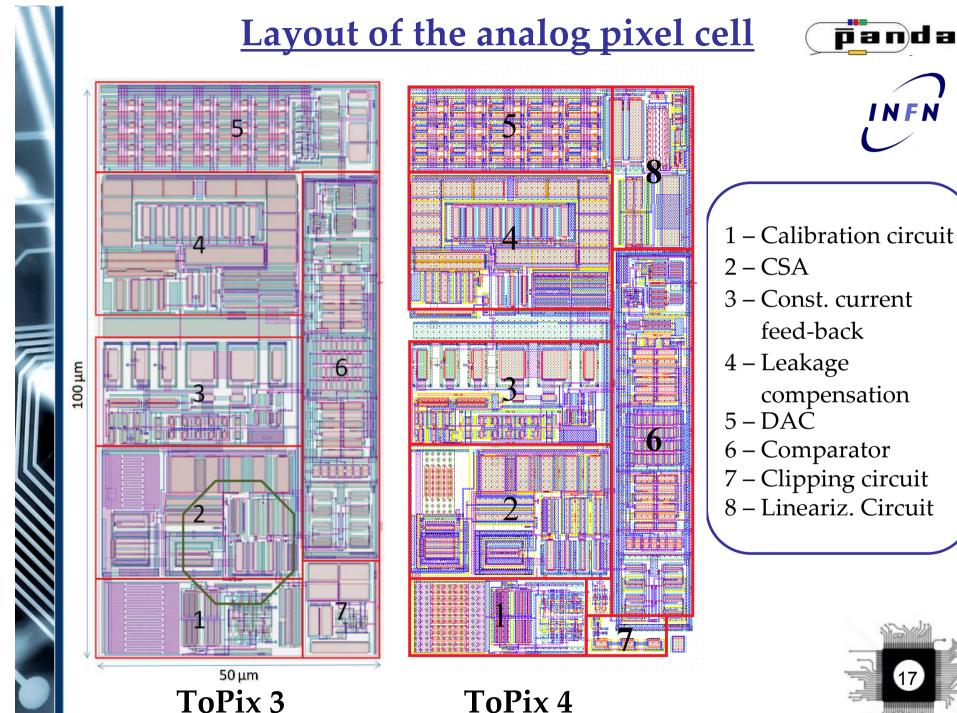

1 – Calibration circuit

INFN

- 3 Const. current

- 6 Comparator

- 7 Clipping circuit

- 8 Lineariz. Circuit

#### **Current Technology A 0.13 μm**

More flavors of devices

High cost

#### □ Proposed Technology B 0.11 µm

Less flavor of devices

Reduced cost

#### Gate oxide Drain terminal P Type N Type N Type

# **Study of the new technology**

### Three configurations

- Standard transistors

- High speed transistors and Stantard Transistors

- All High speed transistors

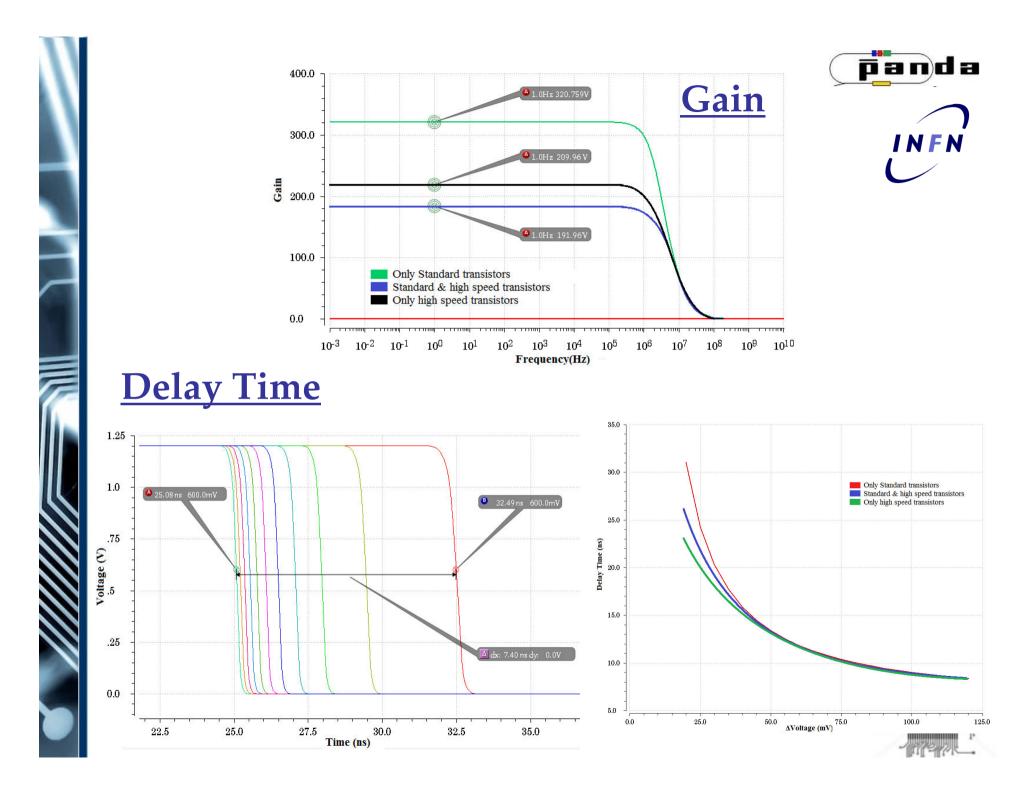

- **The analysis**

- ≻ Gain

- ≻ Offset

- Delay time

p a n d a

INFN

# <u>Results</u>

#### COMPARISON OF TECHNOLOGIES Technology A **Technology B** Stand. & High Speed Param. Standard Standard **High Speed** Trip[mV] 697 699 699 700 Gain 70 191 209 320 Delay[ns] 11 24 22 20 Delay'[ns] 8 8 8 5

#### □ <u>THE NEW TECHNOLOGY ALLOWS TO OBTAIN;</u>

- ➢ Higher gain

- Better control voltage

- ➢ Higher delay time

INFN

# **CONCLUSIONS**

• The solution for the tuning system has been found

- In Novembre 2013 ToPix 4 with the improvement realized was submitted to the foundry for fabrication.

- The analysis of the new technology shows good results for the comparator.

- The study of the new technology for the whole ASIC needs more studies.

# Thank you for your attention!

INFN

716

(MA) 714 (MA) 714 (MA) 712 (MA) 710 (MA

708

706

0.0

50.0

# **Tuning simulation**

than the Vth

# **Other solutions studied**

#### Solution A

DC: generator 1

## **The analogue pixel Architecture**

# **The ASIC for Hybrid Pixel Detectors**

-

| Measurements                | Hit position<br>Energy loss<br>Time |

|-----------------------------|-------------------------------------|

| Pixel Size                  | 100 μm x 100 μm                     |

| Time/charge<br>digitization | At pixel level                      |

| ASIC Size                   | Fixed by the pixel size             |

| Input Polarity              | Selectable                          |

| System Clock                | 155.52 MHz                          |

| Time resolution             | <10 ns                              |

| Trigger                     | Self triggering                     |

| Power Consumption           | $< 20 \ \mu W$                      |

| Noise Level                 | 200 e <sup>-</sup> rms              |

| Linear dynamic range        | Up to 50 fC                         |