#### Università degli Studi di Torino DIPARTIMENTO DI FISICA

Corso di Laurea Magistrale in Fisica

Tesi di Laurea Magistrale in Fisica

## Front-End amplifiers in 65nm CMOS technology for the upgrade of the pixel detector of the CMS experiment

Candidato: Ennio Monteil

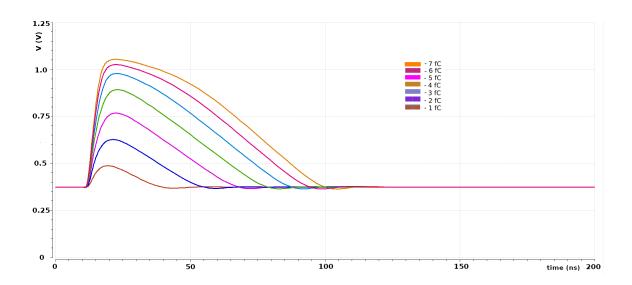

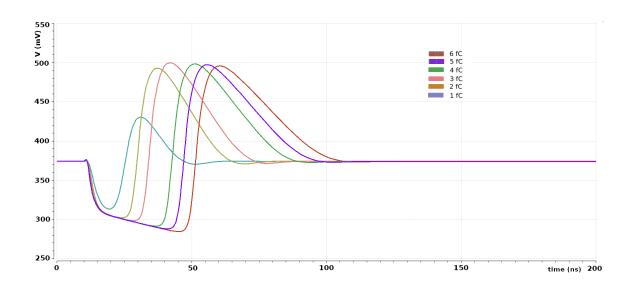

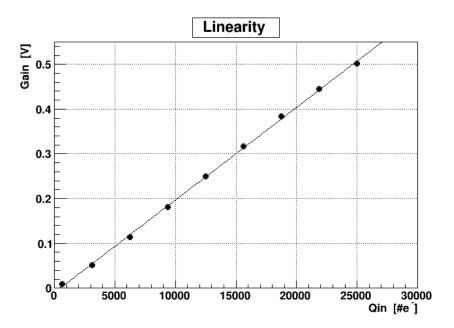

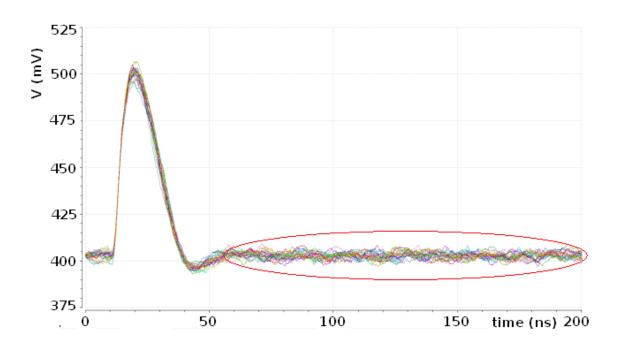

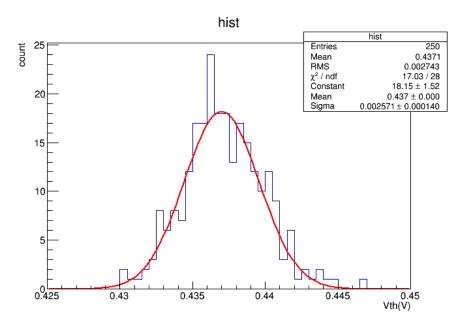

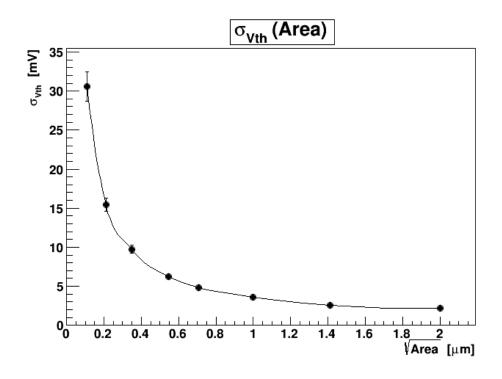

Relatore: Dott. Angelo Rivetti

Anno accademico 2012-13

#### Sommario

La tesi riguarda lo sviluppo di un chip innovativo per un rivelatore a pixel in tecnologia CMOS 65nm per l'upgrade dell'esperimento CMS previsto per l'High Luminosity Large Hadron Collider (HL-LHC) al CERN. La luminosità dell'acceleratore sarà aumentata di quasi un ordine di grandezza rispetto alla situazione attuale. Lo scopo principale dell'esperimento CMS è lo studio del bosone di Higgs e lo sarà anche all' HL-LHC, presso il quale misure di precisione saranno possibili. Per fare questo, è importante mantenere un rivelatore a pixel efficiente e performante anche nelle condizioni maggiormente ostili determinate da HL-LHC. Il rivelatore e la tecnologia attuale non sono sufficienti, pertanto un nuovo R&D è stato avviato sia sull'elettronica che sul sensore. La tesi descriverà in particolare il lavoro sulla catena analogica del nuovo chip per i pixel. I rivelatori a pixel, negli ultimi decenni, sono stati il motore dello sviluppo della tecnologia in HEP, dovendo integrare un'elettronica sofisticata in uno spazio piccolo, fronteggiando alti rate di dati per unità di area e un sensore altamente granulare. I futuri upgrade di LHC stanno spingendo ulteriormente i requisiti per il chip di lettura del pixel. Le principali sfide sono: pixel più piccoli per risolvere le tracce lasciate dalle particelle, più elevati rate di interazione  $(1 - 2GHz/cm^2)$ , tolleranza alle radiazioni senza precedenti (10 MGy), una banda di trasmissione fino ad alcuni GB/s per chip. Inoltre, è importante sviluppare un'elettronica analogica e digitale a bassa dissipazione di potenza, con lo scopo di coprire grandi aree mantenendo basso il quantitativo di materiale. In particolare l'elettronica di Front-End deve avere delle performance a basso noise, essendo al contempo molto compatta e mantenendo un basso consumo di potenza per unità di area. L'argomento di questa tesi è la progettazione di un preamplificatore di front-end, che è il primo blocco della parte analogica. Il lavoro di tesi è organizzato come segue:

- Nel capitolo 1 viene data una panoramica sui rivelatori al silicio e sulle loro proprietà, descrivendo il rivelatore a pixel di CMS e i relativi upgrade.

- Il capitolo 2 riguarda il transistor MOS. La prima parte del capitolo è dedicata alle principali proprietà di questi dispositivi. La seconda parte, invece, riguarda le tecnologie deep submicron CMOS, largamente utilizzate nei circuiti

elettronici per rivelatori di radiazione. Attraverso un confronto tra le tecnologie 65~nm CMOS e 250~nm CMOS, utilizzata nell'attuale chip di lettura, vengono presentati i problemi tipici di queste tecnologie.

- Nel capitolo 3 sono descritti gli elementi di base di un front-end ideale e di i problemi relativi all'implementazione reale, dando particolare attenzione al rapporto segnale-rumore.

- La tecnica di ottimizzazione del noise è riportata nel capitolo 4. Essa viene inoltre applicata a un Charge Sensitive Amplifier, mostrando attraverso le simulazioni al CAD le scelte che permettono la minimizzazione del noise.

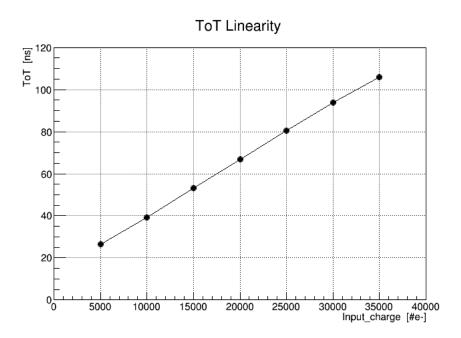

- Nel capitolo 5 vengono confrontati due Charge Sensitive Amplifier più realistici. Per ognuno sono riportate le simulazioni al CAD della potenza consumata, della linearità, del noise e dell'analisi dei mismatch. Viene inoltre studiata la compensazione della corrente di leakage del sensore.

#### Abstract

The thesis is focused on the development of an innovative chip for a pixel detector, using a CMOS 65nm technology, for the needed upgrade of the CMS experiment foreseen for the High Luminosity Large Hadron Collider (HL-LHC) at CERN. The luminosity of the accelerator will be increased of almost an order of magnitude with respect to the present.

The main purpose of the CMS experiment is the study of the Higgs boson and this will remain one of the main goals also at HL-LHC, where precision measurements will be possible. To do so, it is important to maintain an efficient and performant pixel detector even in the more hostile conditions determined by HL-LHC. Present detector and technology are not sufficient, so a new R&D has been launched on both the readout electronics and the sensor of the pixel and the thesis will describe in particular the work on the analog chain of the new pixel chip.

Pixel detectors, in the last decade, have been technology drivers in HEP, having to integrate sophisticated electronics in a small space, coping with high data rates per unit area and a very granular sensor. Future upgrades of LHC are pushing further the requests on a pixel chip. The challenges include: smaller pixels to resolve tracks in boosted jets, much higher hit rates  $(1 - 2GHz/cm^2)$ , unprecedented radiation tolerance (10 MGy), much higher output bandwidth up to few GB/s. Furthermore, it is important to develop highly performant and low power analog and digital electronics, in order to instrument large areas while keeping the material budget low. In particular the very front-end electronics must have low noise performance, while being very compact and maintaining a low power consumption per unit area.

The subject of this thesis is the design of a Front-End preamplifier, the first block of the analog part. The thesis work is organized as follows:

• In chapter 1 an overview about silicon detectors and their properties is given. Furthermore, the CMS pixel detector is described, focusing also on the upgrades and the related requirements.

- Chapter 2 is about MOS transistors. The first part is focused on the main properties of these devices. The second part, instead, is about the deep submicron CMOS technologies, largely used in electronics circuits for radiation sensors. Through a comparison between the 65 nm CMOS and the 250 nm CMOS technology, used in the present readout chip, the issues typical of these technologies are presented.

- In chapter 3 the basic elements of a front-end chain are described in order to explain the key principles driving the design. Consequently, the issues which occur in real circuits are presented. Particular attention is given to the signal-to-noise ratio, which is a primary parameter of any front-end circuit.

- In chapter 4 the noise optimization technique in deep submicron CMOS technologies is reported. In addition, this methodology is applied to a first simple Charge Sensitive Amplifier architecture. The results of the CAD simulations show the best choice which minimizes the noise contribution.

- In chapter 5, finally, two more complete Charge Sensitive Amplifier architectures are compared. For each of them the CAD simulations of the power consumption, gain linearity, noise performance and the mismatch analysis are carried-out. Furthermore, the compensation of the detector leakage current is also studied.

#### Table of contents

| 1        | Par | ticle d         | etection in high energy physics          | 1  |

|----------|-----|-----------------|------------------------------------------|----|

|          | 1.1 | Tracki          | ing detectors                            | 1  |

|          |     | 1.1.1           | Fundamental aspects                      | 3  |

|          | 1.2 | Silicor         | n sensors                                | 4  |

|          |     | 1.2.1           | Signal formation                         | 5  |

|          |     | 1.2.2           | Different types of silicon detectors     | 5  |

|          | 1.3 | The C           | CMS experiment                           | 7  |

|          |     | 1.3.1           | The CMS tracker                          | 8  |

|          |     | 1.3.2           | Pixel detector                           | 8  |

| <b>2</b> | Dee | ep subi         | micron MOS                               | 14 |

|          | 2.1 | NMOS            | S and PMOS                               | 14 |

|          |     | 2.1.1           | Silicon properties                       | 14 |

|          |     | 2.1.2           | NMOS transistor                          |    |

|          |     | 2.1.3           | PMOS transistor                          | 16 |

|          |     | 2.1.4           | MOS symbols                              | 17 |

|          |     | 2.1.5           | Success of CMOS technologies             | 18 |

|          | 2.2 | Electr          | ical characteristics of CMOS transistors | 18 |

|          |     | 2.2.1           | Threshold voltage                        | 19 |

|          |     | 2.2.2           | I/V characteristics                      | 19 |

|          |     | 2.2.3           | Weak inversion operation                 | 21 |

|          |     | 2.2.4           | Small signal parameters                  | 22 |

|          |     | 2.2.5           | The $g_m/I_D$ method                     |    |

|          | 2.3 | Deep :          | submicron CMOS technologies              |    |

|          |     | 2.3.1           | Scaling theory                           | 25 |

|          |     | 2.3.2           | Short-channel effects                    |    |

|          | 2.4 | $65\mathrm{nm}$ | vs 250nm                                 | 28 |

|          |     | 2.4.1           | Summary                                  | 32 |

| 3  | From  | nt-End amplifiers                                  | 33        |

|----|-------|----------------------------------------------------|-----------|

|    | 3.1   | Front-End amplifier                                | 33        |

|    |       | 3.1.1 Charge Sensitive Amplifier                   | 34        |

|    |       | 3.1.2 CR-RC shaper                                 | 35        |

|    | 3.2   | Noise in electronics systems                       | 38        |

|    |       | 3.2.1 Types of noise                               | 39        |

|    |       | 3.2.2 Noise in CMOS technologies                   | 39        |

|    |       | 3.2.3 Noise in Front-End amplifiers                | 40        |

|    | 3.3   | Noise calculations                                 | 41        |

|    |       | 3.3.1 Parallel noise calculation                   | 42        |

| 4  | Noi   | se optimization of the Charge Sensitive Amplifier  | 46        |

| -  | 4.1   | Noise optimization of a Charge Sensitive Amplifier | 46        |

|    | 1.1   | 4.1.1 Transistor in strong inversion               | 47        |

|    |       | 4.1.2 Transistor in moderate or weak inversion     | 48        |

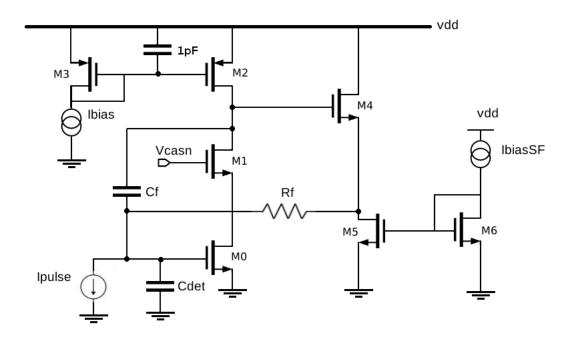

|    | 4.2   | Studied architecture                               | 52        |

|    | 1.2   | 4.2.1 Sensor model                                 | 52        |

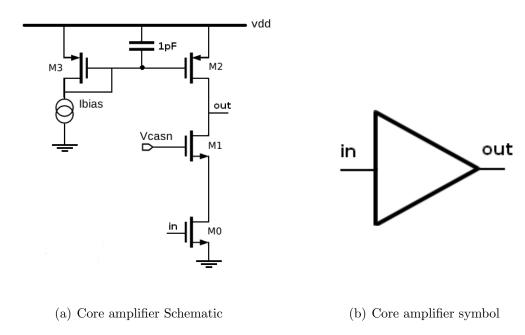

|    |       | 4.2.2 Charge Sensitive Amplifier architecture      | 53        |

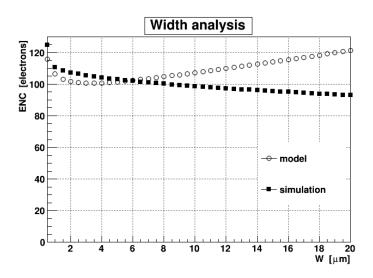

|    |       | 4.2.3 Channel width analysis                       | 53        |

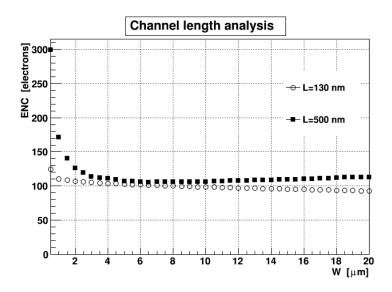

|    |       | 4.2.4 Channel length analysis                      | 55        |

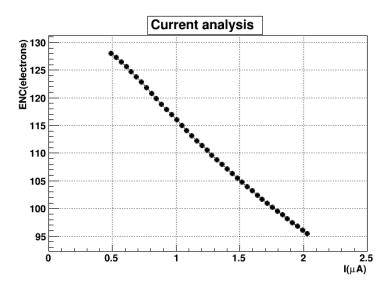

|    |       | 4.2.5 ENC vs current analysis                      | 56        |

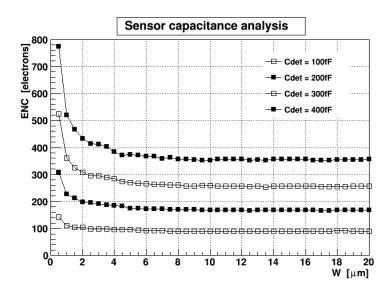

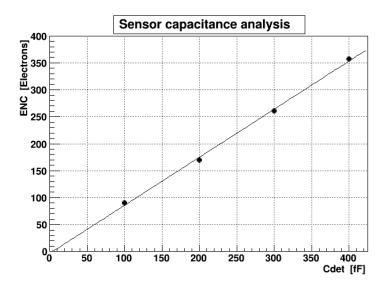

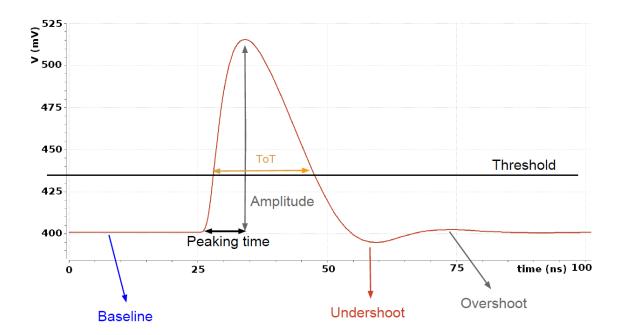

|    |       | 4.2.6 Sensor capacitance analysis                  | 57        |

|    |       | 4.2.7 Summary                                      | 58        |

| 5  | Dec   | cults of simulations                               | 59        |

| J  | 5.1   | Analysis                                           | <b>59</b> |

|    | 5.2   | Feedback network implementation                    | 61        |

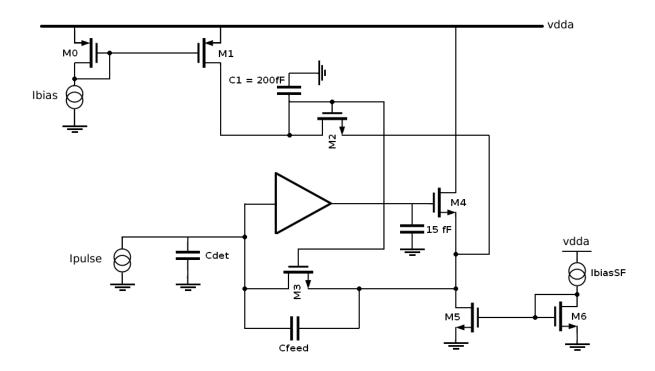

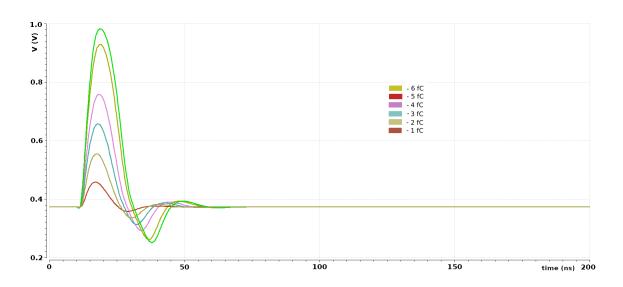

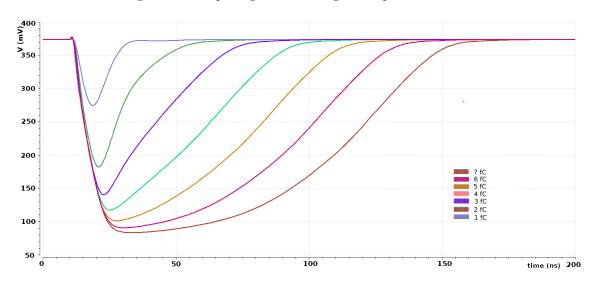

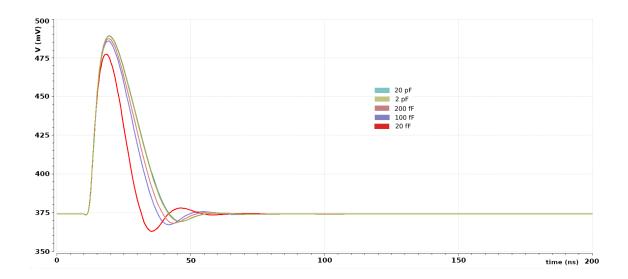

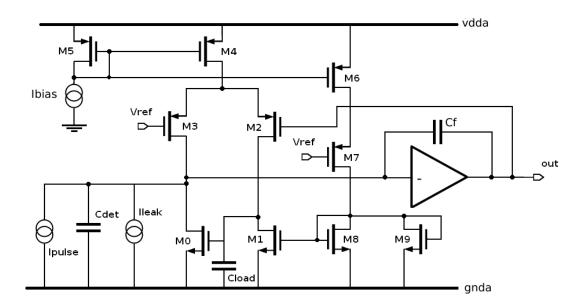

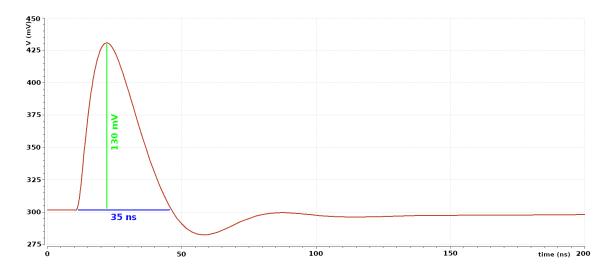

|    | 5.2   | 5.2.1 First architecture                           | 61        |

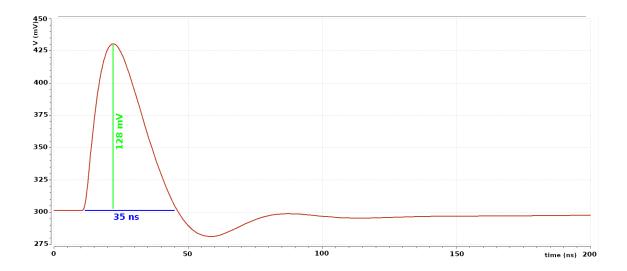

|    |       | 5.2.2 Second architecture                          | 75        |

|    |       | 5.2.3 Summary                                      | 84        |

|    | 5.3   | 0. <u></u>                                         |           |

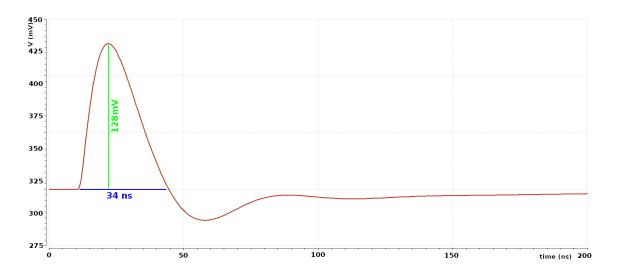

|    | 5.5   | Leakage compensation                               | 91        |

|    | 5.4   | 5.3.1 Summary                                      | 92        |

|    | 0.4   | 1 rospects for time-variant integrators            | 92        |

| 6  | Con   | nclusions                                          | 96        |

| Bi | bliog | graphy                                             | 99        |

#### Chapter 1

### Particle detection in high energy physics

The first part of this chapter deals with the basic concepts of particle detection, focusing in particular on silicon detectors and their properties. The second part is about the CMS experiment, located at the LHC at CERN. A large section of this chapter is about the CMS pixel detector, giving particular attention to the phase 2 pixel upgrade. The front-end architectures studied in this work, in fact, are designed in order to meet the requirements given by this subsystem.

#### 1.1 Tracking detectors

A detector is a device which describes particles properties through the detection of charged or neutral particles. All the detectors are based on the same principle: the particle which goes through the detector volume leaves some energy which is converted in an electrical signal analyzed by an electronic circuit.

In order to identify a particle it is necessary to combine the information which comes from different detectors. In particular tracking detectors are used to measure the particle momentum through a magnetic field and to reconstruct the primary vertex of the interaction. This device is also able to perform a measurement of the energy loss per unit path-length (dE/dX) which is an additional information for particle identification.

In the sensor design a key parameter which has to be taken into account is the mechanism with which charged particles lose energy into materials. This phenomenon happens due to scattering processes with the particles of the detector layers.

The main process is the inelastic Coulomb scattering with the atomic electrons.

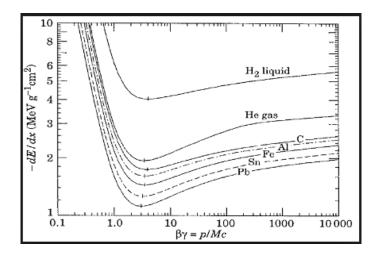

In the region of  $0.1 < \beta \gamma < 10^4$  this energy loss is described by the Bethe-Bloch formula:

$$- \langle \frac{dE}{dx} \rangle = Kz^2 \frac{Z}{A\beta^2} \left[ \frac{1}{2} ln \left( \frac{2m_e c^2 \beta^2 \gamma^2 T_{max}}{I^2} \right) - \beta^2 - \frac{\delta}{2} - \frac{C(I, \beta \gamma)}{Z} \right]$$

(1.1)

with:

$K = 4\pi N_{av} r_e^2 m_e c^2 = 0.30707 \ MeV \times cm^2$  with  $r_e$  classical electron radius

z charge of the incident particle in units of electron charge

Z atomic number of absorption medium (14 for Si)

A atomic mass of absorption medium (28 for Si)

$m_e c^2$  rest energy of the electron

$\beta$  velocity of the incident particle in units of c

$\gamma$  Lorentz factor  $(1-\beta^2)^{\frac{1}{2}}$

I mean excitation energy (137 eV for Si)

$T_{max}$  maximum kinetic energy transfer in single collision

The term  $(\delta/2)$  is a density effect correction and occurs at high energies due to a relativistic expansion of the electric field of the ionizing particle resulting in a slowdown of the logarithmic slope of the function. The term (C/Z) is a shell correction relevant at low energies because in this case electrons are not free and there is a screening effect for the most internal ones.

Figure 1.1: Energy loss for different particles

As one can see from Figure 1.1 the dE/dx is very high for low energy particles and decreases with the increase of particles energy until a minimum: a particle whose energy corresponds to this minimum value is called MIP (Minimum Ionizing

Particle). After the minimum the dE/dx increases with energy until it reaches a plateau for high energy particles.

In Figure 1.1 it is also possible to see that this equation is mass dependent especially in the low momentum region. This dependency can be expected for PID purposes.

#### 1.1.1 Fundamental aspects

Every detector has some features which influence its behavior. In the following paragraphs a list of the main ones is presented.

• **Point resolution** The resolution of a detector is the minimum value of a physical quantity that it is possible to detect with the device. In the case of tracking detectors the target is to have a good vertex resolution: in high energy physics processes a lot of particles decay very little after the primary interaction, giving rise to secondary vertices which are very close to the interaction points.

Another important aspect is the momentum resolution, which plays a key role in the particle identification. In order to measure the momentum, a magnetic field is applied in the detector, leading to a deflection of the charged particles, as described by the Lorentz force formula:

$$F = q(\vec{v} \times \vec{B}) \tag{1.2}$$

Equating the module of this force to the module of the centrifugal force:

$$qvB = \frac{mv^2}{r} \tag{1.3}$$

which, using p = mv becomes:

$$p = qBr (1.4)$$

- Occupancy The occupancy of a detector refers to the number of busy channels, i.e. the number of channels hit by a particle. It is expressed as a percentage. If the occupancy value is too high the tracking becomes ambiguous. Since the pixel detectors at LHC constitute the seed of tracking, it is necessary to have a very low occupancy, below 1%.

- Dead time and pile-up Another very important concept, strictly related to the occupancy is the dead time( $\Delta t$ ), which is the time that the detector takes to process an event and mainly depends on the front-end electronics. It is crucial to reduce it as much as possible in order to increase the speed (and then the number of processed events) and because during the dead time the detection of the next event is not correct. It is possible to identify two different situations:

- If the detector remains unsensitive during the dead time the subsequent event will be lost

- If the detector remains *sensitive* the pile-up of the events occurs, leading to a distortion of the signal and loss of information about the two events.

- Radiation hardness High energy physics experiments are characterized by a large amount of radiation, which has to be tolerated especially by the tracking detectors, which are the most internal ones. It is a fundamental requirement which has to be fulfilled in order to have sensors which can work for a long time (some years) without losing too much in performance.

Regarding the tracking detectors, the best choice to meet these requirements is the use of semiconductor sensors, which are usually made of silicon.

#### 1.2 Silicon sensors

Silicon (A=28, Z=14) is a semiconductor material with a bandgap of 1.12 eV, and the energy required to create an electron-ion pair is 3.6 eV. Another important property is the high mobility of the charged carriers which allows a very fast charge collection time.

As described in paragraph 1.1, particles energy loss is described by the Bethe-Bloch formula. This energy loss leads to the formation of a number of electron-ion pairs proportional to the amount of energy. It is possible to calculate the amount of pairs created by a MIP using the following formula

$$Q_{average} \simeq 100 \frac{q_e}{\mu m} d \tag{1.5}$$

with:

$Q_e$  charge of an electron

d sensor thickness in  $\mu m$

so for example for a thickness of 250  $\mu m$ , which is one of the typical values used, around 25000 electron-hole pairs are produced.

It is important to underline that this is only an average value of a Landau distribution, which has a remarkable tail, so the most probable value is different from the average value. The fluctuation around the maximum is more important if the sensor is thinner: this situation has to be taken into account in the readout circuit design because it affects the dynamic range, i.e. the maximum allowable

voltage swing divided by the total noise voltage in the band of interest [1]. The main reason of the fluctuation is the production of the  $\delta$ -electrons which is a quite rare but significant process, because their direction is perpendicular to the direction of the ionizing particle leading to irregular charge clouds and worse spatial resolution.

#### 1.2.1 Signal formation

Silicon detectors are realized with different technologies but all of them are based on the same principle: they consist of a reverse bias pn junction. In a normal pn junction there is a transition between n-doped and p-doped material, in which some majority charges of one side diffuse into the differently doped side due to concentration difference. For this reason there is a recombination which leads to the formation of a region, close to the junction, where there are no free charge carriers. Therefore, it is called "depletion region". [2]

The sensor junction is reversely biased, in fact an electric field is applied to the two electrodes leading to the largest possible increase of the width of the depletion region. If a free charge enters this region, it will be removed by the electric field, so the charge carriers produced by a ionizing particle drift towards the electrode with the most favorable potential, producing a current in both the electrodes which can be read out.

#### 1.2.2 Different types of silicon detectors

In particle physics different types of silicon detectors are used. The feature which mainly differentiate one of them by another is the shape of the electrodes. For example, silicon strip detectors are segmented in long and narrow elements, the strips, and each of them is an independent reverse-biased pn junction, while pixel detectors are segmented in smaller square elements. For the purposes of this work it is useful to investigate the pixel detector behavior in detail.

#### Silicon pixel detectors

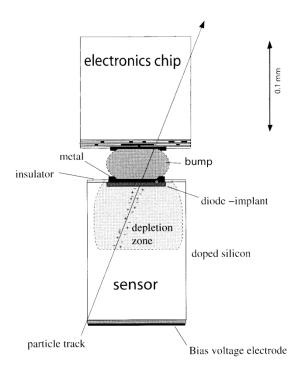

Pixel detectors have had a large development in the last decades thanks to the high granularity due to the small dimensions of the single sensing element. The hybrid pixel detector, whose structure is shown in Figure 1.2, is a largely used type of silicon detector. The surface of the detector is segmented into small squares and the electronics has the same geometry. For each pixel an electronic chain provides amplification and some other functions such as data storage. Sensor and electronics are fabricated separately and subsequently connected through the "bump bonding"

technique, which consists of a metal deposition between the sensor output and the electronics input [3].

Figure 1.2: Hybrid pixel detector

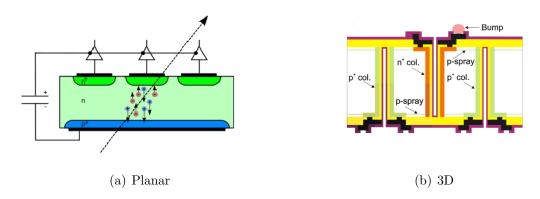

Two notable hybrid pixel detectors tipologies are planar silicon sensors and 3D silicon sensors, shown in 1.3. The former ones are, right now, the most largely used, while the latter ones have experienced a large development during these last years.

Figure 1.3: Planar silicon sensor vs 3D silicon sensor

The main difference between the two configurations is the electrodes arrangement. In the planar geometry, the electrodes are built on the top and bottom surfaces of the sensor. Otherwise, in the 3D geometry electrodes enter the sensor volume, perpendicularly to the surface [3].

#### 1.3 The CMS experiment

CMS (Compact Muon Solenoid) is one of the experiment located at the LHC (Large Hadron Collider) at CERN. LHC is designed to reach collisions at a very high energy (around 7 TeV in the center of mass). The main purpose of the CMS experiment is the discovery and the study of the Higgs boson. Aside from it the experiment deals also with other particle physics topics, such as heavy ions physics. The CMS experiment is composed of some different detectors such as muon chambers(MUON), hadronic calorimeters(HCAL and HF), electromagnetic calorimeter (ECAL) and tracking system. This choice is made because, in order to achieve a good global event reconstruction, it is necessary to match the information which comes from the different detectors. The transverse section of the detector is reported below [4].

# Magnetic Field AT Silicon ECAL Electromagnetic HCAL - Hadron Superconducting Iron return yoke interspersed

Transverse Slice of the Compact Muon Solenoid (CMS) Detector

Figure 1.4: CMS detector

Considering the purposes of this work, in the next section the attention is focused on the tracking detector.

#### 1.3.1 The CMS tracker

The CMS tracking system has been designed to provide precise measurements of the particle trajectories and reconstruction of the secondary vertices. The very special working conditions of the system played a key role in the choice of the detector layout. [5]

At the LHC design luminosity of  $10^{34}cm^{-2}s^{-1}$ , there are on average 1000 particles from more than 20 overlapping proton-proton interactions traversing the tracker per each bunch crossing (i.e. every 25ns). This situation leads to the requirement of a detector with high granularity and fast response in order to identify the trajectories and attribute them to the correct bunch crossing. Another issue is the severe radiation damage that the detector experiences due to the intense particle flux. The main challenge in the design of the tracking system was to develop detector components able to operate in this harsh environment for a long lifetime.

It is not so simple to achieve all these goals: these features also imply a high power density of the on-detector electronics, and therefore an efficient cooling system: the detector operating temperature, in fact, has to be below -10°C in order to minimize radiation damage. Nevertheless, this system has to be implemented with the smallest possible amount of material, in order to minimize multiple scattering, bremsstrahlung, photon conversion and nuclear interaction. In the detector design it is thus necessary to find a compromise with this respect.

These requirements on granularity, speed and radiation hardness lead to a tracker design entirely based on a silicon detector technology. The current CMS tracker is composed of a pixel detector with three barrel layers and a silicon strip tracker with 10 barrel detection layers. Each system is completed by endcaps which consist of 2 disks in the pixel detector and 3 plus 9 disks in the strip tracker on each side of the barrel, extending the acceptance of the tracker up to a pseudorapidity of  $|\eta| < 2.5$ . The system surrounds the interaction point with a diameter of 2.5m.

#### 1.3.2 Pixel detector

The pixel system is the part of the tracking system that is closest to the interaction region. It contributes precise tracking points in  $r - \phi$  and z and therefore is responsible for a small impact parameter resolution, essential for good secondary

vertex reconstruction.

#### Current pixel detector

The detector layout is shown in Figure 1.6. The sensors for the CMS pixel detector adopt the n-on-n concept. The pixels consist of high dose n-implants introduced into a high resistance n-substrate. Despite the higher costs due to the double sided processing this concept was chosen as the collection of electrons ensures a high signal charge at moderate bias voltages (< 600V) after high hadron fluences. Furthermore the double sided processing allows a guard ring scheme keeping all sensor edges at ground potential.

It is interesting to observe that, during data taking, more than 95% of the pixel channels are active [6] and, thanks to its high segmentation, this detector is used not only in the offline track reconstruction but also in the online tracking performed by the HLT (High Level Trigger). [7]

This detector was designed for a maximum luminosity of  $1 \times 10^{34} cm^{-2} s^{-1}$ , at which the electronics chip, the PSI46v2, has a dynamic inefficiency around 4% so it suffers an important data loss as the luminosity increases over this value.

Focusing on radiation hardness, at the specified luminosity the innermost pixel layer, which has a radius of 4.4 cm, experiences a particle fluence of  $3 \times 10^{14} n_{eq}/cm^2/yr$ , but all the pixels are designed to tolerate even a double radiation with respect to this one. However, with the increase of luminosity, also radiation hardness will become an issue.

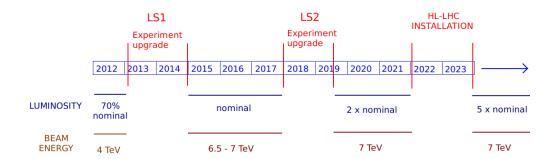

#### LHC development

In 2013 the first Long Shutdown (LS1) of LHC has begun. Its aim is to improve the machine performance, especially in terms of luminosity and beam energy. Now, the collider luminosity is  $7 \times 10^{33} cm^{-2} s^{-1}$  and the beam energy is around 3.5 TeV. In 2015, when the collider will resume operation, it will get the design luminosity  $(10^{34} cm^{-2} s^{-1})$  and the beam energy will increase up to around 6.5 TeV. This fact also requires an upgrade of the detector, because it will no be longer able to tolerate these conditions. To change this situation a new version of the pixel detector (phase 1 upgrade) will be introduced between 2016 and 2017.

LHC will be further upgraded and in 2022-2023 the HL-LHC (High Luminosity LHC) will be built. Its name comes from the fact that the luminosity of the machine will be increased up to  $5 \times 10^{34} cm^{-2} s^{-1}$  at least, while the beam energy will be around 7 TeV. The increased environment hostility will require a further detector upgrade (phase 2 upgrade).

Figure 1.5: LHC timeline

#### Pixel detector upgrade phase 1

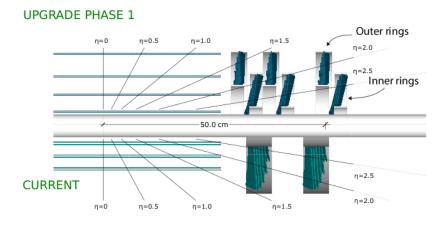

In order to have a detector which maintains or even improves its performance despite the issues which will play a key role in the next LHC runs, it becomes necessary to improve the detector design. In Figure 1.6 a comparison between the current pixel detector and the phase 1 detector is reported.

A first aspect which has to be taken into account is that the first detector layer has to be as close as possible to the beam. This requirement is achieved through the new LHC beam pipe, with a smaller radius. The new element will be introduced paying attention, on the other hand, not to worsen the operating conditions of the accelerator. For this reason a fourth pixel layer will be inserted in the detector.

Figure 1.6: Current pixel detector vs phase 1 pixel detector

Furthermore, comparing the simulation studies of the proposed Phase 1 upgrade

pixel detector operating at a luminosity of  $2 \times 10^{34} cm^{-2} s^{-1}$  with the present pixel detector, it is possible to see the key limitations of the current pixel detector that should be addressed by the upgrade:

- Data loss at high occupancy and trigger rate The purpose is to use a pixel readout chip (ROC) able to tolerate luminosities up to  $2 \times 10^{34} \ cm^{-2} s^{-1}$  and pile up to 50 [7] maintaining a high performance and a low fake rate. The current detector, instead, suffers from a significant data loss in these conditions, also due an insufficient readout speed.

- Material budget and radiation damage In the phase 1 upgrade a new design will be adopted with a different cooling system and electronics boards and connections located out of the interaction volume. The amount of material is, in fact, a major issue due to multiple scattering but not only: some particles can be lost in nuclear interactions. Also the radiation damage is expected to be diminished. In fact, although the nominal radiation damage will be approximately the same, the lower charge threshold for pixel hits mitigates the effects of the reduced collection charge.

#### Pixel detector upgrade phase 2

This upgrade will be performed around 2022-2023, when the LS3 will occur, giving rise to the High Luminosity (HL) LHC. This LHC upgrade results in higher machine performances with which the pixel system has to cope: a luminosity of  $5 \times 10^{34} cm^{-2} s^{-1}$ , a pile-up of 140 (in 25 ns) and an integrated luminosity of  $270 fb^{-1}$  per year [6].

The goals of the upgrade are:

- Higher radiation hardness of inner layers

- Increased granularity using smaller pixels

- Improved rate capability of the ROCs

- Contribution to level 1 trigger

- Lower power consumption

From the geometry point of view the choice will be very similar to the phase 1 geometry, with 4 pixel layers in the barrel, but with more disks in the outer part in order to improve the physics at high  $\eta$  values. The pixel size will be reduced in order to have an improvement in granularity and, consequently, in spatial resolution. The sensor choice has not yet been made. For the outer layers planar silicon sensors

will be definitely used, but for the inner ones there is the chance of using 3D silicon sensors, if their performances will be considered better than the planar ones.

Also the ROC optimization depends of several factors: the pixel size, hit rates, data buffering and readout, but also radiation hardness. It has in fact to tolerate around 300 MRad in 10 years. From the preliminary studies it has been understood that the new chip has to sustain particle rates up to  $2GHz/cm^2$ , taking into account the huge statistical fluctuations expected.

|               | PARAMETER or<br>FEATURE     | 1st generation LHC<br>phase 0 | 2nd generation LHC<br>Phase 1          | 3rd generation LHC<br>Phase 2          |

|---------------|-----------------------------|-------------------------------|----------------------------------------|----------------------------------------|

|               | Max Particle Flux           | ~50 MHz/cm <sup>2</sup>       | ~200 MHz/cm <sup>2</sup>               | ~500 MHz/cm <sup>2</sup>               |

| (             | Max Pixel Flux              | 200 MHz/cm <sup>2</sup>       | 600 MHz/cm <sup>2</sup>                | 2 GHz/cm <sup>2</sup>                  |

| ı             | Rad. Hardness               | 1.5 MGy                       | 3.5 MGy                                | 10 MGy                                 |

| ı             | Pixel Dimension             | 100x150 mm <sup>2</sup>       | 100x150 mm <sup>2</sup>                | 25x150 mm <sup>2</sup>                 |

| l             |                             | 50x400 mm <sup>2</sup>        | 50x250 mm <sup>2</sup>                 | 50x100 mm <sup>2</sup>                 |

|               | Signal Threshold            | 2500-3000 e <sup>-</sup>      | 1500-2000 e <sup>-</sup>               | ~1000 e <sup>-</sup>                   |

|               | L1 Trigger Latency          | 2-3 us                        | 4-6 us                                 | 6-20 us                                |

|               | L1 Trigger Rates            | 100 KHz                       | ~100 KHz                               | 200-1000 kHz                           |

|               | L1 Trigger<br>contribution  | no                            | no                                     | clustering info @L0<br>self-triggering |

|               | ASIC side                   | ~1 cm <sup>2</sup>            | ~4cm <sup>2</sup>                      | 1-4cm <sup>2</sup>                     |

|               | Hit memory per chip         | 0.1 Mb                        | 1 Mb                                   | ~16 Mb                                 |

|               | Chip output<br>bandwidth    | ~40 Mb/s                      | ~320 Mb/s                              | ~3 Gb/s                                |

|               | Power Budget                | ~0.3 W/cm <sup>2</sup>        | ~0.3 W/cm <sup>2</sup>                 | <0.4 W/cm <sup>2</sup>                 |

| $\overline{}$ |                             |                               |                                        |                                        |

|               | Electronics technology node | 250nm CMOS                    | 250nm CMOS (CMS)<br>130nm CMOS (ATLAS) | 65nm CMOS                              |

Figure 1.7: Detector specifications

Given these requirements a different choice has been made about the electronics technology: the 65nm CMOS will replace the 250nm CMOS. It will be done due to the advantages given by the 65nm in terms of:

- **High density** It gives the chance of building complex circuits is a small area, thanks to the smaller transistor dimensions available

- Radiation tolerance It has been already verified that 65nm technology transistors are able to tolerate up to 200 MRad of radiation, and there are ongoing tests also for higher values

- Speed and low power

- Long term availability It is a mature technology and thanks to the fact that it is used in many applications, it will have a long-term availability, which is

an important achievement given that the HL-LHC will operate for around 10 years starting in 2023.

#### Chapter 2

#### Deep submicron MOS

In this chapter a general review about the main features of the MOS transistor, the fundamental building block of all the circuits presented in this work, is given. After an introduction about silicon, the material the transistor is made of, the first part of the chapter is focused on the MOS transistor and its behavior, with a particular attention on the electrical characteristics. The second part, instead, is dedicated to the deep submicron CMOS technologies, with a focus on the fact that in these cases it is necessary to cope with new issues, the "short channel effects". Lastly, since the phase 2 pixel upgrade will use a 65nm CMOS technology in place of the 250nm, a comparison between these two technologies has been performed, in order to point out advantages and disadvantages of the different choice.

#### 2.1 NMOS and PMOS

Before starting with the description of the MOS transistor it is appropriate to enumerate the silicon properties which make advantageous the use of this material in the transistor fabrication.

#### 2.1.1 Silicon properties

Silicon is a tetravalent element, i.e. it has four electrons in the more external level. It is a semiconductor with a band gap energy of 1.12 eV at T = 300K.

Silicon is not the only semiconductor that can be chosen to fabricate transistors. Nevertheless it is the most used thanks to its particular features:

- The abundance of this element

- The easiness of growing high-purity silicon crystals

- The possibility of taking advantage of the electrical properties of silicon through the doping technique, i.e. introducing in the crystal lattice some atoms of other chemical elements

- Its thermical and mechanical properties: silicon devices can operate in a large interval of temperature, usually identified between -55°C and 125°C

- It allows the use of photo-lithographic techniques

#### 2.1.2 NMOS transistor

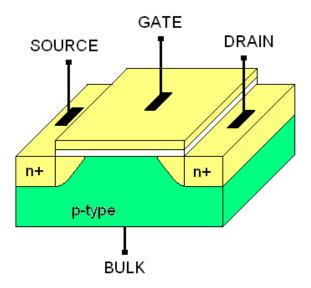

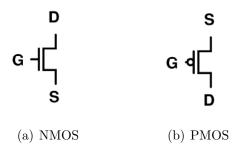

Figure 2.1: NMOS transistor

Figure 2.1 outlines the structure of a NMOS transistor. It consists of a p-doped region, which constitutes the bulk or substrate, on which two  $n^+-doped$  electrodes are implanted. It is important to underline that the distinction between the source and drain terminals indicated in the image is due to the potential applied to the electrodes, which otherwise are identical. As one can see, the electrodes and the substrate form two pn junctions which have to be reverse biased so that the transistor works correctly. The part between source and drain is instead called "channel region". Just over it there is a thin (typical values are in the range 2-7 nm, depending on the technology) layer of oxide  $(SiO_2)$  to separate the channel from the gate, which is the control electrode. The gate is in general made of polysilicon. However, due to the fact that it is grown on a oxide, it does not form a uniform crystal, but it is made of grains with different crystal orientation, hence the name "polysilicon"

or, in short, "poly".

Let's go now to analyze the main parameters which must be taken into account during the device fabrication. Besides the oxide thickness, fundamental quantities are the channel length (L), which is the distance between source and drain, and the channel width (W), the dimension orthogonal to the L. In reality, however, it happens that the two electrodes widen a bit in the channel region, each one by a value  $L_D$ , resulting in a decrease of the channel length: a relevant quantity is then the effective channel length given by:

$$L_{eff} = L - 2L_D \tag{2.1}$$

Nevertheless, bearing in mind these considerations, usually in literature  $L_{eff}$  is simply called channel length and is indicated with L. This parameter is however very important because usually it is the minimum channel length available which defines the technology used. As an example, in the case of sensors Front-End, the currently used technologies are between  $0.35\mu m$  and 65nm.

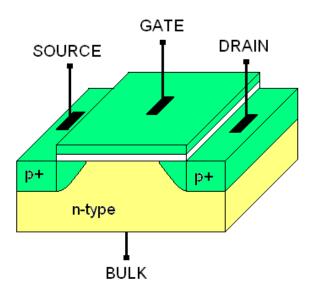

#### 2.1.3 PMOS transistor

In Figure 2.2, instead, it is possible to see the structure of a PMOS transistor.

Figure 2.2: PMOS transistor

At this point the explanation of the PMOS operation is quite simple, because it is completely mirrored with respect to the NMOS. It explaines why it is common to call these process CMOS, i.e. Complementary MOS. In fact, this device consists of a n-doped substrate on which p-doped electrodes are built. In order to have positive quantities in the equation which describe its behavior, source and drain are reversed with respect to the NMOS.

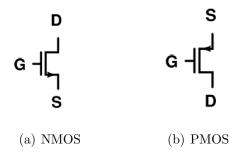

#### 2.1.4 MOS symbols

In the schematics reported in literature it is possible to find a lot of different representations of NMOS and PMOS transistors. In this paragraph only the most used are shown. For example they can be implemented with only three terminals: a very common depiction is the one reported below, in which NMOS and PMOS are distinguished thanks to the different arrow direction on their source terminal:

Figure 2.3: NMOS and PMOS with three terminals

Another frequently used representation is reported in 2.4. In this case the PMOS can be distinguished from the NMOS by the presence of a small circle next to the gate terminal:

Figure 2.4: NMOS and PMOS with three terminals (alternative representation)

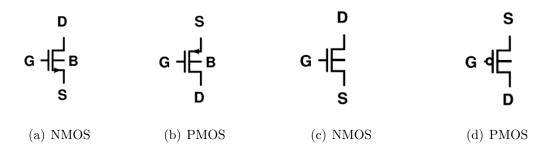

Of course both these representations can also take into account the presence of the bulk terminal, as shown in the following examples, resulting in a four-terminals symbol:

Figure 2.5: NMOS and PMOS with four terminals

#### 2.1.5 Success of CMOS technologies

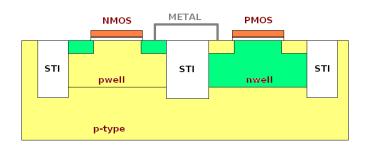

The main advantage of the CMOS processes is the possibility of building both the NMOS and the PMOS on the same substrate. It is usually preferred the usage of a p-type substrate. Firstly, it can be produced more easily than a n-type one. Furthermore, due to a lower mobility resulting in a higher resistivity, it allows the limitation of noise propagation through the substrate in complex IC (Integrated Circuits). At this point it is necessary to understand how to produce a PMOS transistor, assumed that the substrate is p-doped whilst for a PMOS a n-doped one is needed. The idea is to realize a counter-doping in selected areas of the wafer, called nwells. Nevertheless, even if the wafer substrate is p-doped, also in the NMOS fabrication a pwell is realized in order to have a more precise doping profile. In addition, in order to guarantee a full electrical insulation between one device and another, STIs (Shallow Trenched Insulations) are used. This technique results in the removal of the silicon in which devices are not foreseen, replacing it with oxide. Lastly, it is useful to underline that the interconnections between the different devices are realized with metal lines. Figure 2.6 shows a typical structure realized following the previous description.

#### 2.2 Electrical characteristics of CMOS transistors

It is now crucial to understand how NMOS and PMOS behave into an electronic circuit, considering their different operating regions. They basically depend on the bias voltages, i.e. the voltages applied to the device terminals. Keeping in mind that the PMOS behavior is mirrored with respect to the NMOS, the attention is

Figure 2.6: View of a CMOS process

focused on the latter.

#### 2.2.1 Threshold voltage

The first situation which is interesting to analyze is when source, drain and bulk are at zero and only the gate voltage is changed. It is possible to identify some different situations:

- Accumulation: it occurs when the gate voltage is negative and, accordingly, holes are attracted underneath the gate oxide.

- **Depletion**: in this case the gate voltage is just above zero. Holes are now removed from the channel, in which a layer of ionized acceptor atoms is formed, but they can not move.

- **Inversion**: the gate voltage is further increased, giving rise to the presence of electrons free to move in the channel between source and drain.

It is common to choose the source terminal as the voltage reference, so the gate voltage is indicated as  $V_{GS}$  and the drain voltage as  $V_{DS}$ . In first approximation, in classical models, it is possible to say that free electrons are present in the channel only when the condition  $V_{GS} - V_{TH} > 0$  is verified (strong inversion); nevertheless, especially in submicron CMOS technologies, the subthreshold region plays a key role in a lot of circuit implementations.

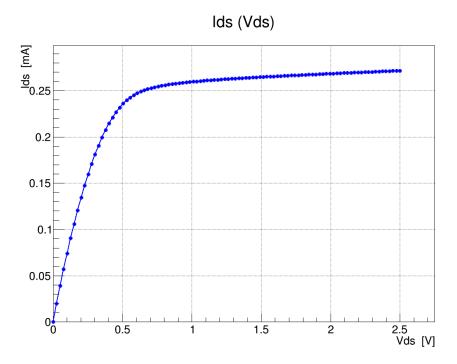

#### 2.2.2 I/V characteristics

Considering the inversion region, also the  $V_{DS}$  voltage has to be taken into account, giving rise, in turn, to two different regions, as shown in the  $I_{DS}$  vs  $V_{DS}$  curve in Figure 2.7

Figure 2.7:  $I_{DS}$  vs  $V_{DS}$

• Linear region If  $V_{DS}$  is very small (up to around two hundreds of mV) the electric field through the channel is constant, leading to a linear relationship between  $I_{DS}$  and  $V_{DS}$ :

$$I_{DS} = \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH}) V_{DS}$$

(2.2)

But if  $V_{DS}$  is raised only a little more the charge density in the channel can not be considered uniform, leading to a modified expression with respect to the 2.2:

$$I_{DS} = \mu_n C_{ox} \frac{W}{L} \left[ (V_{GS} - V_{TH}) V_{DS} - \frac{V_{DS}^2}{2} \right]$$

(2.3)

• Saturation region The Equation 2.3 shows that at a certain point a maximum is reached and, subsequently, according to the Equation 2.3 the current starts to fall. This is not a physical situation. In reality, in the points in which  $V_{DS} > V_{GS} - V_{TH}$  the channel is not anymore inverted: it is usual to say that the channel is "pinched-off", and it does not contribute to the current flow with its own carriers. The current expression then changes in the following way:

$$I_{DS} = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH})^2$$

(2.4)

The element which has to be underlined is that the current is independent from the  $V_{DS}$  voltage, so in the saturation region the transistor behaves as a voltage controlled current source.

However, it is more rigorous to underline that also in the saturation region a little dependence from  $V_{DS}$  remains due to the channel length modulation effect. The latter happens because, increasing  $V_{DS}$ , the pinch-off point moves towards the source, resulting in a decrease of the effective channel length. The current formula has therefore to be written as follows:

$$I_{DS} = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH})^2 (1 + \lambda V_{DS})$$

(2.5)

$\lambda$  is the channel length modulation parameter.

#### 2.2.3 Weak inversion operation

As technology has advanced, the behavior of the simple MOSFET has become more complicated, due to smaller geometries, higher electric fields and a continuing decrease in the power supply voltage. In this context the weak inversion, i.e. the current conduction in the subthreshold region,  $(V_{GS} - V_{TH} < 0)$ , has gained more and more importance. It is interesting to observe that, in weak inversion operation, the  $I_{DS}$  dependence from  $V_{GS}$  is an exponential one, very different from the strong inversion case:

$$I_{DS} = 2n\mu C_{ox} \frac{W}{L} \phi_T^2 e^{\frac{V_{GS} - V_{TH}}{n\phi_T}} \left( 1 - e^{-\frac{V_{DS}}{\phi_T}} \right)$$

(2.6)

#### Inversion coefficient (IC)

Having to discriminate between different regions of inversion, a more useful approach to the interpretation of the MOSFET behavior for analog design, based on the level of inversion (or Inversion Coefficient, IC), can be used. This method provides a convenient way of identifying the operating region and inversion level of MOS transistors, which can be used as a design variable for circuit optimization [8]. The definition of IC is the following:

$$IC = \frac{I_D}{2n\mu C_{OX}\left(\frac{W}{L}\right)\phi_T^2} \tag{2.7}$$

with:

$I_D$  drain current

n slope factor

$C_{OX}$  gate oxide capacitance

$\phi_T$  thermal voltage (=kT/q)

W effective channel width

L effective channel length

The different transistor operating modes are identified by the IC values:

- $IC > 10 \rightarrow$ Strong inversion i.e. if  $V_{GS} > V_{TH}$

- $0.1 < IC < 10 \rightarrow$  Moderate inversion i.e. if  $V_{GS} \simeq V_{TH}$

- $IC < 0.1 \rightarrow$  Weak inversion i.e. if  $V_{GS} << V_{TH}$

Moreover, also another quantity, called "inversion factor" and indicated with the symbol  $\gamma$ , is relevant. The mathematical expression is:

$$\gamma = \frac{1}{2} + \frac{1}{6} \frac{I_C}{I_C + 1} \tag{2.8}$$

It will be used in the following chapters in the noise calculations.

#### 2.2.4 Small signal parameters

The previous found characteristics are not linear, but in the circuits analysis it is very important to deal with linear quantities. Using Taylor series only at the first order approximation it is possible to write, for a function f, the following expression:

$$f(x) = f(x_0) + \left(\frac{\partial f}{\partial x}\right)_{x=x_0} (x - x_0)$$

(2.9)

If this function has a variation around  $x_0$ :

$$\Delta f = \left(\frac{\partial f}{\partial x}\right)_{x=x_0} \Delta x \tag{2.10}$$

The importance of this formula is that it provides a linear relationship between variations that happen at an equilibrium point. Let's now list the main small signal parameters used in the circuit analysis.

#### Gate transconductance

The gate transconductance is the derivative of the  $I_{DS}$  current with respect to the  $V_{GS}$  voltage. The name comes from the fact that these two quantities are measured in different terminals. Using the strong inversion expression of the current:

$$g_m = \frac{\partial I_{DS}}{\partial V_{GS}} = \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH})$$

(2.11)

From the previous relationship it is hence clear that  $g_m$  associates a variation of the  $I_{DS}$  current to a variation of the  $V_{GS}$  voltage.

#### Output conductance

Since the  $V_{DS}$  voltage plays a role in the current value due to the channel length modulation, it is useful to define a quantity which links a variation of the current to a variation of  $V_{DS}$ :

$$g_{ds} = \frac{\partial I_{DS}}{\partial V_{DS}} = \lambda \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH})^2 \simeq \lambda I_{DS}$$

(2.12)

The last equality is approximated because in the  $I_{DS}$  also the channel length modulation would have been taken into account. It is important to underline that the reciprocal of  $g_{ds}$  is the output resistance,  $r_0$ :

$$r_0 \simeq \frac{1}{\lambda I_{DS}} \tag{2.13}$$

Lastly, it is necessary to stress that the output conductance plays a key role in the definition of the gain.

#### 2.2.5 The $g_m/I_D$ method

The  $g_m/I_D$  method is largely used in Integrated Circuit design. It considers the relationship between the ratio of the transconductance  $g_m$  over DC drain current  $I_D$  and the inversion coefficient as a fundamental design tool. Three main reasons lead to the choice of  $g_m/I_D$ : [9]

- It is strongly related to the performances of analog circuits

- It gives an indication of the device operating region

- It provides a tool for calculating the transistor dimensions

Considering a constant current value, the greater is the ratio  $g_m/I_D$  the greater is the transconductance value, so in other words it is possible to say that this ratio is a measure of the efficiency of translating current into transconductance.

Another important property of the  $g_m/I_D$  is that it is related to the transistor operating mode as we can see from the following formula:

$$\frac{g_m}{I_D} = \frac{1}{I_D} \frac{\partial I_D}{\partial V_G} = \frac{\partial (lnI_D)}{\partial V_G} = \frac{\partial \left\{ ln \left[ \frac{I_D}{\left( \frac{W}{L} \right)} \right] \right\}}{\partial V_G}$$

(2.14)

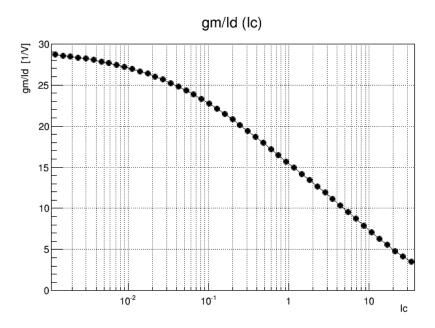

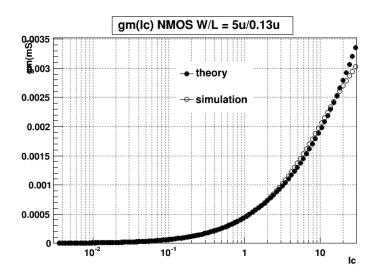

The derivative is maximum in the weak inversion region where the  $I_D$  dependence versus  $V_G$  is exponential while it is quadratic in strong inversion, becoming almost linear deeply in strong inversion. In Figure 2.8 it is shown that the  $g_m/I_D$  ratio decreases as the operating point moves toward strong inversion when  $I_D$  or  $V_G$  are increased.

Figure 2.8:  $g_m/I_d$  for a NMOS transistor

#### 2.3 Deep submicron CMOS technologies

In the last decades the number of transistors in electronics devices is tremendously grown, thanks to the transistor scaling which leads to the production of

smaller and smaller transistors. This element, together with the zero static power dissipation of CMOS logic, underlies the dominance of CMOS technologies [10]. But the scaling process is not so simple, because a lot of effects emerge when the channel length is approximately below  $3\mu m$ , affecting the transistor behavior: they are called "short channel effects". First of all, however, it is necessary to explain the scaling theory, i.e. how the transistor modifies its behavior with scaling.

#### 2.3.1 Scaling theory

The ideal transistor scaling is marked by three principles [10]:

- Reduction of all the lateral and vertical dimensions by a factor  $\alpha$

- Reduction of the threshold and supply voltages by  $\alpha$

- Increase of all the doping levels by  $\alpha$

It is then important to underline that, due to the contemporary scaling of dimensions and voltages, all the electric fields in the transistor remain approximately constant. The scaling of these quantities obviously results in a change of the  $I_{DS}$  current equations. In strong inversion:

$$I_{DS,scaled} = \frac{1}{2}\mu\alpha C_{ox} \frac{W}{L} \left(\frac{V_{GS}}{\alpha} - \frac{V_{TH}}{\alpha}\right)^2 = \frac{I_{DS}}{\alpha}$$

(2.15)

Other interesting aspects are the behaviors of the transconductance and the channel capacitance, always in strong inversion:

$$g_{m,scaled} = \alpha \mu C_{ox} \frac{W}{L} \frac{(V_{GS} - V_{TH})}{\alpha} = g_m$$

(2.16)

$$C_{ch,scaled} = \frac{W}{\alpha} \frac{L}{\alpha} (\alpha C_{ox}) = \frac{1}{\alpha} W L C_{ox}$$

(2.17)

The transconductance does not scale because the decrease of the overdrive voltage is compensated by the increase in the density of the gate capacitance. The total channel capacitance, instead, decreases with scaling: this is a remarkable advantage, because it leads to an increase in speed and in a reduction of power dissipation.

#### 2.3.2 Short-channel effects

The short-channel effects mainly happen due to [1]:

• Increase of the electric fields caused by a non-proportional power supply voltage scaling.

- The built-in potential is neither scalable nor negligible.

- Complexity in reducing the depth of Source-Drain junction.

- Decrease of the mobility due to the increase of the substrate doping.

It is then important to make a list of the main short-channel effects, since they have a great influence on the simulation of circuits developed with deep submicron CMOS technologies.

#### Threshold voltage variation

In scaled transistors the  $V_{TH}$  value is strongly affected by the channel length. In fact, the depletion regions associated to source and drain tend to extend a bit into the channel area, so the immobile charge imaged by charge on the gate is reduced, resulting in a lowering of the threshold voltage. It means that the threshold voltage increases with L. If L is very little, however, the widening of the depletion regions is so relevant that they can come in proximity with each other, filling almost all the channel. To fix this situation a non uniform doping implant, called "Halo implant", is performed near the depletion region. The halo implant, however, gives rise to the "Reverse Short Channel Effect (RSCE)": the threshold voltage is high when L is small, then increasing L the threshold voltage diminishes.

#### Mobility reduction

If the  $V_{GS}$  voltage is large, the constant-field configuration described before can not be applied. In fact, the high electric field between gate and channel results in a constriction of the region under the oxide in which carriers can move, leading to an increment of multiple scattering which reduces the mobility. This effect can be represented using an empirical equation:

$$\mu_{eff} = \frac{\mu_0}{1 + \theta(V_{GS} - V_{TH})} \tag{2.18}$$

$\mu_0$  denotes the mobility value when the degradation is not present. Since the mobility expression is changed, also the current expression is modified:

$$I_{DS} = \frac{1}{2} \frac{\mu_0 C_{ox}}{1 + \theta (V_{GS} - V_{TH})} \frac{W}{L} (V_{GS} - V_{TH})^2$$

(2.19)

#### Velocity saturation

It is necessary to underline that the mobility has also a dependence on the lateral electric fields in the channel, dropping for fields higher than  $1V/\mu m$ . The carrier

velocity is

$$v = \mu E \tag{2.20}$$

so it tends to saturates at around  $10^7 cm/s$ , leading to a  $I_{DS}$  saturation before the pinch-off point. The expression of the current is modified:

$$I_{DS} = WC_{ox}v_{sat}\frac{(V_{GS} - V_{TH})^2}{V_{GS} - V_{TH} + 2\frac{v_{sat}L}{\mu_{eff}}}$$

(2.21)

It is however useful to stress that if  $V_{sat}$  or L are large, the Equation 2.21 reduces to the well known square-law relationship, pointing out that this effect is relevant only with small channel lengths.

#### Gate leakage current

In deep submicron technologies also the oxide thickness is scaled-down becoming very thin. Some electrons are hence allowed to tunnel through the oxide, giving rise to a small current. In some cases, especially when the oxide thickness is below 1.5 nm (luckily it happens for 45nm or below CMOS technologies), this current can significantly rise, compromising the insulation between the gate and the channel. Also in 65nm technologies it is however important to carefully control the leakage current values, especially if many transistors are put in parallel.

#### Hot carrier effects

High  $V_{DS}$  voltage values result in large lateral electric fields. As a consequence, despite the saturation of the charge average velocity, the instantaneous velocity increases, and then also the kinetic energy, giving rise to the so called "Hot carriers". Near the drain these carriers can hit silicon atoms at high speeds producing impact ionization. In other words, it gives rise to an additional number of electrons and holes and, hence, to a drain-substrate current. In fact, electrons are absorbed by the drain and holes by the substrate. This issue has to be taken into account as it affects the output conductance behavior.

#### Output impedance variation with $V_{DS}$

Until now the assumption of a constant output impedance  $r_0$  in the saturation region has been made. In reality, however, this is not the real situation because  $r_0$  increases with  $V_{DS}$ . In fact, an increment of the  $V_{DS}$  corresponds to a shift of the pinch-off point towards the source, resulting in a reduction of the rate with which the depletion region around the source becomes wider. Furthermore, as explained in the previous paragraph, also hot carriers play a role in the output conductance

determination.

The real consequences of all these effects can be however better understood through examples. Therefore, in the next section, a comparison between two different submicron technologies is performed, in order to highlight how the short channel effects influence the transistor behavior.

#### 2.4 65 nm vs 250 nm

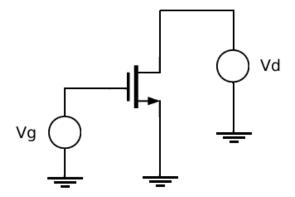

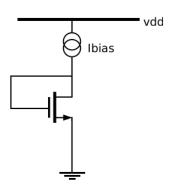

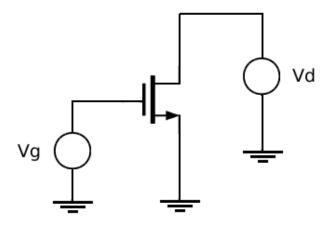

The comparison has been carried out between the 250nm CMOS technology and the 65nm CMOS technology, because the current CMS pixel detector uses a Front-End architecture based on the former, while the phase 2 upgrade detector will use the latter. Before starting, it has to be underlined that the supply voltage decreases from 2.5 V in the 250nm to 1.2 V in the 65nm. The analysis has been performed, in both cases, simply using a NMOS transistor biased as shown in Figure 2.9.

Figure 2.9: Simulation test bench

#### Threshold voltage

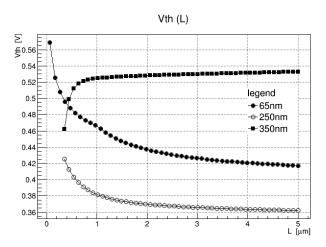

In Figure 2.10 also the 350nm technology slope has been reported, in order to better understand the effects due to halo implants.

In the 350nm technology halo doping is absent. Accordingly,  $V_{TH}$  increases with the channel length while in both 65nm and 250nm technologies halo doping is used, resulting in a decrease of the  $V_{TH}$  with the channel length. It is furthermore interesting to notice that in the 65nm technology, unless the slope has the same behavior with respect to the 250nm, the threshold value is a little higher, due to the different production processes.

Figure 2.10:  $V_{TH}(L)$  for different technologies

#### Output conductance and intrinsic gain

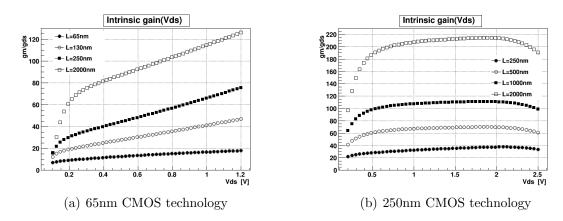

In all amplifiers the most important parameter is the gain. Then it is very useful to evaluate the intrinsic gain, i.e. the maximum gain achievable with a single transistor. In formula it can be expressed as follows:

$$A_0 = \frac{g_m}{g_{ds}} \tag{2.22}$$

Subsequently, the first thing to do is the analysis of the  $g_m$  and  $g_{ds}$  behavior separately.

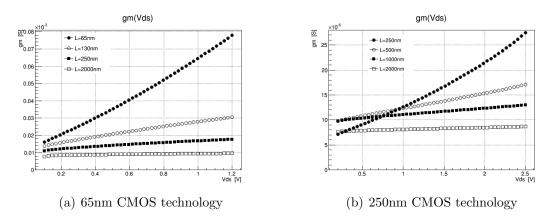

• Transconductance Focusing on the  $g_m$  behavior, shown in Figure 2.11, it is possible to see that at  $L_{min}$  the trend is quite different from the others in both technologies.

Furthermore,  $g_m$  looks like to have a linear dependence on the  $V_{DS}$  value due to the channel length modulation effect. Choosing  $L = 2\mu m$  in both the technologies it is possible to see that the trend is very similar. As a consequence, it is possible to say that there is not a big difference between the two technologies in terms of transconductance.

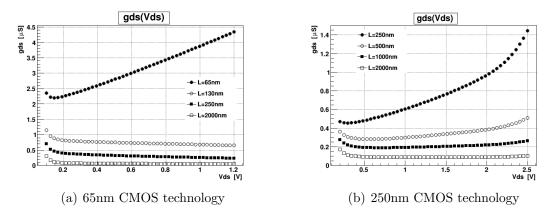

• Output conductance Let's go now to talk about  $g_{ds}$ . It is a key parameter because it is the reciprocal of the output resistance. A useful way to get some information about this parameter is to plot  $g_{ds}$  vs  $V_{DS}$  for different channel length values in both the technologies, as shown in Figure 2.12.

Firstly, it has to be stressed that the  $L_{min}$  is not the right choice neither in 65nm nor in 250nm. In fact, the  $g_{ds}$  value is significantly higher, resulting,

Figure 2.11:  $g_m(V_{DS})$  for different technologies

Figure 2.12:  $g_{ds}(V_{DS})$  for different technologies

as a consequence, in a smaller output resistance value. Furthermore, it is possible to see that the trend is different for high  $V_{DS}$  values, in fact in the 250nm technology the output conductance value rises, effect which does not occur in the 65nm. It is due to the impact ionization effect, which is probably better controlled in the 65nm technology. Finally, choosing the same L value  $(L=2\mu m)$  in both the technologies, it can be seen that the output conductance values is nearly the same in the two cases.

• Intrinsic gain Referring now to the intrinsic gain, the same kind of comparison has been performed.

This comparison shows that the choice of small channel length values leads to little gain values. However, it is also clear that in the 65nm technology

Figure 2.13: Intrinsic gain for different technologies

the intrinsic gain is reduced compared to the 250nm case. In fact, choosing  $L = 2\mu m$ , the intrinsic gain is halved in the 65nm technology.

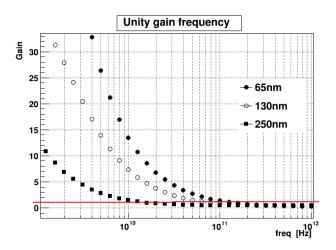

## Unity gain frequency

The unity gain frequency  $(f_T)$  is the frequency at which the transistor gain is 1. Accordingly it indicates the bandwidth of the single transistor. In order to find the  $f_T$  value, a plot of gain vs frequency has been realized, also using a 130nm technology to better explain the situation.

Figure 2.14: Gain(f) for different technologies

Figure 2.14 shows that the unity gain value, represented by the red line, is reached at progressively higher frequencies as the technology node decreases. In the 65nm

technology the unity gain value corresponds to a frequency of about 100 GHz, an order of magnitude higher than in the 250nm case, in other words the bandwidth is larger in 65nm.

# 2.4.1 Summary

Putting things together, this comparison shows that the fundamental transistor parameters are not very different in the two technologies. The main difference which comes out is that with the decreasing of the technology node there is a progressive reduction of the intrinsic gain but, on the other hand, a widening of the bandwidth. The main advantages in using the 65nm is however that, as mentioned in Chapter 1, circuits occupy a smaller area and the overall power consumption is reduced, in particular in the digital part.

# Chapter 3

# Front-End amplifiers

In this chapter an overview of a typical electronics Front-End for silicon detectors will be given. In the second part the attention will be focused on noise in electronics systems. In this section the main noise contributions will be calculated, since their mathematical expressions are very important to understand the noise optimization procedure which will be described in the following chapter.

# 3.1 Front-End amplifier

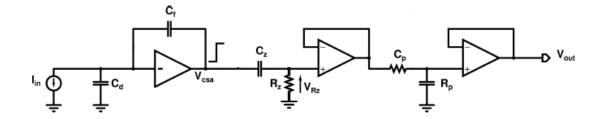

In Figure 3.1 an overview of a Front-End amplifier is shown.

Figure 3.1: Front-End amplifier

The first stage, which directly receives the signal rising from the sensor, is the Charge Sensitive Amplifier (CSA). It is followed by a shaper, whose purpose is a further signal processing. Let's now analyze more in detail the behavior of the single stages.

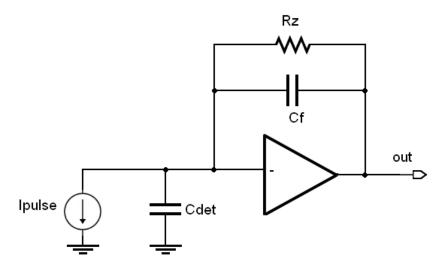

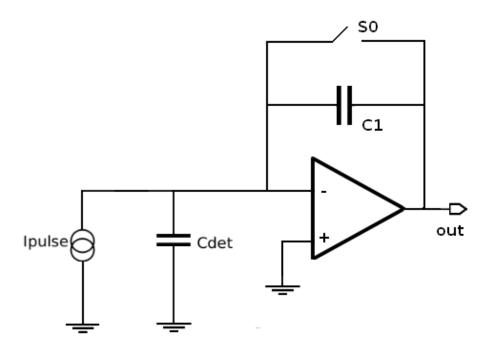

Figure 3.2: Scheme of a Charge Sensitive Amplifier

## 3.1.1 Charge Sensitive Amplifier

The Charge Sensitive Amplifier (CSA), shown in Figure 3.2, is the first element of the chain. The core component of the CSA is a high-gain amplifier with a feedback network implemented with a capacitor  $C_f$ . The resistor  $R_f$  is then added in order to provide a steady DC input level, as it is required by high-gain amplifiers. However, the resistor value is so high (about tens of  $G\Omega$ ) that it does not affect signal processing.

The following assumptions are useful to understand the behavior of an ideal CSA:

- The input signal is a  $\delta$ -like pulse

- The core amplifier has infinite gain and infinite bandwidth

If these requirements are accomplished the CSA can be described as an ideal integrator, so:

$$V_{out} = \frac{1}{C_f} \int dt \ I_{in}(t) \tag{3.1}$$

With a  $\delta$ -like input,  $(I_{in}(t) = Q_{in} \delta(t))$  the previous relationship becomes:

$$V_{out} = \frac{Q_{in}}{C_f} u(t) \tag{3.2}$$

In the frequency domain, using the Laplace transform of u(t) which is  $\frac{1}{s}$ , the output signal can be rewritten:

$$V_{out} = \frac{Q_{in}}{C_f} \frac{1}{s} \tag{3.3}$$

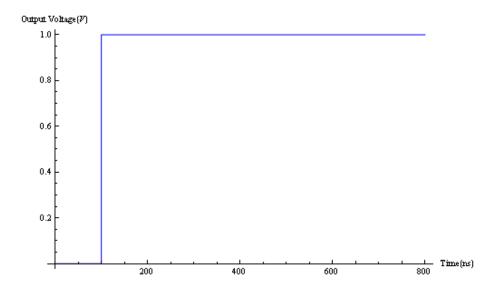

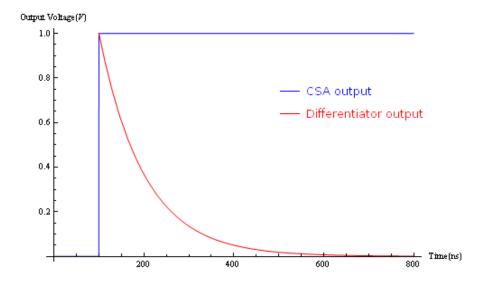

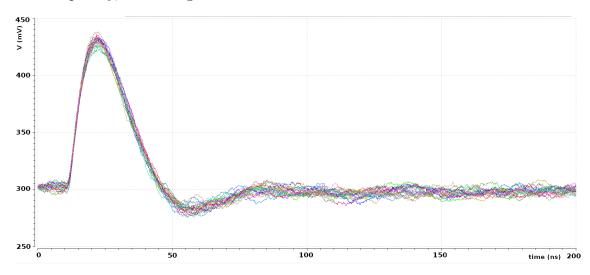

In Figure 3.3 it is possible to see the output signal of an ideal CSA. When the input signal arrives, the CSA output reaches immediately its maximum. However, in real amplifiers, the rise time of the output signal is not negligible, and it is usually around some ns.

Figure 3.3: Output signal of an ideal CSA

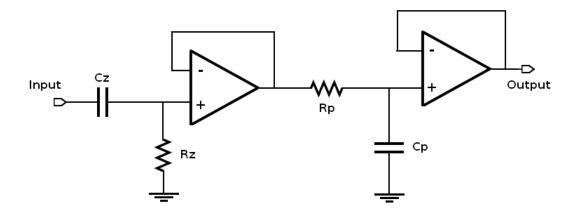

# 3.1.2 CR-RC shaper

The CSA output signal has to be furthermore elaborated in order to facilitate the signal analysis performed in the successive electronics chain. This purpose is accomplished by the shaper stage. It can be implemented in many ways, but it is substantially composed of a series of differentiators and integrators. In Figure 3.4 a typical choice, the CR-RC shaper, is shown. It is a sequence of a high-pass filter, which is a differentiator, and a low-pass filter, which is an integrator and it is an appropriate choice to understand how the shapers behave.

In order to analyze the behavior of the stage, it is useful to write the transfer functions of the differentiator and the integrator in the frequency domain. The

Figure 3.4: Scheme of a CR-RC shaper

high-pass filter transfer function is:

$$T(s) = \frac{sRC}{1 + sRC} \tag{3.4}$$

while the low-pass filter one is:

$$T(s) = \frac{1}{1 + sRC} \tag{3.5}$$

In order to understand step-by-step how the chain of CSA and shaper operates, it is firstly appropriate to consider the sequence of CSA and high-pass filter. It is now useful to write the output signal in the frequence domain using the Laplace transforms.

$$V_{R_z} = \frac{Q_{in}}{sC_f} \frac{sC_z R_z}{1 + sC_z R_z} = \frac{Q_{in}}{C_f} \frac{\tau_z}{1 + s\tau_z}$$

(3.6)

This expression shows that the pole introduced by the CSA is cancelled by the zero introduced by the high-pass filter. However, the expression in the time domain is convenient to understand the signal form shown in Figure 3.5, which shows that the output of the differentiator decreases with an exponential law with time constant  $\tau_z$ .

$$V_{out,R_z} = \frac{Q_{in}}{C_f} e^{-\frac{t}{\tau_z}} \tag{3.7}$$

The purpose of the differentiator is thus to give rise to a signal which goes back to the baseline. It is now appropriate to underline that a very important information to be measured is the peak height, because it is proportional to the charge released

Figure 3.5: Output signal of the differentiator stage

in the sensor by the particles. But in this configuration the signal fall is very quick, requiring a circuit which makes a very precise measurement. For this reason it is convenient to diminish the variations around the maximum. This purpose is reached elaborating the signal in the integrator. The output signal of the full chain, calling  $\tau_p$  the time constant of the integrator, is then given by the following relationship:

$$V_{out}(t) = \frac{Q_{in}}{C_f} \frac{\tau_z}{\tau_z - \tau_p} (e^{-\frac{t}{\tau_z}} - e^{-\frac{t}{\tau_p}})$$

(3.8)

This expression is correct if the gain of differentiator and integrator is the same. If  $\tau_z = \tau_p$  the previous expression is simplified:

$$V_{out}(t) = \frac{Q_{in}}{C_f} \left(\frac{t}{\tau}\right) e^{-\frac{t}{\tau}} \tag{3.9}$$

This particular case is very convenient. The return to the baseline is in fact dominated by the smaller time constant, so for example if the integration time constant is significantly greater than the other one, the integration of the signal will be very little. A good compromise between these different configurations is then the choice of equal time constants, usually made in CR-RC shaper.

Having made the time constants choice, it becomes interesting to determine the value of the peaking time, i.e. the time taken by the signal to reach its maximum. It can be obtained equalling to zero the first derivative of the output signal:

$$\frac{dV_{out}}{dt} = \frac{1}{\tau}e^{-\frac{t}{\tau}} - \frac{t}{\tau^2}e^{-\frac{t}{\tau}} = 0 \tag{3.10}$$

then

$$T_P = \tau \tag{3.11}$$

The maximum value of the signal at the shaper output is instead:

$$V_{out,max} = \frac{Q_{in}}{C_f} \frac{1}{e} \tag{3.12}$$

At the shaper output, therefore, there is a loss in the gain, which can be compensated by an increase of the gain of the following stages.

Until now an ideal Front-End description has been carried out, but obviously, it has to be implemented with real components: as a consequence in the circuit design it is necessary to take into account the intrinsic noise contribution which rise from the electronics chain. For this reason, the next part of the chapter is focused on this issue and on the calculation of the main contributions.

# 3.2 Noise in electronics systems

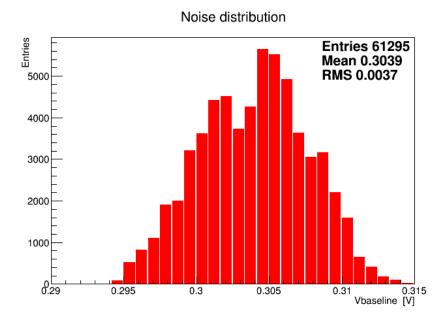

The noise analysis is a key element in the circuit design. In fact, especially in analog circuits for the readout of radiation sensors, the noise evaluation plays a key role, because it is crucial to have the best possible Signal-to-Noise Ratio (SNR). In other words, it is desirable to have the smaller possible influence of the noise on the signal form. Noise is a random process caused by the fluctuations of currents and voltages generated into the device [11]. As a consequence, it is not possible to predict the instantaneous noise value in the time domain, so the noise analysis is performed observing the noise for a long time developing a statistical model. It means that the predictable noise properties are average values. [1]. To each noise source is associated a power spectral density  $S_n^2$ , which indicates how much noise power is present at a given frequency. Furthermore, it is usual to call "white noise sources" the noise signals with a flat power spectral density, i.e. independent from the frequency.

Moreover, the electric charge is not a continuous quantity: the unity is the electron charge. For this reason, the noise is usually expressed in ENC(Equivalent Noise Charge), i.e. the number of electrons which must be collected in order to have a signal equivalent to the noise one.

In general, in the simulations the noise effects are measured at the output and then properly referred to the input. The power spectral density can be used to obtain the value of the square rms of the output noise generated by the input source by multiplying it for the square of the noise source transfer function and then integrating on the frequency spectrum:

$$V_{n,out}^2 = \int_0^\infty df \ S_n^2 |T_n(j2\pi f)|^2 \tag{3.13}$$

The total output noise, considering uncorrelated sources, is then given by:

$$V_{n,out\ rms} = \sqrt{V_{n,out1}^2 + V_{n,out2}^2 + \dots + V_{n,outn}^2}$$

(3.14)

The ENC of a single noise source is then given by:

$$ENC = \frac{1}{q_e} \frac{1}{A_0} V_{n,outn} \tag{3.15}$$

The total ENC instead is:

$$ENC_{tot} = \sqrt{ENC_1^2 + ENC_2^2 + \dots + ENC_n^2} = \frac{1}{q_e} \frac{1}{A_0} V_{n,out\ rms}$$

(3.16)

$q_e$  Electron charge expressed in Coulomb

$A_0$  Gain of the stage

# 3.2.1 Types of noise

The principal noise sources are the thermal and the flicker noise [12].

- The thermal noise is caused by the thermal excitation of charge carriers in a semiconductor. It has a white spectral density and is proportional to the absolute temperature.

- The flicker noise is present only with DC currents and originates from the traps in the semiconductor that hold the carriers which constitute the DC flow for some time before releasing them. It is often called "1/f noise" because its spectral density can be represented as a  $1/f^{\alpha}$  function, (0.8 <  $\alpha$  < 1.3), in which f is the frequency.

# 3.2.2 Noise in CMOS technologies

Also in MOS transistors the main noise sources are the thermal and the flicker noise. The MOS channel has a resistive behavior, consequently the contribution of thermal noise, as for resistors, is relevant. Flicker noise is instead due to the fact that in MOS transistor the current conduction is near to the surface, which behaves as traps, capturing and releasing charges. These statements have to be taken into account in the representation of the noise sources due to MOS transistors.

# 3.2.3 Noise in Front-End amplifiers

However, it is important to understand how to represent these noise sources in Front-End amplifiers. The most used method is the representation of the main noise contributions in terms of current of voltage sources. The distinction between these two cases is performed in the following way:

- **Series noise**: noise contribution represented by a voltage source put in series with the amplifier input

- Parallel noise: noise contribution represented by a current source placed in parallel with the amplifier input

Now a list of the main noise sources is given.

#### Series noise sources

• White noise due to resistors connected in series with the input:

$$V_{nR_s}^2 = 4kTR_s \tag{3.17}$$

in which k is the Boltzmann constant and T is the absolute temperature.

• White noise due to the input transistor:

$$V_{nw1}^2 = 4kT\gamma \frac{1}{g_{m1}} \tag{3.18}$$

in which  $g_{m1}$  is the transconductance of the input transistor and  $\gamma$  is the inversion factor introduced in 2.2.4

• White noise due to the current source:

$$V_{nw2}^2 = 4kT\gamma \frac{g_{m2}}{g_{m1}^2} \tag{3.19}$$

in which  $g_{m1}$  and  $g_{m2}$  are the transconductances of the two transistor which form the current mirror, i.e. the implementation of the current source at the transistor level.

• Flicker noise intrinsically generated by the amplifier

$$V_{n1/f}^2 = \frac{K_f}{C_{ox}WL} \frac{1}{f} \tag{3.20}$$

where  $K_f$  is a constant value once the gate length is fixed.

#### Parallel noise sources

All the following parallel noise sources have white spectral density. Some of them are internal to the Front-End amplifier:

• Noise due to current sources directly connected to the input

$$I_{ns}^2 = 4kT\gamma g_m \tag{3.21}$$

• Noise generated by the feedback resistor of the CSA:

$$I_{n,R}^2 = \frac{4kT}{R_f} {(3.22)}$$

This relationship shows that it is advantageous to have a large feedback resistor.

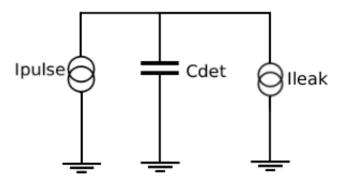

There is also another noise source, which does not depend on the electronics, but which has a great influence on the Front-End system. It is generated by the detector leakage current, which increases with the radiation damage. It is a parallel noise source:

$$I_{n,leak}^2 = 2qI_{leak} (3.23)$$

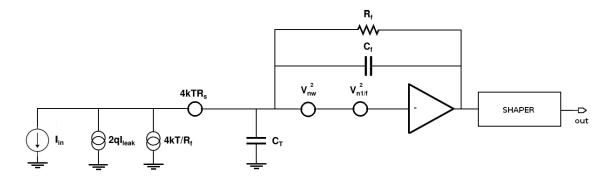

Figure 3.6 shows how noise contributions are represented in a typical Front-End amplifier.

Figure 3.6: Noise sources

# 3.3 Noise calculations

At this point it is necessary to calculate the total ENC generated by the Front-End amplifier, following the method indicated by the equation 3.16. These calculations can be performed either in the time domain or in the frequency domain. In this case the former is chosen , because it is particularly suitable in white parallel and white series noise calculations. Only the former will be presented in a complete way because the other case is very similar.

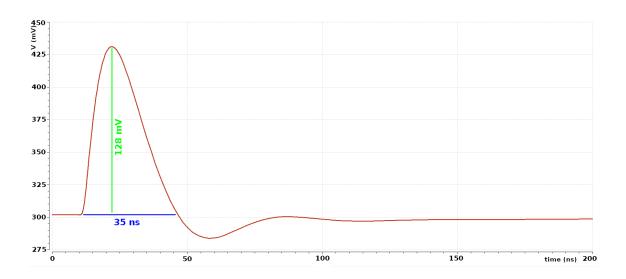

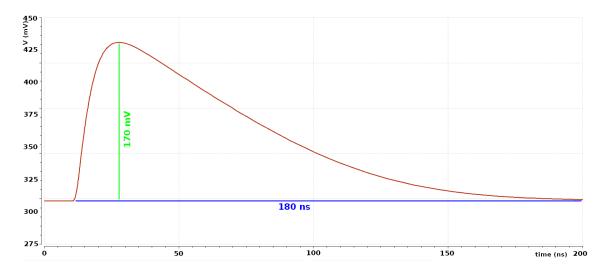

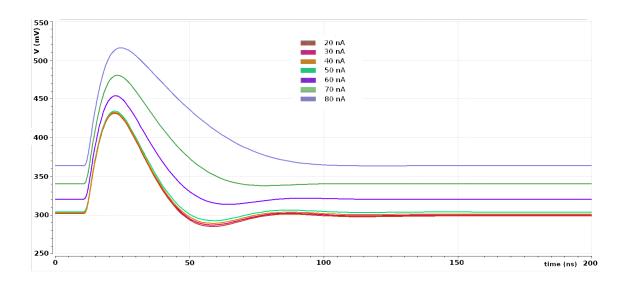

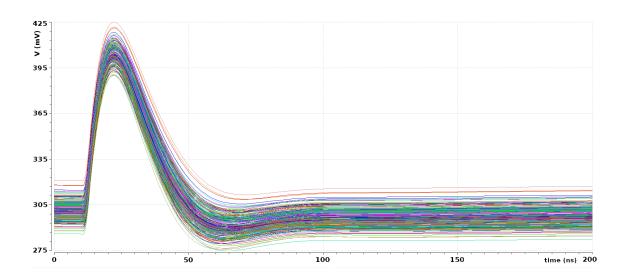

#### 3.3.1 Parallel noise calculation