Università degli Studi di Torino Dipartimento di Fisica Sperimentale

### Scuola di Dottorato in Scienza ed Alta Tecnologia

Indirizzo di Fisica ed Astrofisica XIV ciclo

# Integrated Front-End Electronics for High Precision Timing Measurements with Radiation Detectors

Ph.D. Student: Sara Garbolino

Supervisor: Dr. Angelo Rivetti

Coordinator: Prof. Guido Boffetta

Anni accademici 2009-2010-2011 Settore Scientifico Disciplinare FIS/01

Alla mia famiglia.

## Acknowledgements

Un ringraziamento particolare va al mio supervisore Angelo Rivetti per i suoi preziosi insegnamenti e consigli. Ringrazio il gruppo di NA62, in particolare Gianni Mazza, Flavio Marchetto, Giulio Dellacasa e Richard Wheadon. Grazie anche ai miei colleghi e amici Thanu, Alberto e Manuel (Pedro) per il piacevole tempo passato insieme. Grazie a tutti coloro che hanno camminato al mio fianco finora. Anche se le nostre strade si sono incrociate solo per poco l'impronta di tutti voi resterà sempre impressa di fianco alla mia. Grazie a chi ho perso per strada, per voi ci sarà sempre un angolo nei miei pensieri. Grazie anche ai nuovi arrivati, al gruppo del fiume e della montagna, per tutto ciò che mi avete insegnato, per i bei momenti e per la passione che mi avete trasmesso. Ma soprattutto grazie a voi che ancora camminate con me e che mi sostenete e supportate ogni giorno, che credete in me e che semplicemente riempite la mia vita di felicità. Grazie perché senza di voi tutto questo non avrebbe senso. Grazie a mamma, a papà e a Dani, grazie a Valentina, a Marta, a Frank, a Matteo, a Carmen, a Denise e a tutti gli altri. E grazie a Davide, ora che ti ho trovato spero di poterti accompagnare a lungo.

## Contents

|   | Ack                                      | nowlee                                                             | dgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | iii                                                                                                  |  |

|---|------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|

|   | $\operatorname{List}$                    | of Fig                                                             | gures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | xi                                                                                                   |  |

|   | List of Tables                           |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                      |  |

|   | Intr                                     | oducti                                                             | on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                    |  |

| 1 | Pree<br>puls<br>1.1<br>1.2<br>1.3<br>1.4 | es<br>Princi<br>1.1.1<br>1.1.2<br>1.1.3<br>1.1.4<br>Optim<br>Optim | traction of timing information from nuclear radiation         ples of time pick-off         Leading edge timing         Constant fraction discrimination         Amplitude correction         1.1.3.1         Waveform digitization         1.1.3.2         Time over threshold         Crossover timing         um filtering for energy measurements         um filtering for timing         sate timing with semiconductor detectors         Signal characteristics in semiconductor detectors         The preamplifier | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                 |  |

|   |                                          | 1.4.4                                                              | Monolithic CFD implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 34                                                                                                 |  |

| 2 | <b>The</b> 2.1<br>2.2                    | Expert<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>2.1.5                | 2 experiment         imental approach         Detector layout         Tracking stations         Timing requirements         Veto system         Particle identification         TK detector         Detector requirements and architecture         The silicon sensor                                                                                                                                                                                                                                                     | $\begin{array}{rrrr} . & 44 \\ . & 46 \\ . & 47 \\ . & 47 \\ . & 48 \\ . & 48 \\ . & 48 \end{array}$ |  |

| 3 | <b>Fro</b><br>3.1                        |                                                                    | architectures for NA62 GTK<br>walk compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>52</b><br>. 52                                                                                    |  |

|             | 3.2                                                                                                                                          | Time to digita                                                                                                                                                                                                          | al conversion                                                                                                                                                 | . 53                                                                                                                                                                                     |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | 3.3                                                                                                                                          | Two complem                                                                                                                                                                                                             | entary architectures                                                                                                                                          | . 54                                                                                                                                                                                     |

|             |                                                                                                                                              | 3.3.1 The P                                                                                                                                                                                                             | TDC architecture                                                                                                                                              | . 58                                                                                                                                                                                     |

|             |                                                                                                                                              | 3.3.1.1                                                                                                                                                                                                                 | The P-TDC pixel cell                                                                                                                                          | . 58                                                                                                                                                                                     |

|             |                                                                                                                                              | 3.3.1.2                                                                                                                                                                                                                 | The P-TDC end of column logic                                                                                                                                 | . 66                                                                                                                                                                                     |

| 4           | $\operatorname{Res}$                                                                                                                         | ults from the                                                                                                                                                                                                           | first prototypes of the P-TDC architecture                                                                                                                    | 68                                                                                                                                                                                       |

|             | 4.1                                                                                                                                          | The first prot                                                                                                                                                                                                          | otype chip for CFD testing                                                                                                                                    | . 68                                                                                                                                                                                     |

|             |                                                                                                                                              | 4.1.1 The pi                                                                                                                                                                                                            | $ xel cell architecture \ldots \ldots$ | . 70                                                                                                                                                                                     |

|             |                                                                                                                                              | 4.1.1.1                                                                                                                                                                                                                 | 1 1                                                                                                                                                           |                                                                                                                                                                                          |

|             |                                                                                                                                              | 4.1.1.2                                                                                                                                                                                                                 |                                                                                                                                                               |                                                                                                                                                                                          |

|             |                                                                                                                                              | 4.1.1.3                                                                                                                                                                                                                 |                                                                                                                                                               |                                                                                                                                                                                          |

|             |                                                                                                                                              | 4.1.1.4                                                                                                                                                                                                                 | The zero crossing discriminator with non-symmetrica                                                                                                           | 1                                                                                                                                                                                        |

|             |                                                                                                                                              |                                                                                                                                                                                                                         | hysteresis                                                                                                                                                    |                                                                                                                                                                                          |

|             |                                                                                                                                              | 4.1.1.5                                                                                                                                                                                                                 |                                                                                                                                                               |                                                                                                                                                                                          |

|             | 4.2                                                                                                                                          |                                                                                                                                                                                                                         | cototype for full functionality test                                                                                                                          |                                                                                                                                                                                          |

|             |                                                                                                                                              |                                                                                                                                                                                                                         | -TDC demonstrator: the pixel analog section $\ldots$ .                                                                                                        |                                                                                                                                                                                          |

|             |                                                                                                                                              | 4.2.1.1                                                                                                                                                                                                                 | 1 1                                                                                                                                                           |                                                                                                                                                                                          |

|             |                                                                                                                                              | 4.2.1.2                                                                                                                                                                                                                 |                                                                                                                                                               |                                                                                                                                                                                          |

|             |                                                                                                                                              | 4.2.1.3                                                                                                                                                                                                                 |                                                                                                                                                               |                                                                                                                                                                                          |

|             |                                                                                                                                              | 4.2.1.4                                                                                                                                                                                                                 | Test results                                                                                                                                                  | . 93                                                                                                                                                                                     |

|             |                                                                                                                                              |                                                                                                                                                                                                                         |                                                                                                                                                               |                                                                                                                                                                                          |

| <b>5</b>    |                                                                                                                                              |                                                                                                                                                                                                                         | ASIC with improved pulse shape rejection                                                                                                                      | 131                                                                                                                                                                                      |

| 5           | 5.1                                                                                                                                          | The CFD filte                                                                                                                                                                                                           | er                                                                                                                                                            | . 132                                                                                                                                                                                    |

| 5           | $5.1 \\ 5.2$                                                                                                                                 | The CFD filte<br>The preampli                                                                                                                                                                                           | er                                                                                                                                                            | . 132<br>. 135                                                                                                                                                                           |

| 5           | $5.1 \\ 5.2 \\ 5.3$                                                                                                                          | The CFD filte<br>The preampli<br>The CFD am                                                                                                                                                                             | er                                                                                                                                                            | . 132<br>. 135<br>. 139                                                                                                                                                                  |

| 5           | $5.1 \\ 5.2 \\ 5.3 \\ 5.4$                                                                                                                   | The CFD filte<br>The preampli<br>The CFD amp<br>The discrimin                                                                                                                                                           | er                                                                                                                                                            | . 132<br>. 135<br>. 139<br>. 140                                                                                                                                                         |

| 5           | $5.1 \\ 5.2 \\ 5.3$                                                                                                                          | The CFD filte<br>The preampli<br>The CFD amy<br>The discrimin<br>Simulation res                                                                                                                                         | er                                                                                                                                                            | . 132<br>. 135<br>. 139<br>. 140<br>. 143                                                                                                                                                |

| 5           | $5.1 \\ 5.2 \\ 5.3 \\ 5.4$                                                                                                                   | The CFD filte<br>The preamplit<br>The CFD amp<br>The discrimin<br>Simulation res<br>5.5.1 The lin                                                                                                                       | er                                                                                                                                                            | . 132<br>. 135<br>. 139<br>. 140<br>. 143<br>. 143                                                                                                                                       |

| 5           | $5.1 \\ 5.2 \\ 5.3 \\ 5.4$                                                                                                                   | The CFD filte<br>The preamplit<br>The CFD amy<br>The discrimin<br>Simulation res<br>5.5.1 The lin<br>5.5.2 The le                                                                                                       | er                                                                                                                                                            | . 132<br>. 135<br>. 139<br>. 140<br>. 143<br>. 143<br>. 145                                                                                                                              |

| 5           | $5.1 \\ 5.2 \\ 5.3 \\ 5.4$                                                                                                                   | The CFD filte<br>The preamplit<br>The CFD amp<br>The discrimin<br>Simulation res<br>5.5.1 The lin<br>5.5.2 The let<br>5.5.3 The or                                                                                      | er                                                                                                                                                            | . 132<br>. 135<br>. 139<br>. 140<br>. 143<br>. 143<br>. 143<br>. 145<br>. 147                                                                                                            |

| 5           | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6                                                                                                       | The CFD filte<br>The preamplit<br>The CFD amp<br>The discrimin<br>Simulation res<br>5.5.1 The lin<br>5.5.2 The let<br>5.5.3 The or                                                                                      | er                                                                                                                                                            | . 132<br>. 135<br>. 139<br>. 140<br>. 143<br>. 143<br>. 143<br>. 145<br>. 147                                                                                                            |

| 6           | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> </ul>                                                                  | The CFD filte<br>The preamplit<br>The CFD amp<br>The discrimin<br>Simulation res<br>5.5.1 The lin<br>5.5.2 The le<br>5.5.3 The ov<br>A flexible from                                                                    | er                                                                                                                                                            | . 132<br>. 135<br>. 139<br>. 140<br>. 143<br>. 143<br>. 145<br>. 147<br>. 151<br><b>155</b>                                                                                              |

| 6           | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> </ul>                                                                  | The CFD filte<br>The preamplit<br>The CFD amp<br>The discrimin<br>Simulation res<br>5.5.1 The lin<br>5.5.2 The le<br>5.5.3 The ov<br>A flexible from                                                                    | er                                                                                                                                                            | . 132<br>. 135<br>. 139<br>. 140<br>. 143<br>. 143<br>. 143<br>. 145<br>. 147<br>. 151                                                                                                   |

| 6           | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> </ul> 5.6 Cor The                                                      | The CFD filte<br>The preamplit<br>The CFD amy<br>The discrimin<br>Simulation res<br>5.5.1 The lin<br>5.5.2 The le<br>5.5.3 The ov<br>A flexible from<br>nclusions                                                       | er                                                                                                                                                            | . 132<br>. 135<br>. 139<br>. 140<br>. 143<br>. 143<br>. 145<br>. 147<br>. 151<br><b>155</b>                                                                                              |

| 6<br>A      | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>Cor</li> <li>The</li> <li>The</li> </ul>              | The CFD filte<br>The preamplit<br>The CFD amp<br>The discrimin<br>Simulation res<br>5.5.1 The lif<br>5.5.2 The le<br>5.5.3 The ov<br>A flexible from<br><b>nclusions</b><br><b>e time walk a</b><br><b>e CFD progra</b> | er                                                                                                                                                            | <ul> <li>. 132</li> <li>. 135</li> <li>. 139</li> <li>. 140</li> <li>. 143</li> <li>. 143</li> <li>. 145</li> <li>. 147</li> <li>. 151</li> <li>155</li> <li>158</li> </ul>              |

| 6<br>A<br>B | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>Cor</li> <li>The</li> <li>The</li> <li>Fun</li> </ul> | The CFD filte<br>The preamplit<br>The CFD amy<br>The discrimin<br>Simulation res<br>5.5.1 The lin<br>5.5.2 The le<br>5.5.3 The ov<br>A flexible from<br>nclusions<br>e time walk at<br>e CFD program                    | r                                                                                                                                                             | <ul> <li>. 132</li> <li>. 135</li> <li>. 139</li> <li>. 140</li> <li>. 143</li> <li>. 143</li> <li>. 145</li> <li>. 147</li> <li>. 151</li> <li>155</li> <li>158</li> <li>164</li> </ul> |

# List of Figures

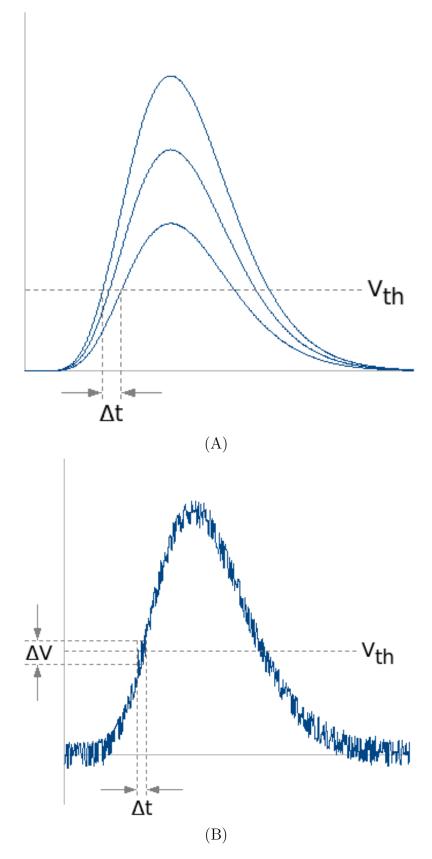

| 1.1  | (A) Signal amplitude variations generating time walk and (B) jitter                                            |                |

|------|----------------------------------------------------------------------------------------------------------------|----------------|

|      | induced by noise                                                                                               | 4              |

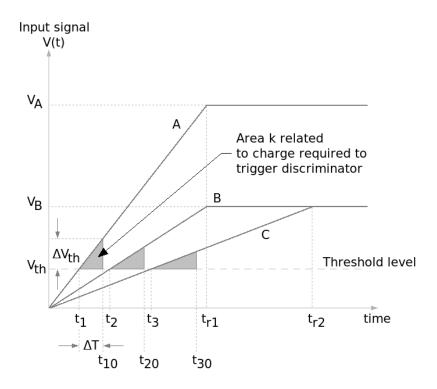

| 1.2  | Time walk in leading edge discriminator due to amplitude and rise<br>time variations and to charge sensitivity | 6              |

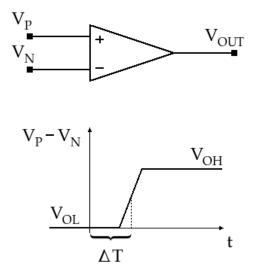

| 1.3  | Leading edge discriminator output is affected by a propagation delay                                           |                |

|      | equal to the time needed by the output to reach the 50% of the signal,                                         |                |

|      | measured with respect to the threshold crossing time                                                           | 6              |

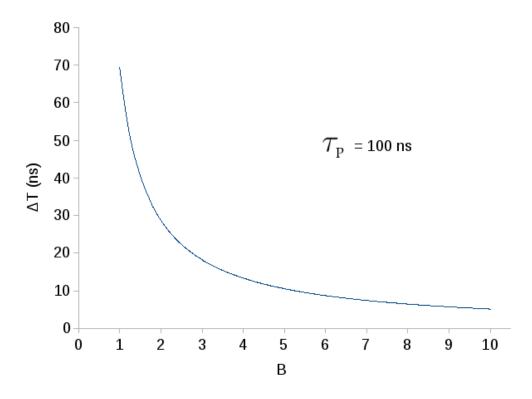

| 1.4  | Propagation delay versus the ratio between the actual and the mini-                                            | -              |

|      | mum detectable signal for $\tau_{\rm P} = 100 \text{ ns} \dots \dots \dots \dots \dots \dots$                  | $\overline{7}$ |

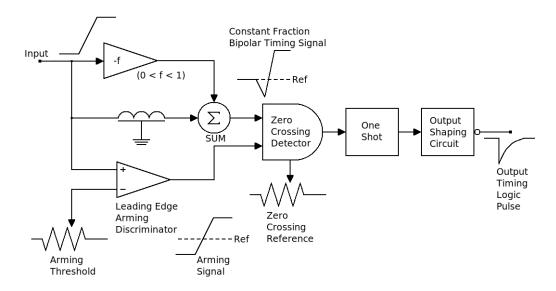

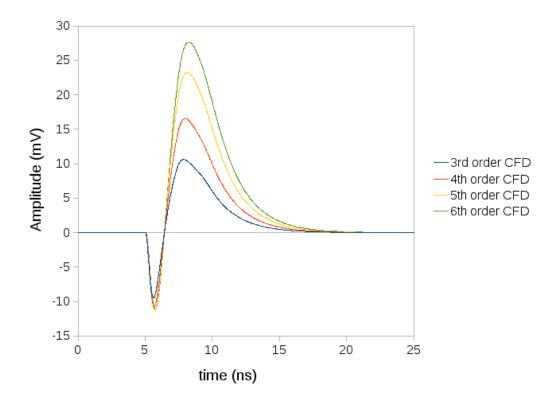

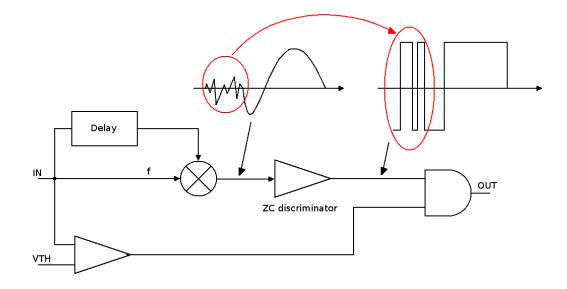

| 1.5  | Functional representation of a CFD                                                                             | 8              |

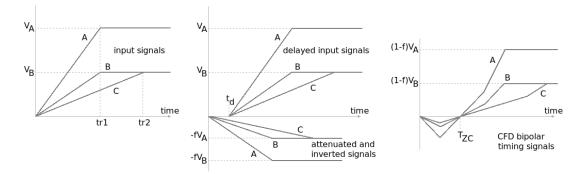

| 1.6  | Signal formation in a CFD                                                                                      | 9              |

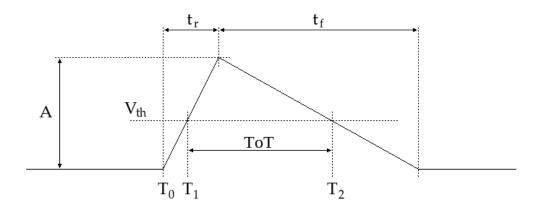

| 1.7  | Triangular signal with a rise time $t_r$ and a fall time $t_f$                                                 | 12             |

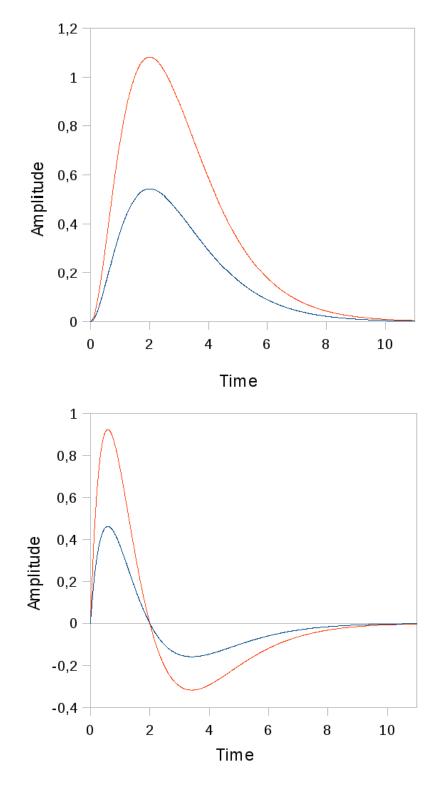

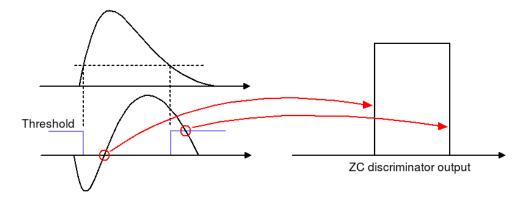

| 1.8  | Principle of the crossover technique                                                                           | 14             |

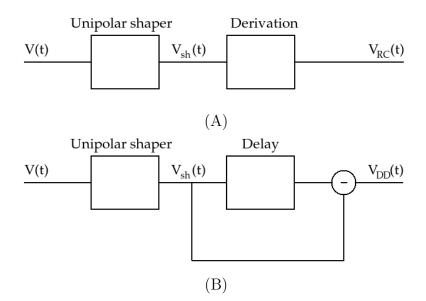

| 1.9  | Block diagram of the two mostly used alternative to implement a                                                |                |

|      | bipolar filter starting from an unipolar shaper: (A) the RC shaper                                             |                |

|      | and (B) the double delay line                                                                                  | 15             |

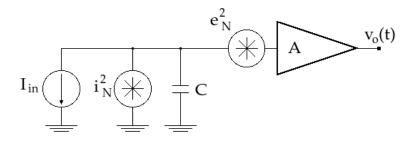

| 1.10 | Block diagram of the detector and the preamplifier with noise sources                                          | 17             |

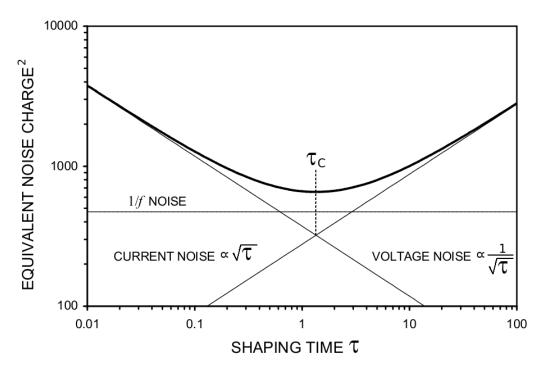

|      | The dependence of the preamplifier noise contribution on the ampli-                                            |                |

|      | fier shaping time constant                                                                                     | 18             |

| 1.12 | Output of the full chain composed by the amplifier, whitening filter                                           |                |

|      | and shaper for optimum energy measurement                                                                      | 19             |

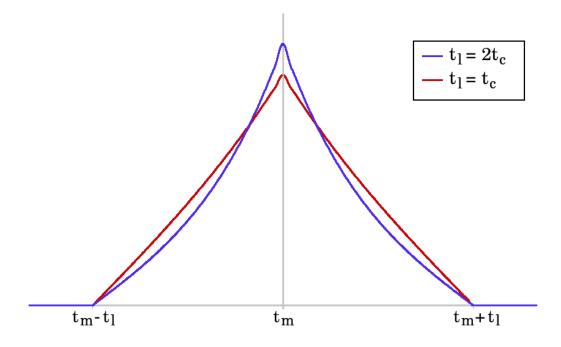

| 1.13 | Output of the sub-optimum filter with finite duration $t_1 \ldots \ldots \ldots$                               | 21             |

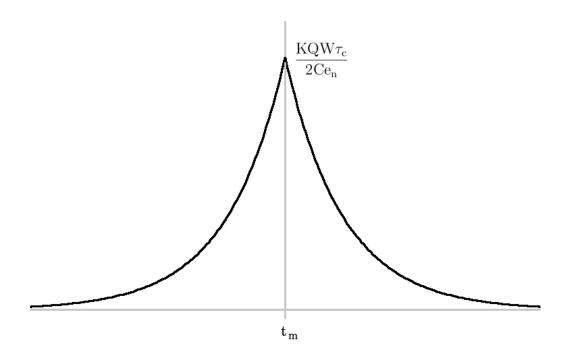

| 1.14 | Output of the full chain composed by amplifier, whitening filter and                                           |                |

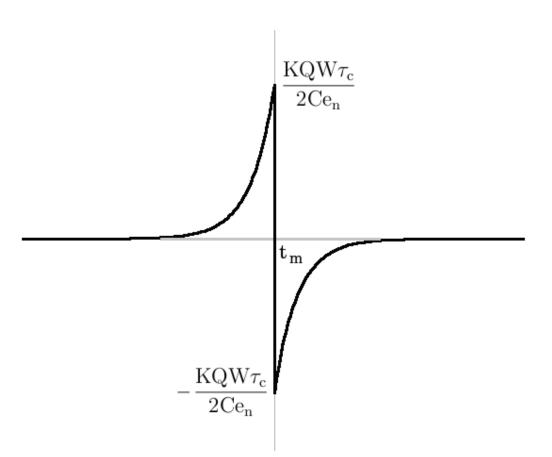

|      | shaper for optimum timing                                                                                      | 23             |

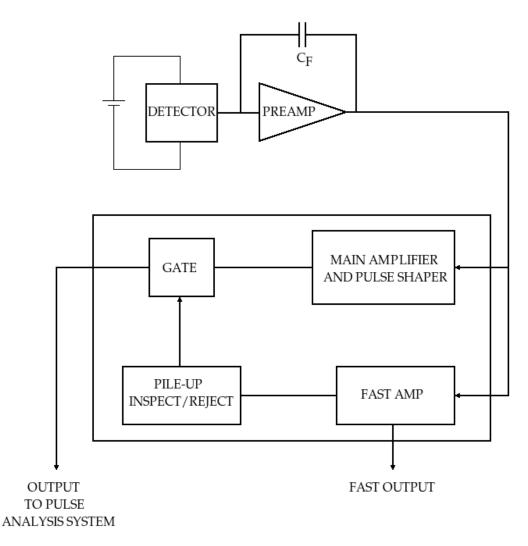

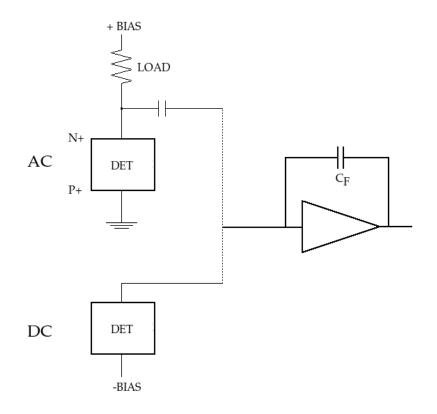

| 1.15 | Basic block diagram of a spectroscopy system                                                                   | 24             |

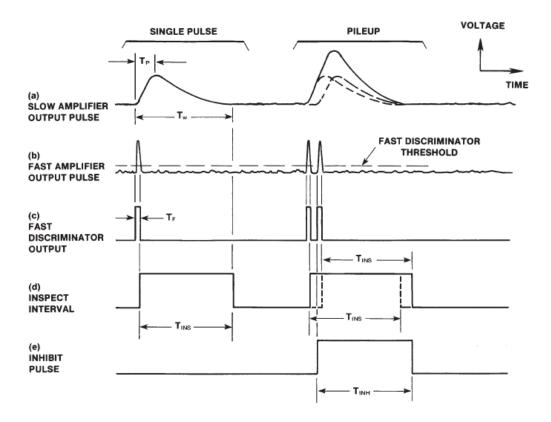

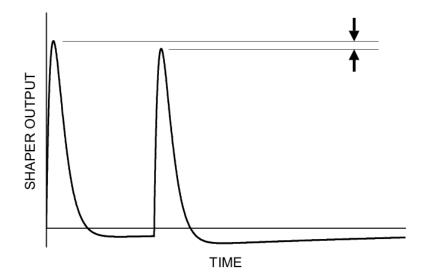

| 1.16 | Basic waveform in the pile-up rejector                                                                         | 25             |

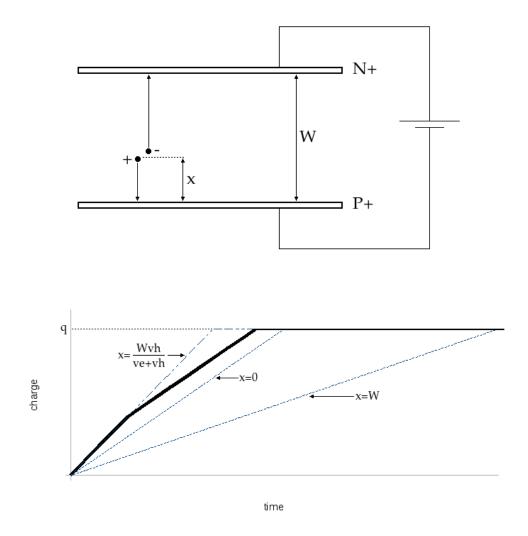

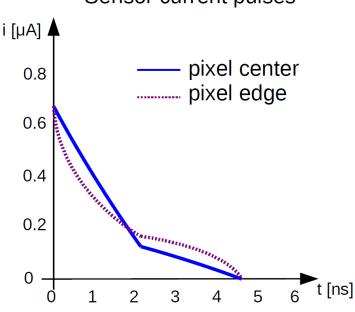

| 1.17 | Pulse shape generation in a planar detector                                                                    | 27             |

|      | Coupling of the detector with the preamplifier                                                                 | 29             |

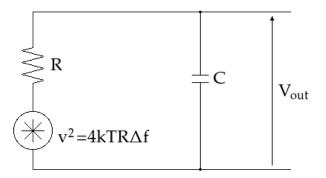

|      | Equivalent input circuit of a detector preamplifier circuit                                                    | 29             |

|      | Loss of resolution at high counting rates due to baseline variations                                           | 30             |

|      | Pole-zero cancellation circuit                                                                                 | 30             |

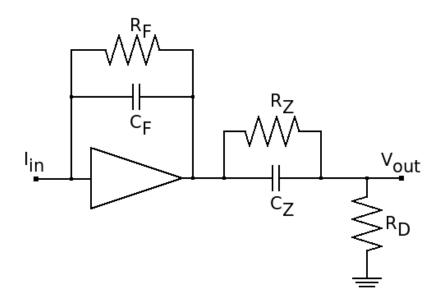

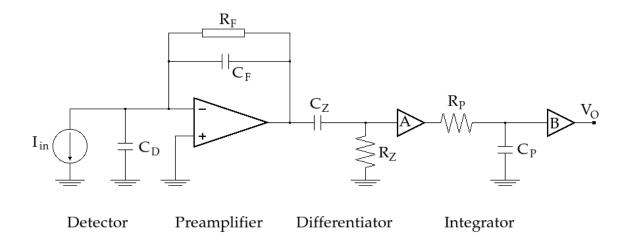

|      | Basic CR-RC shaper                                                                                             | 32             |

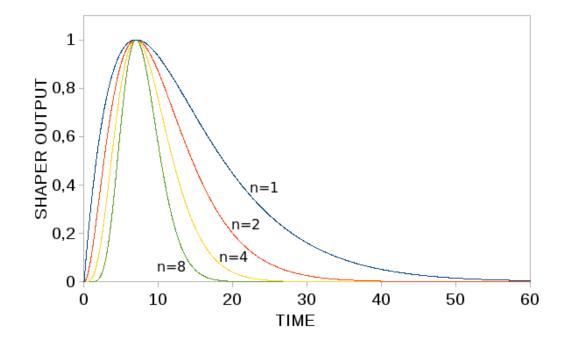

| 1.23 | Output of CR-RC <sup>n</sup> filters with the time constants adjusted to preserve                              |                |

|      | the peaking time                                                                                               | 32             |

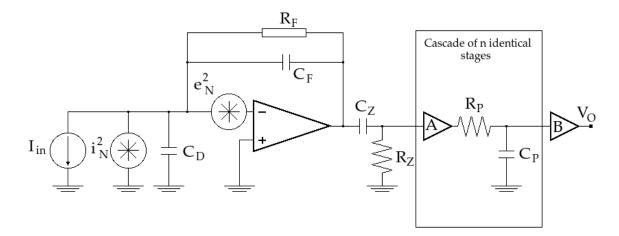

|      | Block diagram of a CR-RC <sup>n</sup> shaper with noise sources                                                | 33             |

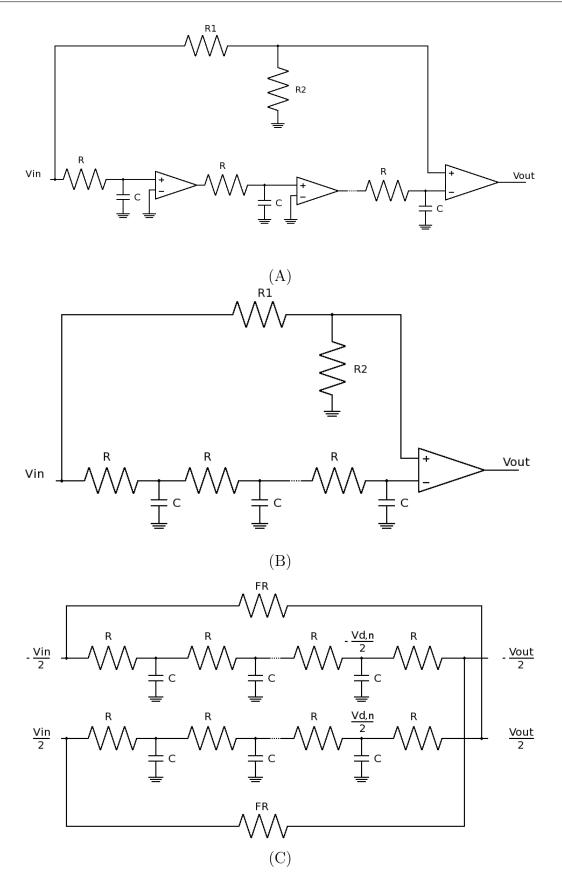

| 1.25 | (A) Implementation of the CFD using a distributed RC delay line                                                |                |

|      | with (B) and without fast buffers. (C) Cross coupling CFD topology                                             | 36             |

| 1.26 | Output of the three considered CFD architectures shown in Fig. 1.25                                            | 37             |

### LIST OF FIGURES

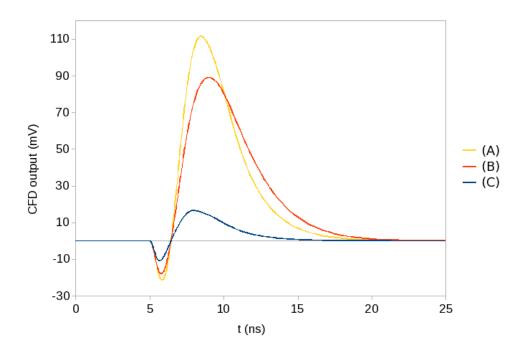

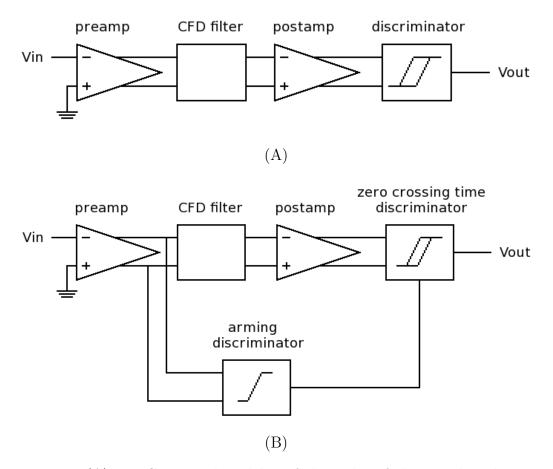

| 1.27<br>1.28      | Simulation result of the cross coupling CFD with different filter orders<br>and a fixed fraction of the 25%                                                                                                                  | . 38<br>. 40 |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

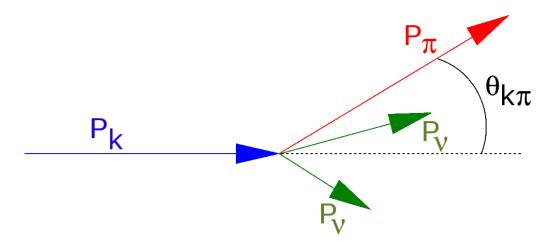

| 2.1               | Kinematics of $K^+ \to \pi^+ \nu \overline{\nu}$                                                                                                                                                                             | . 42         |

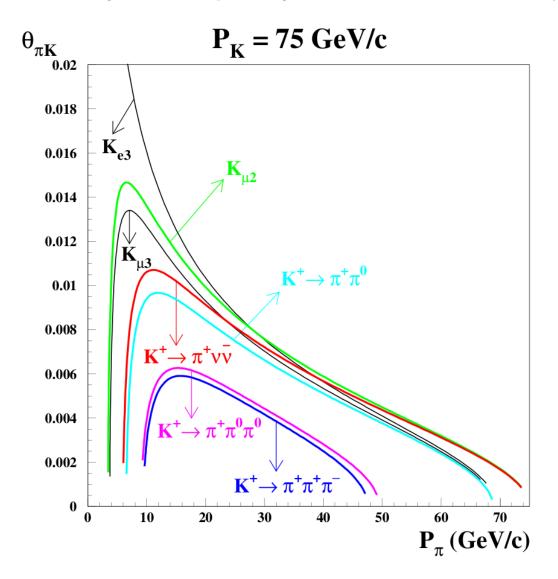

| 2.1<br>2.2<br>2.3 | Angle-momentum relation for $K^+$ decays $\ldots \ldots \ldots \ldots \ldots$<br>Squared missing mass distribution for signal and background events                                                                          | . 43         |

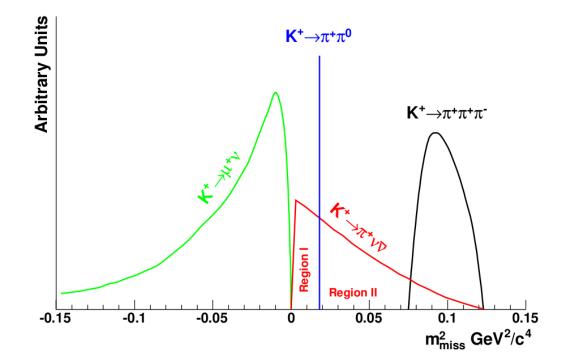

| 0.4               | under the hypothesis that the final state is a $\pi^+$                                                                                                                                                                       |              |

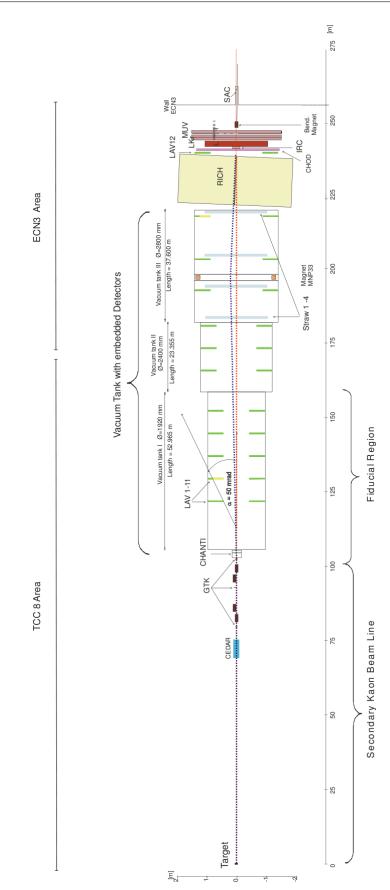

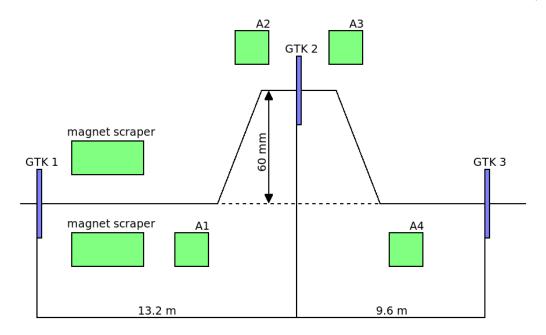

| 2.4               | NA62 experimental setup                                                                                                                                                                                                      |              |

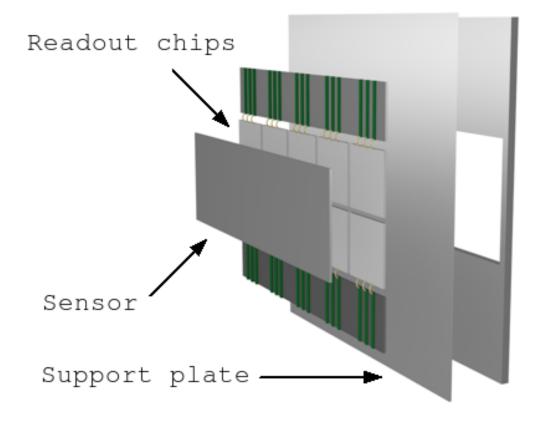

| $2.5 \\ 2.6$      | Schematic layout of the Gigatracker                                                                                                                                                                                          |              |

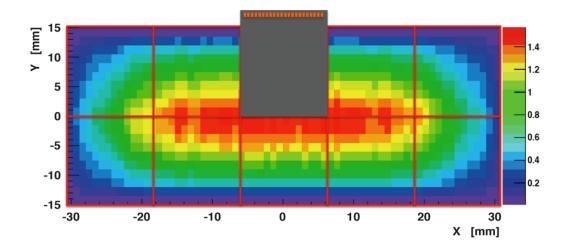

| 2.7               | sensor are supported by a carbon plate outside the beam area $\ldots$ . GTK beam intensity distribution expressed in MHz/mm <sup>2</sup> . The ASICs placed in the central region of the beam must sustain a higher particle | . 49         |

|                   | flux                                                                                                                                                                                                                         | . 50         |

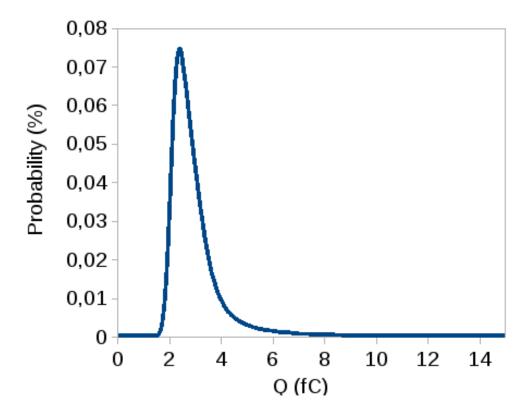

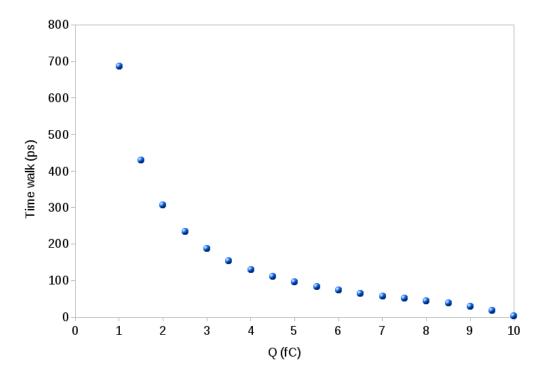

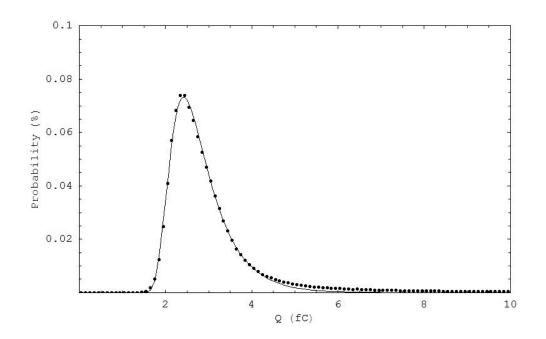

| 3.1               | Landau distribution of input charges generated in 200 $\mu$ m silicon layer                                                                                                                                                  | 50           |

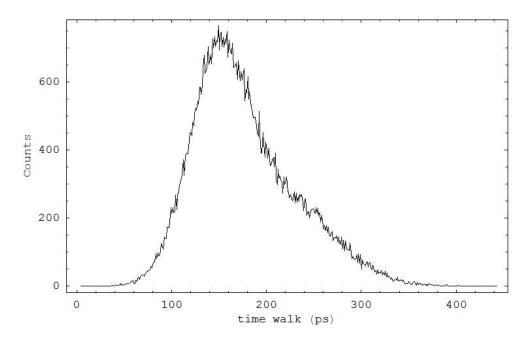

| 3.2               | with most probable value around 2.4 fC                                                                                                                                                                                       |              |

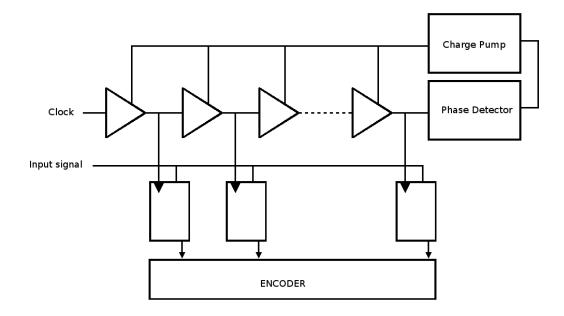

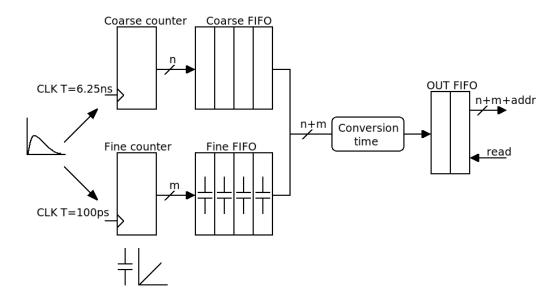

| э.∠<br>3.3        | The DLL based TDC principle                                                                                                                                                                                                  |              |

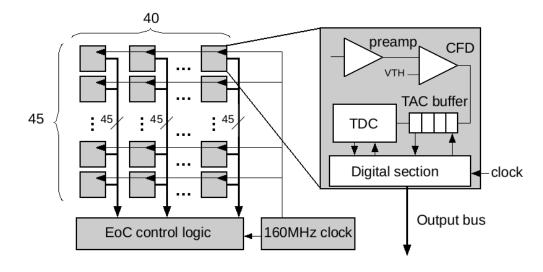

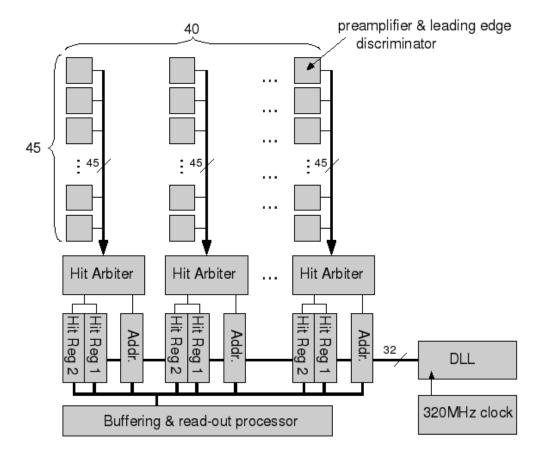

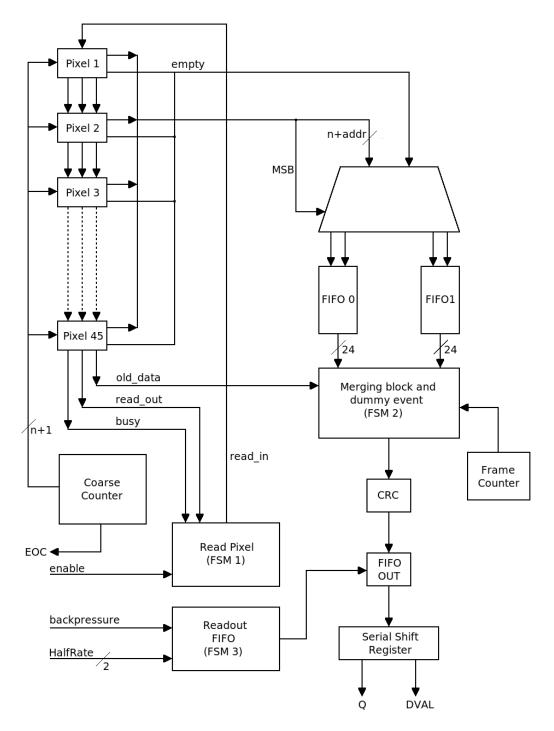

| 3.3<br>3.4        | The P-TDC architecture block diagram                                                                                                                                                                                         |              |

| $3.4 \\ 3.5$      | Block diagram of the EoC pixel cell                                                                                                                                                                                          |              |

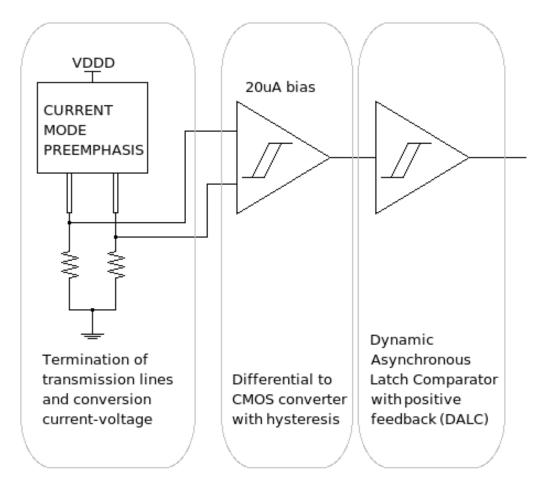

| 3.6               | Block diagram of the transmission line receiver                                                                                                                                                                              |              |

| 3.7               | Block diagram of the P-TDC pixel cell                                                                                                                                                                                        |              |

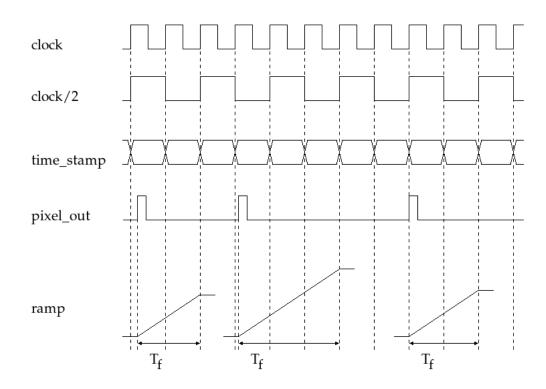

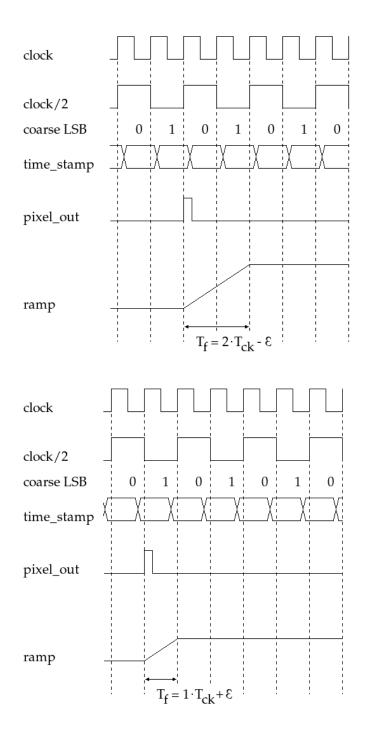

| 3.8               | Generation of the time information in the TAC based TDC                                                                                                                                                                      |              |

| 3.9               | Possible conditions which can lead to the state <i>Error</i> 1                                                                                                                                                               |              |

| 3.10              | Possible conditions which can lead to the state <i>Error</i> $2 \ldots \ldots$                                                                                                                                               | . 62         |

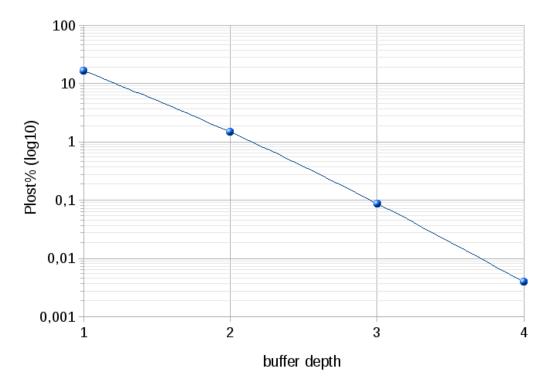

| 3.11              | Probability of losing one event with a number of buffers from 1 to 4                                                                                                                                                         | . 64         |

| 3.12              | The pixel model for multi-event buffer simulations with VHDL                                                                                                                                                                 | . 65         |

| 3.13              | The P-TDC end of column block diagram                                                                                                                                                                                        | . 67         |

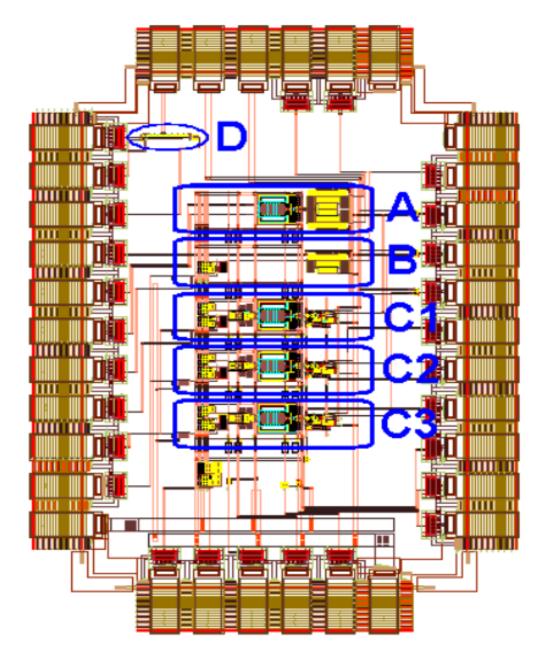

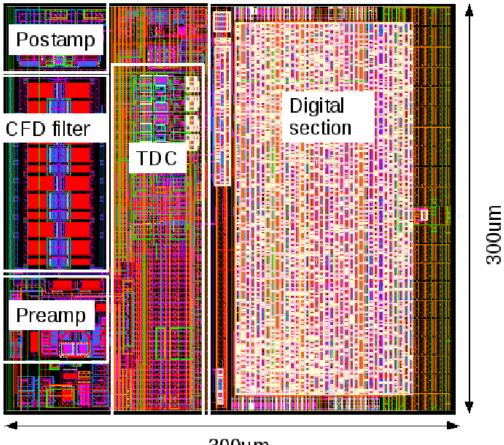

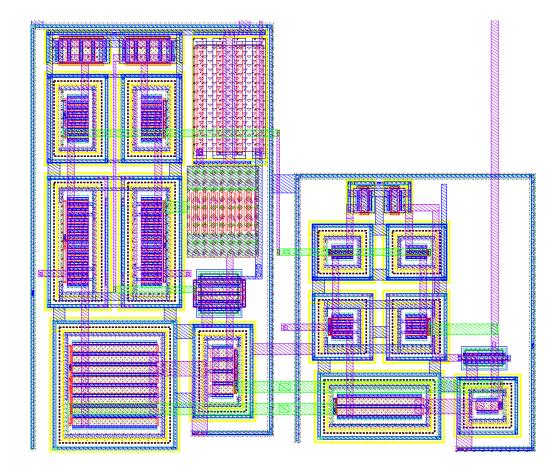

| 4.1               | First prototype chip layout                                                                                                                                                                                                  | . 69         |

| 4.2               | First prototype pixel cell layout                                                                                                                                                                                            |              |

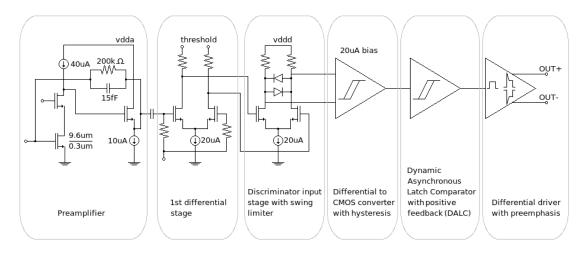

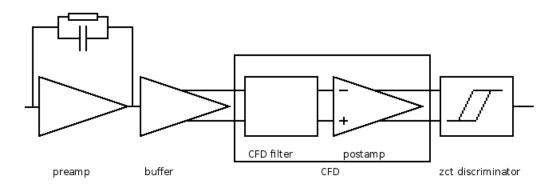

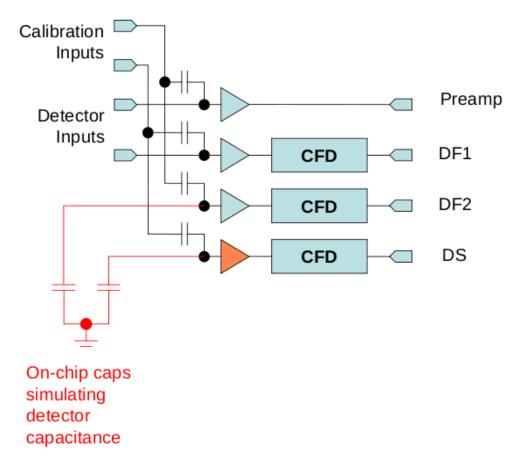

| 4.3               | Block diagram of the pixel cell of the first prototype                                                                                                                                                                       |              |

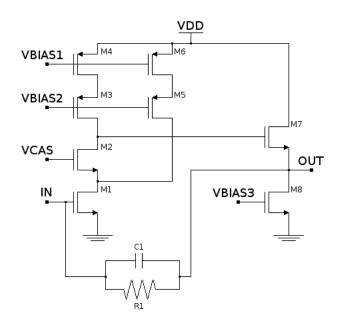

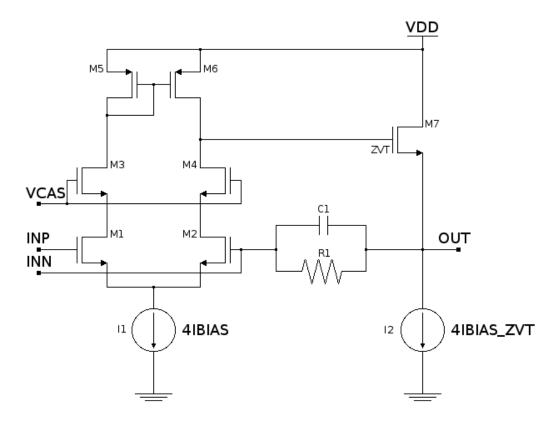

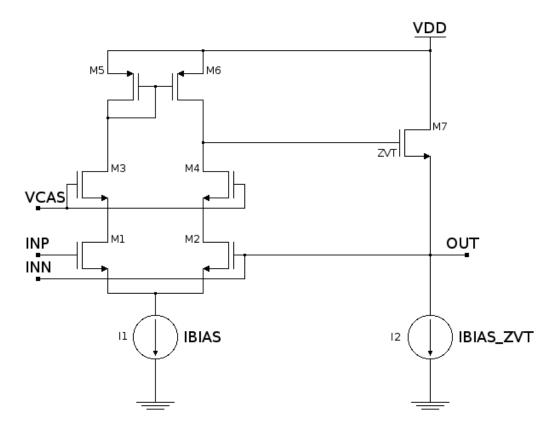

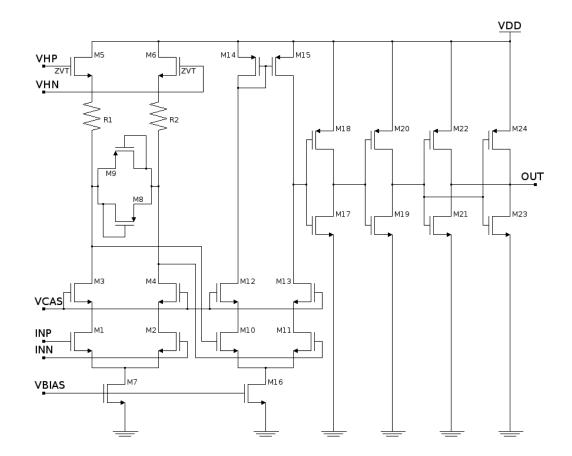

| 4.4               | Low noise preamplifier schematic                                                                                                                                                                                             |              |

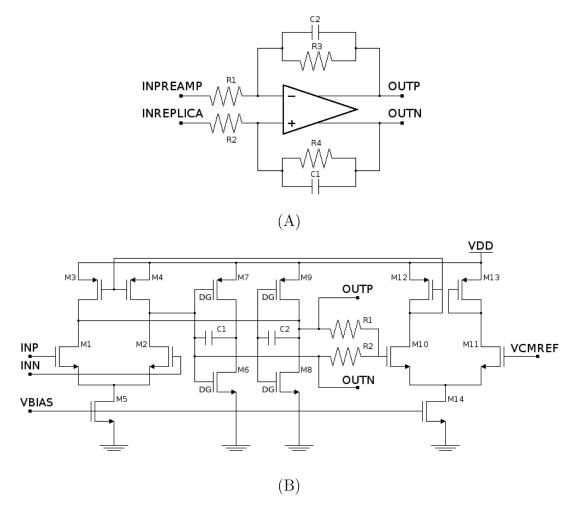

| 4.5               | (A) Buffer single-ended to differential configuration and (B) op-amp                                                                                                                                                         |              |

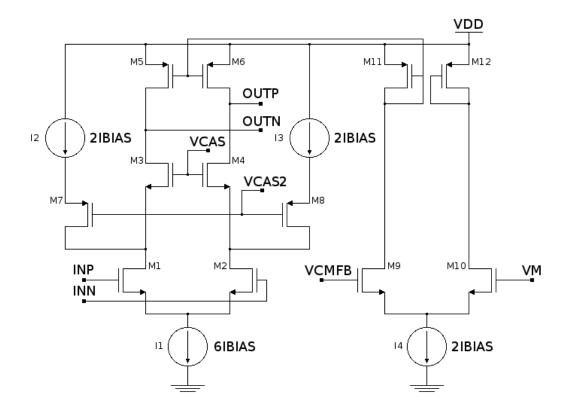

|                   | schematic                                                                                                                                                                                                                    |              |

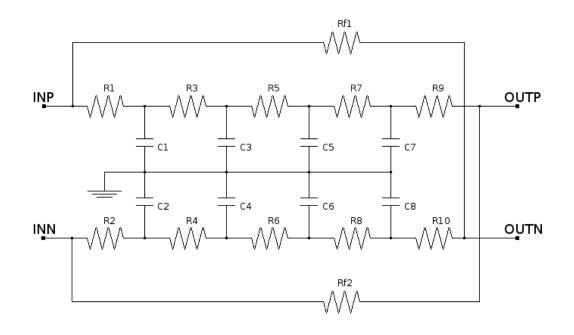

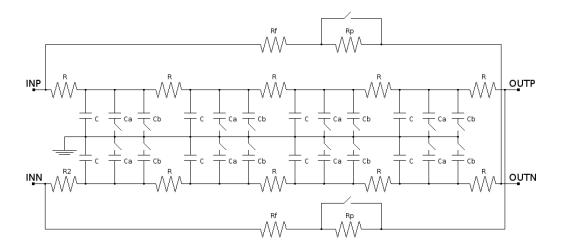

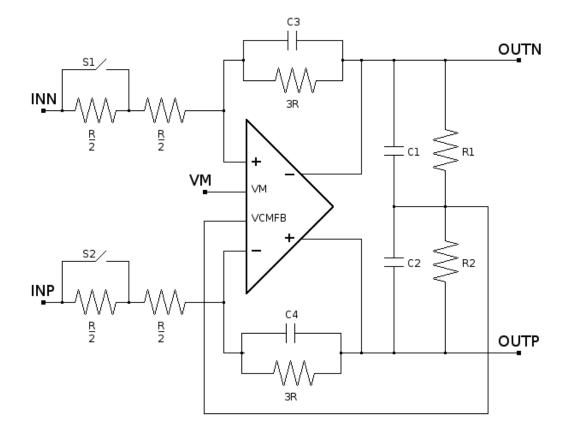

| 4.6               | (A) CFD filter (B) and zero crossing post amplifier schematics                                                                                                                                                               | . 74         |

| 4.7               | Complete schematic of the CFD block, including the dynamic offset                                                                                                                                                            |              |

| 1.0               | compensation circuit                                                                                                                                                                                                         |              |

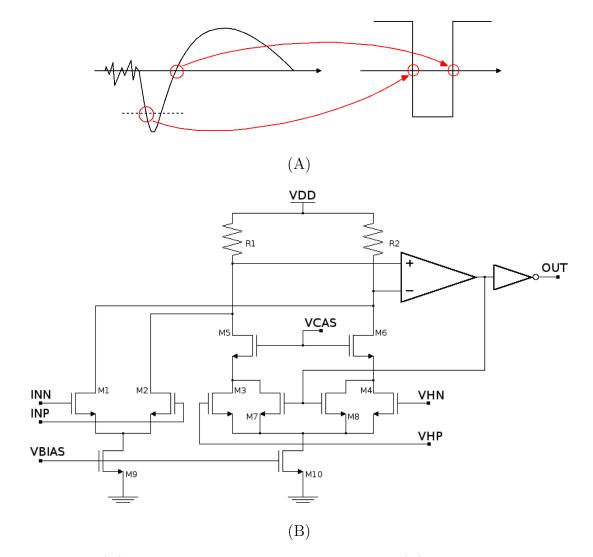

| $4.8 \\ 4.9$      | Traditional implementation of the zero crossing discrimination circuit (A) Non-symmetrical hysteresis principle. (B) Schematic of the zero                                                                                   |              |

|                   | crossing discriminator implementing the threshold hysteresis                                                                                                                                                                 |              |

| 4.10              | Block diagram of the prototype chip                                                                                                                                                                                          | . 78         |

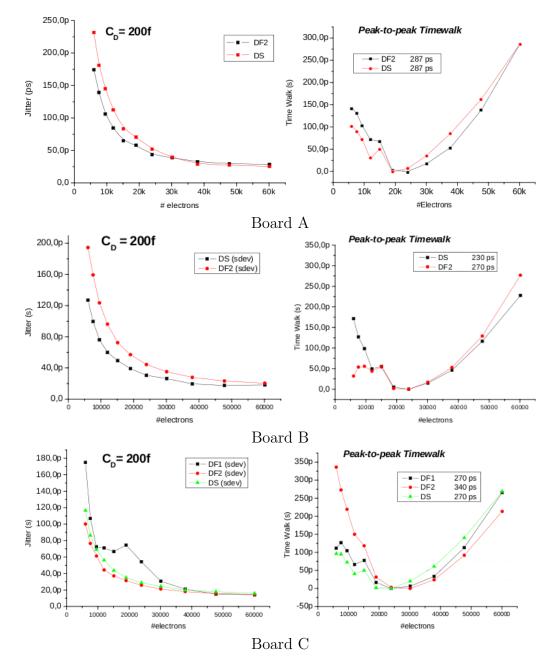

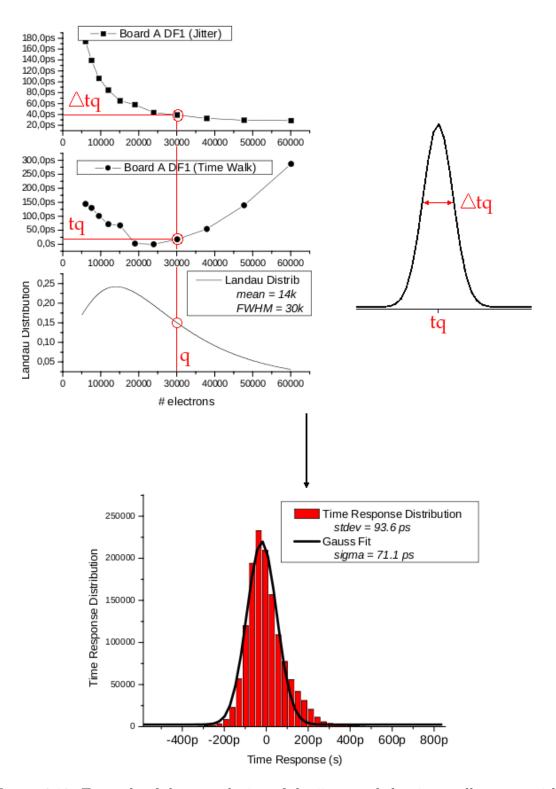

| 4.11 | Jitter and time walk resulting from the electrical tests of boards A, B and C | 79  |

|------|-------------------------------------------------------------------------------|-----|

| 4.12 | Example of the convolution of the jitter and the time walk curves             | 19  |

|      | with the expected Landau of the experiment centered at 1 MIP                  | 80  |

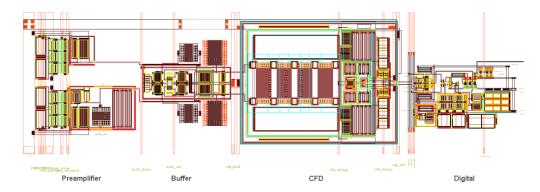

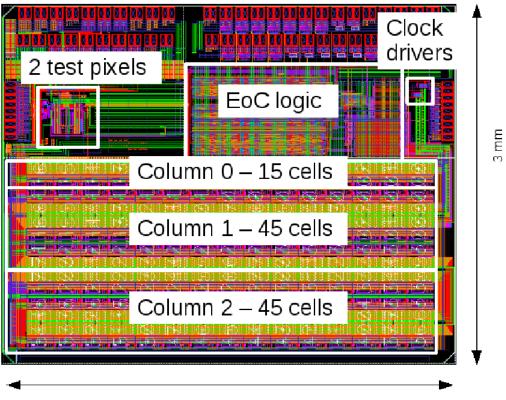

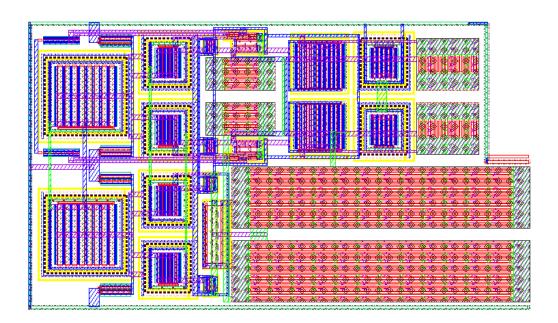

| 4.13 | Second prototype chip layout                                                  | 82  |

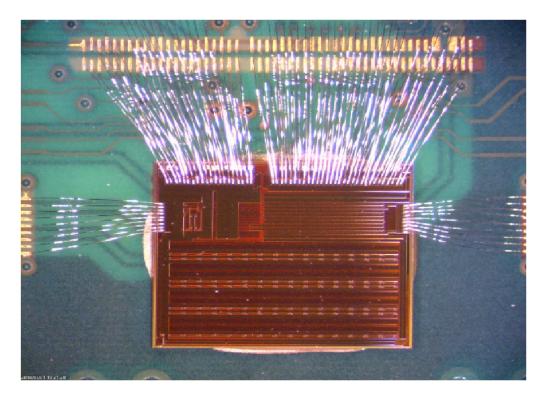

|      | Picture of the P-TDC ASIC prototype wire bonded to the PCB                    | 82  |

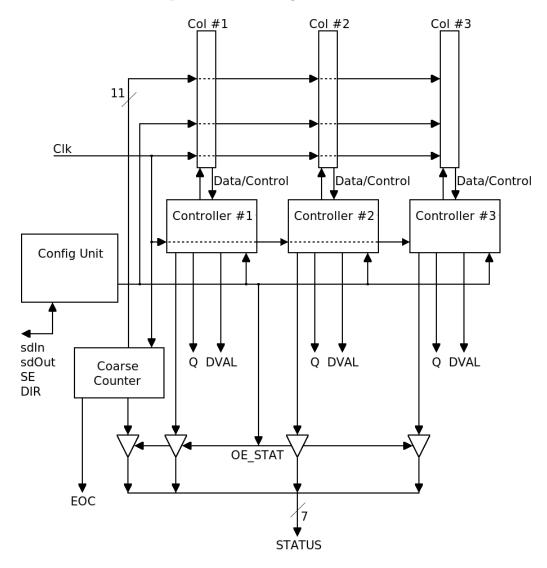

|      | P-TDC demonstrator ASIC block diagram                                         | 83  |

|      | Second prototype pixel cell layout                                            | 84  |

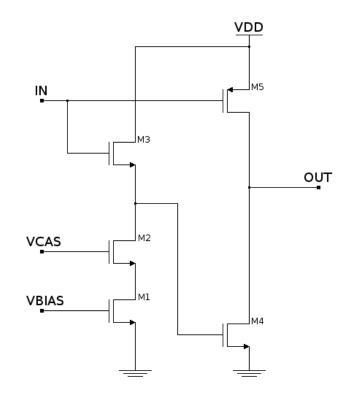

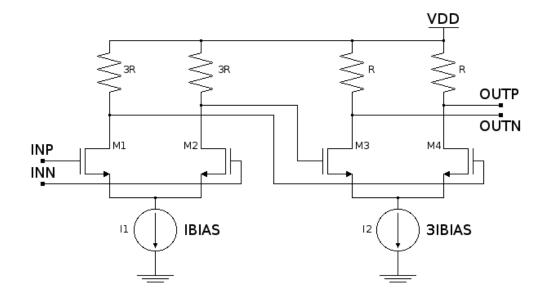

|      | First stage of the preamplifier                                               | 85  |

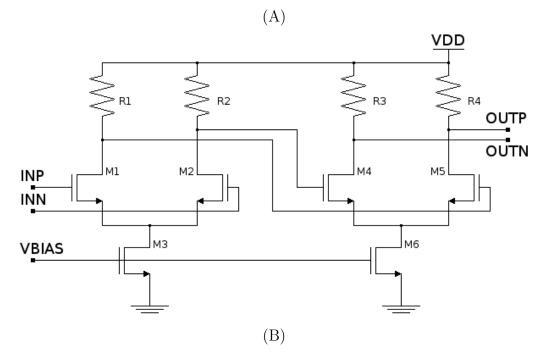

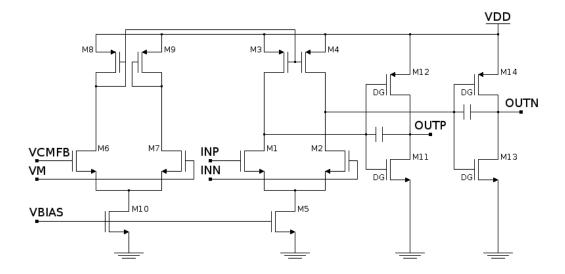

|      | Simplified schematic of the class AB output stage of the preamplifier         | 86  |

|      | Schematic of the preamplifier with the leakage compensation circuit .         | 86  |

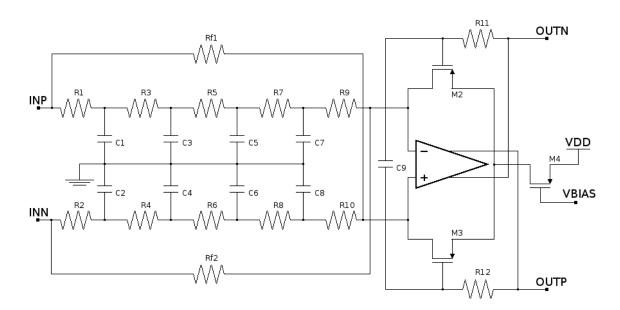

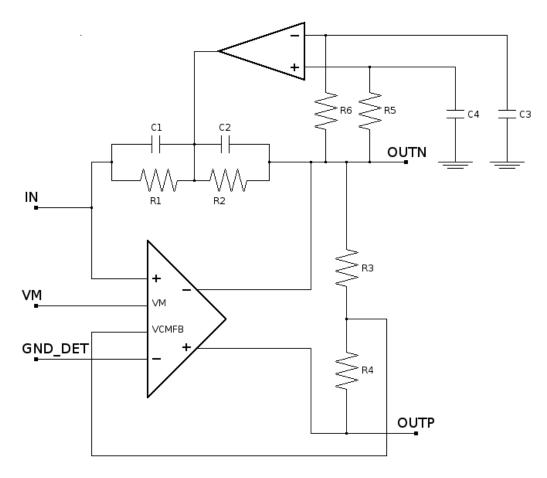

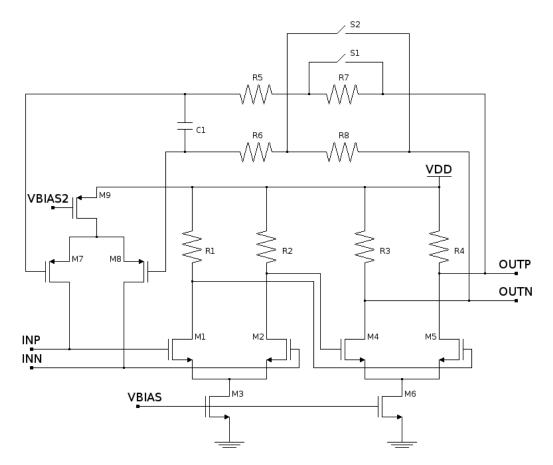

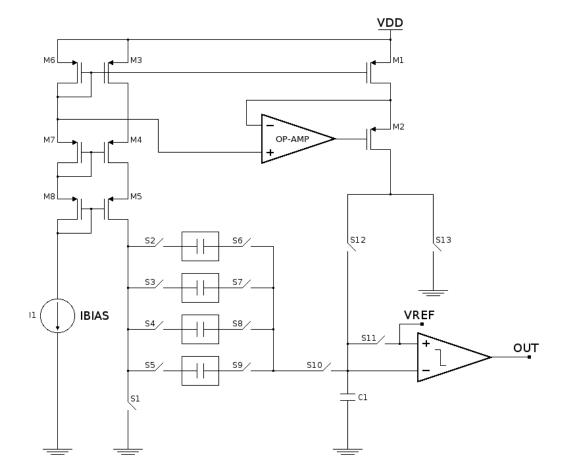

|      | Schematic of the programmable CFD filter                                      | 87  |

|      | Post amplifier stage with the dynamic offset compensation circuit.            |     |

|      | For high amplitude signals it has been forseen a reset in order to            |     |

|      | prevent a big dead time                                                       | 88  |

| 4.22 | Last discriminator stage                                                      | 89  |

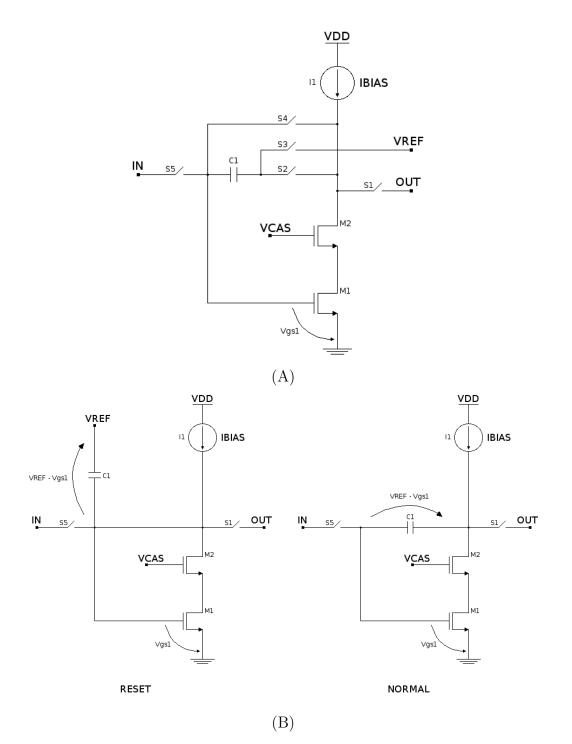

|      | (A) Schematic of the TAC buffer and (B) principle of operation in             |     |

| 1.20 | reset and normal mode                                                         | 91  |

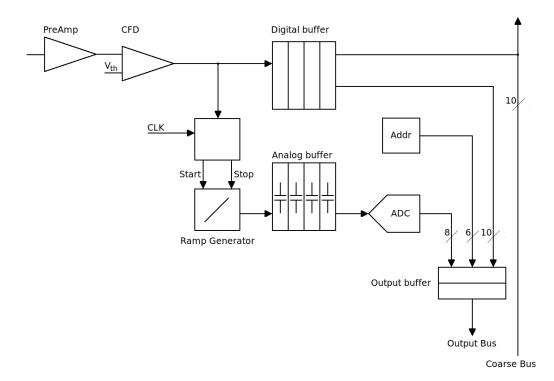

| 4.24 | TAC based TDC block diagram                                                   | 92  |

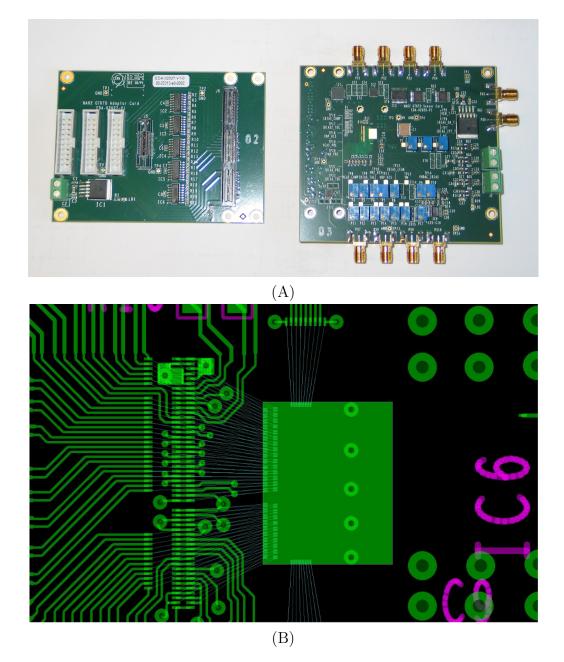

|      | (A) Picture of the PCBs used for the ASIC tests. On the right the             | 0_  |

| 1.20 | sensor card with the chip wirebonded, on the left the adapter card            |     |

|      | used with the DPG and the LSA. (B) Detail of the bonding area of              |     |

|      | the sensor card                                                               | 94  |

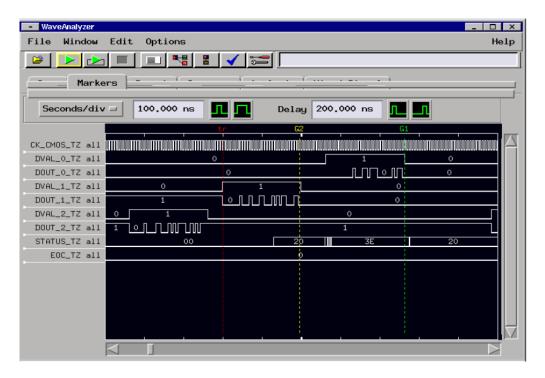

| 4.26 | LSA screenshot of the EoC output data                                         | 96  |

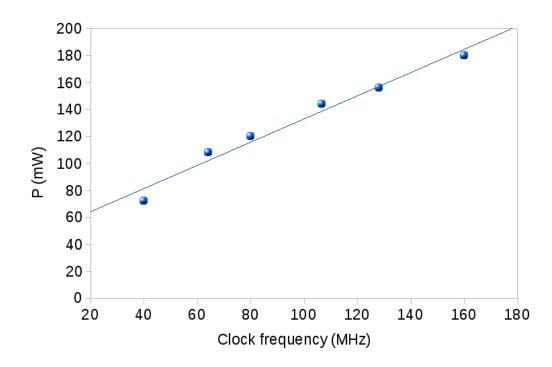

|      | Dependency of the power consumption of the EoC on clock frequency             | 97  |

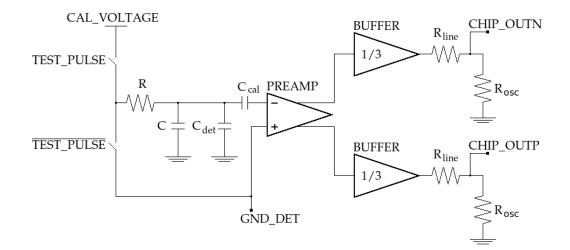

|      | On chip charge injection mechanism and preamplifier output buffering          | 01  |

| 1.20 | in the test pixel                                                             | 98  |

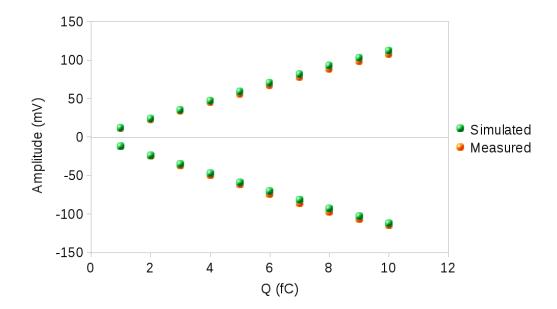

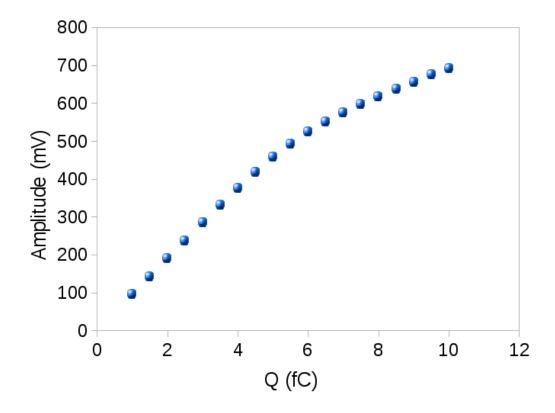

| 429  | Preamplifier output peak amplitude compared with the simulation               | 00  |

| 1.20 | results in the dynamic range from 1 fC to 10 fC                               | 98  |

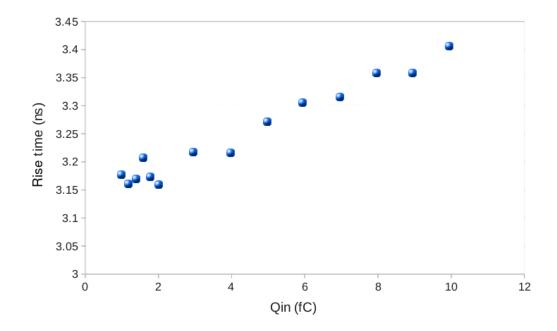

| 4 30 | Peaking time of the preamplifier signal measured in the dynamic range         | 50  |

| 1.00 | from 1 fC to 10 fC                                                            | 99  |

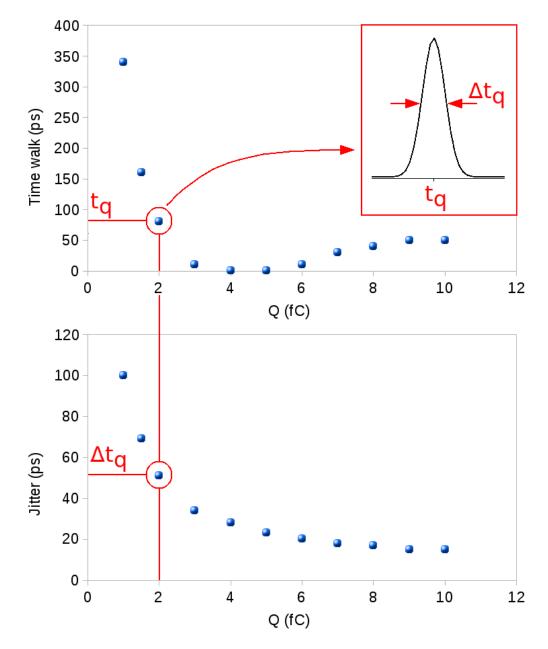

| 4 31 | Time walk curve and jitter measured from the test pixel on the bipolar        | 55  |

| 1.01 | signal at the oscilloscope                                                    | 100 |

| 4 32 | Convolution of the time walk and of the jitter measured from the test         | 100 |

| 1.02 | pixel with the expected Landau of the experiment                              | 101 |

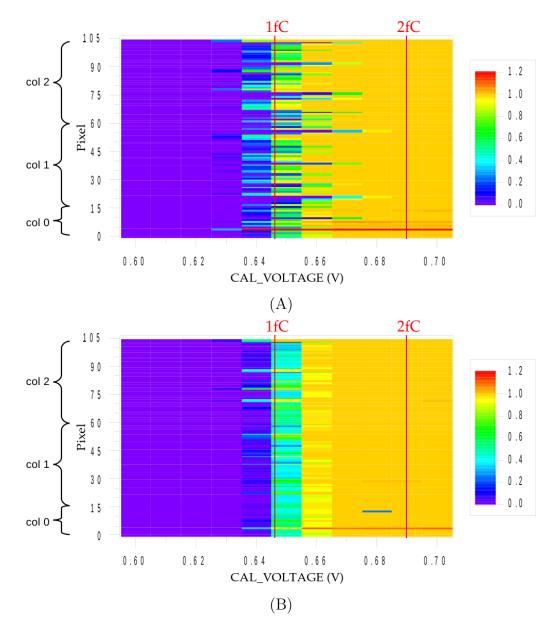

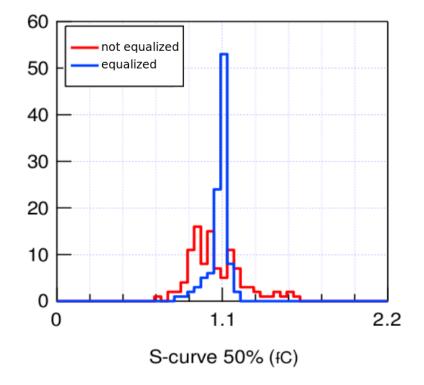

| 4 33 | Scan of the threshold of all the discriminators in the matrix (A) before      | 101 |

| 1.00 | and (B) after the equalization with the DAC on chip                           | 102 |

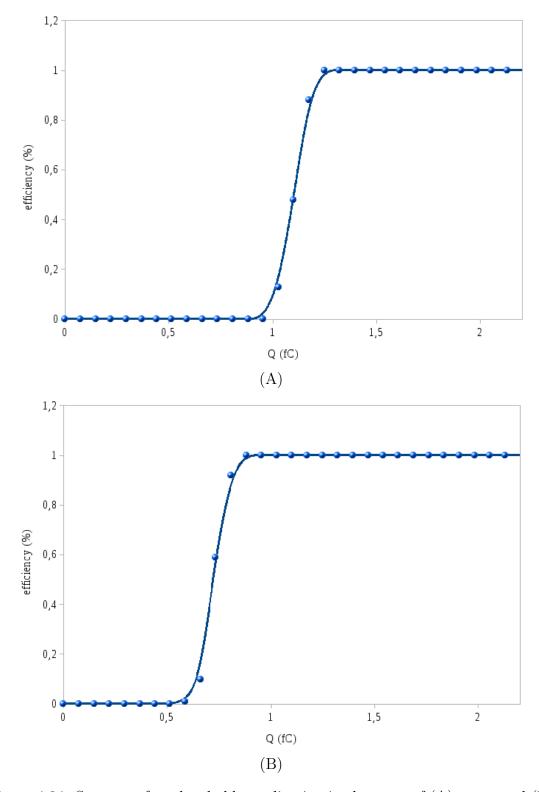

| 4 34 | S curves after threshold equalization in the cases of (A) worse and           | 102 |

| 1.01 | (B) best efficiency                                                           | 103 |

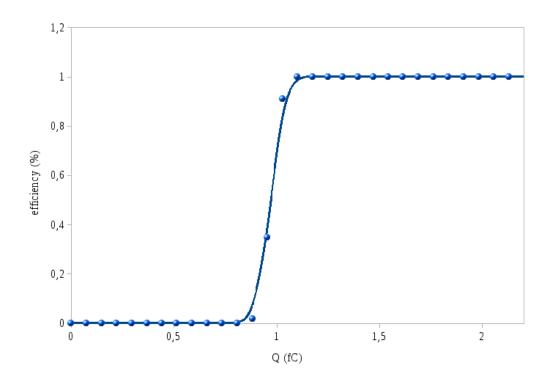

| 1 35 | S curves after threshold equalization in the cases of typical efficiency.     |     |

|      | Histogram of the charge value at which the efficiency is 50% for all          | 104 |

| т.00 | the matrix pixels before and after the threshold equalization                 | 104 |

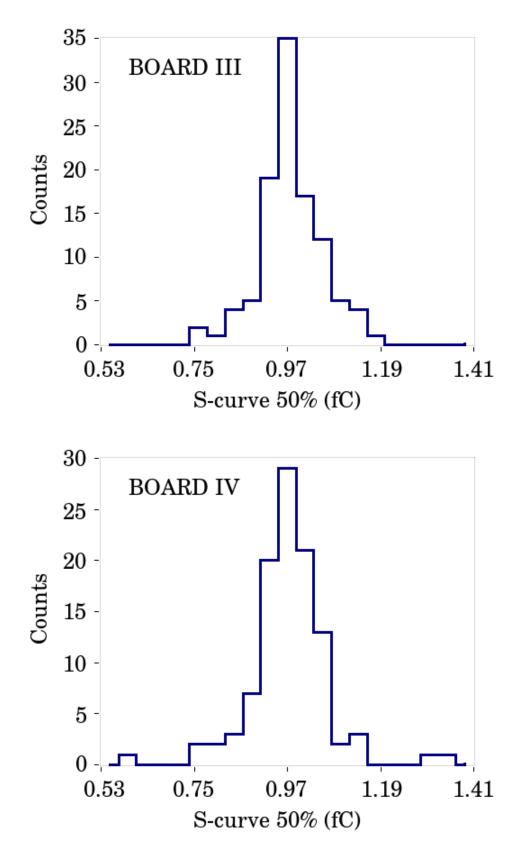

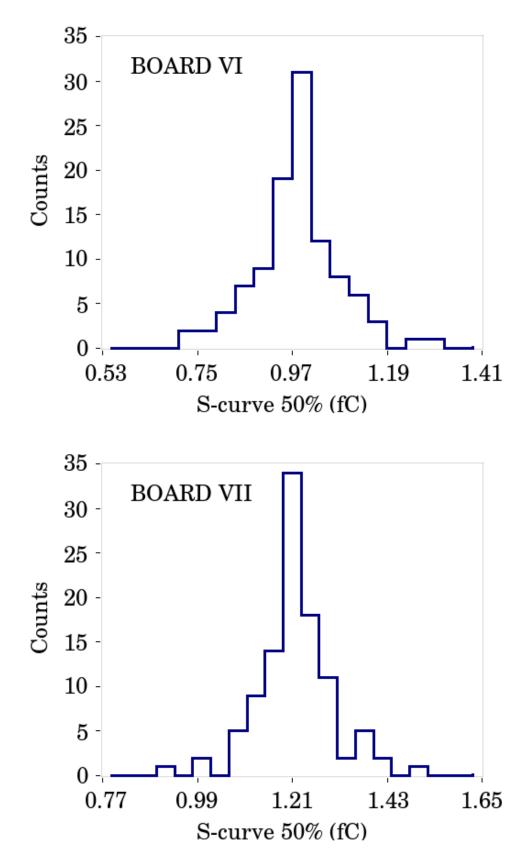

| 1 27 | Threshold dispersion after equalization for different chips mounted           | 104 |

| 4.01 | on boards III and IV                                                          | 105 |

| 1 28 | Threshold dispersion after equalization for different chips mounted           | 100 |

| т.90 | on boards V and VII                                                           | 106 |

|      |                                                                               | 100 |

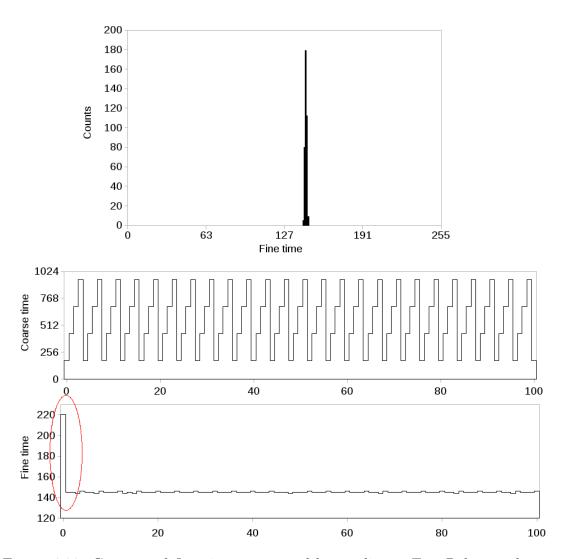

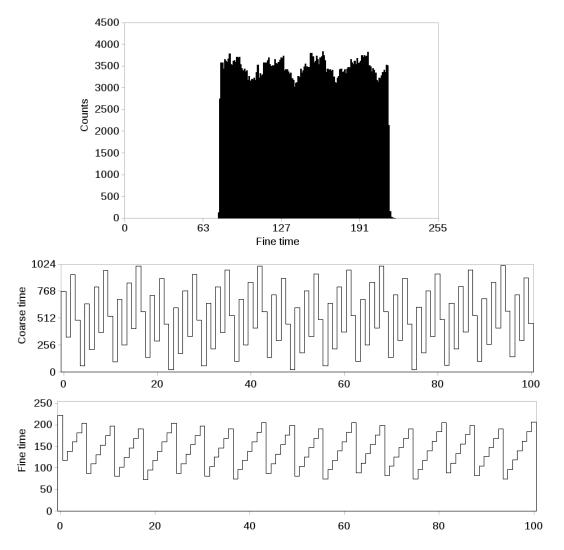

| 4.39 | Coarse and fine times measured by sending a <i>Test Pulse</i> synchronous  |       |

|------|----------------------------------------------------------------------------|-------|

|      | to the clock. To be noted the first point in the fine time plot due to     |       |

|      | the discharging of the TAC storage capacitor in idle mode                  | . 108 |

| 4.40 | Coarse and fine times measured by sending a <i>Test Pulse</i> asynchronous |       |

|      | to the clock                                                               | . 109 |

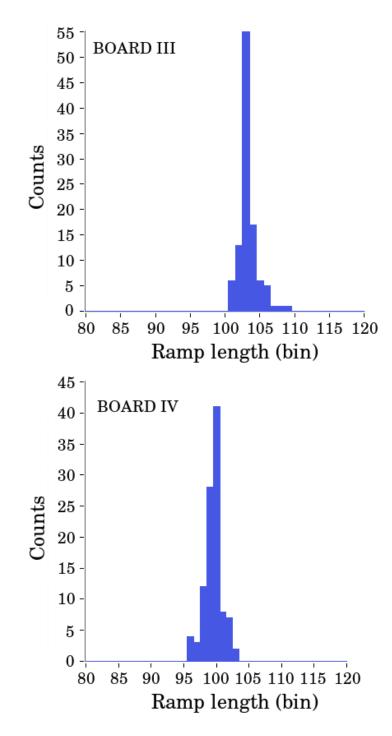

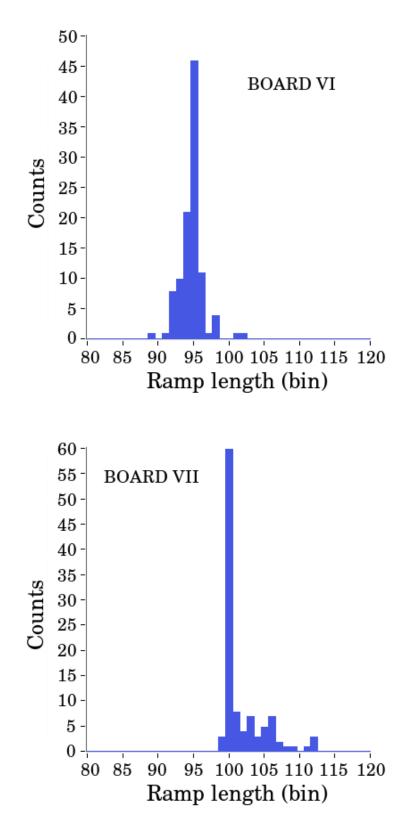

| 4.41 | TDC ramp length after the equalization for all the matrix pixels of        |       |

|      | chips mounted on board III and IV                                          | . 111 |

| 4.42 | TDC ramp length after the equalization for all the matrix pixels of        |       |

|      | chips mounted on board VI and VII                                          | . 112 |

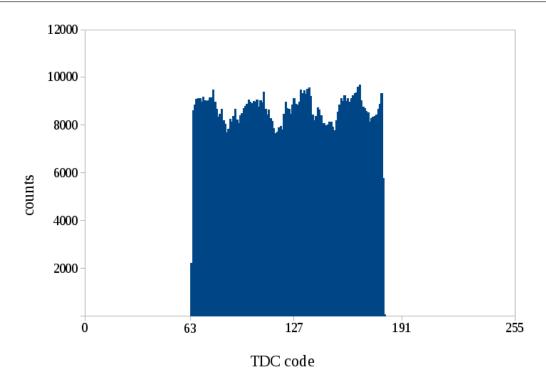

| 4.43 | Output of the TDC obtained by sending a set of asynchronous <i>Test</i>    |       |

|      | Pulses                                                                     | . 113 |

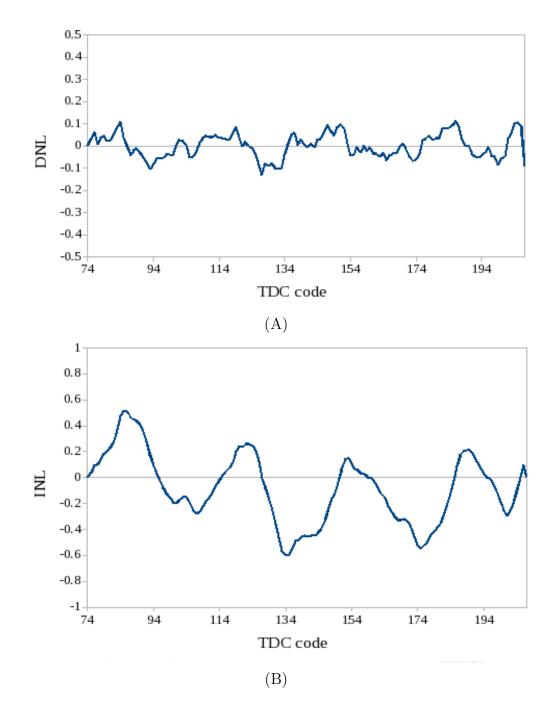

| 4.44 | DNL and INL calculated for one pixel                                       |       |

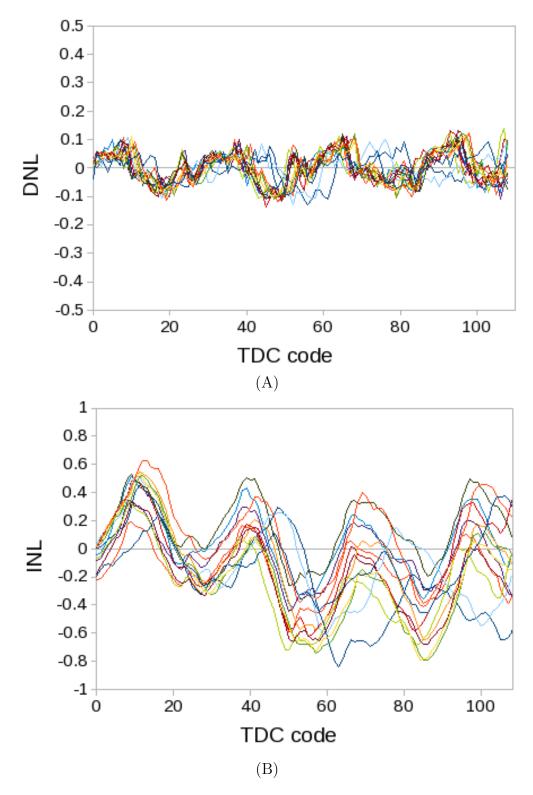

|      | DNL and INL of a full column                                               |       |

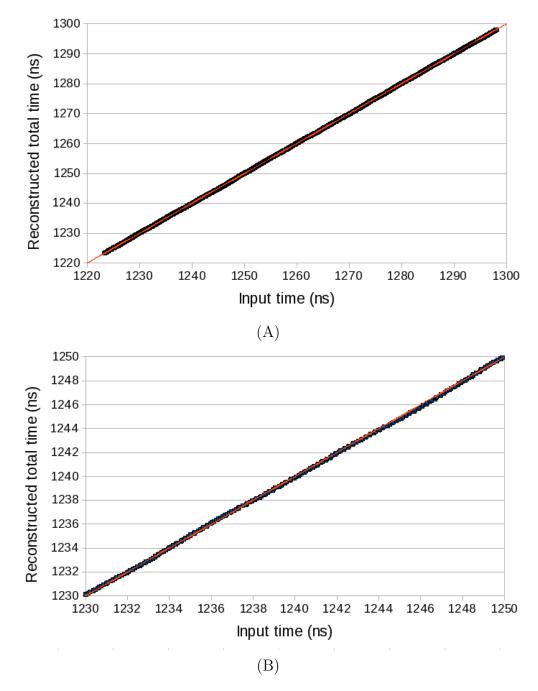

| 4.46 | (A) Total output times reconstructed on 6 clock cycles and (B) a           |       |

|      | zoom on the same measure                                                   | . 116 |

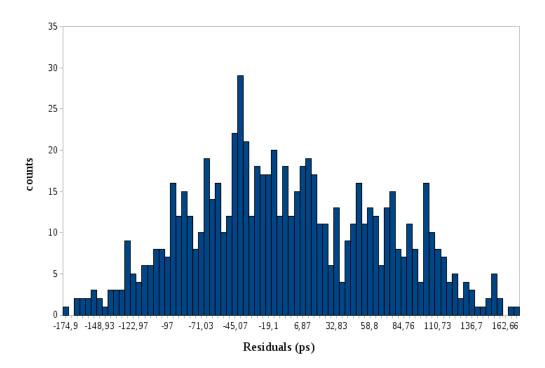

| 4.47 | (Histogram of the difference between the reconstructed and the ex-         |       |

|      | pected times                                                               | . 117 |

| 4.48 | Measure of the mismatch of the second TAC buffer with respect to           |       |

|      | the first                                                                  | . 117 |

| 4.49 | Measure of the mismatch of the third TAC buffer with respect to the        |       |

|      | first                                                                      | . 118 |

| 4.50 | Measure of the mismatch of the fourth TAC buffer with respect to           |       |

|      | the first                                                                  | . 118 |

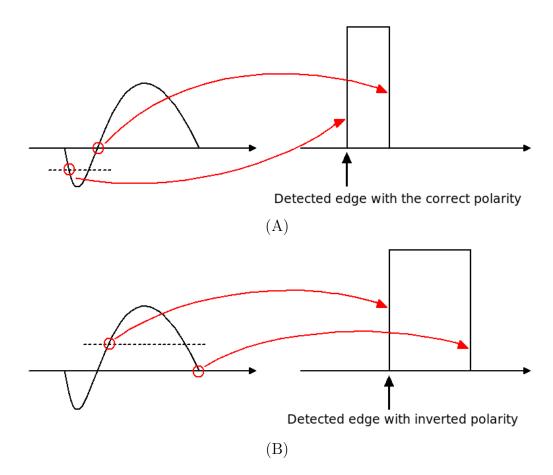

| 4.51 | (A) An issue in the asynchronous digital logic of the CFD causes the       |       |

|      | TDC to work on the wrong edge of the discriminator. (B) In this            |       |

|      | situation, better performance are obtained by changing the polarity        |       |

|      | bit and triggering on the leading edge of the bipolar signal overdrive     | . 119 |

| 4.52 | Time walk obtained in simulation by triggering on the leading edge         |       |

|      | of the CFD signal                                                          | . 120 |

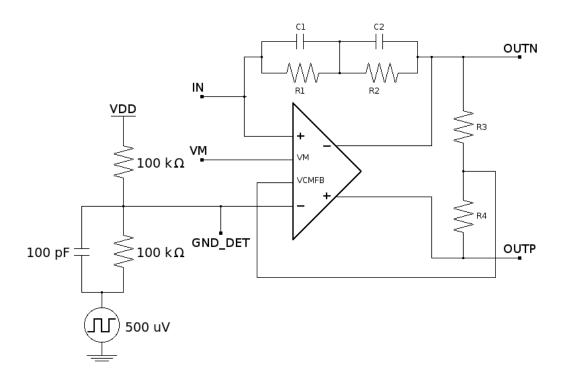

| 4.53 | Schematic of the injection circuit used to reproduce the clock inter-      |       |

|      | ference mechanism on GND_DET                                               | . 121 |

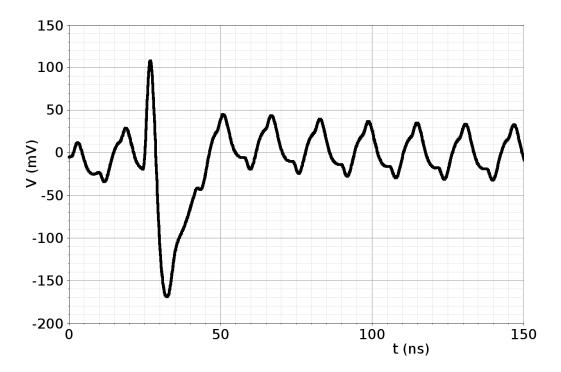

| 4.54 | Result of the simulations of the clock interference on the front-end       |       |

|      | with the 500 $\mu$ V noise on the reference ground at 62.5 MHz $\ldots$    | . 121 |

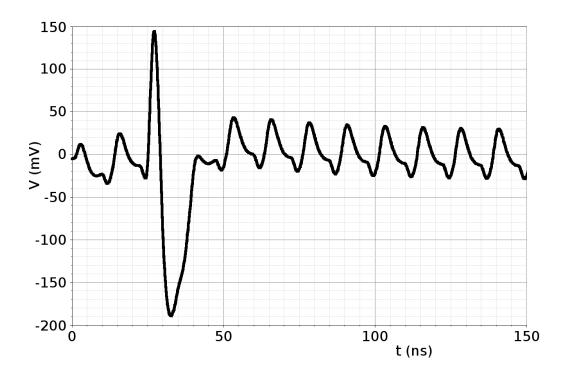

| 4.55 | Result of the simulations of the clock interference on the front-end       |       |

|      | with the 500 $\mu$ V noise on the reference ground at 80 MHz $\ldots$      | . 122 |

| 4.56 | Result of the simulations of the clock interference on the front-end       |       |

|      | with the 500 $\mu$ V noise on the reference ground at 160 MHz              | . 122 |

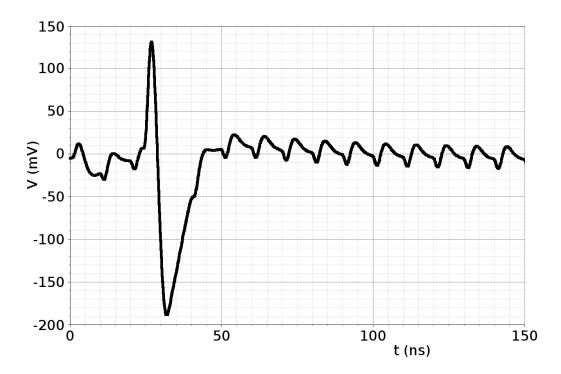

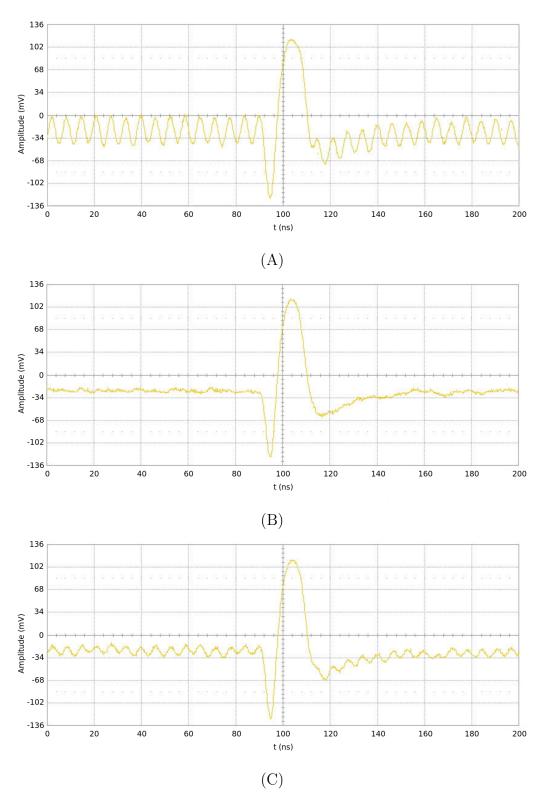

| 4.57 | Oscilloscope screenshots of the CFD output from the test pixel for a       |       |

|      | 3.5 fC input charge and for different values of clock frequency. Wave-     |       |

|      | forms (A), (B) and (C) have been obtained with a clock frequency of        |       |

|      | 80 MHz, 128 MHz and 160 MHz respectively                                   | . 123 |

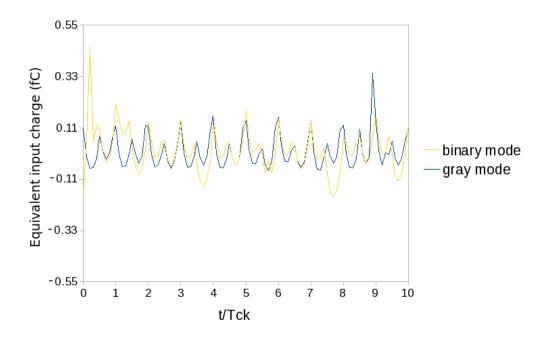

| 4.58 | Measurement of the baseline noise at 80 MHz from a pixel in the            |       |

|      | matrix with the counter in gray and in binary modes                        | . 124 |

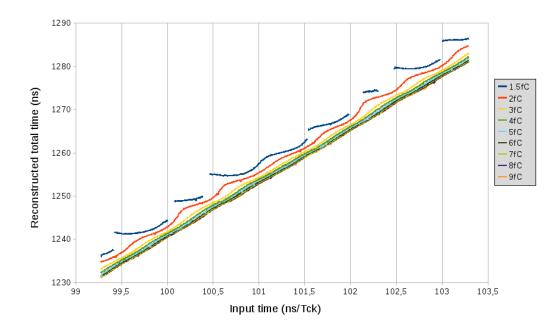

| 4.59 | Reconstruction of the total output times from a pixel of the matrix        |       |

|      | for different values of input charge before the PCB optimization $\ldots$  | . 125 |

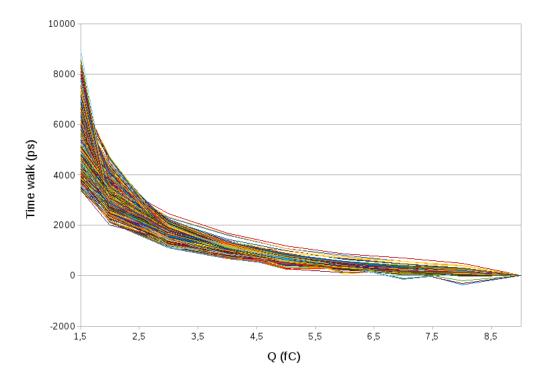

| 4.60 | Time walk curves measured from a pixel in the matrix obtained for different values of <i>Test Pulse</i> delay before the PCB optimization | 10   | 25  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|------|-----|

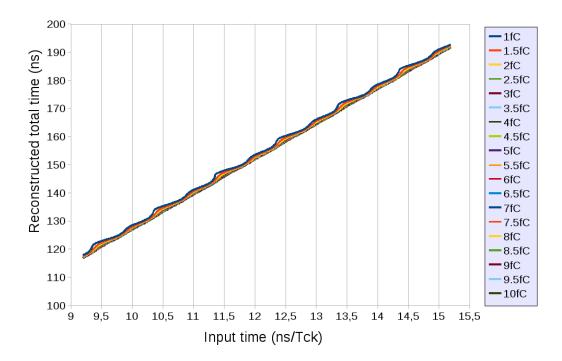

| 4 61 | Reconstruction of the total output times from a pixel of the matrix                                                                       | • 12 | 20  |

| 4.01 | for different values of input charge after the PCB optimization                                                                           | 19   | 26  |

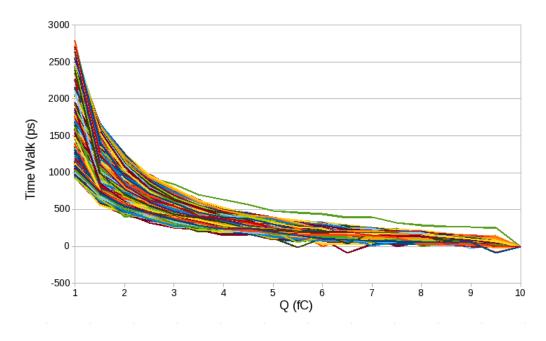

| 4 62 | Time walk curves measured from a pixel in the matrix obtained for                                                                         | • 14 | 20  |

| 4.02 | different values of <i>Test Pulse</i> delay after the PCB optimization                                                                    | 19   | 26  |

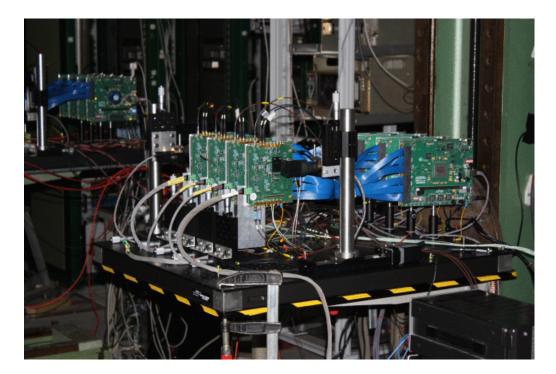

| 1 63 | Test bench of the beam test at CERN PS                                                                                                    |      |     |

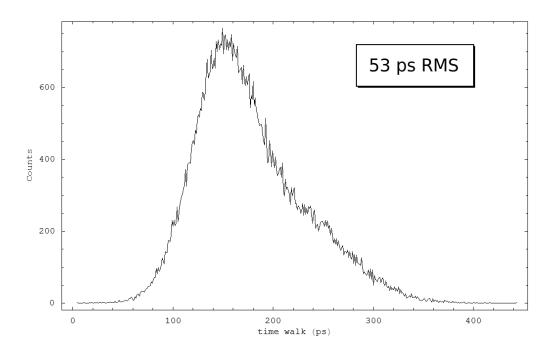

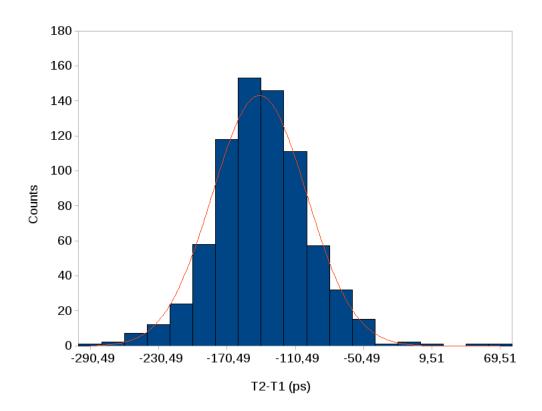

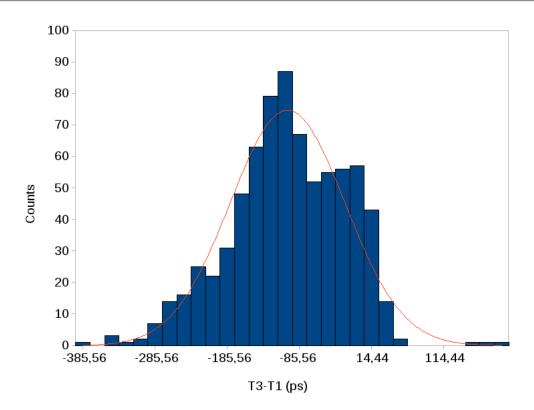

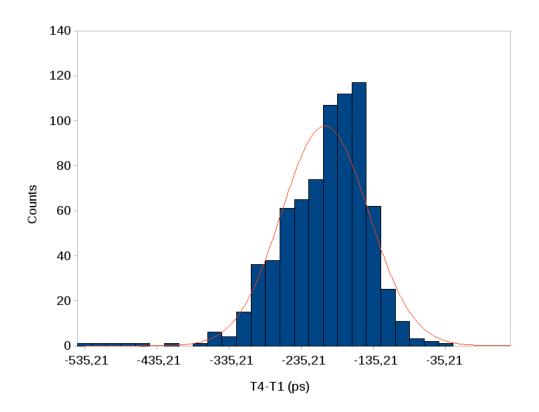

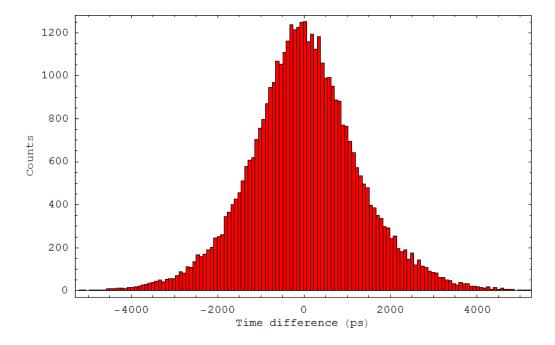

|      | Time difference distribution of 43041 coincident events on two boards                                                                     | • 12 | - 1 |

| 4.04 | measured at the beam test                                                                                                                 | 10   | 7   |

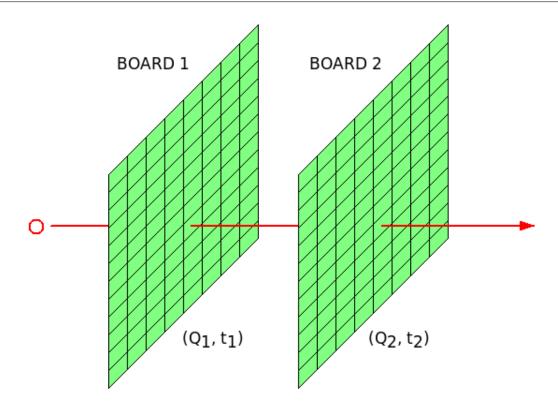

| 4 65 | Principle of the Montecarlo simulation performed to evaluate the ex-                                                                      | • 12 | - 1 |

| 4.00 | pected time resolution of the system                                                                                                      | 19   | 20  |

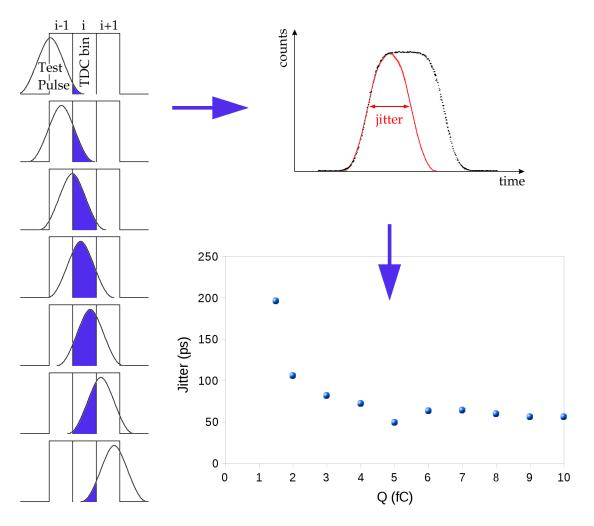

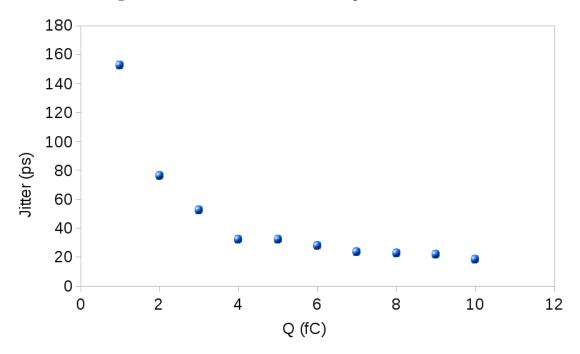

| 1 66 | Jitter measured from a pixel in the matrix                                                                                                |      |     |

|      | Jitter measured from the text pixel with a 80 MHz clock                                                                                   |      |     |

| 4.07 | Sitter measured from the text pixel with a 60 MHz clock                                                                                   | • 12 | 29  |

| 5.1  | Signal shape variations due to border effects                                                                                             | . 13 | 31  |

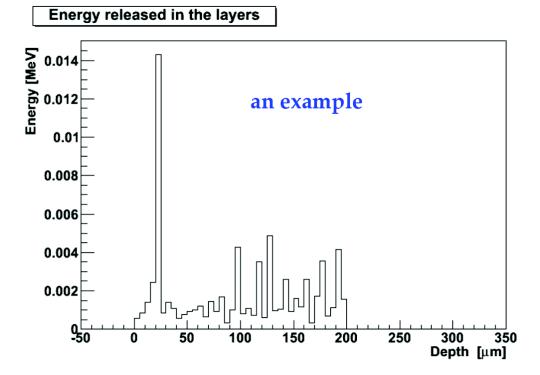

| 5.2  | Charge straggling along the sensor                                                                                                        |      |     |

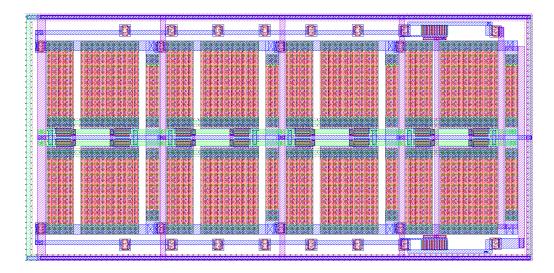

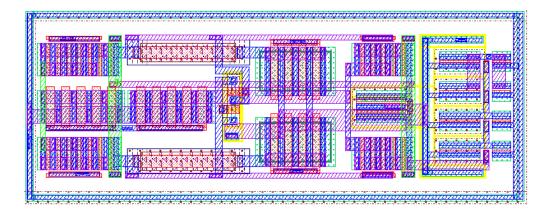

| 5.3  | Layout of the optimized CFD                                                                                                               | . 13 | 33  |

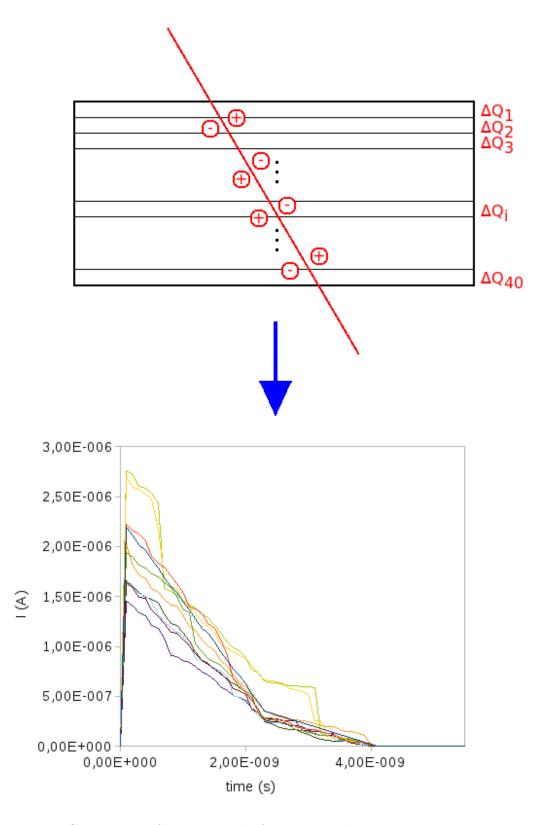

| 5.4  | Generation of input signals for Montecarlo simulation. The sensor                                                                         |      |     |

|      | has been divided in 40 slices. The resulting current pulses differ                                                                        |      |     |

|      | for amplitude and shape due to statistical fluctuations in the charge                                                                     |      |     |

|      | release process                                                                                                                           | . 13 | 34  |

| 5.5  | Schematic of the first stage of the preamplifier                                                                                          | . 13 | 35  |

| 5.6  | Replica circuit of the first preamplifier stage                                                                                           | . 13 | 36  |

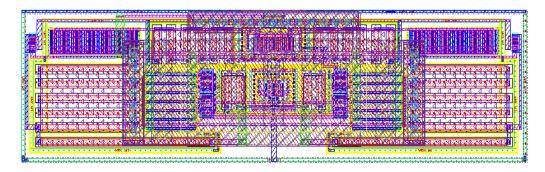

| 5.7  | Layout of the first stage of the preamplifier with the replica circuit .                                                                  | . 13 | 37  |

| 5.8  | Schematic of the op-amp of the second preamplifier stage                                                                                  | . 13 | 37  |

| 5.9  | Block diagram of the second stage of the preamplifier                                                                                     | . 13 | 38  |

| 5.10 | Layout of the second stage of the preamplifier                                                                                            |      |     |

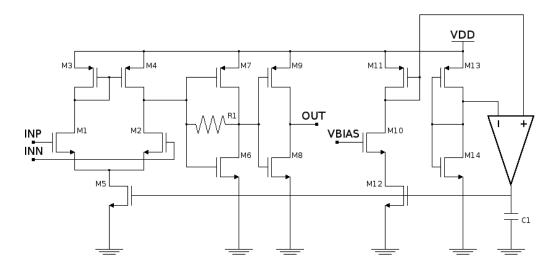

| 5.11 | Optimized CFD amplifier output stage                                                                                                      | . 13 | 39  |

| 5.12 | Layout of the CFD amplifier output stage with dynamic offset com-                                                                         |      |     |

|      | pensation circuit                                                                                                                         | . 14 | 10  |

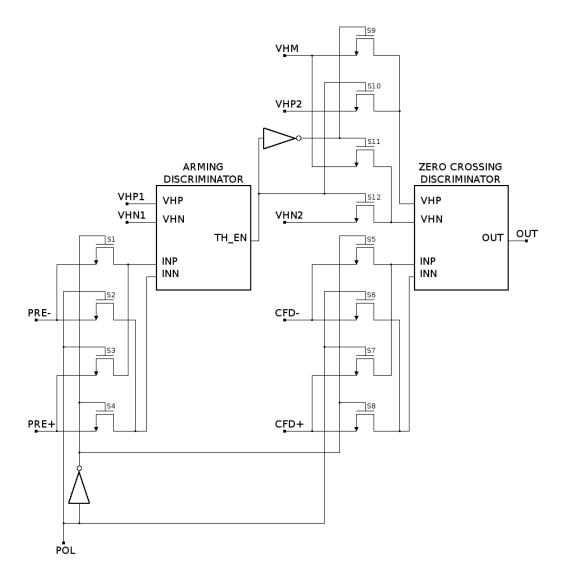

| 5.13 | Schematic of the discriminator used both for the arming and for the                                                                       |      |     |

|      | zero crossing                                                                                                                             | . 14 | 11  |

| 5.14 | polarity selection in the discriminator system                                                                                            | . 14 | 12  |

|      | Layout of the discriminator                                                                                                               |      |     |

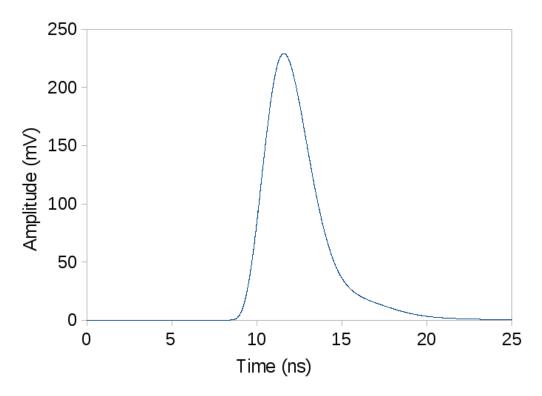

| 5.16 | Output of the preamplifier for 1 MIP                                                                                                      | . 14 | 13  |

| 5.17 | Linearity of the preamplifier                                                                                                             | . 14 | 14  |

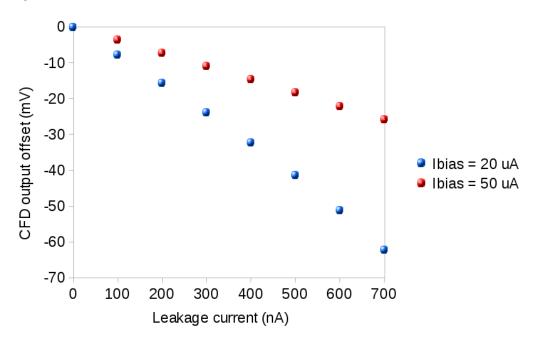

| 5.18 | Offset at the input of the zero crossing discriminator for leakage cur-                                                                   |      |     |

|      | rents up to 700 nA                                                                                                                        |      |     |

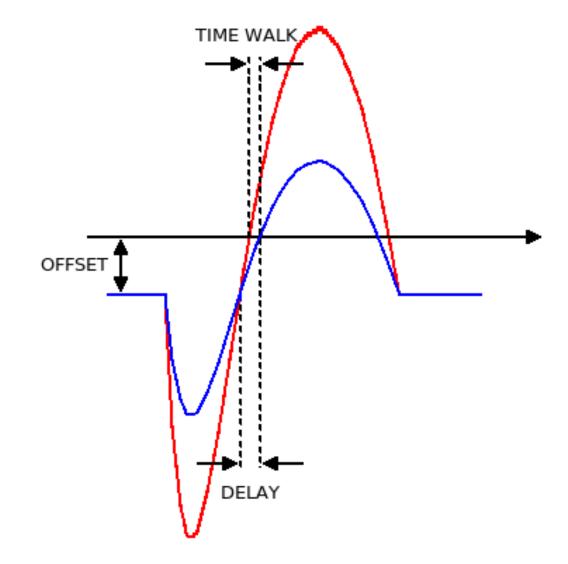

| 5.19 | Additional time walk introduced by offsets                                                                                                | . 14 | 16  |

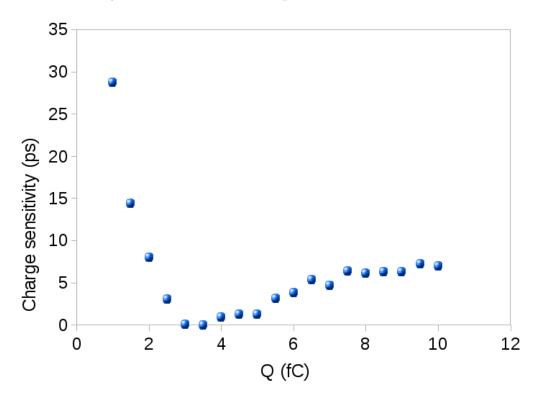

| 5.20 | Charge sensitivity of the discriminator                                                                                                   | . 14 | 17  |

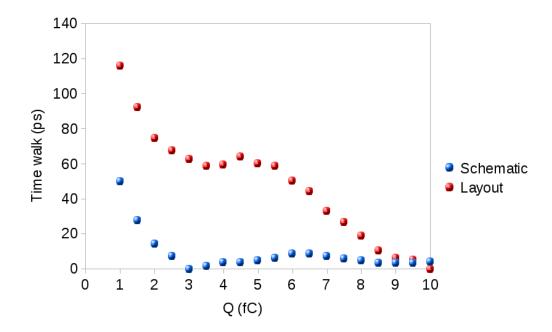

| 5.21 | Time walk of the full analog chain obtained by both schematic and                                                                         |      |     |

|      | layout simulations in typical mean                                                                                                        | . 14 | 18  |

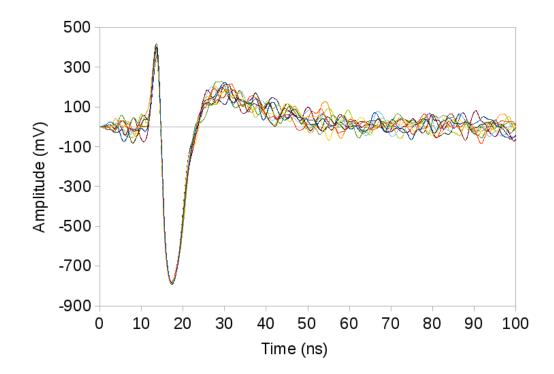

| 5.22 | CFD output for 2.4 fC input charge obtained with a transient noise                                                                        |      |     |

|      | analysis                                                                                                                                  | . 14 | 19  |

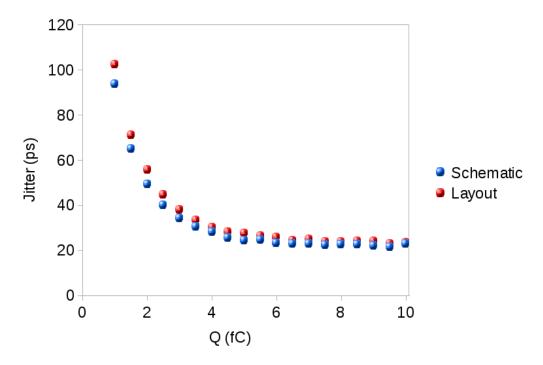

| 5.23 | Jitter of the new front-end design obtained by schematic and layout                                                                       |      |     |

|      | simulations in typical mean                                                                                                               | . 14 | 19  |

### LIST OF FIGURES

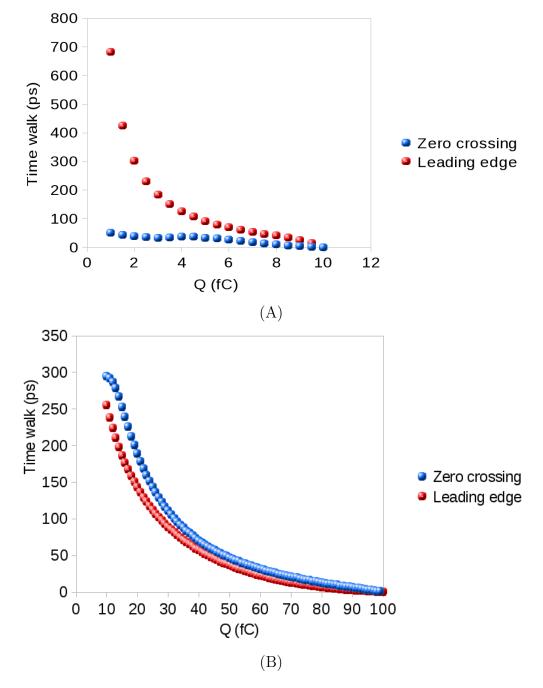

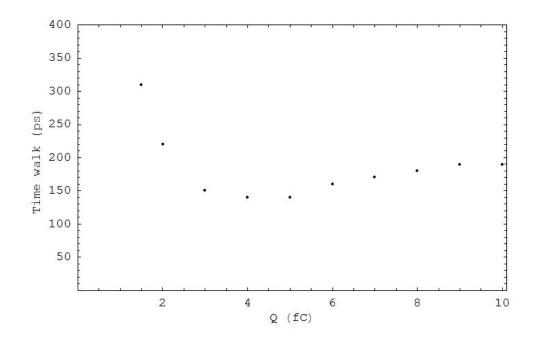

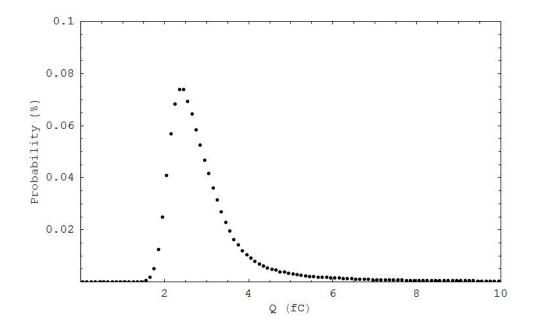

| 5.24 | Time walk of the zero crossing and of the leading edge discriminators                                                                                                                                                                        |     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | in the dynamic range (A) from 1f C to 10 fC and (B) from 10 fC to                                                                                                                                                                            |     |

|      | 100 fC                                                                                                                                                                                                                                       | 152 |

| 5.25 | Output of the ZC discriminator                                                                                                                                                                                                               | 153 |

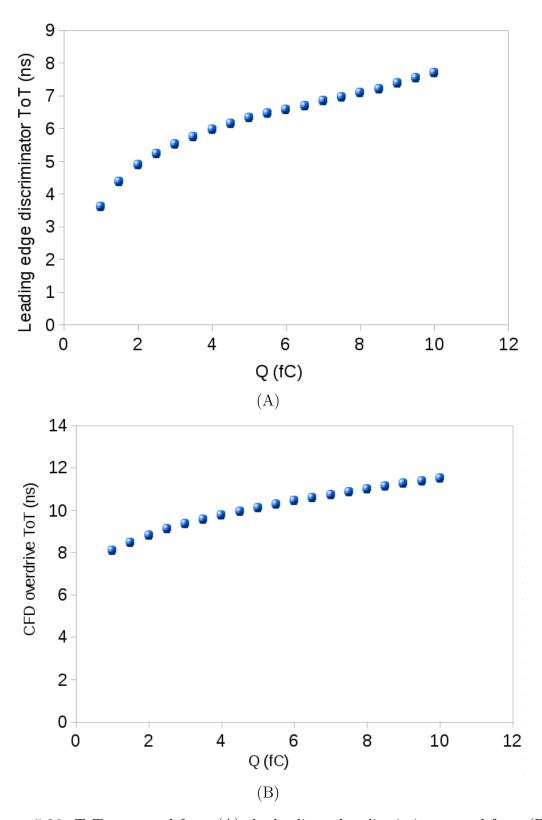

|      | ToT measured from (A) the leading edge discriminator and from (B)                                                                                                                                                                            |     |

|      | the ZC discriminator                                                                                                                                                                                                                         | 154 |

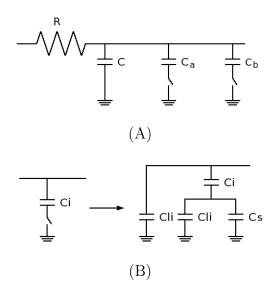

| B.1  | (A) The delay of the CFD is programmable to front the variation of their value with the process. (B) The switches, when open, have a parasitic capacitance $C_s$ which couples with the parasitic plate capacitance $C_l$ of $C_1$ and $C_2$ | 165 |

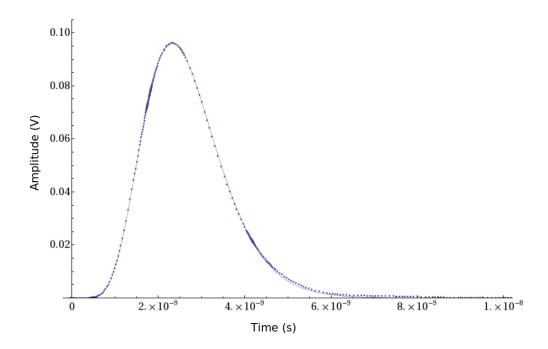

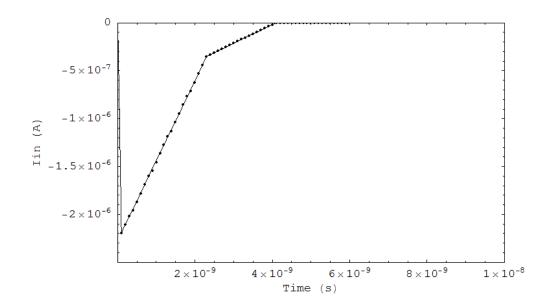

| C.1  | Fit of the output of the preamplifier when stimulated with a delta                                                                                                                                                                           |     |

|      | signal                                                                                                                                                                                                                                       | 168 |

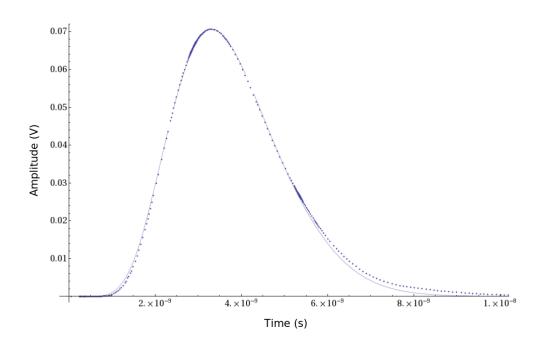

| C.2  | Sensor triangular typical signal                                                                                                                                                                                                             | 168 |

| C.3  | Fit of the output of the preamplifier when stimulated with a sensor                                                                                                                                                                          |     |

|      | like triangular signal                                                                                                                                                                                                                       | 169 |

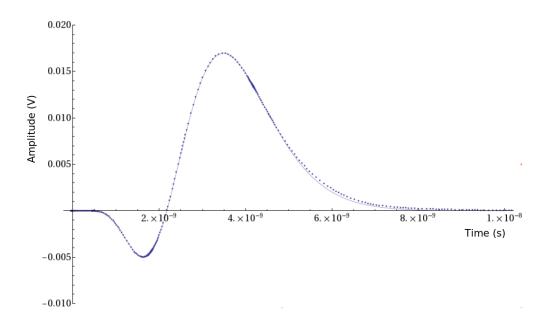

| C.4  | Fit of the output of the CFD when stimulated with a delta signal                                                                                                                                                                             | 170 |

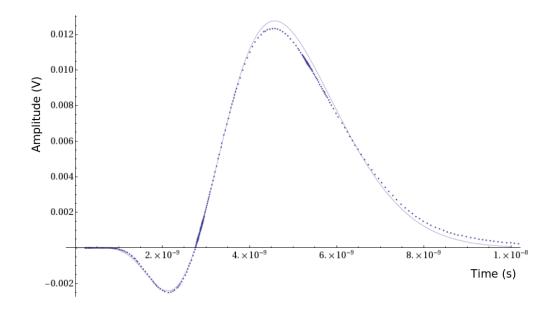

| C.5  | Fit of the output of the CFD when stimulated with a sensor like                                                                                                                                                                              |     |

|      | triangular signal                                                                                                                                                                                                                            | 170 |

## List of Tables

| $\begin{array}{c} 1.1 \\ 1.2 \end{array}$ | Values of $\epsilon$ for different materials and at different temperatures<br>Intrinsic detector resolution for Si and Ge detectors at 77 K for dif- | 25   |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|                                           | ferent energies                                                                                                                                      |      |

| 1.3                                       | Form factors for different filter shaper                                                                                                             |      |

| 1.4                                       | Jitter of the three configurations                                                                                                                   | 35   |

| 1.5                                       | Value of the RC time constants used in simulation for different filter<br>orders. The values have been calculated in order to have the same          |      |

|                                           | delay in all situations                                                                                                                              | 38   |

| 2.1                                       | Some of the most probable $\mathrm{K}^+$ decay modes and rejection criteria $~.~.$                                                                   | 42   |

| 2.1<br>2.2                                | GTK components material budgets                                                                                                                      |      |

| 2.2<br>2.3                                | GTK detector requirements                                                                                                                            |      |

| 2.0                                       |                                                                                                                                                      | 91   |

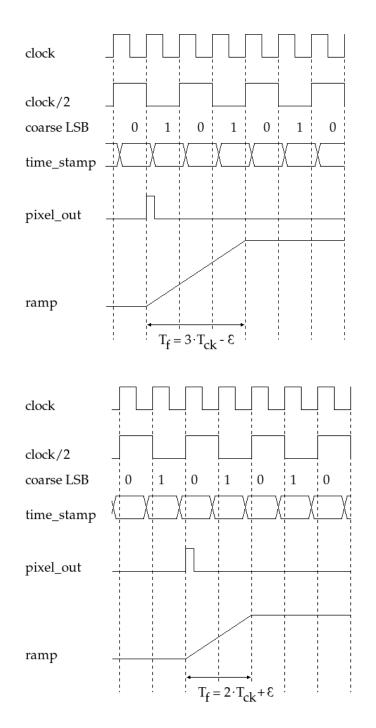

| 3.1                                       | Total time reconstruction equations                                                                                                                  | 60   |

| 3.2                                       | Error conditions in the particular configuration in which the coarse                                                                                 |      |

|                                           | counter and the half clock are in counter phase                                                                                                      | 60   |

| 3.3                                       | Time reconstruction including error correction in the configuration in                                                                               |      |

|                                           | which the coarse counter and the half clock are in counter phase                                                                                     | 63   |

| 3.4                                       | Time reconstruction including error correction in the configuration in                                                                               |      |

|                                           | which the coarse counter and the half clock are in phase                                                                                             | 63   |

| 3.5                                       | VHDL simulations results and theoretical predictions for 3-level multi-                                                                              |      |

|                                           | buffer FIFO                                                                                                                                          | 65   |

| 3.6                                       | VHDL simulations results and theoretical predictions for 4-level multi-                                                                              |      |

|                                           | buffer FIFO                                                                                                                                          | 66   |

| 4 1                                       |                                                                                                                                                      | 70   |

| $4.1 \\ 4.2$                              | Power consumption of all the block in the pixel cell                                                                                                 |      |

| 4.2<br>4.3                                | Parameters of each channel of the prototype chip                                                                                                     |      |

| 4.3<br>4.4                                | Summary of the electrical test results from the three boards Values of the passive components of the CFD filter                                      |      |

| 4.4<br>4.5                                | Possible TDC configurations                                                                                                                          |      |

| 4.5<br>4.6                                | Dissipation of the analog and digital sections of the prototype with                                                                                 | 95   |

| 4.0                                       |                                                                                                                                                      | 95   |

| 4.7                                       | 1.2 V power supply                                                                                                                                   | 90   |

| 4.1                                       | the tested boards after threshold equalization                                                                                                       | 101  |

| 4.8                                       | Avarage value of the ENC and corresponding SNR at 1fC for the                                                                                        | 101  |

| <b>1.</b> 0                               | tested boards after threshold equalization                                                                                                           | 107  |

| 4.9                                       | TAC buffers mismatch with respect to the first one measured at 80                                                                                    | 101  |

| т.Ј                                       | MHz                                                                                                                                                  | 11/  |

|                                           | 1111122                                                                                                                                              | TT.4 |

| 5.1 | Values of the passive components of the CFD filter optimized for       |

|-----|------------------------------------------------------------------------|

|     | signal shape rejection                                                 |

| 5.2 | Main contributors to total noise                                       |

| 5.3 | Simulation results of shape correcting CFD design                      |

| 5.4 | Simulation results of the overall time resolution including jitter due |

|     | to noise and signal shape variations and amplitude time walk 150       |

| 5.5 | Characteristics of the new front-end design                            |

|     |                                                                        |

## Introduction