# **TOFPET ASIC Characterization Results**

Manuel Dionísio Rolo, Ricardo Bugalho, Angelo Rivetti, Joao Varela, Rui Silva, Jose C Silva, Richard Wheadon, Carlos Gaston, Marco Mignone, Gianni Mazza, Fernando Goncalves

LIP - Laboratorio de Instrumentacao e Fisica Experimental de Particulas INFN - Istituto Nazionale di Fisica Nucleare sez. Torino

"The research leading to these results has received funding from the European Union Seventh Framework Programme (FP7/ 2007-2013) under Grant Agreement n°256984."

Workshop on Real time, self triggered front end electronics for multichannel detectors INFN Torino 27-28 November 2013

2 Differential vs. Single-ended

### 3 Characterization Results (update October 2013)

- Test Setup

- Electrical Characterization Results

- Tests with MPPCs

- Tests with crystals

# Outline

## Introduction

2 Differential vs. Single-ended

### Characterization Results (update October 2013)

- Test Setup

- Electrical Characterization Results

- Tests with MPPCs

- Tests with crystals

### Outlook

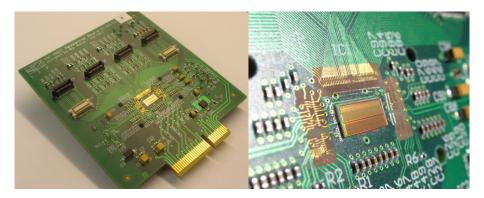

- one-shot submission (prototype, system chip) with CERN engineering run (June 2012)

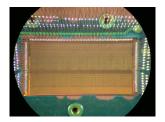

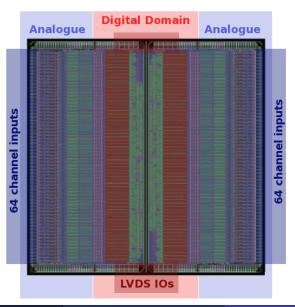

- 64-channel ASIC

- CMOS 130 nm

- 17x17mm BGA package for 128 SiP

- chips received February 2013

- 2 independent test setups (Torino, Lisboa)

- setups for test of packaged and bare dice

# 128-channel System-in-a-Package

M. D. Rolo (LIP, Univ of Turin)

**TOFPET ASIC Characterization Results**

- Design of a low power SiPM readout ASIC for Time of Flight applications

- integrates signal conditioning and discrimination circuitry and high-performance TDCs for each of 64 independent channels

- targets 25 ps r.m.s. intrinsic resolution and features fully digital output

- TOFPET ASIC developed in the framework of the **FP7 project EndoTOFPET-US**

- PET time-of-flight detector plate ( 4000 channels)

- MPPC (16-channel arrays, 3x3 mm2) and LYSO crystals

- Coincidence time resolution (CTR) 200 ps (FWHM)

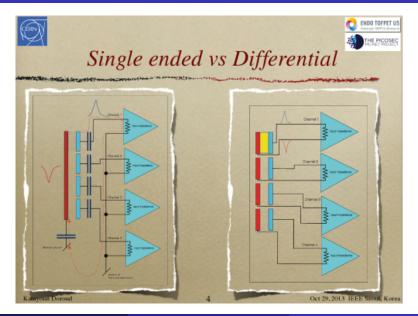

• The TOFPET ASIC features single-ended inputs  $\hookrightarrow$  Is such a chip suitable for Fast Timing Applications?

### Introduction

### 2 Differential vs. Single-ended

### Characterization Results (update October 2013)

- Test Setup

- Electrical Characterization Results

- Tests with MPPCs

- Tests with crystals

### Outlook

# Differential vs. Single-Ended readout

# Differential vs. Single-Ended readout

Katayoun Doroud M. D. Rolo (LIP, Univ of Turin) Oct 29, 2013 IEEE Seoul, Korea

- less sensitive to ground bounce, board-to-board (MPPC, ASIC) ground disturbances, crossing power boundaries

- In principle, no signal return through ground.

- This holds true if:

- current flows in a closed loop and if the differential sum is 0 everywhere in the loop

- $\hookrightarrow$  Otherwise, current does flow to ground and ground caring is needed!

- Severe routing constraints: symmetry of pair signalling is crucial

- same length, to avoid current return to ground

- same separation, to keep differential impedance constant

- The large signal of the SiPM does induce coupling into neighbouring traces or planes

- inductive or capacitive, even if differential impedance is low

- use of a plane under differential lines?

- reduces self-inductance

- hosts these induced loop currents

- Excess off-chip passive components (AC coupling)

Chip pad number doubled

- less sensitive to ground bounce, board-to-board (MPPC, ASIC) ground disturbances, crossing power boundaries

- In principle, no signal return through ground.

- This holds true if:

- current flows in a closed loop and if the differential sum is 0 everywhere in the loop

- $\,\hookrightarrow\,$  Otherwise, current does flow to ground and ground caring is needed!

- Severe routing constraints: symmetry of pair signalling is crucial

same length, to avoid current return to ground

- same separation, to keep differential impedance constant

- The large signal of the SiPM does induce coupling into neighbouring traces or planes

- inductive or capacitive, even if differential impedance is low

- use of a plane under differential lines?

- reduces self-inductance

- hosts these induced loop currents

- Excess off-chip passive components (AC coupling)

Chip pad number doubled

- less sensitive to ground bounce, board-to-board (MPPC, ASIC) ground disturbances, crossing power boundaries

- In principle, no signal return through ground.

- This holds true if:

- current flows in a closed loop and if the differential sum is 0 everywhere in the loop

- $\, \hookrightarrow \,$  Otherwise, current does flow to ground and ground caring is needed!

- Severe routing constraints: symmetry of pair signalling is crucial

- same length, to avoid current return to ground

- same separation, to keep differential impedance constant

- The large signal of the SiPM does induce coupling into neighbouring traces or planes

- inductive or capacitive, even if differential impedance is low

- use of a plane under differential lines?

- reduces self-inductance

- induced loop currents

- Excess off-chip passive components (AC coupling)Chip pad number doubled

- less sensitive to ground bounce, board-to-board (MPPC, ASIC) ground disturbances, crossing power boundaries

- In principle, no signal return through ground.

- This holds true if:

- current flows in a closed loop and if the differential sum is 0 everywhere in the loop

- $\,\hookrightarrow\,$  Otherwise, current does flow to ground and ground caring is needed!

- Severe routing constraints: symmetry of pair signalling is crucial

- same length, to avoid current return to ground

- same separation, to keep differential impedance constant

- The large signal of the SiPM does induce coupling into neighbouring traces or planes

- inductive or capacitive, even if differential impedance is low

- use of a plane under differential lines?

- reduces self-inductance

- hosts these induced loop currents

- Excess off-chip passive components (AC coupling)

- Chip pad number doubled

- less sensitive to ground bounce, board-to-board (MPPC, ASIC) ground disturbances, crossing power boundaries

- In principle, no signal return through ground.

- This holds true if:

- current flows in a closed loop and if the differential sum is 0 everywhere in the loop

- $\,\hookrightarrow\,$  Otherwise, current does flow to ground and ground caring is needed!

- Severe routing constraints: symmetry of pair signalling is crucial

- same length, to avoid current return to ground

- same separation, to keep differential impedance constant

- The large signal of the SiPM does induce coupling into neighbouring traces or planes

- inductive or capacitive, even if differential impedance is low

- use of a plane under differential lines?

- reduces self-inductance

- hosts these induced loop currents

- Excess off-chip passive components (AC coupling)

- Chip pad number doubled

- less sensitive to ground bounce, board-to-board (MPPC, ASIC) ground disturbances, crossing power boundaries

- In principle, no signal return through ground.

- This holds true if:

- current flows in a closed loop and if the differential sum is 0 everywhere in the loop

- $\,\hookrightarrow\,$  Otherwise, current does flow to ground and ground caring is needed!

- Severe routing constraints: symmetry of pair signalling is crucial

- same length, to avoid current return to ground

- same separation, to keep differential impedance constant

- The large signal of the SiPM does induce coupling into neighbouring traces or planes

- inductive or capacitive, even if differential impedance is low

- use of a plane under differential lines?

- reduces self-inductance

- hosts these induced loop currents

- Excess off-chip passive components (AC coupling)

- Chip pad number doubled

### • A flood of disadvantages...

- very susceptible to ground loops

- suspeptible to board-to-board ground disturbances

- signal return via common ground can cause electrical crosstalk

- ground bounce due to switching currents

### • But, all above can be minimized:

- with an appropriate grounding scheme

- if signal travels in a low noise surrounding and/or is properly shielded

### • Question of The Day:

→ For Fast Timing with large signal photosensors, isn't power system integrity (aka Grounding) the main issue, irrespective if we use a differential or a single-ended readout?

### • A flood of disadvantages...

- very susceptible to ground loops

- suspeptible to board-to-board ground disturbances

- signal return via common ground can cause electrical crosstalk

- ground bounce due to switching currents

- But, all above can be minimized:

- with an appropriate grounding scheme

- if signal travels in a low noise surrounding and/or is properly shielded

### • Question of The Day:

→ For Fast Timing with large signal photosensors, isn't power system integrity (aka Grounding) the main issue, irrespective if we use a differential or a single-ended readout?

### • A flood of disadvantages...

- very susceptible to ground loops

- suspeptible to board-to-board ground disturbances

- signal return via common ground can cause electrical crosstalk

- ground bounce due to switching currents

- But, all above can be minimized:

- with an appropriate grounding scheme

- if signal travels in a low noise surrounding and/or is properly shielded

- Question of The Day:

- → For Fast Timing with large signal photosensors, isn't power system integrity (aka Grounding) the main issue, irrespective if we use a differential or a single-ended readout?

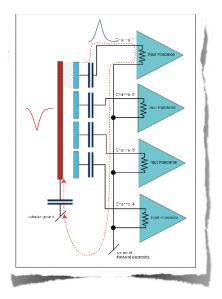

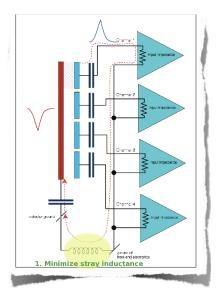

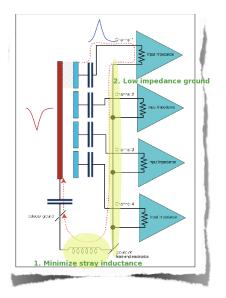

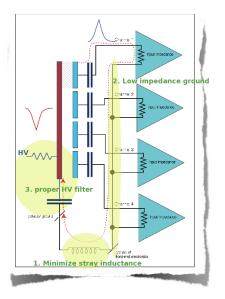

- minimize the stray inductance of the current return path

- care the ground of the ASIC

- design a proper HV biasing scheme

# • minimize the stray inductance of the current return path

- care the ground of the ASIC

- design a proper HV biasing scheme

- minimize the stray inductance of the current return path

- care the ground of the ASIC

- design a proper HV biasing scheme

- minimize the stray inductance of the current return path

- care the ground of the ASIC

- design a proper HV biasing scheme

### Introduction

### 2 Differential vs. Single-ended

### Characterization Results (update October 2013)

- Test Setup

- Electrical Characterization Results

- Tests with MPPCs

- Tests with crystals

### Outlook

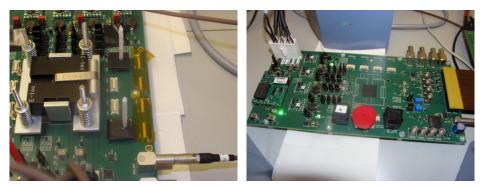

# Test Setups Packaged Dice 1&2

### First test boards with/without BGA socket

- Electrical characterization

- Coincidence tests: single crystal and matrices

- Severe power bouncing package, test board, setup

### Test board designed for and by the 4DMPET collaboration<sup>1</sup>

- Electrical characterization

- Tests with MPPCs (SPTR, MPTR)

- Coincidence tests

<sup>1</sup>Acknowledgement: Marco Mignone, Richard Wheadon

M. D. Rolo (LIP, Univ of Turin)

TOFPET ASIC Characterization Results

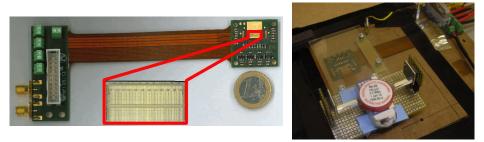

# Test Setup Bare Die 2

### New board designed at LIP - ready since October 2013

- Electrical characterization

- Tests with MPPCs (SPTR, MPTR)

- Coincidence tests

- bare die directly bonded on the test board

- <u>setup includes</u> power supplies, low jitter reference clock source, FPGA interface and bias voltage for the SiPM arrays

- latest tests with MPPC S12642-0404PB-50 (TSV MPPC array)

- FPGA handles:

- ASIC configuration and data reception

- generates a test pulse which is delivered to the ASIC or to a pulsed laser driver for testing purposes

- TP: ajustable timing but synchronous to the reference clock

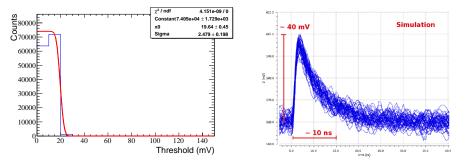

- number of events as function of threshold (both thresholds set to the same value)

- fit to a cumulative probability distribution function

- 2.5 mV r.m.s. (agrees to simulation results)

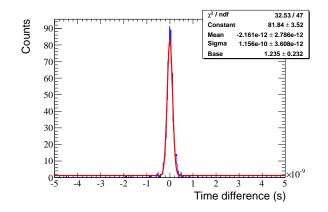

# **TDC** Quantization Error

- Step 1: TDC calibrated with a test pulse sweep across 50 ns (500 ps step, 10000 pulses p/ step)

- Step 2: Correct for TDC non-linearity

- **Step 3**: Trigger simultaneously two channels and measure time difference (removes common mode test pulse jitter)

• Distribution with 29 ps r.m.s., corresponds to a **per channel error of 21 ps r.m.s.**

### • Tests with Bare Die

- MPPC: TSV arrays (3x3 mm2)

- (for CTR only): 3.1x3.1x15mm<sup>2</sup>LYSO

- nominal: 160 MHz, DVDD=1v5

- PicoQuant Laser

- MPTR: LI=1.5, no optical attenuator ( $N_{ph} >> 1000$ )

- SPTR: LI=7.5, WITH optical attenuator  $(N_{ph} = 1)$

- Nominal test conditions:

- T = 18-20 C

- TP rate = 80 KHz

- $V_{thE}$  approx 500mV above  $V_{th,noise}$

- $V_{thT}$  approx  $10 \text{mV}^2$  above  $V_{th,noise}$

<sup>2</sup>for CRT with LYSO, nominal  $V_{thT}$  setting is to 100 mV above noise (corresponds to a threshold of 2-3 equivalent photoelectron charge)

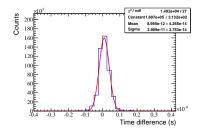

# Multi-Photon Time Resolution

• Laser: no optical attenuator ( $N_{ph} > 1000$ )

$\,\hookrightarrow\,$  32 ps r.m.s., includes jitter from the laser and the test pulse

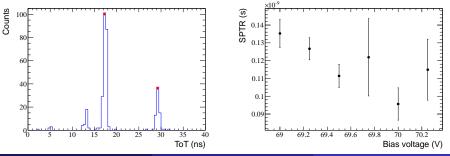

# Single-Photon Time Resolution

- Laser: w/ optical attenuator ( $N_{ph} = 1$ )

- both thresholds set to 0.5 p.e. level

- laser triggered at 80 kHz rate, known time in respect to the start-of-frame

- ToT distribution of events within 1 ns of the expected laser pulse time show the 1 photon and 2 photon peaks

- $\,\hookrightarrow\,$  110 ps r.m.s., after optimization of the HV

- Two MPPC S12642-0404PB-50 (TSV MPPC 16-channel matrices)biased and connected to the ASIC

- Only one pixel with a 3.1x3.1x15 mm3 LYSO crystal

- All channels set to a 2 p.e. charge (sweep 1-10 p.e.) equivalent threshold

- Geometrically neighbouring channels (avg 4-6) produce data due to optical crosstalk on epoxy

- Events selected within  $1\sigma$  of the photopeak

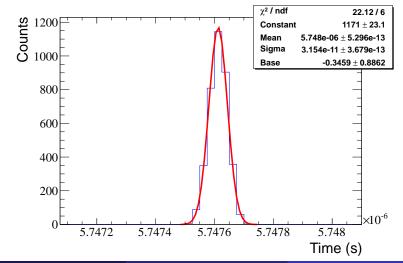

# Coincidence Time Resolution - preliminary

#### • CTR = 270 ps FWHM

- Result does not depend on the threshold setting other channels

- CTR value is higher than the extrapolation based on SPTR meas.

→ under investigation

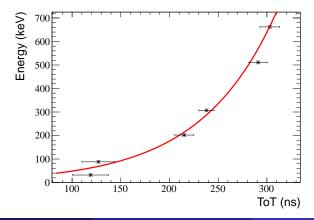

# Energy Calibration - preliminary

- ToT vs. Qin characteristic is non-linear

- Data aquired with <sup>22</sup>Na, <sup>176</sup>Lu, <sup>137</sup>Cs

- Fit to an exponential function to correct energy spectrum

- Preliminary energy resolution 17%

### Introduction

2 Differential vs. Single-ended

### Characterization Results (update October 2013)

- Test Setup

- Electrical Characterization Results

- Tests with MPPCs

- Tests with crystals

### 4 Outlook

- ASIC distributed to several groups for Medical Imaging and HEP

- offspring under way

- PASTA chip for Panda

- readout of strips

- Linear ToT

- TOFPET v2.0

- Targets time resolution better than 10 ps r.m.s.

- Rate per channel more than 1 MHz

- Linear ToT

- improved energy resolution

# EndoTOFPET-US FP7: Endoscopic PET and Ultrasound

# Thank you!

M. D. Rolo (LIP, Univ of Turin)

**TOFPET ASIC Characterization Results**