# High-speed CMOS integrated circuit design

### Outline

- Basic concepts

- Data properties

- Circuit noise

- Bandwidth

- BER

- Jitter

- FEC

- Circuit concepts

- Common-source amplifier

- Optimum current density

- Bandwidth extension

- Multistage amplifier

- Negative impedances

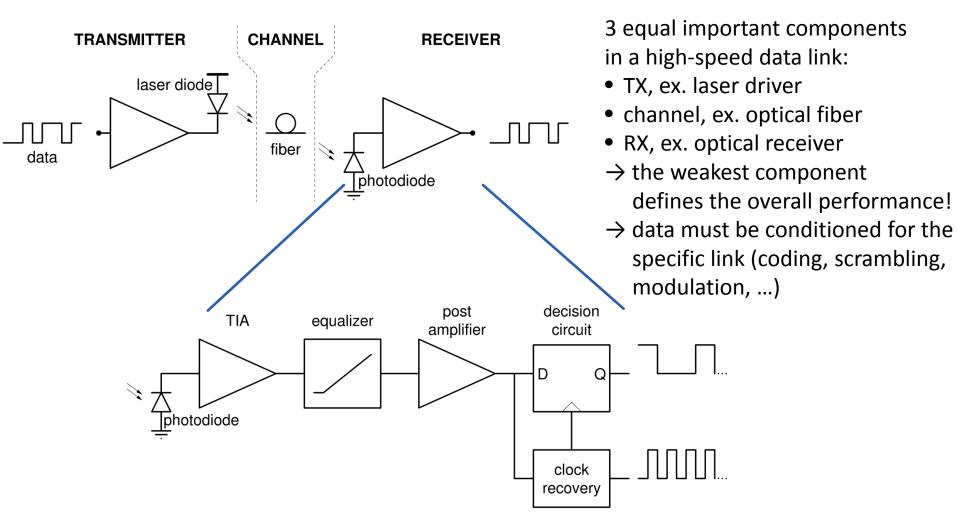

### High-speed (optical) data communication

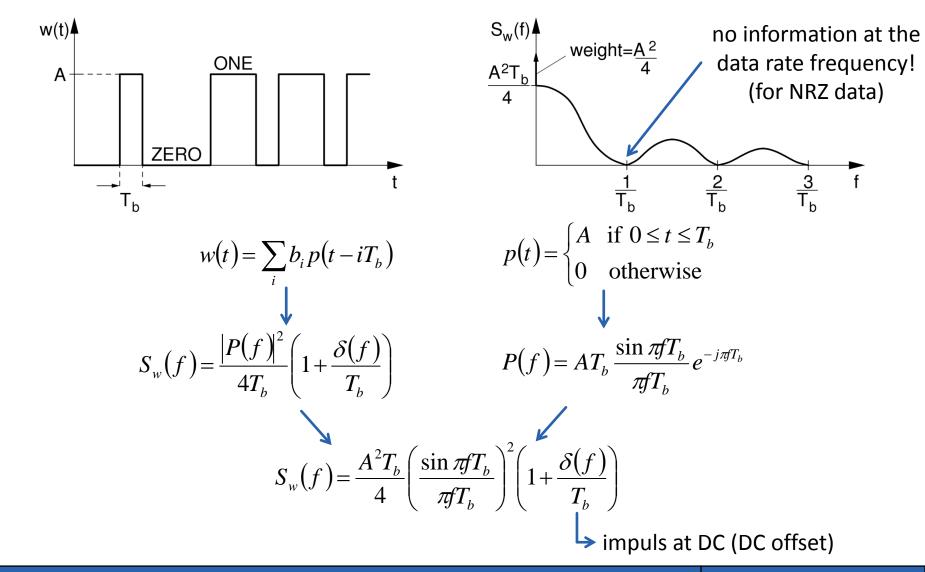

## Random digital data

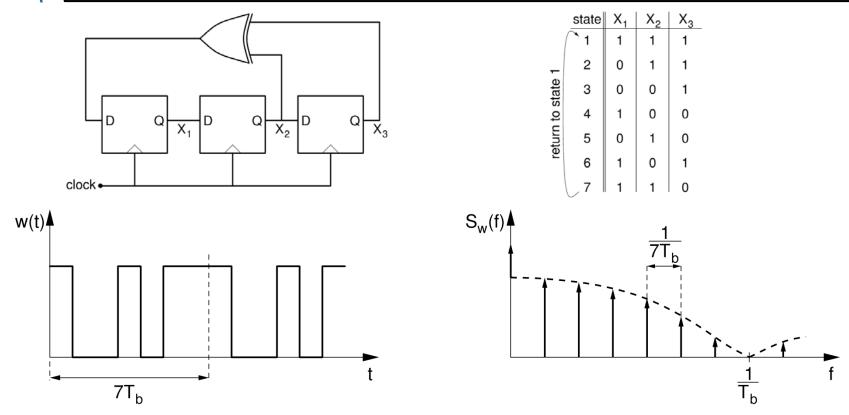

## Pseudo-random digital data

- same pattern is repeated; pattern length = 2<sup>n</sup>-1 (n = # memory elements)

- PRBS used frequently to test high-speed data links (n typically between 7 and 31)

- continuous spectrum of truly random data becomes line spectrum because of the repetition of the same pattern every 2<sup>n</sup>-1 bits

- distance between spectral lines inversely proportional to pattern length

# CERN

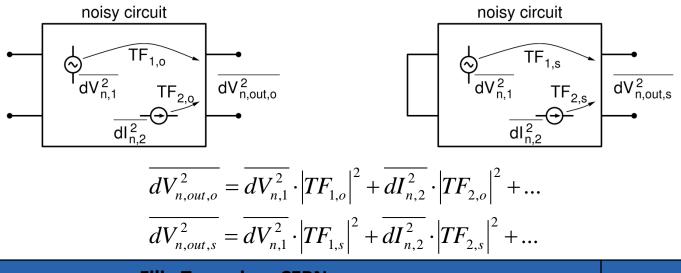

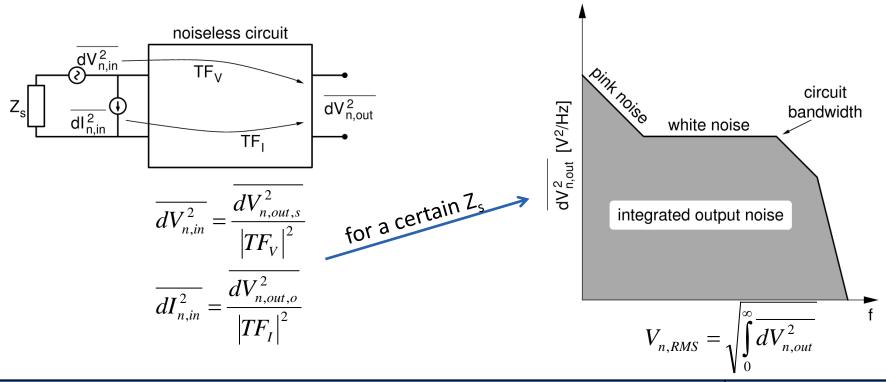

## Circuit noise (1)

• when working with noise, always use the **spectral noise densities**

$$\begin{bmatrix} \overline{dV_{n,R}^2} = 4kTR \cdot df + V_R^2 \frac{K_R R_{sq}}{A_R} \cdot \frac{df}{f} & \text{for resistors} \\ \overline{dV_{n,T}^2} = 4kTR_{eff} \cdot df + \frac{K_T}{WLC_{ox}^2} \cdot \frac{df}{f} & \text{for MOS transistors} \\ \overline{dI_{n,D}^2} = 2qI_D \cdot df + I_D \frac{K_D}{A_D} \cdot \frac{df}{f} & \text{for diodes} \end{bmatrix}$$

- every noise source in a circuit has its own transfer function towards the output

- output noise spectral density depends on the input impedance!

## Circuit noise (2)

- equivalent input noise is a purely mathematical quantity (can go infinitely high if the gain of the circuit goes to zero!)

- both a voltage and a current noise source are required to characterize the circuit noise

- for an open input ( $Z_s = \infty$ ), the output noise is only determined by the current source

- for a shorted input ( $Z_s = 0$ ), the output noise in only determined by the voltage source

- for a finite Z<sub>s</sub>, the output noise is determined by both the voltage and the current source

# CERN

## **Circuit noise and BER**

p(V)

p(V)∮

p(V|ZERO)=1

Ŷ,

p(V|ZERO)

V.

V<sub>n,RMS</sub>

p(V|ONE)=1

V<sub>h</sub>

p(V|ONE)

V(t)

V<sub>h</sub>

V(t)

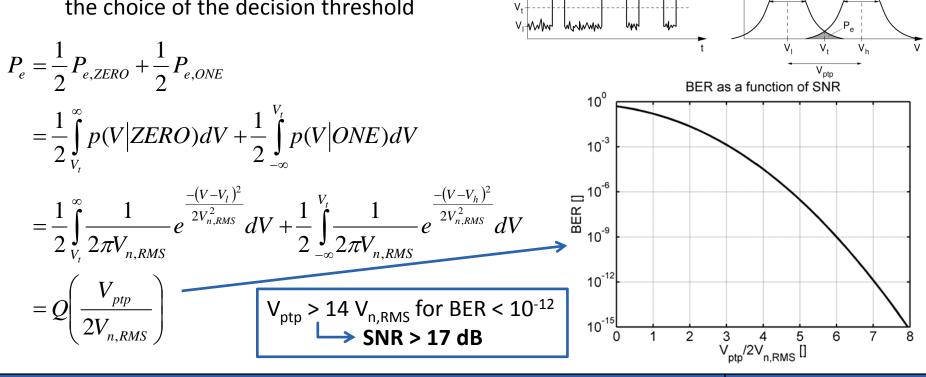

- without noise, there is no chance of making a wrong decision provided that the decision threshold is between the low and high signal values

- with noise, there is a chance of making an error which depends on the choice of the decision threshold

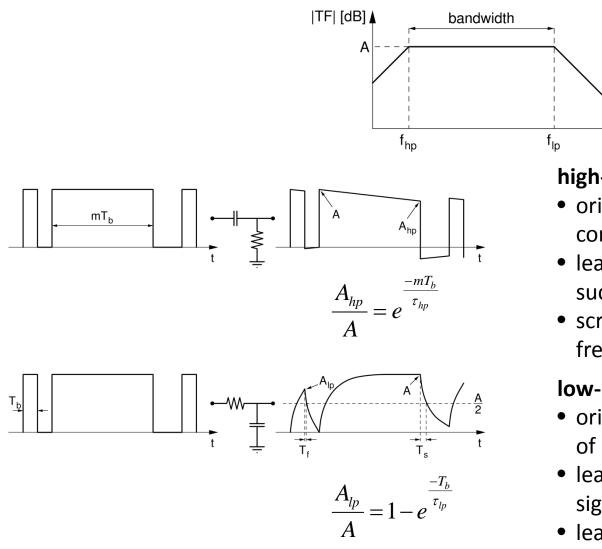

### Bandwidth

#### high-pass filtering

- originates from AC-coupling, offset compensation, ...

- leads to DC wander with a long succession of identical bits

- scrambling data to reduce the low frequency content

#### low-pass filtering

- originates from limited performance of circuits at high frequencies

- leads to incomplete settling of the signal within the bit interval = ISI

- leads to jitter

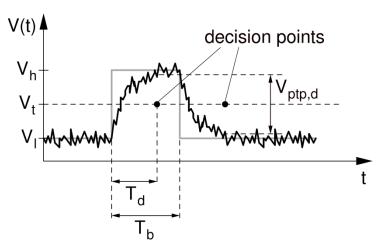

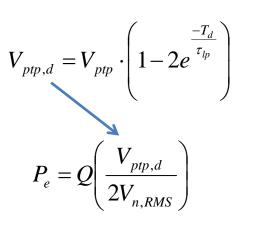

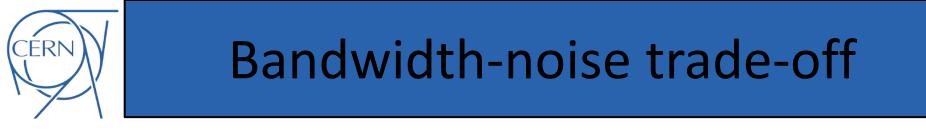

# Bandwidth, circuit noise and BER

finite receiver BW  $\rightarrow$  signal not settled at the decision point  $\rightarrow$  lower effective SNR

#### Example:

- bit rate = 1 Gbit/s (T<sub>b</sub> = 1 ns) and  $f_{lp}$  = 500 MHz ( $\tau_{lp}$  = 318 ps)  $\rightarrow V_{ptp,d}$  = 0.585 V<sub>ptp</sub> for a decision point in the middle of the bit interval

- $\rightarrow$  BER  $\approx$  1e-5 if V<sub>ptp</sub> = 14 V<sub>n,RMS</sub> (compared to 1e-12!)

#### **Question:**

Is it a good idea to postpone the decision point towards the end of the bit interval to profit from the better settling?

Sweet spot: BW is around 70 % of the bit rate (for example 700 MHz for 1 Gbit/s data)

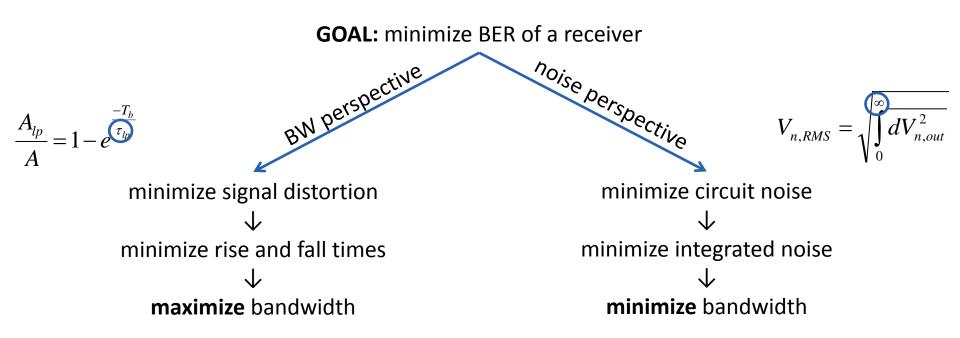

### Jitter

#### voltage axis

- noise leads to a finite BER

- BW limitation leads to ISI

#### time axis

- noise leads to random jitter

- BW limitation leads to deterministic jitter \_\_\_\_\_\_

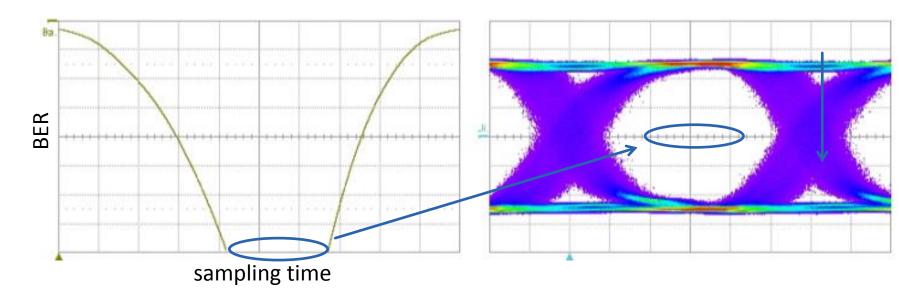

BER is determined bythe sampling time as well as the threshold voltage

ideal decision point is probably in the exact center of the eye opening

Filip Tavernier - CERN

### Jitter and BER

optimum sampling time range is usually very limited for the minimal BER  $\downarrow$ tight control of sampling time is critical  $\downarrow$ difficult due to static clock phase errors, jitter in the recovered clock, ...  $\downarrow$ ideal CDR would 'track' the jitter of the input data to always sample in the center of the eye

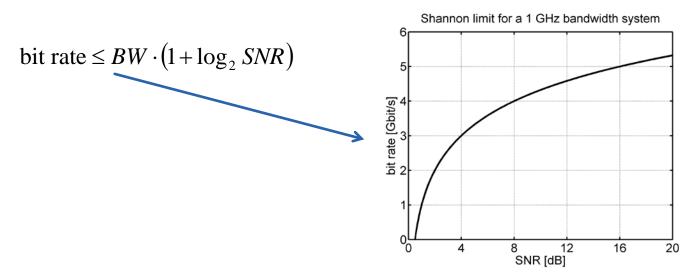

### Forward error correction

- for a BER of 1e-12, an SNR of at least 17 dB is needed, assuming no bandwidth limitation

- Shannon's channel capacity theorem states that: error-free transmission over a channel with additive white Gaussian noise is possible if

- with 17 dB SNR, error-free operation at 5 Gbit/s for a 1 GHz bandwidth!

- how? → forward error correction coding (FEC)

FEC = add redundancy bits in the TX to correct for transmission errors examples: add parity bits, Reed-Solomon code, ...

### Outline

- Basic concepts

- Data properties

- Circuit noise

- Bandwidth

- BER

- Jitter

- FEC

- Circuit concepts

- Common-source amplifier

- Optimum current density

- Bandwidth extension

- Multistage amplifier

- Negative impedances

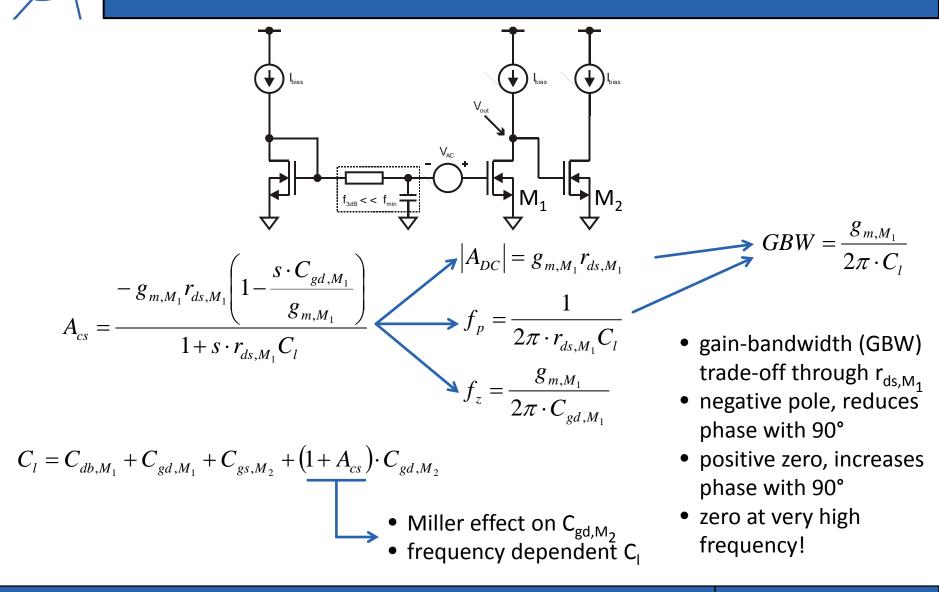

### **Common-source** amplifier

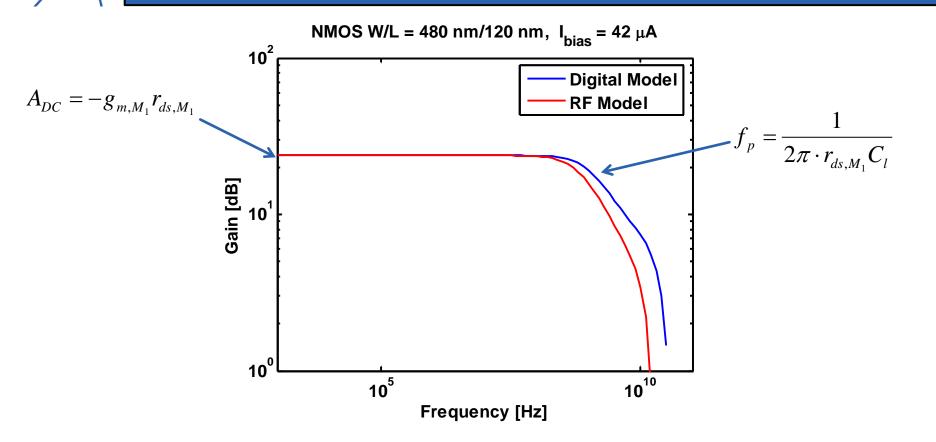

### Frequency response of CS amplifier

bandwidth depends strongly on parasitics!

$\rightarrow$  RF transistor model covers some of the layout parasitics

$\rightarrow$  extracted schematics include even more of them

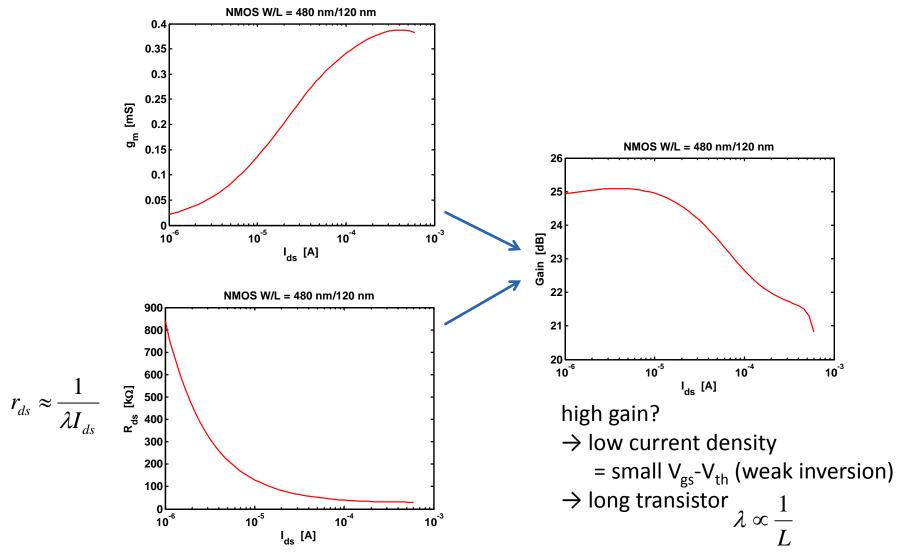

## Transistor biasing for gain

## Transistor biasing for bandwidth

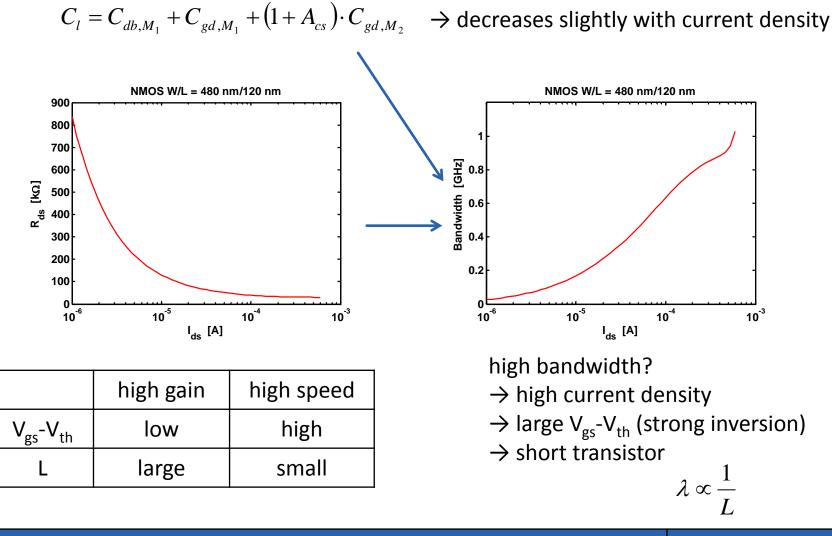

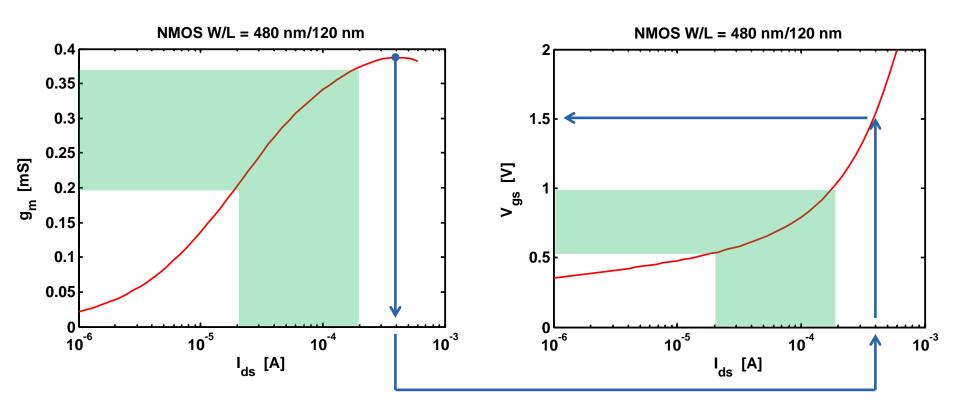

## Biasing for maximum g<sub>m</sub>?

- high-speed circuits?  $\rightarrow$  maximize  $g_m$

- maximum g<sub>m</sub> is obtained for a large current density and large overdrive voltage

- no signal headroom for the maximum  $g_m (V_{dd} = 1.5 V)$

- in practice: 0.5 V < V<sub>gs</sub> < 1 V  $\rightarrow$  70-80 % of maximum g<sub>m</sub>

- maximum bandwidth is obtained for a large current density and large overdrive voltage

- no signal headroom for the maximum bandwidth ( $V_{dd}$  = 1.5 V)

- in practice: 0.5 V < V\_{gs} < 1 V  $\rightarrow$  25-75 % of maximum bandwidth

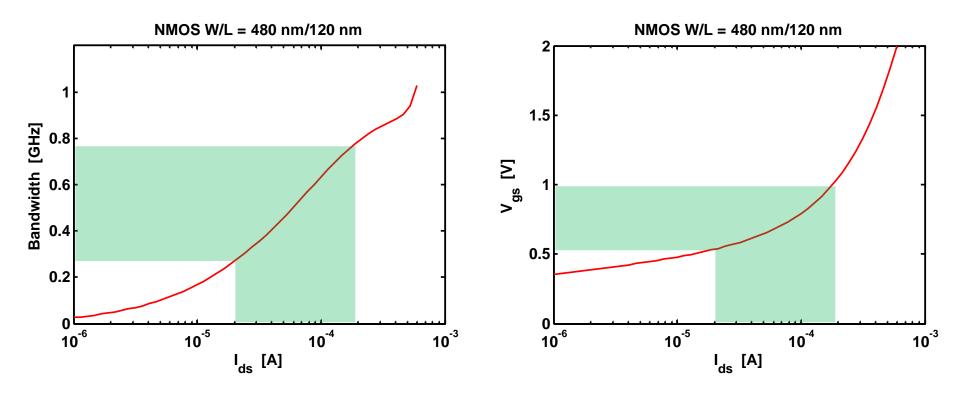

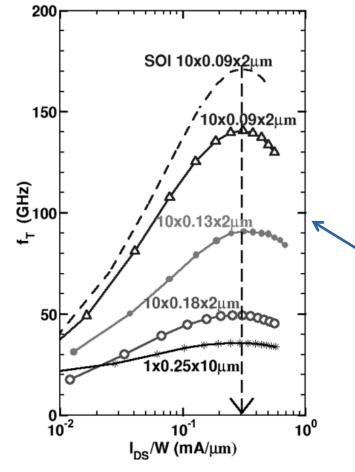

# Invariance of optimum current density (1)

<sup>(</sup>T. O. Dickson et al. - JSSC vol. 41, no. 8, p. 1830, August 2006)

• intrinsic speed of transistor  $\rightarrow f_t$

$$f_t = \frac{g_m}{2\pi \cdot C_{gs}}$$

• maximum  $f_t$  can be found at a current density of J =  $\pm$  0.3 mA/ $\mu$ m

$$J = \frac{I_{ds}}{W} [\text{mA}/\mu\text{m}]$$

- relatively broad optimum

- independent on foundry

- independent on technology node (due to constant field scaling)

- independent on transistor length

- valid for nMOS and pMOS transistors (for pMOS, the optimum is 0.15 mA/μm)

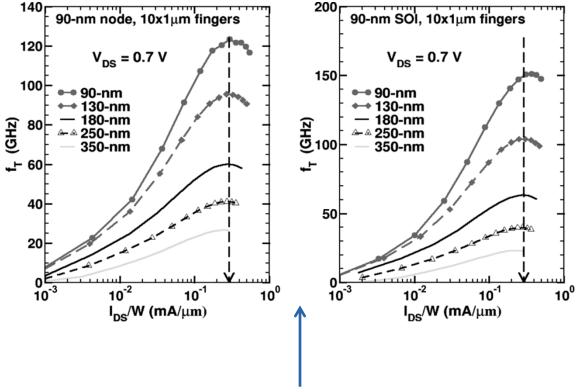

# Invariance of optimum current density (2)

optimum current density

- independent on transistor length

- identical for bulk or SOI processes

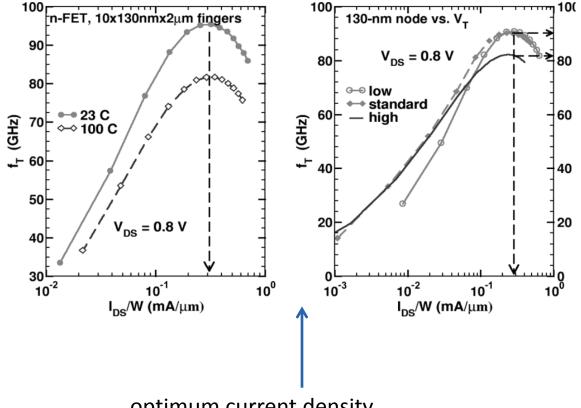

# Invariance of optimum current density (3)

optimum current density

- independent on temperature

- Independent on threshold voltage

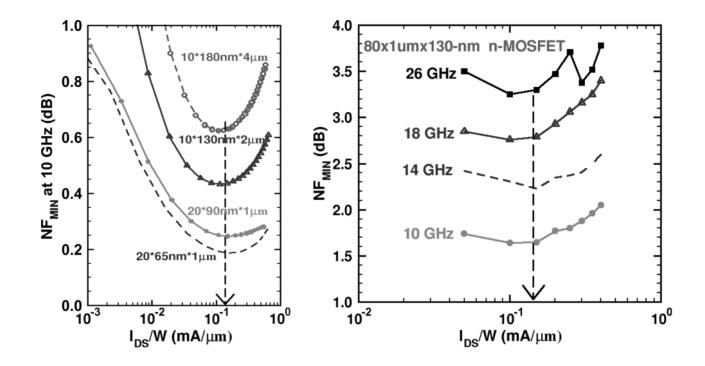

## Invariance of optimum current density (4)

a comparable optimum can be found when considering noise (J =  $\pm$  0.15 mA/ $\mu$ m)  $\rightarrow$  wider transistors and smaller V<sub>gs</sub> – V<sub>th</sub> if noise is more important than bandwidth

## CML stage and optimum current density

delay changes less than 10 % for a current density in the range 0.15 mA/ $\mu$ m – 0.5 mA/ $\mu$ m 20 18 16 14 τ (bs) 12 10 130nm 180nm 10<sup>-1</sup> 10<sup>0</sup>  $I_T/W$  (mA/µm)  $\tau = \frac{\Delta V}{I_T} \left[ C_{gd} + C_{db} + \left( k + \frac{R_g}{R_L} \right) \left[ C_{gs} + (1 + g_m R_L) C_{gd} \right] \right]$

→ time constant at the output of the CML stage when fully switching the tail current

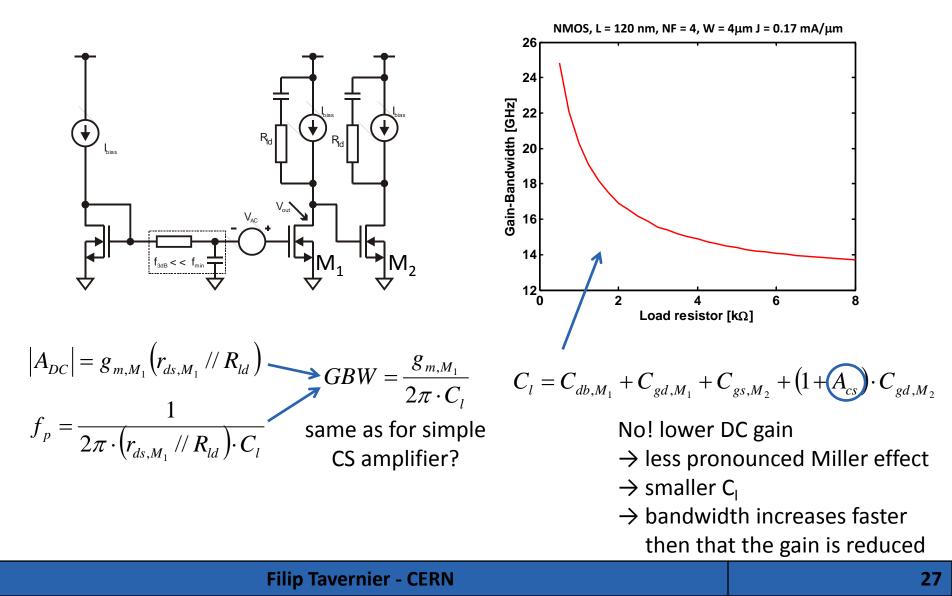

# Common-source amplifier with resistive load

# Common-source amplifier with common-drain stage

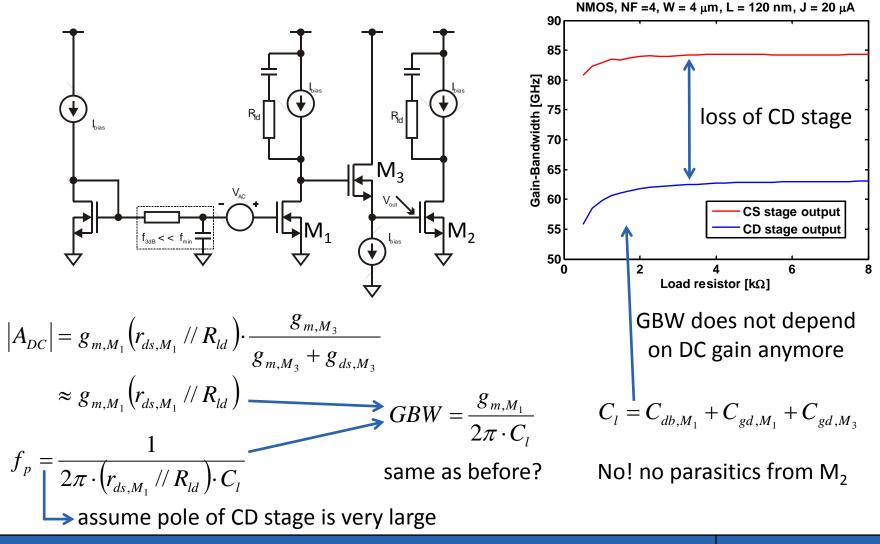

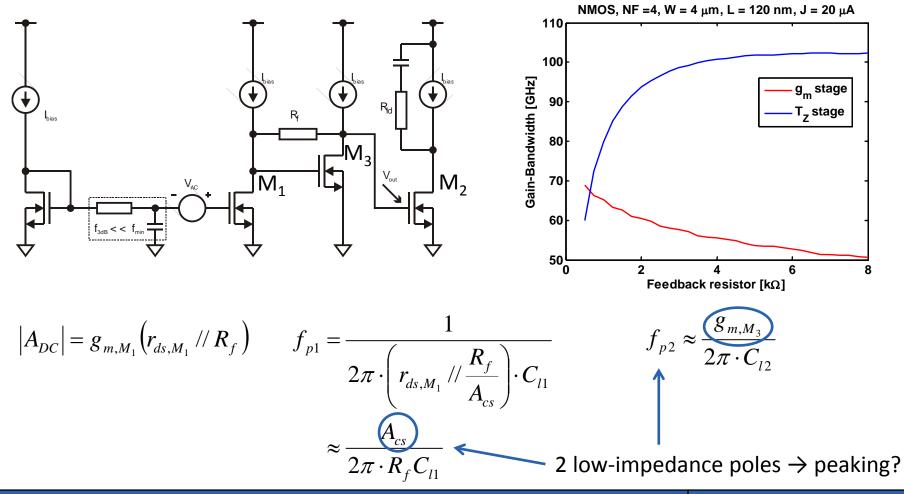

## **Cherry-Hooper amplifier**

principle: no high impedance nodes

→ alternate transconductance and transimpedance stages

# CERN

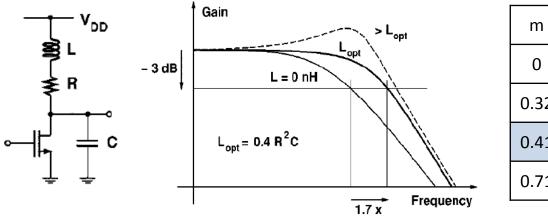

## Inductive peaking

problem: output capacitance reduces output impedance at higher frequencies

- $\rightarrow$  lower output voltage since output current sees lower impedance

- ightarrow pole at relatively low frequency

**solution:** add an inductor in series with the load resistor = shunt peaking

- ightarrow impedance of inductor increases with frequency

- → this increased inductor impedance can balance the reduced capacitance impedance

- $\rightarrow$  voltage gain can be maintained over wider frequency range

- $\rightarrow$  pole at a higher frequency

$L = mR^2C$

| m    | BW increase | response            |

|------|-------------|---------------------|

| 0    | 1           | no peaking          |

| 0.32 | 1.6         | optimum group delay |

| 0.41 | 1.72        | maximally flat      |

| 0.71 | 1.85        | maximum bandwidth   |

$1^{st}$  order system  $\rightarrow 2^{nd}$  order system  $\rightarrow$  peaking

## Active inductive peaking

**problem:** on-chip inductors require a lot of area solution: emulate an inductor by means of a resistor, a capacitor and a transistor  $\rightarrow$  at low frequencies, the g<sub>m</sub> generates a low impedance  $\rightarrow$  at very high frequencies, gate and source of the transistor are shorted through the gate-source capacitance  $\rightarrow$  at very high frequencies, the impedance is high as it is only determined by R<sub>p</sub> (and by the output resistance of the transistor)  $\rightarrow$  at intermediate frequencies, the impedance is inductive!  $Z_p$  $R_n$  $Z_p$  $g_{m,M_{I}}$ out  $g_{m,M_p}$  $\log f$  $\overline{2\pi} \cdot R_p C_{gs,M_p}$  $2\pi \cdot C_{gs,M_n}$  $\rightarrow$  modify pole locations by adding a capacitor in parallel with C<sub>gs</sub>

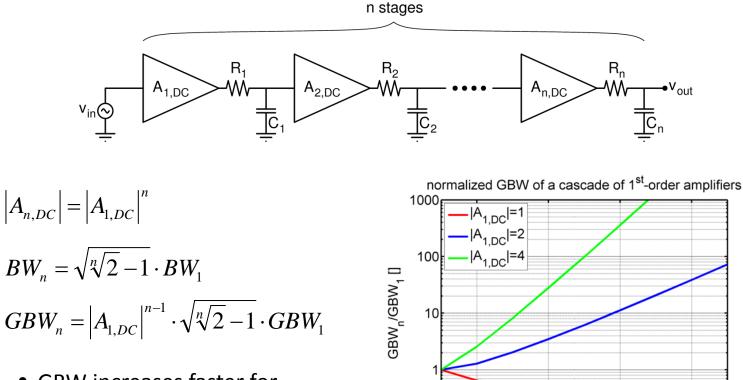

## Multistage amplifier (1)

sometimes, gain **AND** bandwidth are required  $\rightarrow$  multistage amplifier

0.1

2

6

number of stages []

8

- GBW increases faster for higher single-stage gains

- power consumption increased by the number of stages

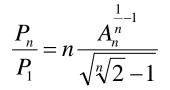

## Multistage amplifier (2)

What if we want to design a multistage amplifier with a certain gain and bandwidth? How many stages do we need?

$$\frac{GBW_1}{GBW_n} = \frac{A_n^{\frac{1}{n}-1}}{\sqrt{\sqrt[n]{2}-1}}$$

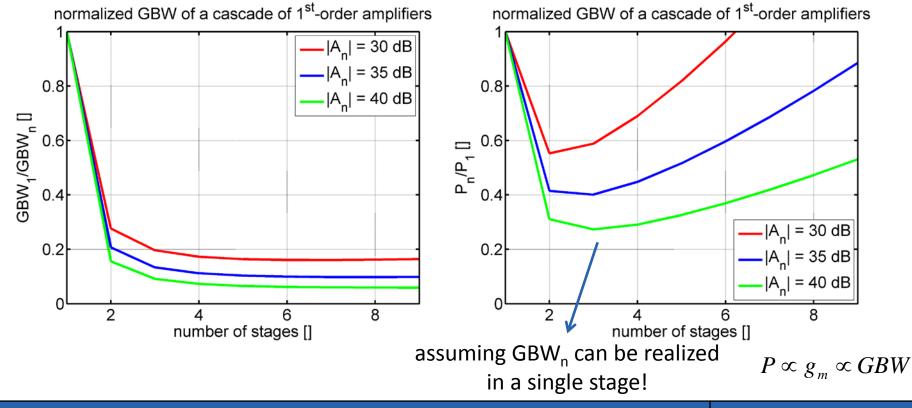

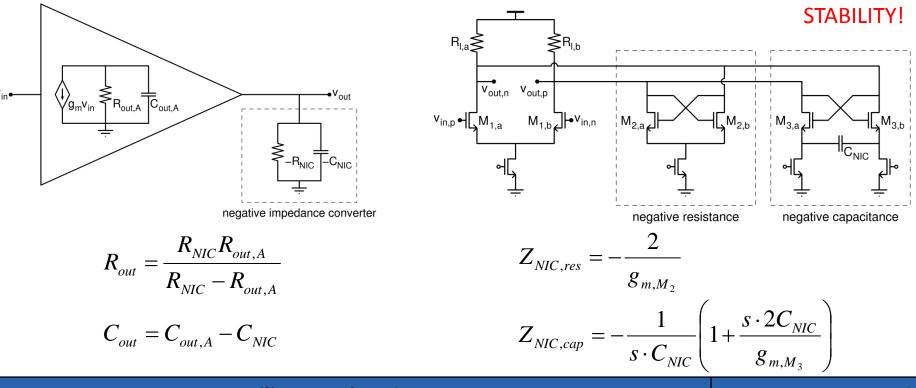

## Negative impedances?

Can we increase gain and bandwidth simultaneously?

- negative resistance to increase the overall output resistance

- $\rightarrow$  gain is increased

- ightarrow bandwidth is reduced

- negative capacitance to decrease the overall output capacitance

→ bandwidth is increased

### Acknowledgements

• Paulo Moreira