#### Estimation of the depletion capacitance in a monolithic pixel sensor

Laboratorio di Fisica Nucleare e Subnucleare II

Luca Pacher

INFN and University of Turin

Turin, 15/05/2013

pacher@to.infn.it

- monolithic pixel sensors

- pixel matrix segmentation

- on-chip and off-chip read-out electronics

- DAQ system

- Iab measurements

- setup linearity

- sensor capacitance estimation

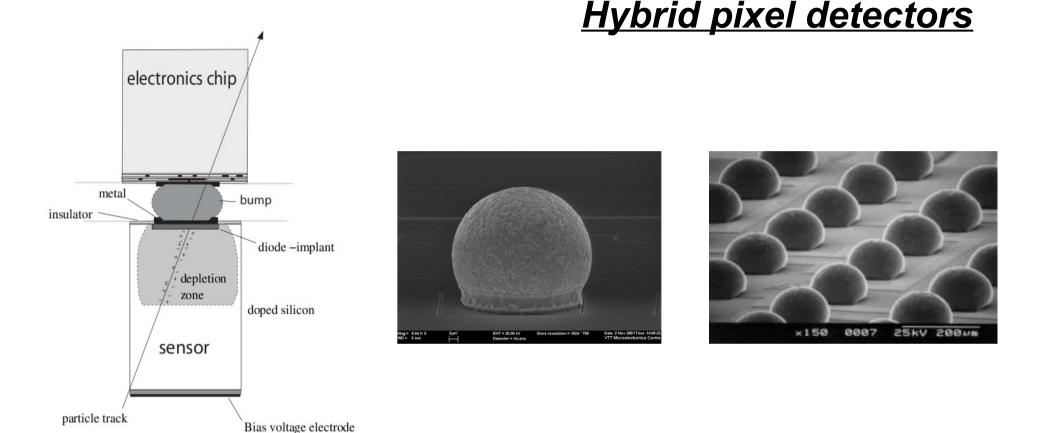

- sensor and electronics made on *two different silicon dies* and then mated together

- **bump bonding** technique  $\rightarrow$  expensive (cost can be afforded to cover max. area  $\sim m^2$ )

- charge collection  $\underline{by \ drift} \rightarrow OK$  speed and radiation hardness

- power consumption ~ 250 mW/cm<sup>2</sup>

- material budget ~ 300 µm

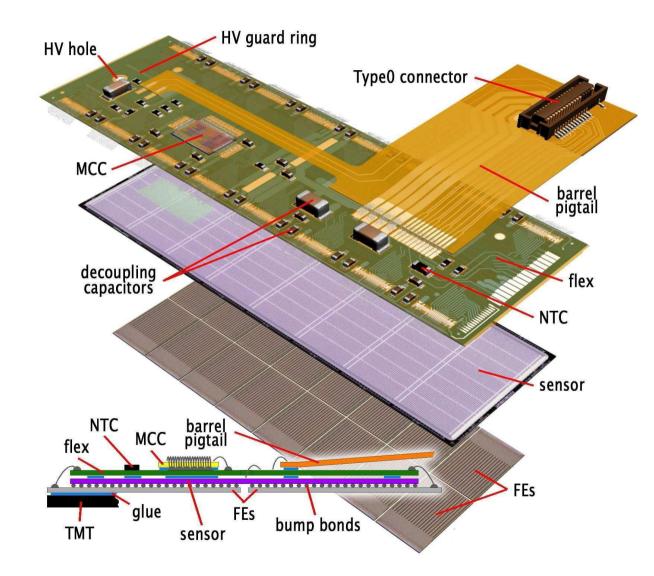

### Full module example (ATLAS)

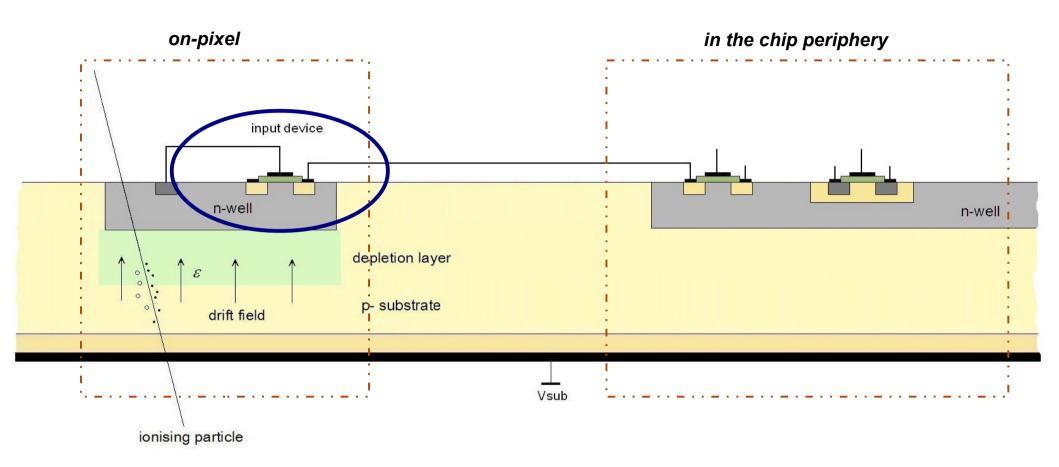

### <u>LePix</u>

- 90 nm *commercial* CMOS technology

- <u>reverse biased substrate</u> (~ 30V)  $\rightarrow$  charge collection by drift

- the *first transistor* of the analog front-end electronics is built at the top of each the pixel !

- the remaining electronics is placed in a dedicated n-well *at the periphery* of the sensitive region

- the n-well must be *insulated* from the reverse biased substrate to avoid *breakdown* !

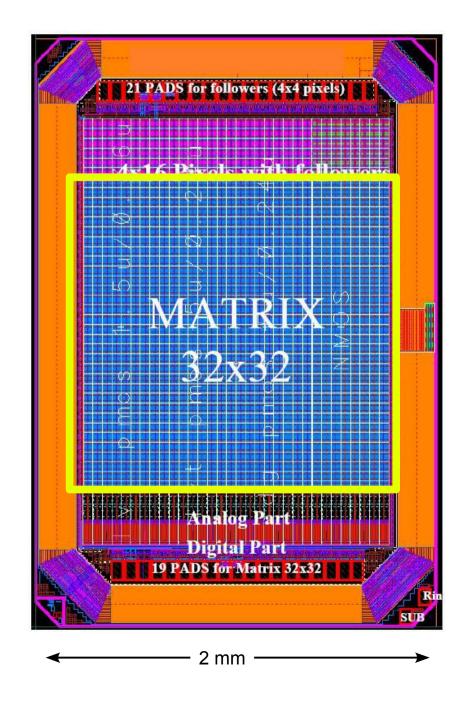

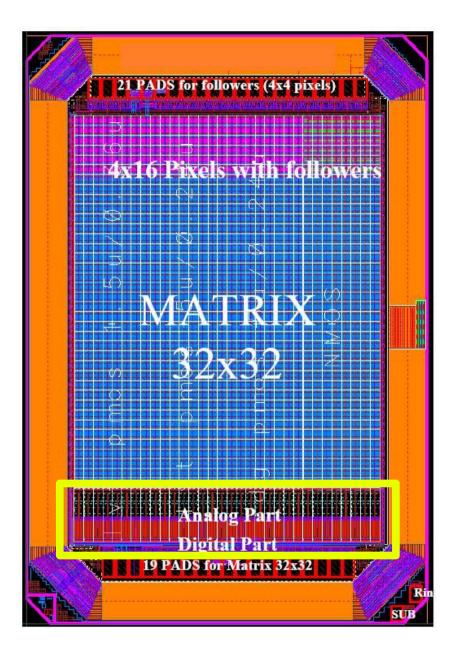

# Matrix segmentation (1)

.5 mm

N

- sensitive area + read-out electronics are <u>integrated on the same chip</u> !

- monolithic approach

- no separation between sensor and electronics

- a <u>guard ring</u> structure (200 µm around the matrix) ensures a uniform depletion region

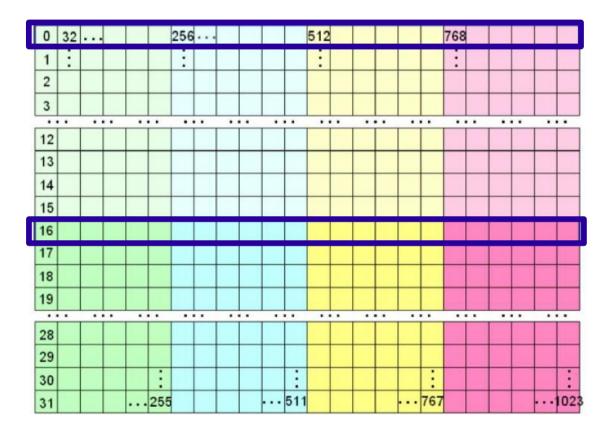

- two asymmetric regions in the matrix

- TOP part  $\rightarrow$  6 rows x 32 columns

- CORE part  $\rightarrow$  32 rows x 32 columns

- only CORE part pixels (1024 pixels) will be used for lab measurements

Matrix segmentation (2)

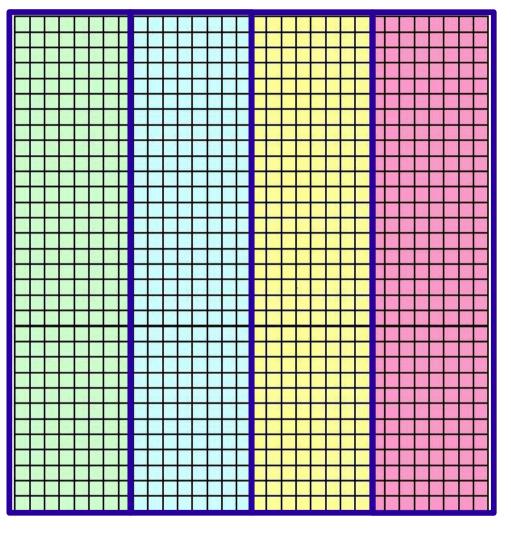

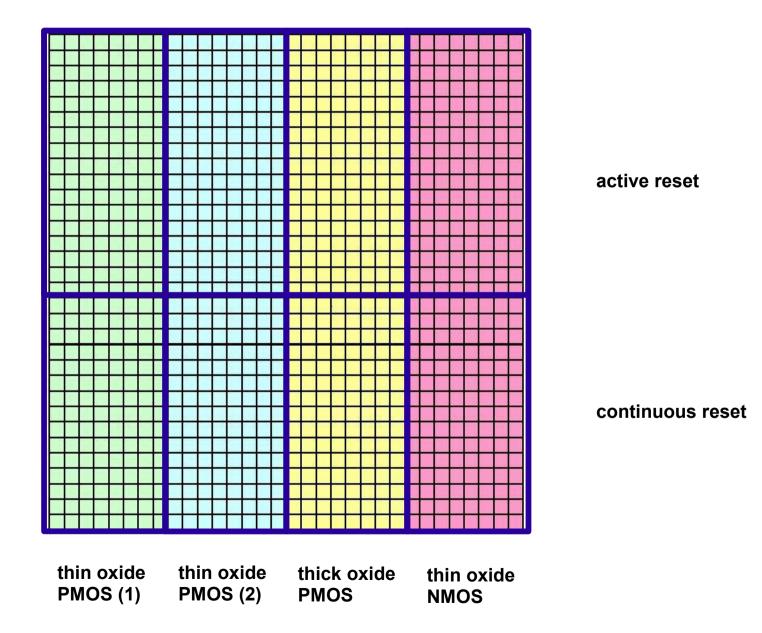

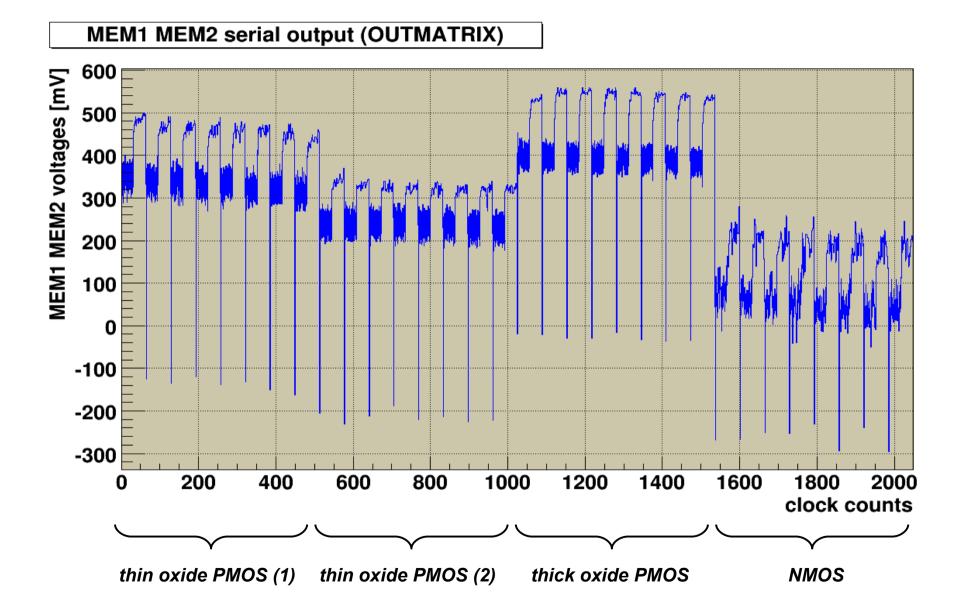

- different options have been implemented for the on-pixel transistor

- vertical segmentation → pixels with <u>4 different</u>

<u>types of input transistor</u>

- 8 columns thin oxide PMOS (1)

- 8 columns thin oxide PMOS (2)

- 8 columns thick oxide PMOS

- 8 columns thin oxide NMOS

- due to the limited available area PMOS input devices are preferable

thin oxide PMOS (1) thin oxide thick oxide PMOS (2) PMOS

thin oxide NMOS

# Matrix segmentation (3)

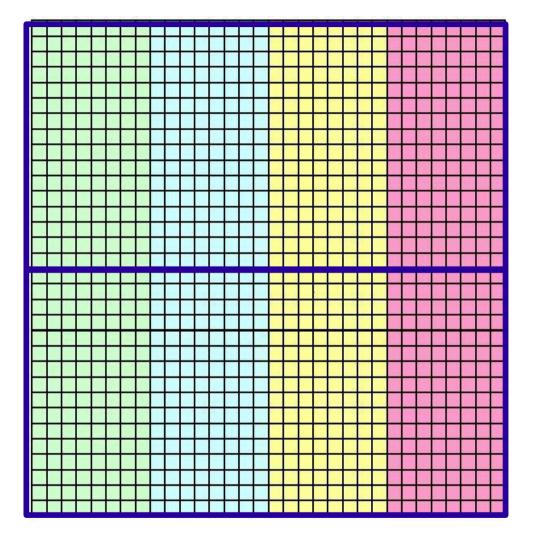

- each pixel cell needs to <u>discharge</u> the depletion capacitance after a particle hit has been detected

- on-pixel <u>reset scheme</u> (next slide)

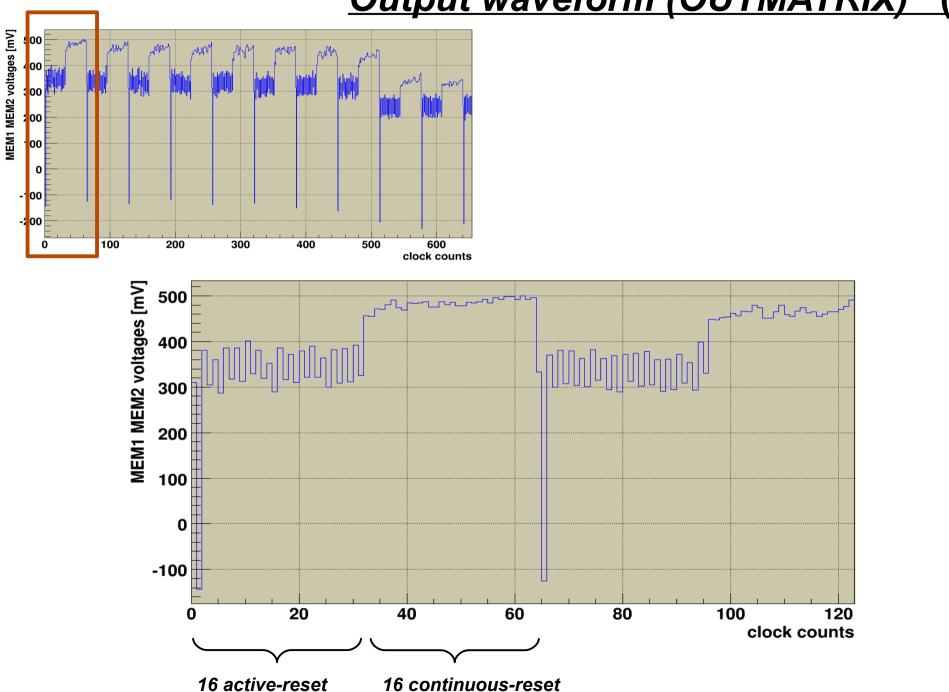

- horizontal segmentation → pixels with 2 different types of reset schemes

- 16 raws with active reset

- 16 raws with continuous reset

## Matrix overall layout

### <u>Reset schemes</u>

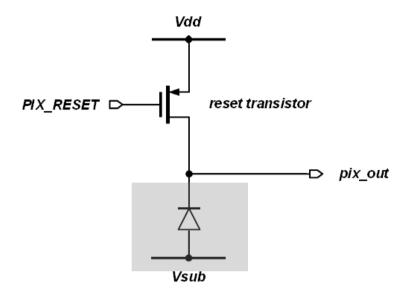

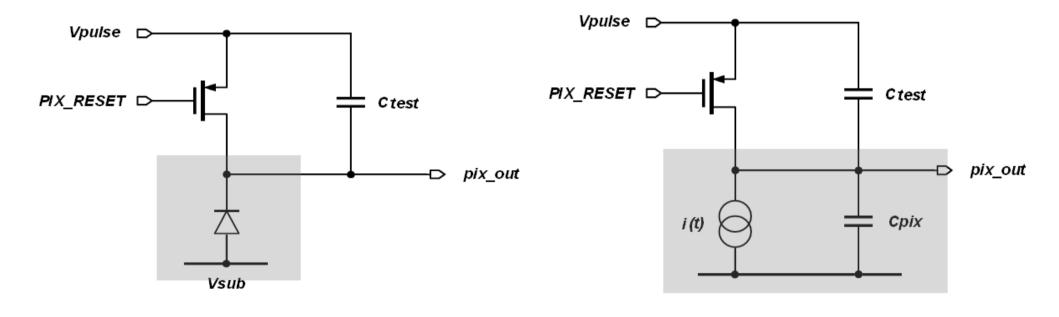

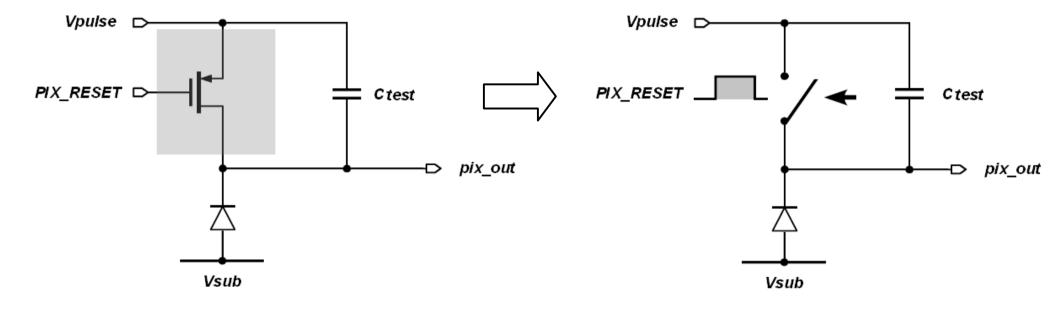

#### Active reset

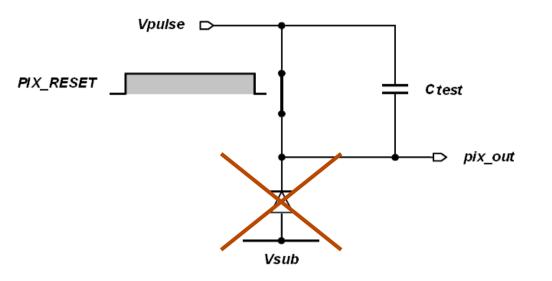

In active-reset pixels a PMOS <u>reset transistor</u> is used to reset the sensor. The gate is driven by a digital signal **PIX\_RESET**.

When *PIX\_RESET* = 0 a current discharges the pixel capacitance.PIX\_RESET

#### Continuous reset

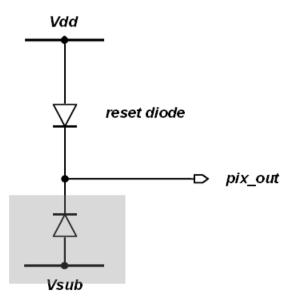

Continuous-reset pixels discharge the sensor capacitance though a <u>diode</u> connected to a DC voltage.

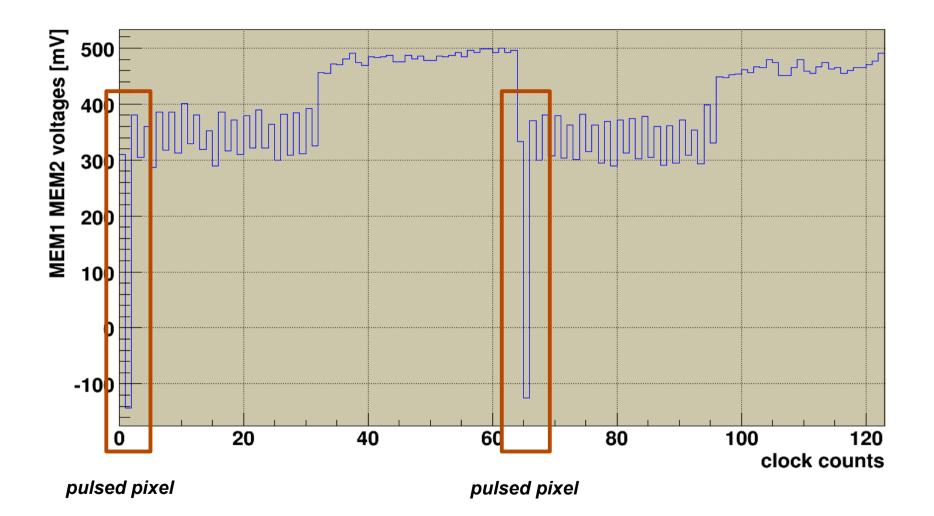

### **Pulsed rows**

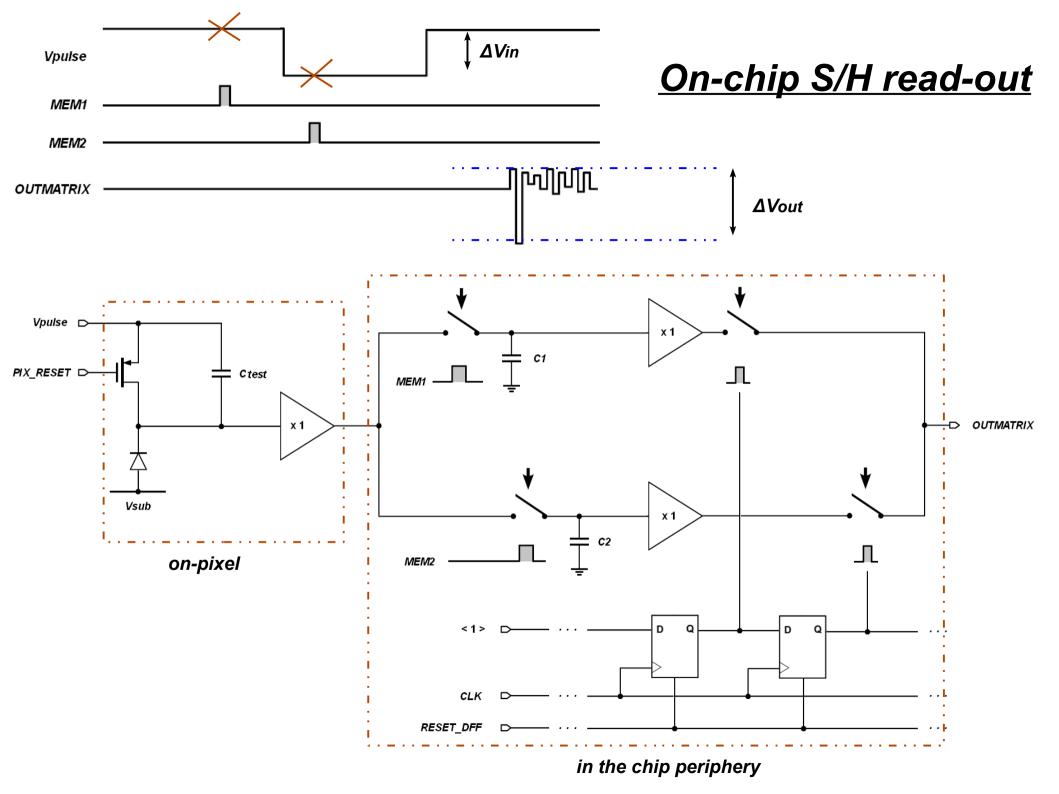

For testing purposes two rows (16 + 16 = 32 pixels) in the CORE part can be pulsed by using an external <u>test</u> <u>pulse</u> applied over a <u>test capacitance</u>

- 16 pixels with *active reset* (raw 0)

- 16 pixels with *continuous reset* (raw 16)

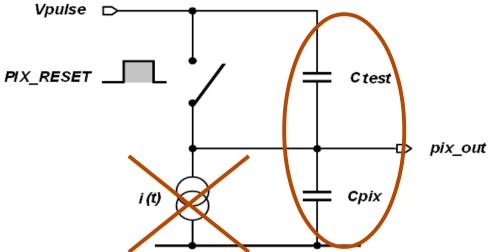

#### Sensor electrical model

#### Active reset + pulsed pixels (1)

## Active reset + pulsed pixels (2)

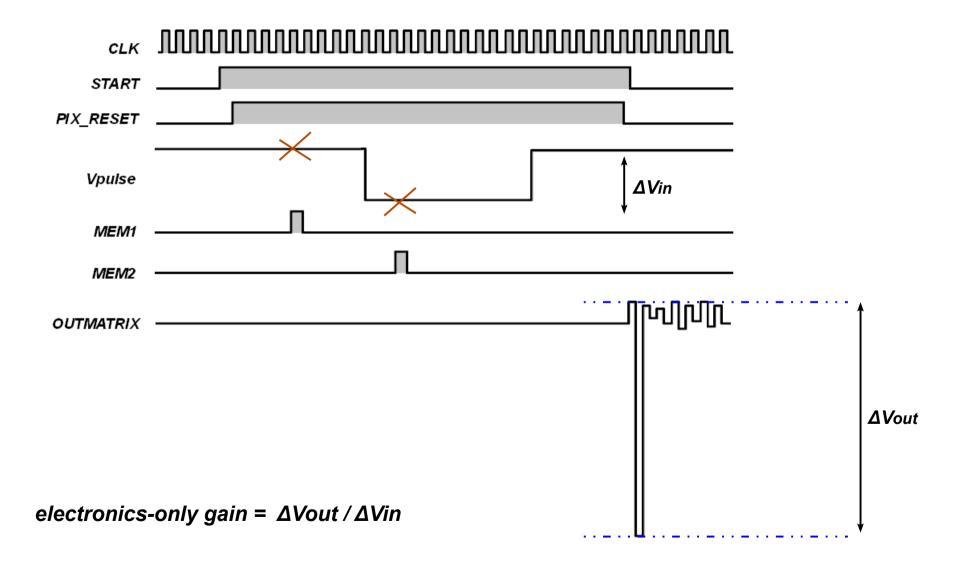

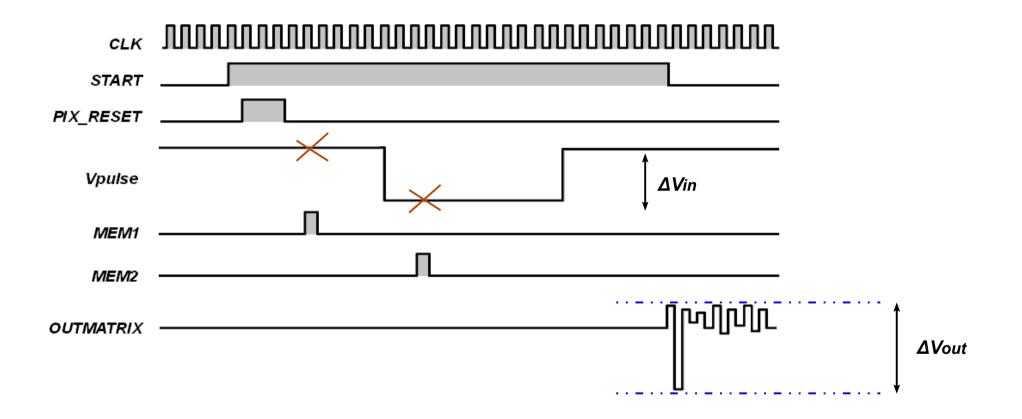

- **PIX\_RESET** is kept high for the entire acquisition

- PMOS switch ~short circuit

- pix\_out ≈ Vpulse

- the sensor is <u>excluded</u> from the read-out !

- useful configuration for <u>electronics-only</u> <u>characterizations</u>

- **PIX\_RESET** is a short pulse (a few clock cycles)

- the switch opens when *PIX\_RESET* goes low

- i(t) = 0 (you will not perform a test beam!)

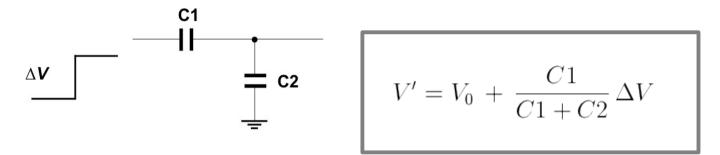

- test and sensor capacitances form a simple capacitive divider

- an estimation of the sensor capacitance *Cpix* can be obtained by applying a test pulse *Vpulse*

Analog and digital circuits are built in the <u>chip periphery</u> and <u>integrated</u> on the same sensor silicone die !

analog part

digital part

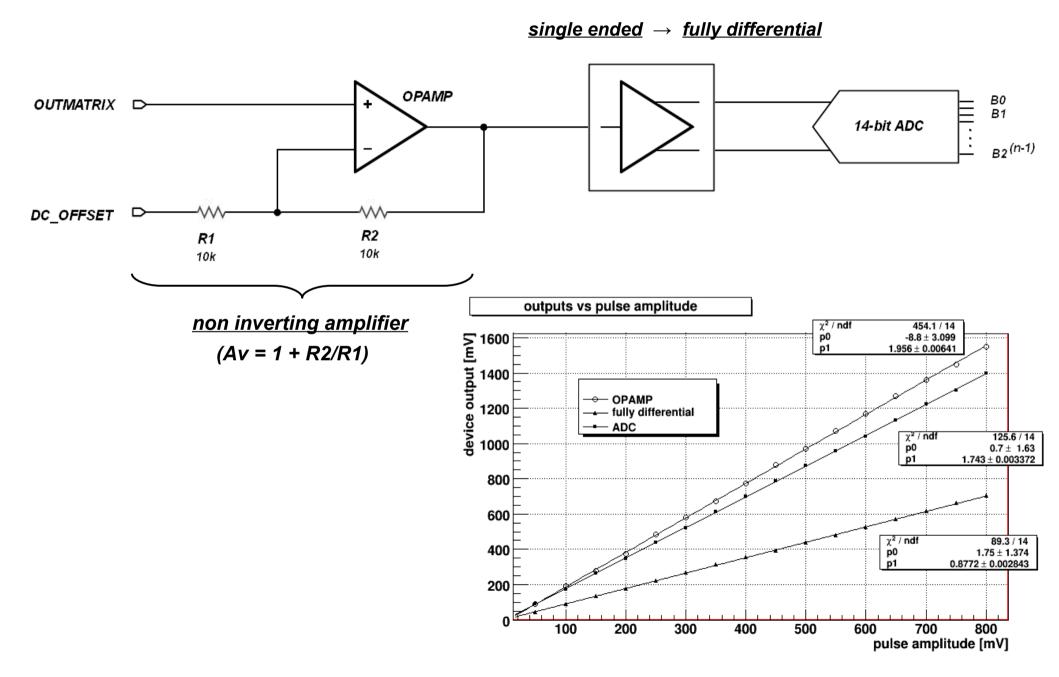

#### Off-chip read-out

LePix chip

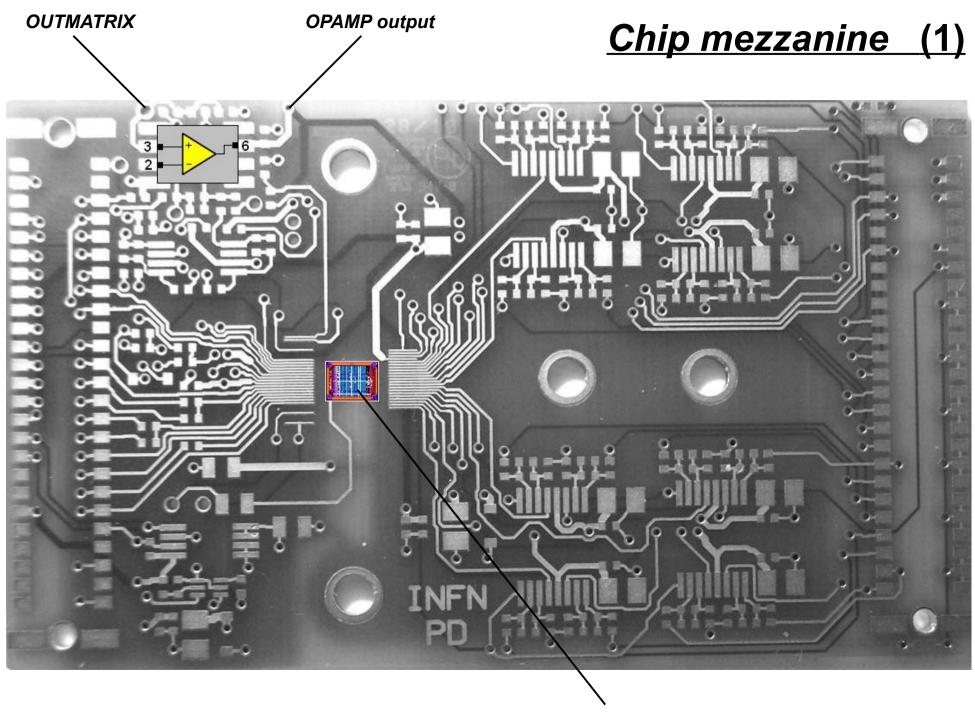

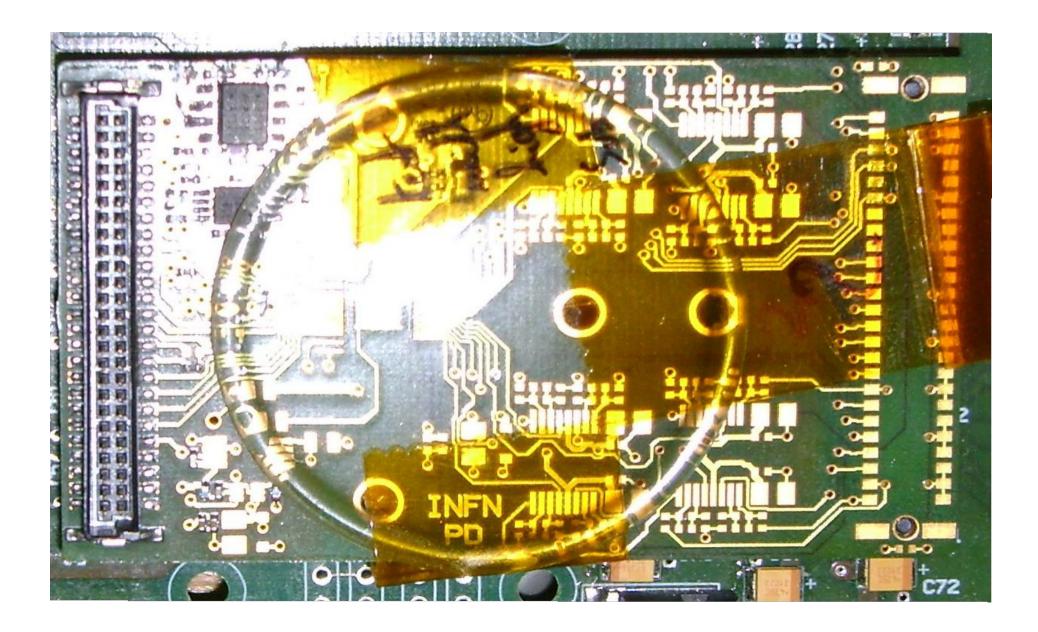

# <u>Chip mezzanine (2)</u>

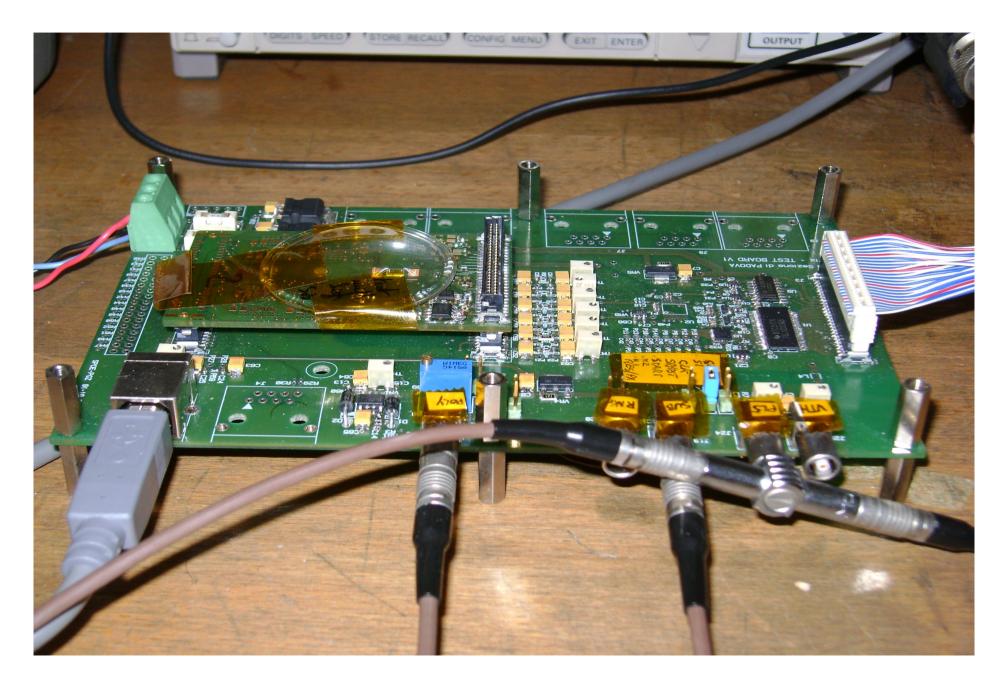

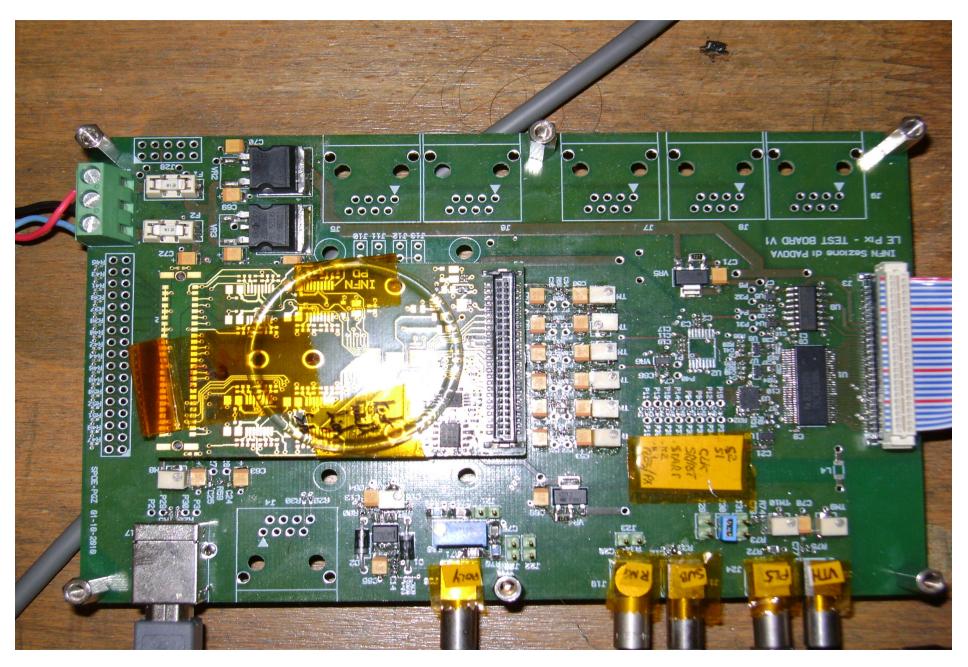

# Test PCB (1)

## Test PCB (2)

## **Experimental setup**

- plug-and-play mezzanine

- test PCB

- power supplies

- test PCB biasing (±5V)

- sensor depletion voltage (max. -30 V)

- parasitic transistors

- pulse generator

- digital oscilloscope

- DAQ (14-bit ADC with USB interface)

- computer with acquisition interface

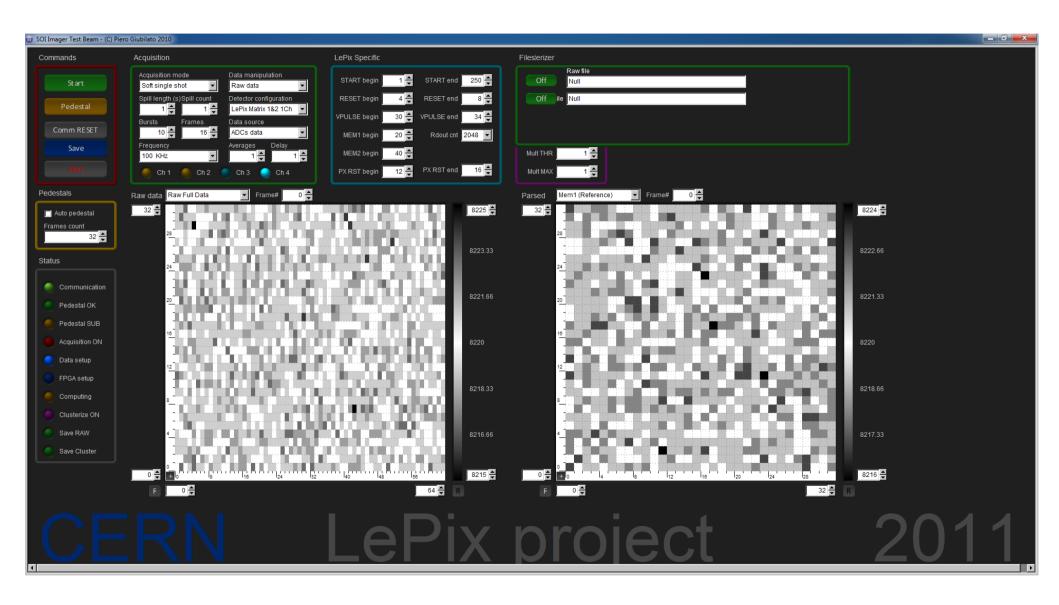

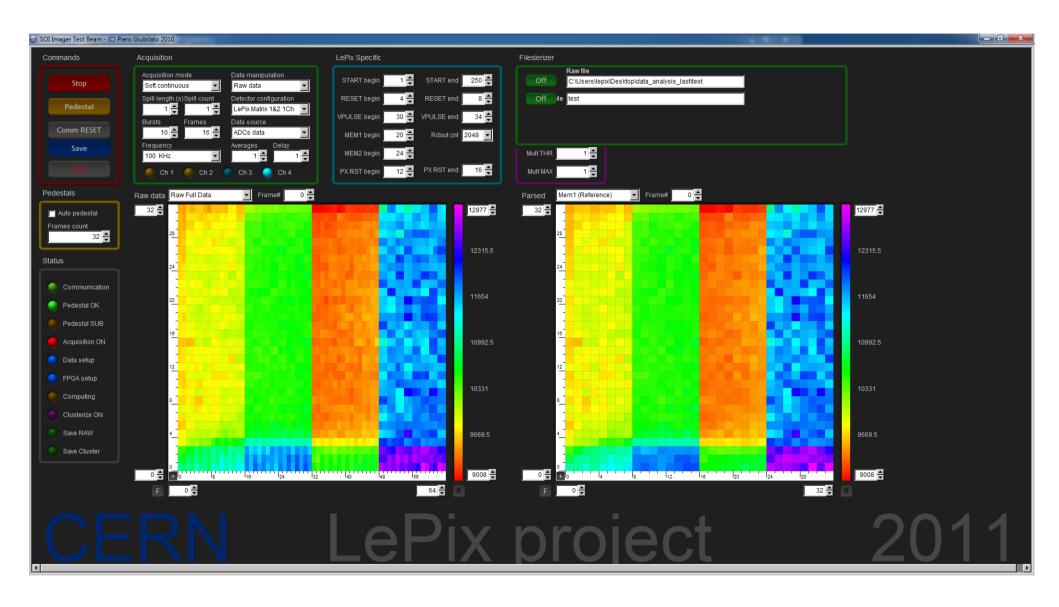

## **DAQ interface (1)**

## **DAQ interface (2)**

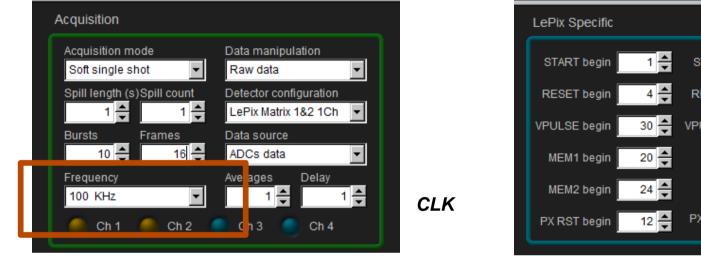

## **Control signals – DAQ interface**

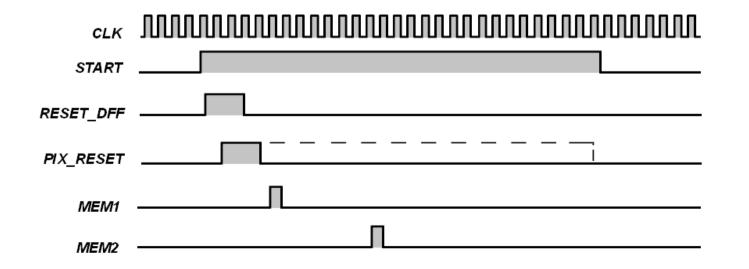

The *timing* for digital control signals is set from DAQ interface

LePix Specific

START begin

Image: Start begin

(start/stop are defined in term of n = n clock cycles)

## **Control signals on the test PCB**

## **Control signals at the oscilloscope**

#### **Getting started**

Set a right timing for the control signal (check it out using the oscilloscope!)

## Test pulse measurements (1)

## Test pulse measurements (2)

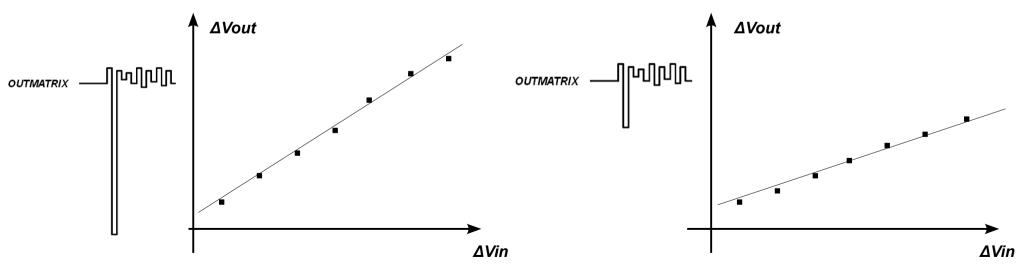

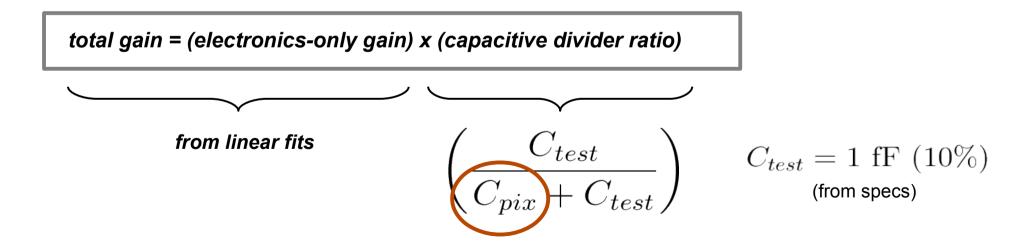

total gain (sensor + electronics) =  $\Delta Vout / \Delta Vin$

## **Output waveform (OUTMATRIX) (1)**

600

50

-100 -200 -300

MEM1 MEM2 voltages [mV]

## **Output waveform (OUTMATRIX) (2)**

www.law

8 columns

#### **Output waveform (OUTMATRIX) (3)**

### **Output waveform (OUTMATRIX) (4)**

## Lab measurements (1)

#### Electronics gain measurements

Measure  $\Delta Vout$  at the oscilloscope for the first pulsed pixel by applying <u>test pulses with different amplitudes</u>  $\Delta Vin$

- excluding the sensor from read-out (*PIX\_RESET* always on) → <u>electronics-only gain</u>

- including the sensor capacitance  $\rightarrow$  <u>sensor + electronics gain</u>

#### electronics-only (PIX\_RESET always ON)

| ΔVin   | ΔVout |

|--------|-------|

| 100 mV |       |

| 200 mV |       |

|        |       |

#### <u>sensor + electronics</u>

| ΔVin   | ΔVout |

|--------|-------|

| 100 mV |       |

| 200 mV |       |

|        |       |

read-out voltage gain =  $\Delta Vout / \Delta vin \rightarrow liner fit slope$

## Lab measurements (2)

#### <u>Refresh</u>

capacitive divider formula

#### Sensor capacitance estimation

An estimation of the pixel depletion capacitance can be obtained from electronics gain measurements:

Make a comparison with capacitance values obtained for silicon strips...