# **University of Turin**

Faculty of Mathematical, Physics and Natural Sciences

**Physics degree thesis**

# LePix: monolithic pixel detector for LHC tracking systems

Supervisor: M. Costa

Co-Supervisor: A. Rivetti

**Examiner**: M. Gallio

L. Pacher

October 10, 2011

# **Outline**

## Background

- LHC upgrades scenarios

- hybrid and monolithic architectures for pixel detectors

## The LePix project

- basic sensor concept

- the first 90 nm LePix submission

- Measurements and results

- Conclusions

## LHC upgrades scenarios

### first 2010-2012 physics run

- > nowaday LHC operating conditions:  $\sqrt{s} = 7$  TeV, luminosity ~ 3 x 10 <sup>33</sup> cm <sup>-2</sup> s <sup>-1</sup>, 50 ns bunch crossing

- > operating conditions for 2012 are under consideration both for  $\sqrt{s}$  and for the bunch spacing

- first long shutdown in 2013 (LS1)

second long shutdown in 2017 (LS2)

- third long shutdown in 2021 (LS3)  $\rightarrow$  Super-LHC (sLHC)

- $\blacktriangleright$  luminosity up to 10<sup>35</sup> cm <sup>-2</sup> s <sup>-1</sup>

first R&D programs must start now in order to be ready for ~ 2020 (each project requires a typical man-power of 5 ÷10 man-years)

- replacement of the entire ALICE, ATLAS and CMS tracking systems

- more layers equipped with sensors featuring high granularity, speed and adequate radiation hardness also in tracker regions at present instrumented with conventional silicon strip detectors

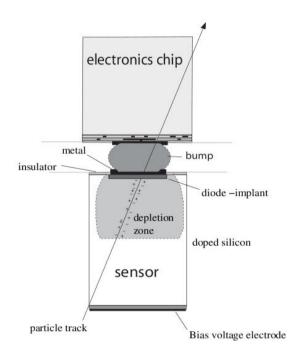

## Hybrid vs. monolithic

#### hybrid pixel detectors

- *bump bonding* technique → expensive

- charge collection by drift → speed & RH

- material budget ~ 300 µm

- power consumption ~ 250 mW/cm<sup>2</sup>

- cost can be afforded in the innermost

2 ÷ 3 layers of a collider tracking system

covering ~ m<sup>2</sup>

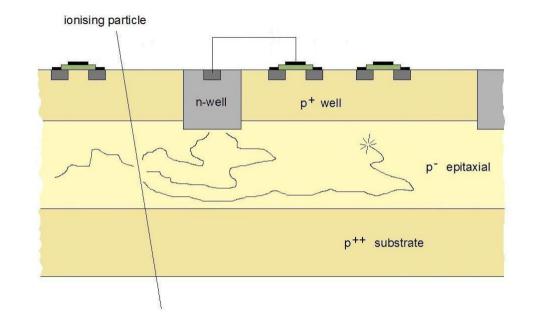

Monolithic Active Pixel Sensors (MAPS)

- detector & read-out electronics on the same piece of silicon

- charge collection by diffusion (~ 100 ns)  $\rightarrow$  no reverse bias

- Iow material budget ~ 10 ÷ 30 μm

- Iow power consumption (a few tens of mW/cm<sup>2</sup>)

- standard CMOS technologies → low production cost

## The LePix project

a long-term *R*&*D* project potentially suitable for ~ 2021 LHC trackers upgrades and for future HEP experiments

the project explores the possibility of implementing monolithic pixel detectors in very deep submicron CMOS technologies

- the goal is to combine advantages of MAPS and hybrid pixel detectors architectures

- MAPS exhibit low power consumption and low material budget, integrating the sensor and its read-out electronics on the same substrate according to the monolithic approach

- > in hybrid pixel detectors the charge collection by drift ensures speed and adequate radiation tolerance

- the key difference with respect to traditional MAPS is the reverse-biased substrate

- $\blacktriangleright$  charge collection by drift  $\rightarrow$  speed and radiation tolerance

- high resistivity (≥ 100 Ω cm) wafers → depletion layers of  $10 \div 40 \,\mu\text{m}$  by applying moderate reverse biases (50 ÷ 100 V)

- possibility offered by the foundry of porting standard CMOS processes on high resistivity wafers

- > the remaining electronics is built in a dedicated *n*-well of *low resistivity* (~  $1 \div 2 \Omega$  cm) at the border of the sensitive region

- ➤ the *n*-well must be insulated from the reverse-biased substrate in order to avoid breakdown → non standard and aggressive layout (special masks, protection structures, etc.)

## Prototyping strategy

- first LePix submission in standard CMOS <u>90 nm</u> technology (March 2010)

- breakdown and transistor test structures, a large diode for radiation tolerance measurements and 4 test pixel matrices have been submitted with the foundry

- > a *layout problem* arised during first tests performed at CERN in summer 2010 (see later)

- structures submitted on *standard resistivity wafers* only

- a prototype of the LePix digital circuitry has not yet been implemented

- > matrices instrumented with some few simplified read-out schemes

- according to measurements and results presented in this work our description is only focused on pixel matrices, in which detecting elements and read-out electronics are integrated on the same piece of silicon

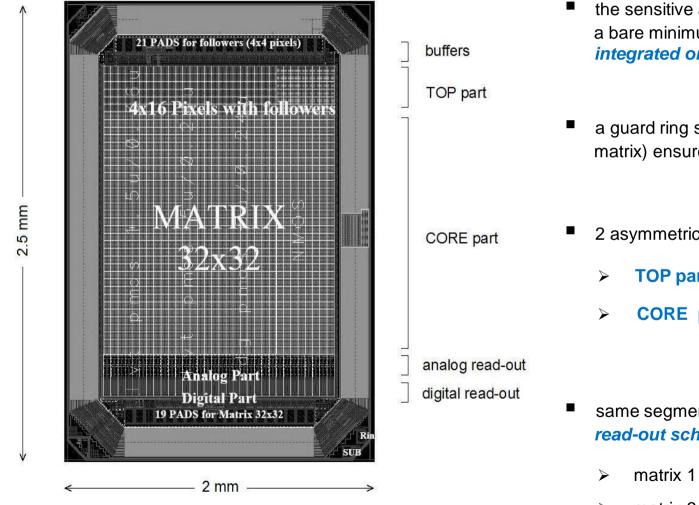

## Matrix overall layout

- the sensitive area, the analog read-out and a bare minimum standard digital circuitry are integrated on the same chip (2 mm x 2.5 mm)

- a guard ring structure (200 µm around the matrix) ensures a uniform depletion layer

- 2 asymmetric regions

- **TOP part** 6 rows x 32 columns

- CORE part 32 rows x 32 columns

same segmentation and structure, different read-out schemes

- matrix 1 2  $\rightarrow$  analog serial read-out

- matrix 3 4  $\rightarrow$  binary serial-read-out  $\geq$

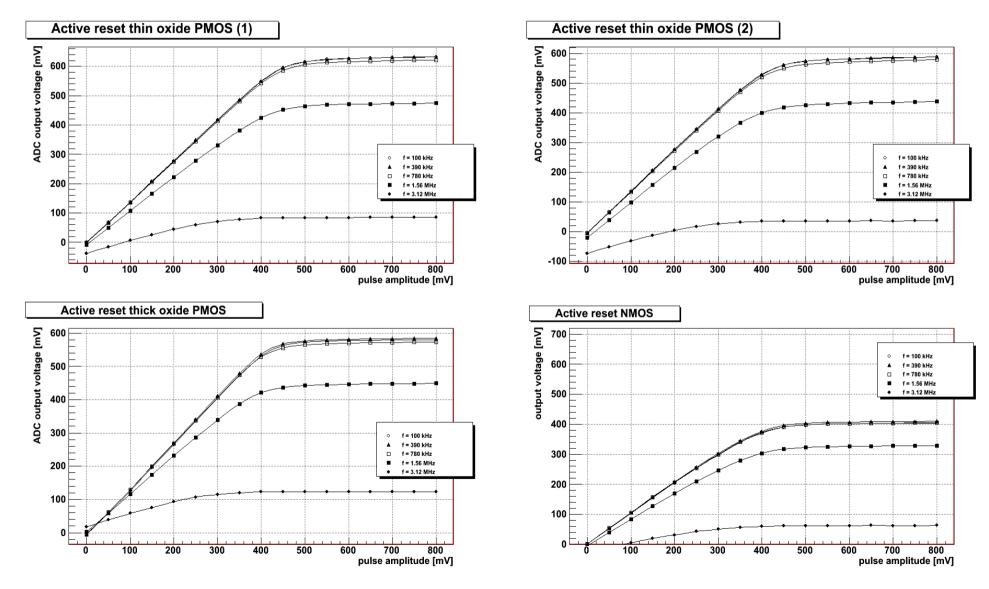

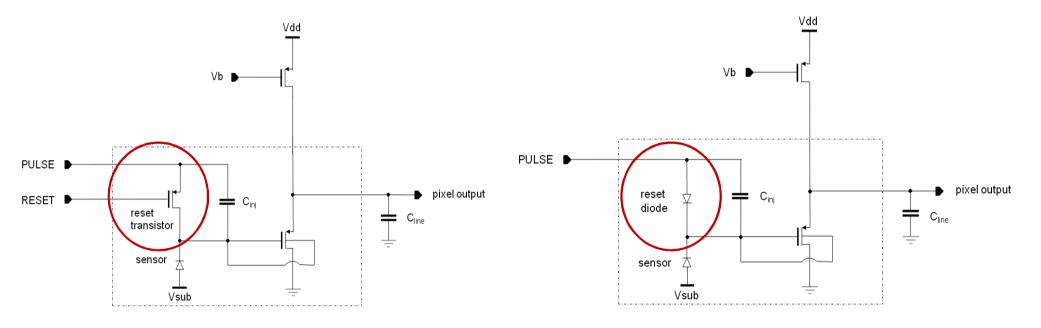

## Reset schemes & test pulse

each sensor needs to discharge the parasitic capacitance after a particle hit has been detected

$\succ$  2 discharge schemes implemented  $\rightarrow$  *active-reset* and *continuous-reset*

■ 3 rows in each matrix can be *electrically pulsed* by applying a voltage step (test pulse) over a *injection capacitor*

#### active-reset (6 rows TOP part + 16 rows CORE part)

A PMOS reset transistor is employed to reset the sensor. The gate is driven by a digital voltage pulse PIX\_RESET and a weak-inversion current discharges the pixel capacitance. Depending on the duration of the PIX\_RESET signal the reset transistor can behave like a switch or a linear resistor.

#### continuous-reset (16 rows CORE part)

Continuous-reset pixels discharge the sensor capacitance through a diode (connected to a reference DC voltage) which absorbs the leakage current from the pixel.

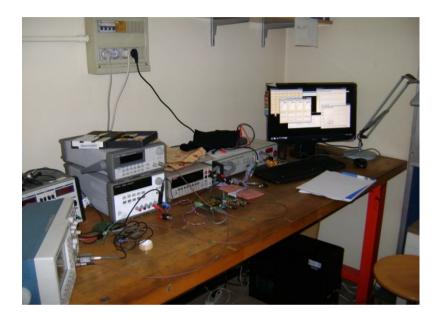

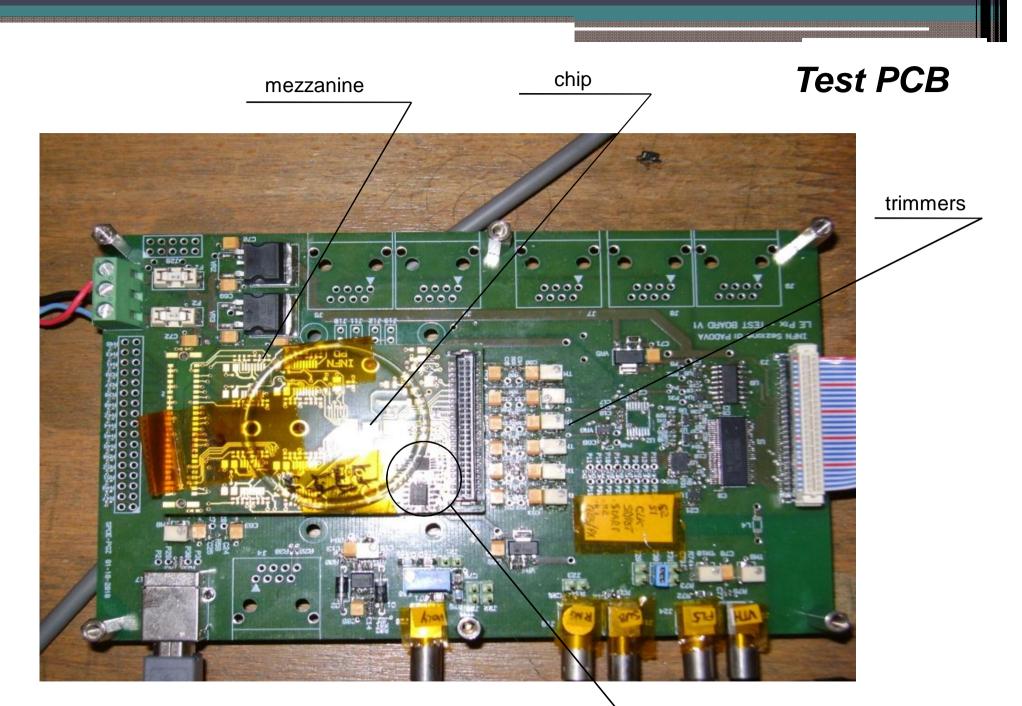

## A plug-and-play setup

- the chip is wire-bonded onto a mezzanine, which provides mechanical support, output test points and a bare minimum standard circuitry

- main test PCB (bias trimmers, further output test points, signals, power)

- DAQ with FPGA and 14 bit ADC

- a simple USB cable from DAQ to the acquisition PC (Windows 7 OS)

external chip read-out (OPAMP + FDA)

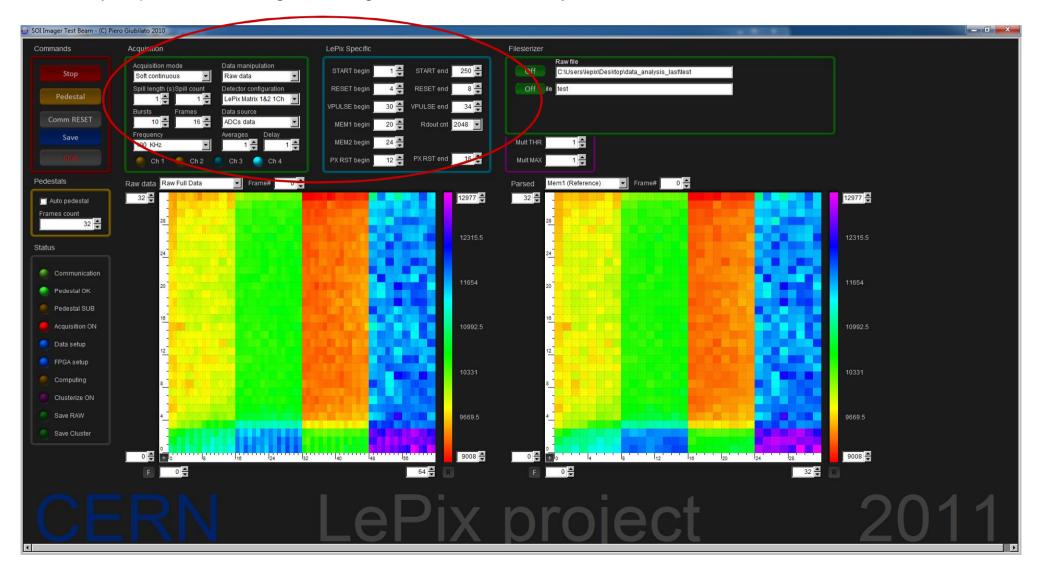

- ROOT 5.26 acquisition interface built with Visual C++ 2010

- on-line reconstruction of the CORE part pixel-map (1024 pixels)

- CLOCK frequency + timing for acquisition digital signals

- binary output files containing ADC integers  $\rightarrow$  off-line data analysis

## Acquisition interface

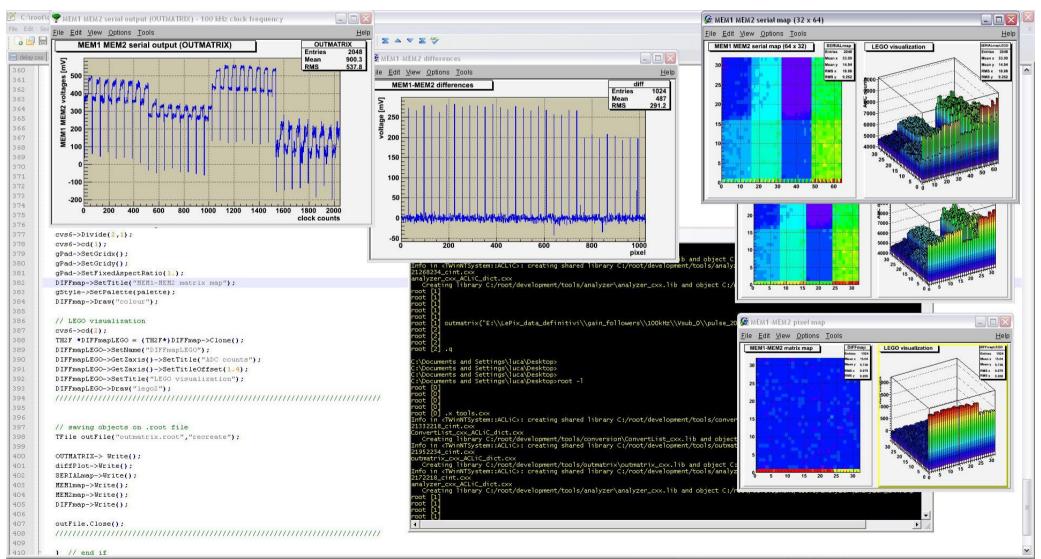

## **Off-line software (1)**

#### off-line matrix serial output and pixel-map reconstruction

C++ source file

INS

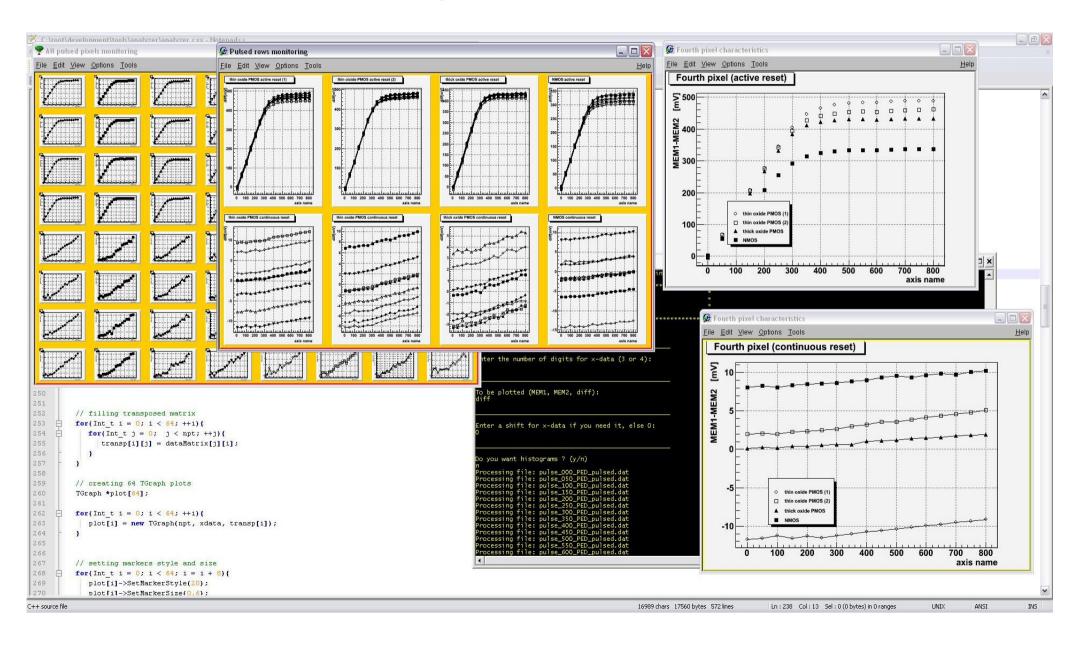

off-line extraction of *pixel characteristics* → output voltages as a function of a certain parameter under consideration (e.g. PULSE amplitude)

## **Off-line software (2)**

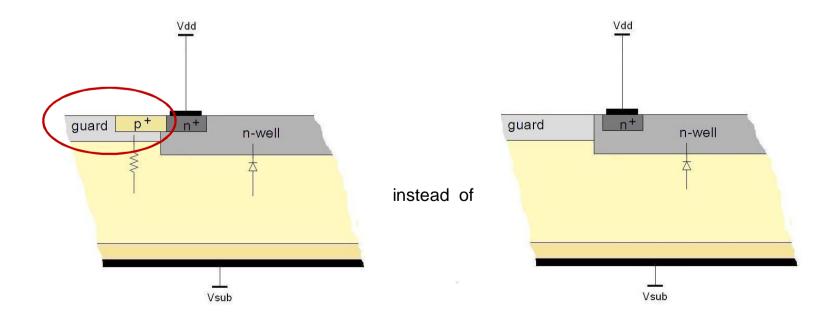

## Layout issue

- pattern density rules in very deep submicron technologies are very restrictive

- LePix requires a really non standard and aggressive layout

- beside standard masks provided by the foundry several *custom masks* were needed to be drawn in order to better insulate the electronics from the reverse-biased substrate

- > due to a mismatch with the foundry one of these special masks has been misinterpreted

- > all matrices of the first submission on standard resistivity received a systematic  $p^+$  implant in the external guard ring  $\rightarrow$  *layout issue*

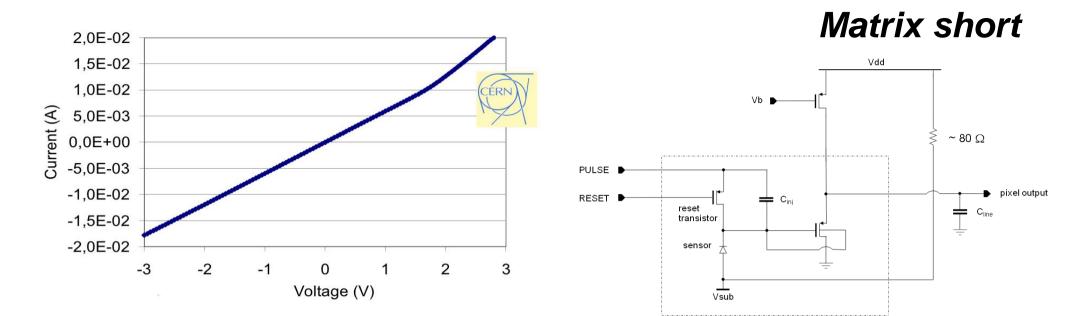

- Inear behaviour discovered with first matrix breakdown tests @ CERN

- > the  $p^+$  implant introduces a *resistive path*

- > mA currents through the resistive path vs. typical substrate leakage currents ~ nA

- > the lot on high resistivity immediately put on hold, requiring adequate corrections

- nominal reverse biases are forbidden  $\rightarrow$  -5 V is enough to *damage the chip*

- > the chip substrate can not be depleted  $\rightarrow$  no particle hits can be detected

- tests and measurements can be performed only on the read-out electronics, excluding the sensor

- > only active-reset pixels can be excluded

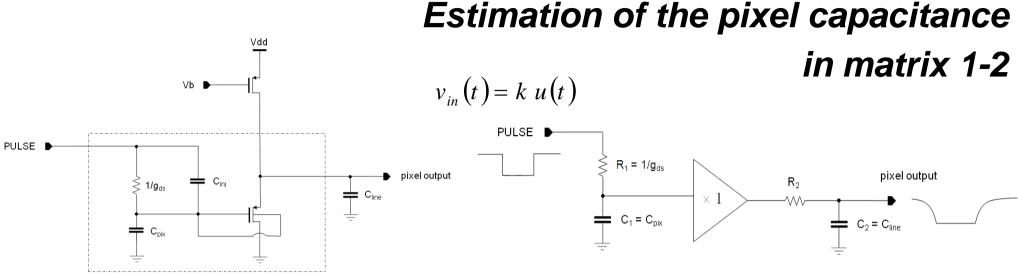

$$V_G = \frac{C_{inj}}{C_{pix} + C_{inj}} V_{PULSE}$$

$$C_{pix} >> C_{inj}$$

## Measurements and results

- breakdown voltage > 30 V close to expectations + radiation tolerance @ CERN

(but a systematic characterization of the read-out electronics embedded in the sensors has not been performed)

- setup validation (external-chip read-out with OPAMP + FDA + ADC)

- setup linearity (DC characteristics + voltage gain)

- > noise

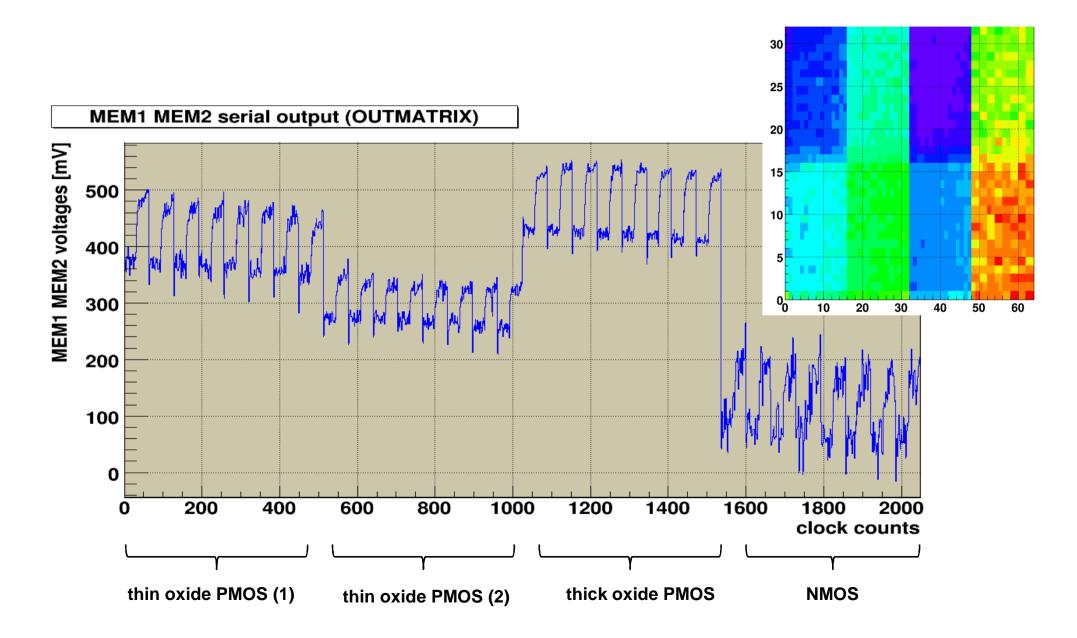

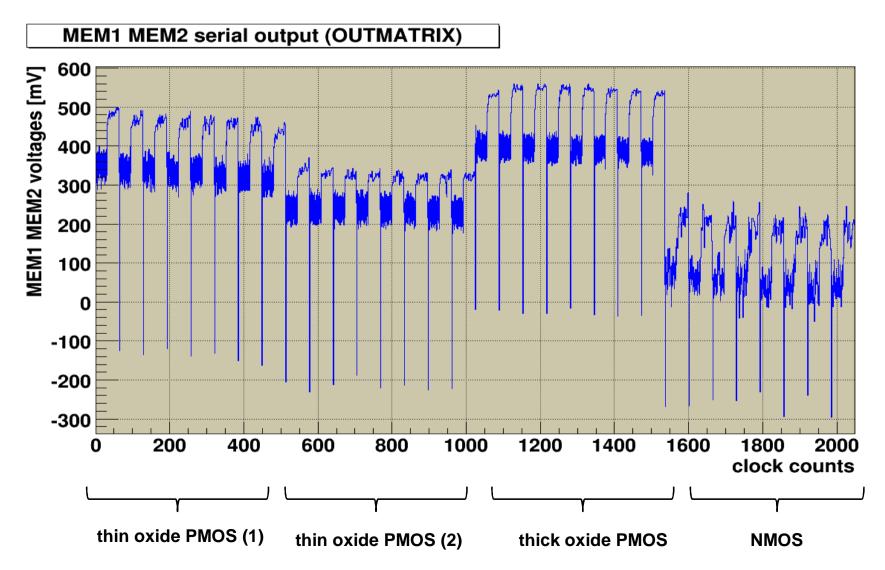

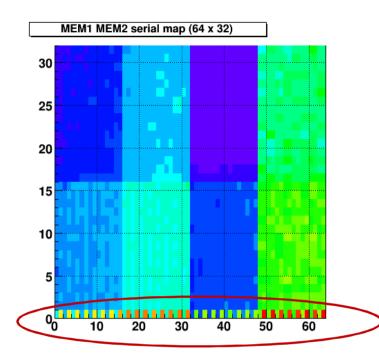

- matrix 1-2 CORE part characterization (MAPS-like double sample analog serial read-out)

- matrix output

- > source followers (SFs) characterizations  $\rightarrow$  measurements at the transistor level,

- estimation of the pixel capacitance

- matrix 3-4 CORE part characterization (binary serial read-out based on PREAMP + DISC)

- matrix output

- threshold scan and thermal noise

- PREAMPs and DISCs homogeneity

- bias characteristics

discussed

validating the 90 nm LePix electronics

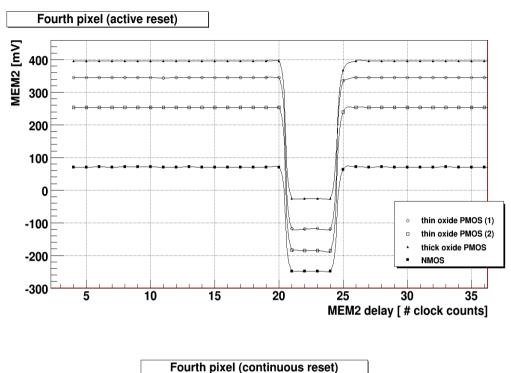

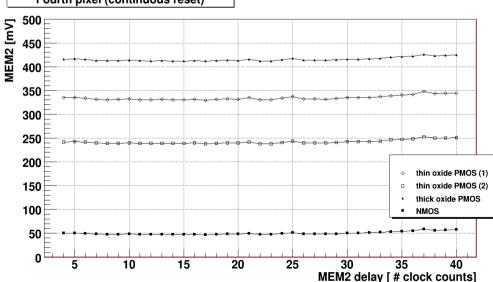

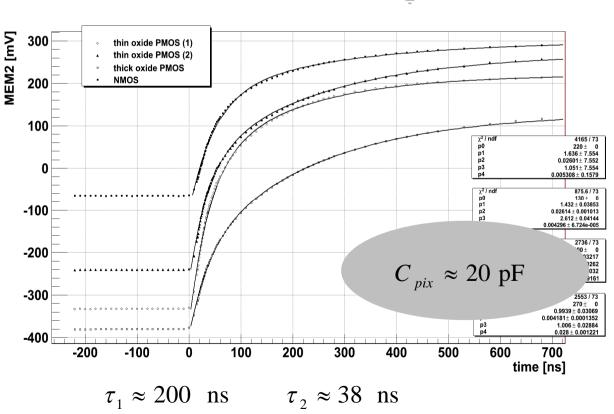

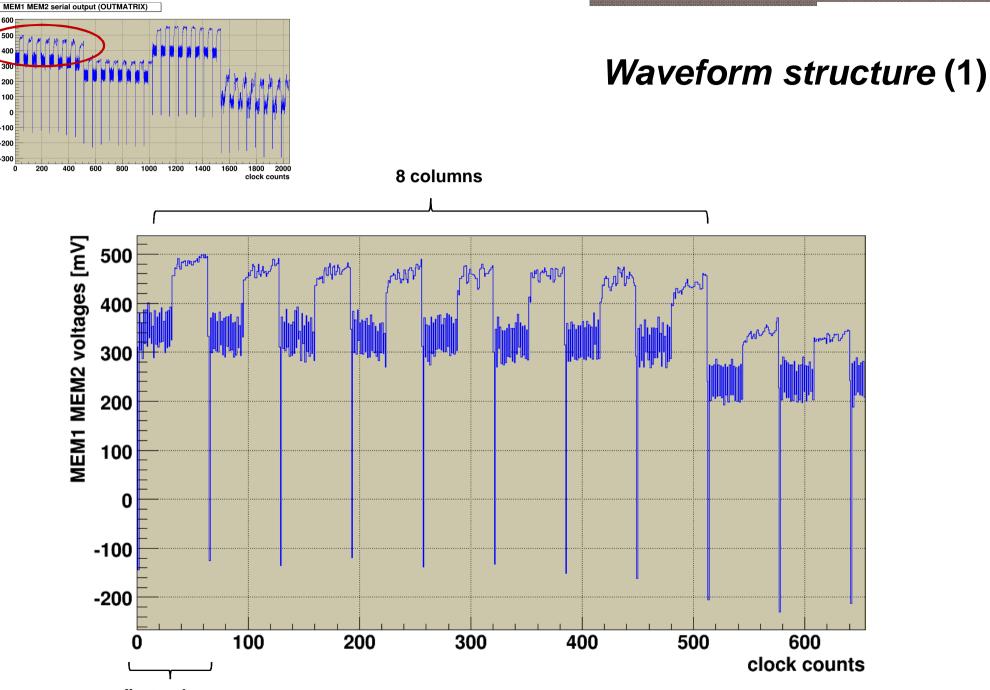

## PULSE reconstruction in matrix 1-2

A direct proof of the severe constraint introduced by the short in the guard ...

... due to the large capacitance of the not depleted sensor only input transistors of the active-reset pulsed row received the PULSE !

Although the external PULSE is a signal with sharp rising and falling edges the output waveform is expected to have *smooth transitions due to parasitic capacitances*

- two integrations performed by

2 buffered RC low-pass filters

- fine scan of the PULSE rising and falling edges, fitting experimental data with the predictable function (Laplace theory)

Simplified fitting function :

$$v_{out}(t) = k (1 - a e^{-bt} - c e^{-dt})$$

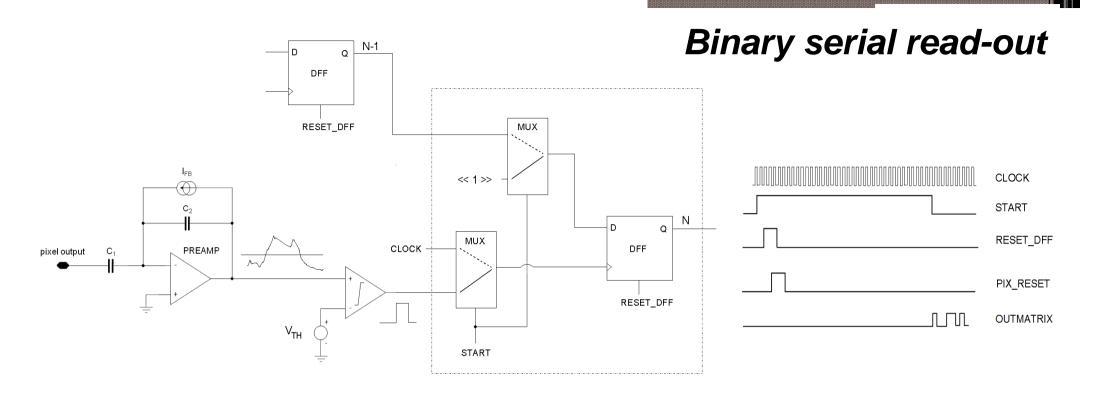

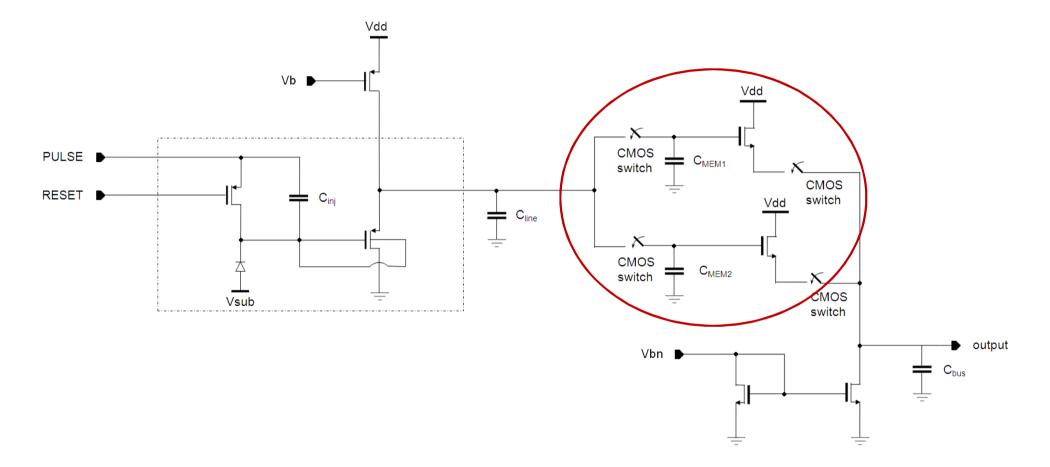

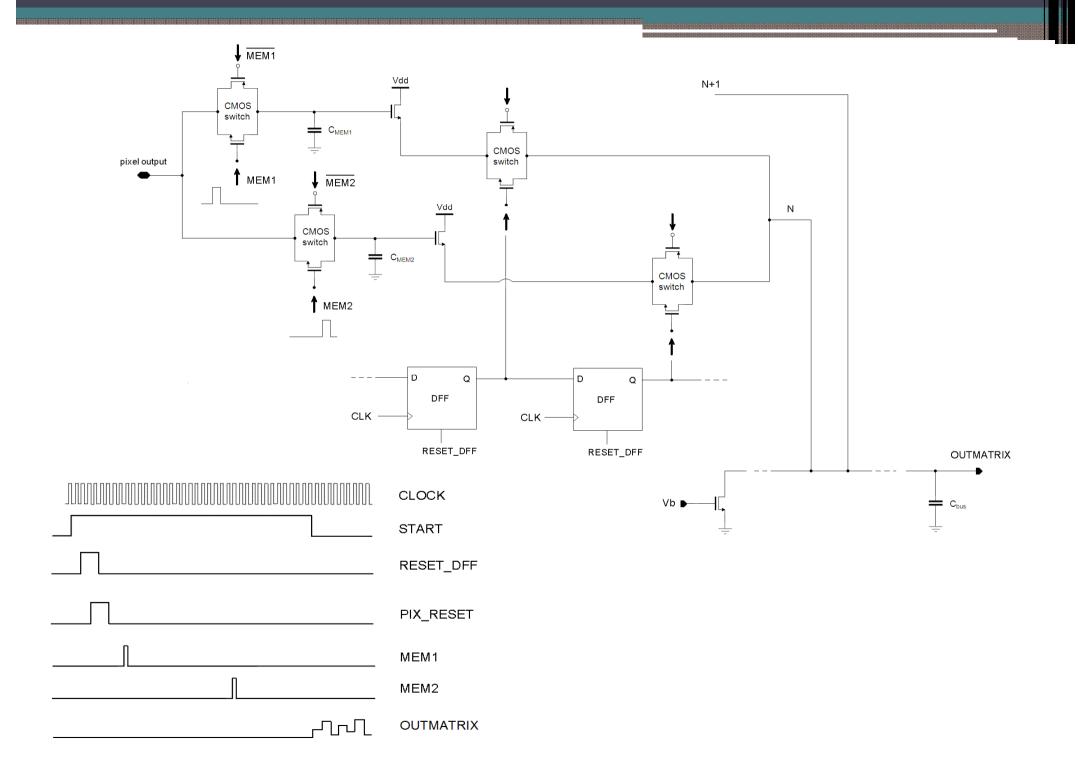

# Matrix 3-4 CORE part characterization

- input transistor in SF configuration AC coupled to a voltage amplifier (PREAMP) followed by a comparator (DISC)

- no support for ToT available

- parallel analog read-out of the CORE part towards the periphery of the matrix + serial digital read-out

- 2 multiplexers (MUX) and a D-Flip/Flop (DFF) for each pixel

- 1024 DFFs configured as a shift register → *binary serial read-out*

- > if a *transition* occurs the DISC produces a digital output pulse, providing a clock rising edge for the DFF

- > the output is a sequence of **1024** *logic values* 1/0 fed to the ADC through the external-chip read-out chain

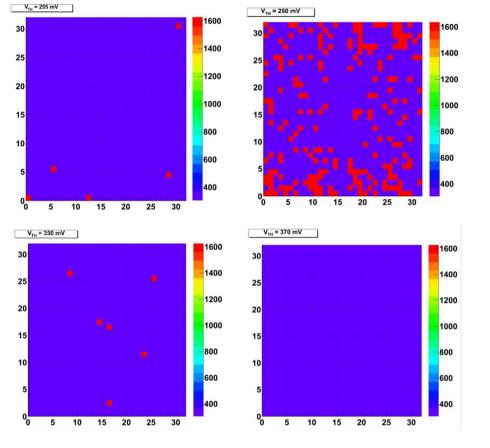

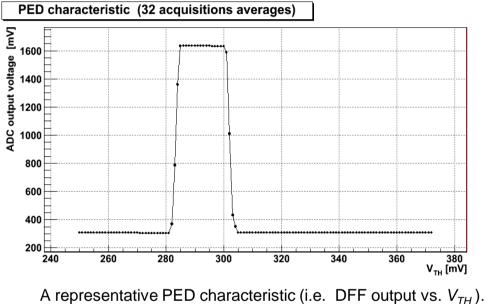

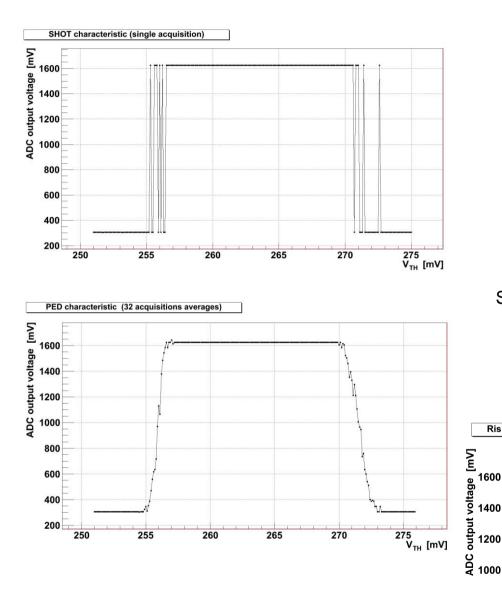

A representative PED characteristic (i.e. DFF output vs.  $v_{TH}$ ) Something interesting occurs in rising and falling edges...

- despite no particle hits can be measured, the front-end electronics register some transitions by varying the threshold voltage

- DFF outputs as a function of the DISC threshold voltage V<sub>TH</sub>

- > each DFF produces a 1 in the 250 to 370 mV threshold range

- $\succ$  if  $V_{TH}$  is too low or exceeds a certain maximum value all DFF ouputs become 0

- > a parasitic signal is superimposed to the baseline  $\rightarrow$  some *noise* affects DISC inputs

1600

1400

1200

800

600

400

200

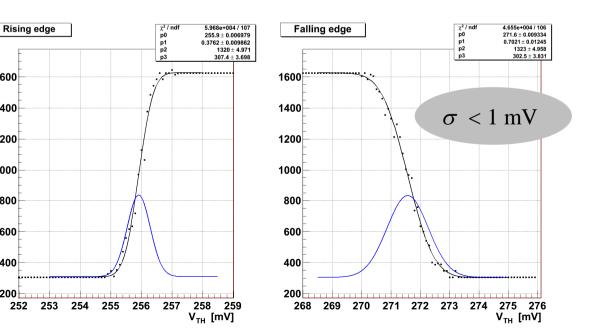

A measurement of thermal voltage fluctuations is obtained by fitting edges with 2 sigmoids

# Edges fine threshold scan

V<sub>TH</sub>

Some thermal noise superimposes to the main parasitic signal

- rising and falling edges SHOT values are indeterminated  $\geq$

- PED values are averages of one by one logic values,  $\triangleright$ resulting at the end in no more logic values

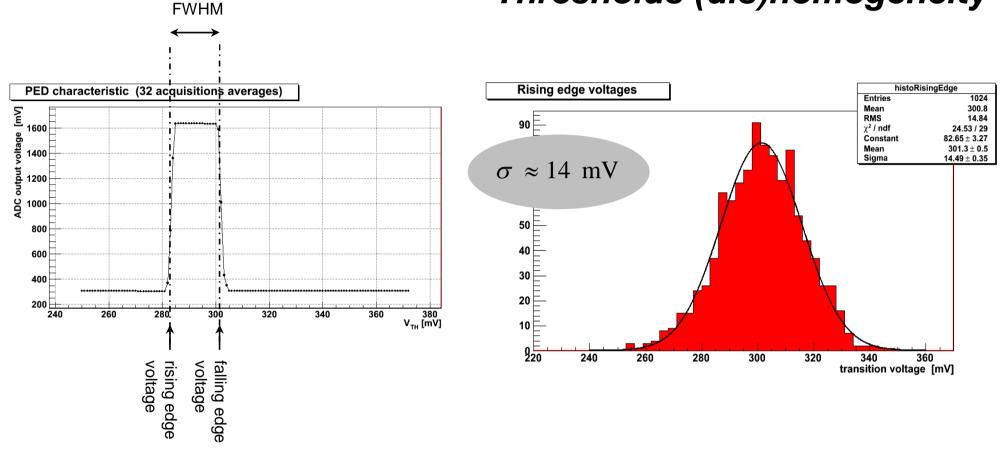

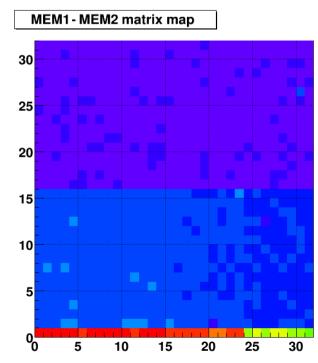

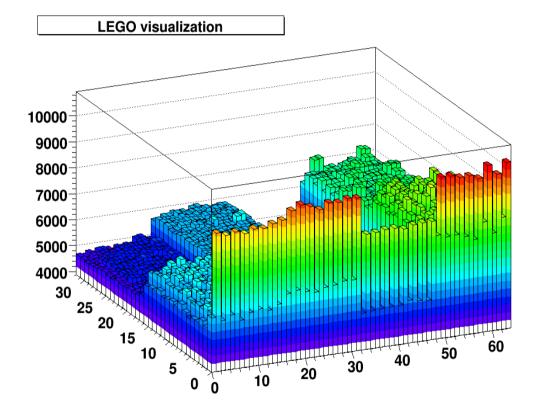

## Thresholds (dis)homogeneity

The set of 1024 DFF outputs shows different edge transition voltages

- > the spread of the distribution quantify the DISC *thresholds dishomogeneity*

- > a Standard Deviation of 14 mV is quite large with respect to the nominal threshold (20 mV above the baseline)

- this dishomogeneity confirms difficulties introduced by the LePix aggressive and non standard layout, necessary to meet the tigh area requirements (e.g. mismatches at the transistor level in DISC devices)

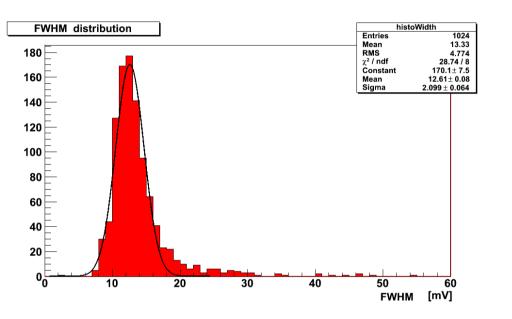

## noise amplitude ~ 10 ÷ 18 mV (Gaussian spread)

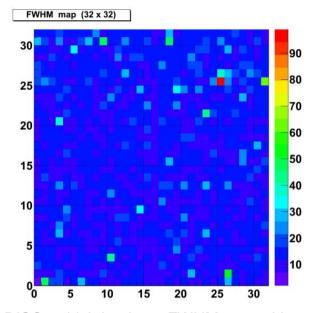

## FWHM distribution

DISCs which lead to a FWHM > 20 mV are scattered randomly. No evidence of a systematic clusterization.

- the FWHM of a PED characteristic represents the noise amplitude

- the set of 1024 DFF outputs shows different FWHM

- Gaussian trend followed by an excess of devices (~10%) affected by a larger noise (FWHM > 18 ÷ 20 mV)

- if the noise is injected before the PREAMP stage, a certain Gaussian spread can be attributed to a dishomogeneity in the PREAMP voltage gains

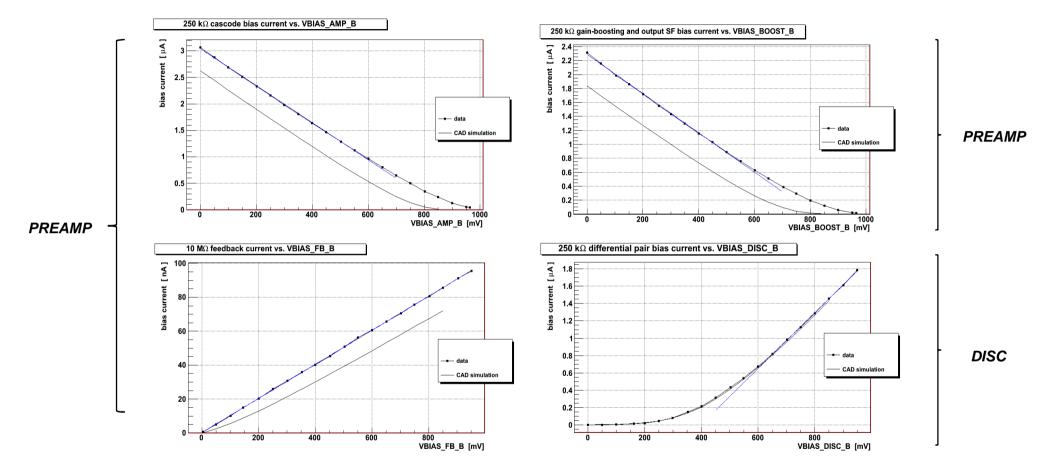

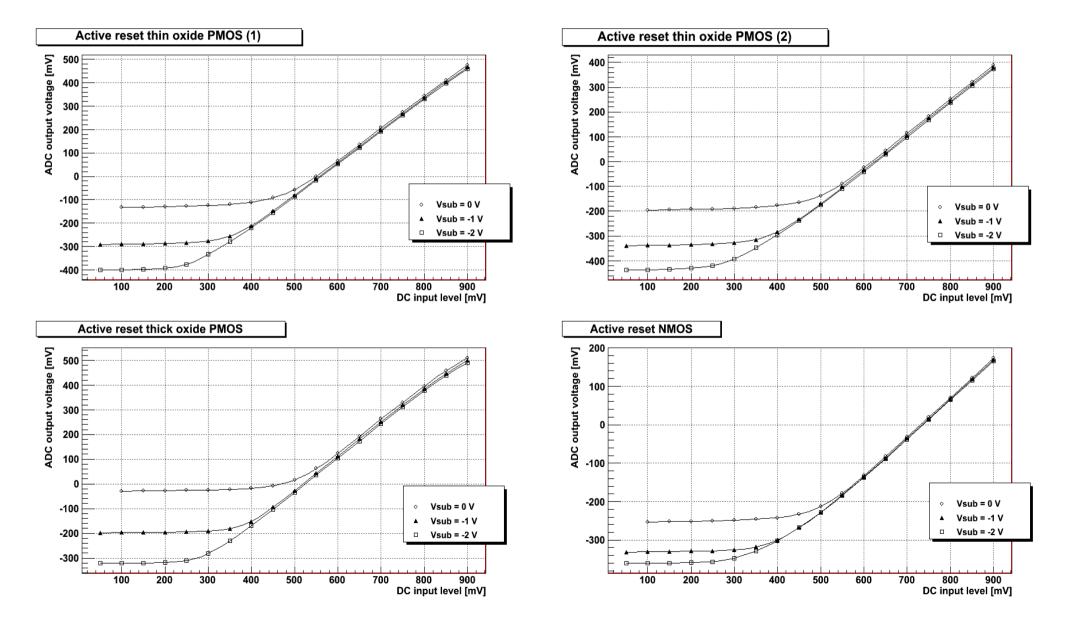

## **Bias characteristics vs. CAD simulations**

devices requires some *bias currents* that must be regulated externally  $\rightarrow$  *trimmers* placed on the external test PCB

- measured bias currents versus trimmer output voltages

- data compared with theoretical values predicted by **DC** simulations

- proper bias voltages must be choosen within the linear regions

some differences between data & simulations  $\rightarrow$  non standard layout

## Conclusions

- the LePix project explores the possibility of implementing monolithic pixel detectors in very deep submicron CMOS technologies with performance adequate for the LHC upgrades and for future HEP experiments

- at present both the ALICE and CMS collaborations have been shown an interest for the project

- within the LePix collaboration the INFN has been an important reference point

- design of matrices 3-4 analog read-out (Turin)

- experimental setup and acquisition software (Padova)

- this thesis has been devoted to the characterization of the matrix prototypes of the first Lepix submission in standard 90 nm CMOS technology, exploiting the experimental setup available in Turin

- setup commissioning and validation of the acquisition software

- development of the software for the off-line data analysis

- pratical design and implementation of the LePix sensor layout are challenging and the first submission with the foundry has shown that the excercise is not easy  $\rightarrow$  discovered a *layout problem*

- > lot on high resistivity put on hold, requiring adequate corrections

- > severe limitations for the characterization of the detector, imposing the pixels exclusion

- > validation of the read-out electronics implemented in first matrix prototypes

- after corrections tests structures on high resistivity substrates have been submitted and they are expected back from the foundry in October 2011 → tests performed on new prototypes will define the actual LePix capabilities

# Thank you for your attention !

# **Backup** slides

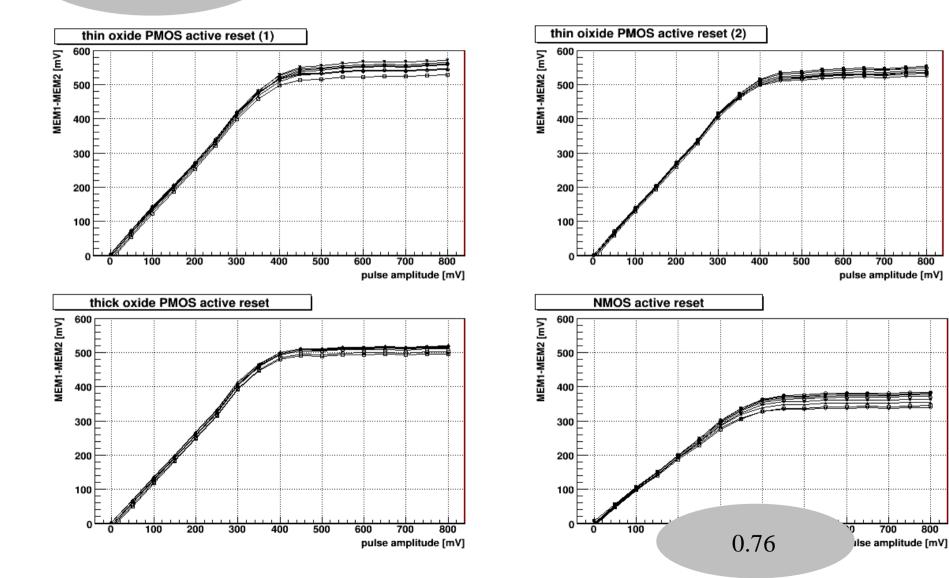

# Matrix 1-2 CORE part characterization

## Double sample analog read-out

Two analog values are stored for each pixel (**double sample**), the difference between these two voltages corresponds to the signal collected by the sensor.

this is an *extremely simple read-out scheme*, designed to optimize the sensor characterization (very similar to traditional serial MAPS)

## Matrix output no PULSE

## Matrix output with PULSE

first column

600 j Σ 500 400

MEM2 MEM1

> -100 -200 -300

> > 0

Waveform structure (2) clock count 16 continuous-reset MEM1 MEM2 voltages [mV] pulsed pixel pulsed pixel -100 clock counts

16 active-reset

## **Pulsed rows**

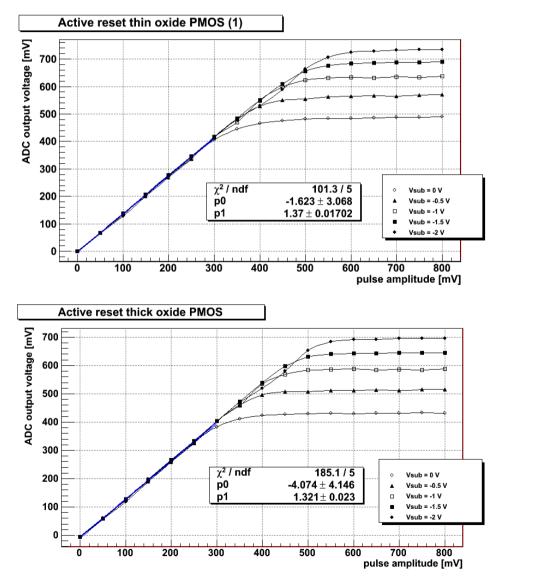

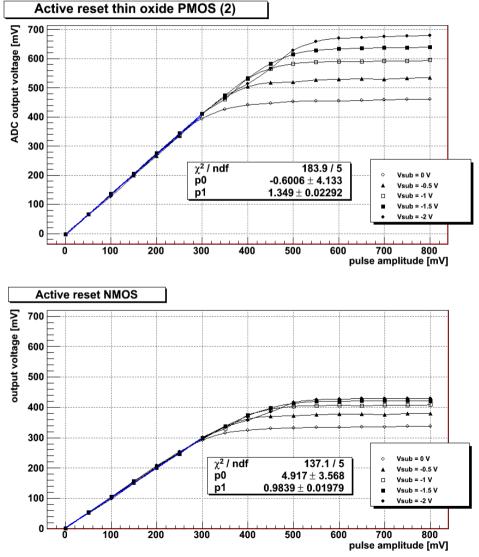

## SFs DC analysis

$0.87 \div 0.89$

SFs gain (active-reset)

## SFs gain vs. reverse bias

## *f* = 100 *kHz*

## SFs gain vs. frequency

### Vsub = -1 V