Università degli Studi di Torino Facoltà di Scienze Matematiche Fisiche e Naturali Dottorato di Ricerca in Fisica – XXI ciclo (A.A. 2005-2008) FIS/01 – Fisica Sperimentale

# The NA62 experiment: Gigatracker readout architecture

Candidato:

Dr. Giulio Dellacasa

Tutore

Dr. Flavio Marchetto

Coordinatore

Prof. Guido Boffetta

16/04/2010

## Contents

| Introduction                                                           | 5  |

|------------------------------------------------------------------------|----|

| Physical motivations                                                   | 9  |

| 2.1 The $K^+ \rightarrow \pi^+ v \bar{v}$ decay and the Standard Model | 9  |

| 2.1 Other physics opportunities                                        | 13 |

| 2.2 Principle of the experiment                                        | 14 |

| Experimental apparatus                                                 | 17 |

| 3.1 The beam for the experiment                                        |    |

| 3.1.1 K <sup>+</sup> tagging                                           | 20 |

| 3.1.2 Beam tracking and momentum measurement                           | 21 |

| 3.1.3 Decay region                                                     | 23 |

| 3.2 Detector overview                                                  | 24 |

| 3.3 The Gigatracker                                                    |    |

| 3.3.1 System architecture and requirements                             |    |

| 3.3.2 The sensor                                                       |    |

| 3.3.3 Cooling and mechanics                                            |    |

| 3.4 Magnetic spectrometer                                              |    |

| 3.5 Photon vetoes system                                               |    |

| 3.5.1 LAV                                                              |    |

| 3.5.2 LKr                                                              |    |

| 3.5.3 Small angle vetoes                                               | 41 |

| 3.6 Charged ANTI counter (CHANTI)                                      |    |

| 3.7 Ring Imaging Cherenkov counters (RICH)                             |    |

| 3.8 Muon vetoes (MUV)                                                  | 44 |

| The Gigatracker readout electronics                                    | 45 |

| 4.1 Chip specifications                                                |    |

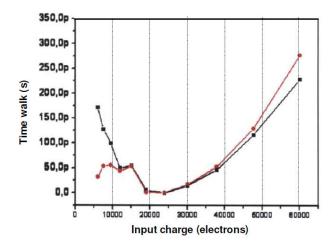

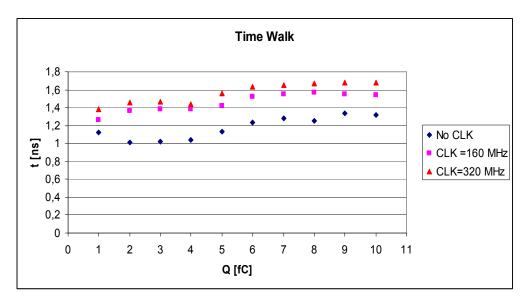

| 4.2 Time walk compensation                                             | 48 |

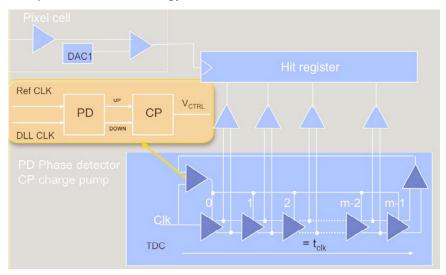

| 4.3 The time measurement                                     | 49  |

|--------------------------------------------------------------|-----|

| 4.4 Off-detector readout electronics                         | 51  |

| 4.5 The End of Column TDC prototype                          | 52  |

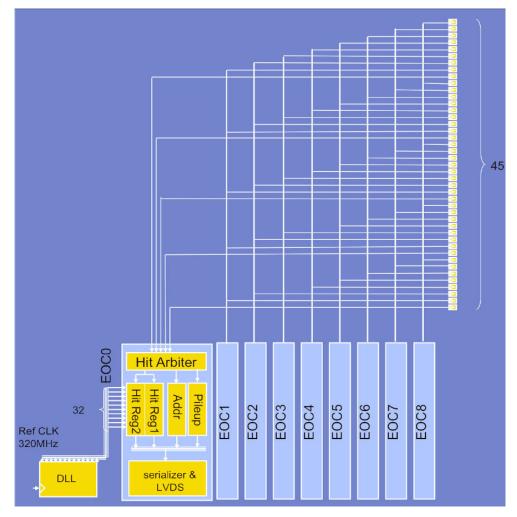

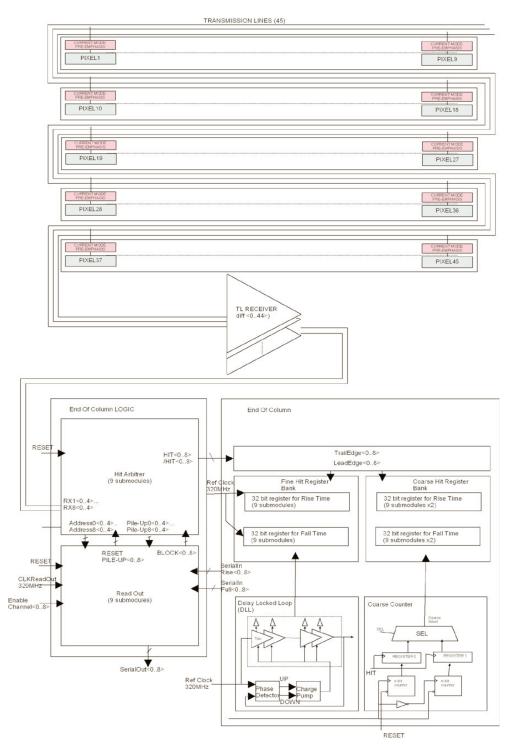

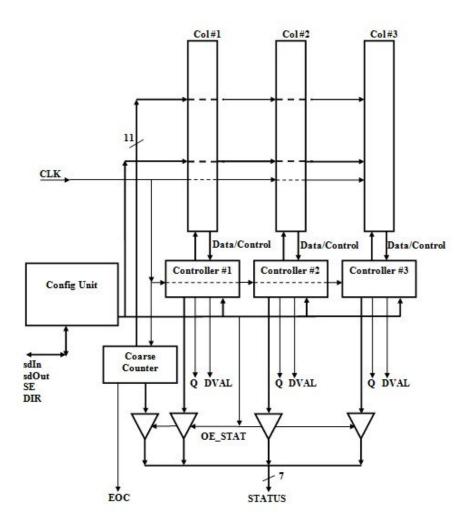

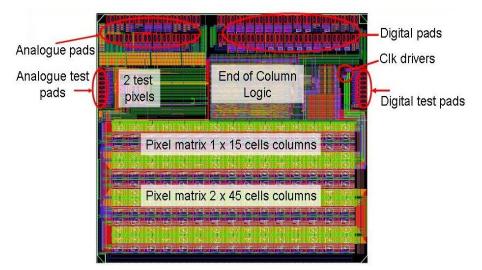

| 4.5.1 Global architecture                                    | 52  |

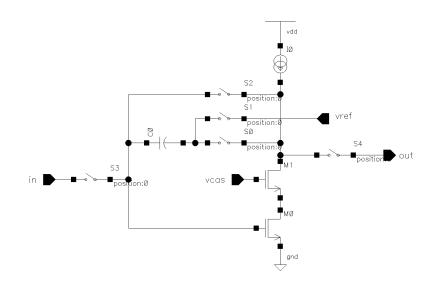

| 4.5.2 The EOC analogue pixel front end                       | 53  |

| 4.5.3 The transmission line                                  | 55  |

| 4.5.4 The End of Column logic                                | 57  |

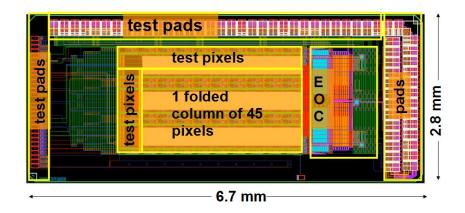

| 4.5.5 End of Column TDC demonstrator                         | 59  |

| 4.5.6 Test setup                                             | 61  |

| 4.5.7 Preliminary results                                    | 62  |

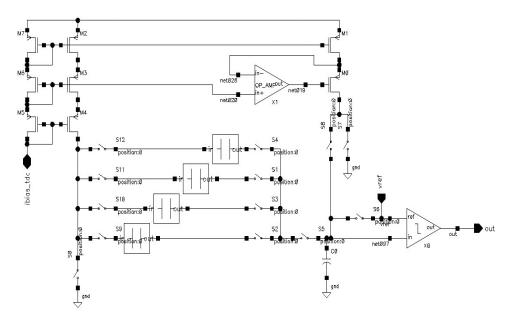

| 4.6 TDC per pixel prototype                                  | 66  |

| 4.6.1 Global architecture                                    | 66  |

| 4.6.2 The P-TDC pixel cell                                   | 68  |

| 4.6.3 Pixel rate simulation                                  | 70  |

| 4.6.4 The analogue blocks in the pixel cell                  | 74  |

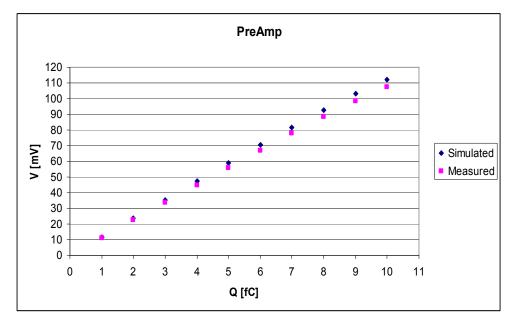

| 4.6.4.1 The preamplifier                                     | 74  |

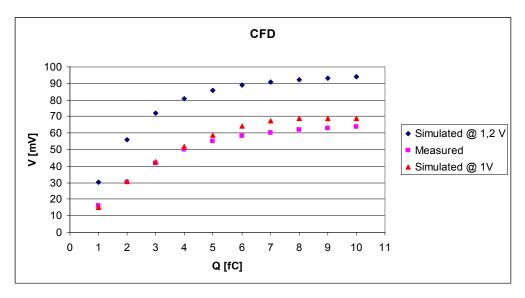

| 4.6.4.2 The constant fraction discriminator filter           | 75  |

| 4.6.4.3 The TAC based TDC                                    | 78  |

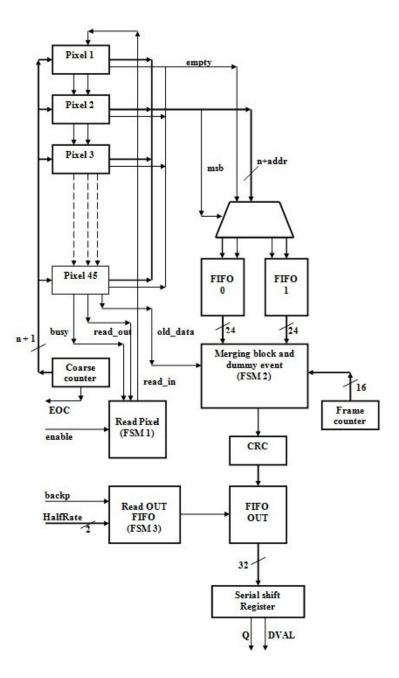

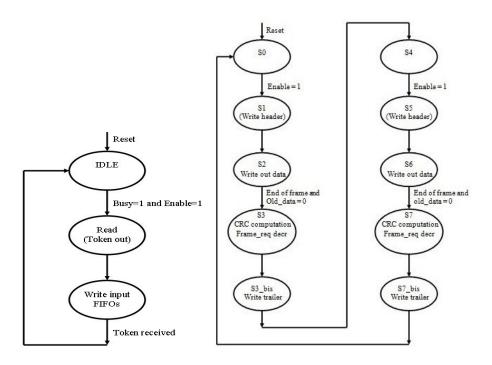

| 4.6.5 The demonstrator chip of the P-TDC architecture        | 80  |

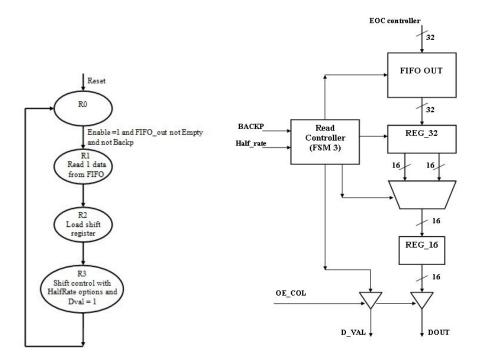

| 4.6.6 The End of Column logic of the P-TDC demonstrator chip | 83  |

| 4.7 Summary on the two readout architectures                 | 90  |

| Preliminary results on the TDC per pixel prototype           | 91  |

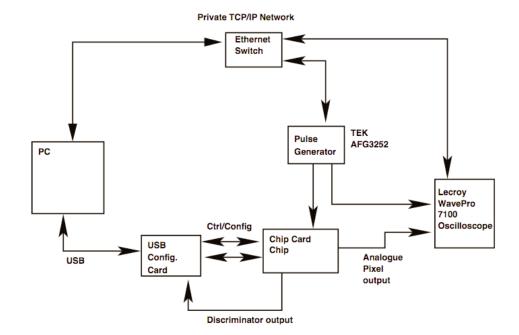

| 5.1 Test setup                                               | 91  |

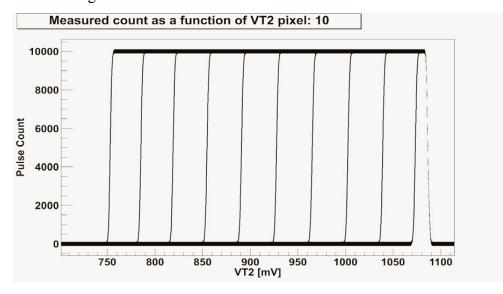

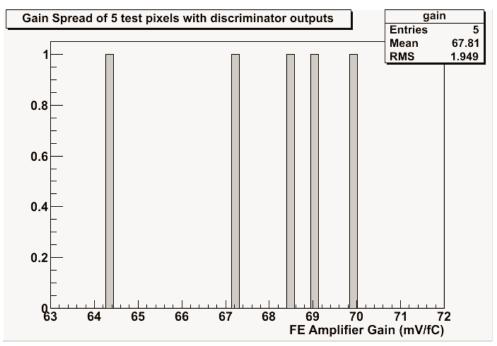

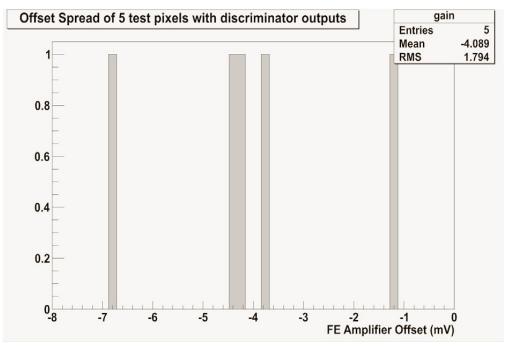

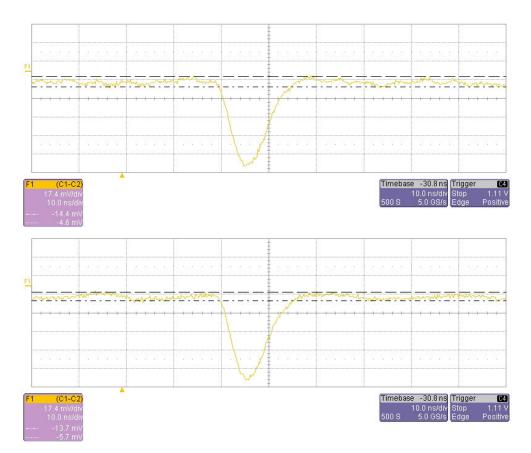

| 5.2 Preliminary analogue results                             | 93  |

| 5.3 Digital tests                                            | 99  |

| Appendix A                                                   | 100 |

| Hamming code implementation                                  | 100 |

| References                                                   | 104 |

| Acknowledgments                                              | 109 |

## Overview

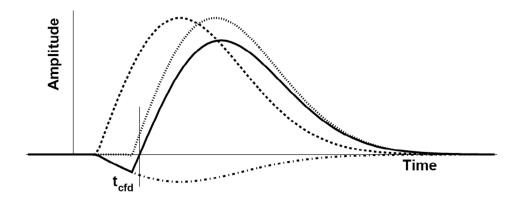

The NA62 experiment at CERN SPS aims to collect 80  $K^+ \rightarrow \pi^+ v \bar{v}$  events. in order to obtain a direct measurement of the CKM matrix parameter V<sub>td</sub>. A crucial detector of the NA62 experiment is the beam spectrometer named Gigatracker. It consists of three stations of hybrid silicon pixels sensors with an overall 150 ps (rms) time resolution and 100 µm (rms) space resolution. In addition the system will operate under a high radiation environment due to the high density of particles (up to 1.5 MHz/mm<sup>2</sup> in the centre corresponding to 0.8 - 1 GHz in total). The time resolution requirement is very challenging and none of the existing systems has such a capability. To achieve this goal the readout electronics must compensate the discriminator time-walk and the dead time should be below 1%. In order to evaluate the best solution, two readout Application Specific Integrated Circuit (ASIC) designs have been developed. One is based on the constant-fraction discriminator technique and the other one is based on the use of a time-overthreshold circuit. The first one is the object of this thesis and it is widely described in this work.

The layout of the thesis is the following: chapter 1 is a short introduction to the kaon physics and the interest in the mainframe of the Standard Model. The second chapter is dedicated to an overall overview of the physics motivations of the experiment NA62. The chapter 3 contains a description of the NA62 detector, with more details on the Gigatracker system. Chapter 4 is dedicated to the electronics readout of the Gigatracker, with the description of the possible architectures under development. Two ASIC prototypes, which have been submitted in 2009, are presented. More details are given for the in pixel TDC architecture, which it is the object of this work. Finally in chapter 5 the preliminary results on the P-TDC demonstrator ASIC are reported.

## **Chapter 1**

### Introduction

Since their discovery by the cosmic radiation [1], K mesons played a very important role in the field of high energy particle physics. In the early 1950s, with the advent of particles accelerators, kaons were studied in details.

A. Pais introduced the *strangeness* [2] to explain the fact that these particles are easily created by strong collisions, but their decay time is much longer than expected by the strong interaction  $(10^{-10}$  seconds instead of the expected  $10^{-23}$ ). It was thus assigned to each particle type an additive quantum number, S, assuming to be conserved by the strong interactions operating in the production, but violated by the weak interactions at the decay. Moreover antiparticle had to have strangeness opposite to the corresponding particle.

Furthermore it appeared that two types of neutral mesons with opposite strangeness were necessary to cope with the observed reactions at the production stage. The two types of neutral mesons were indicated respectively as K<sup>0</sup> with S=+1, and  $\overline{K}^0$  with S=-1. It was then observed that both K<sup>0</sup> and  $\overline{K}^0$  could decay, among a large variety of channels, by weak interaction, thus violating the strangeness, into 2 pions,  $\pi^+ \pi^-$  and  $\pi^0 \pi^0$ , or 3 pions,  $\pi^0 \pi^0 \pi^0$  and  $\pi^+ \pi^- \pi^0$ . The decays show two distinct lifetimes: 5.4 x 10<sup>-8</sup> sec (long-lived) and 8.6 x 10<sup>-11</sup> sec (short-lived).

From the above experimental observations, Gell-Mann and Pais [3] concluded that neutral kaon states of definite mass ( $K^0$  and  $\overline{K}^0$ ) and neutral kaon states of definite lifetime ( $K_1$ : short-lived and  $K_2$ : long-lived) could be related by the following relationship:

$$|K_{1}\rangle \equiv \frac{|K^{0}\rangle + |\overline{K}^{0}\rangle}{\sqrt{2}}, \qquad |K_{2}\rangle \equiv \frac{|K^{0}\rangle - |\overline{K}^{0}\rangle}{\sqrt{2}}$$

and

$$|K^{0}\rangle \equiv \frac{|K_{1}\rangle + |K_{2}\rangle}{\sqrt{2}}, \qquad |\overline{K}^{0}\rangle \equiv \frac{|K_{1}\rangle - |K_{2}\rangle}{\sqrt{2}}$$

where  $K_1 \rightarrow \pi \pi$  is allowed and  $K_2 \rightarrow \pi \pi$  is not permitted.  $K_2$  could decay into  $3\pi$ .  $K_1$  and  $K_2$  are not expected to have the same decay constant and in fact  $K_2$ , which has been observed in 1956 [4], has a lifetime much longer. This is expected due to the phase space volume which is largely different between the 2-pions and 3-pions decays.

The decays of kaons have been fundamental to understand that weak interactions did not conserve parity (P) and charge-conjugation (C).

Following the historical development, it was believed that the eigenvalue of the operator CP has to be conserved, though both separately P and C were not. Based on the decay final states (2 and  $3\pi$ ) of short and long-lived states it was natural assign CP = +1 to K<sub>1</sub> and CP=-1 to K<sub>2</sub>. Thus  $CP|K_1\rangle = +|K_1\rangle$  and  $CP|K_2\rangle = -|K_2\rangle$ .

With these assignments and applying CP to  $K^0$  and  $\overline{K}^0$ , one obtains:  $CP | K^0 >= | \overline{K}^0 > \text{ and } CP | \overline{K}^0 >= | K^0 >.$

In 1964 Christenson, Cronin, Fritch and Turlay studied the decay of the long-lived kaon and detected a substantial probability of decay into two pions. This observation led to the conclusion that CP is violated in weak decays [5]. They measured for the first time the following decay modes ratio:

$$\frac{K_L \to \pi^+ \pi^-}{K_L \to \text{all charged modes}} = (2.0 \pm 0.4) \times 10^{-3}$$

CP violation implies that T symmetry is broken because of the CPT theorem elaborated in 1954 [6] [7]. This fact has been observed in fundamental interactions that have a privileged time direction, where it was expected to be invariant under time reversal symmetry (T). In 1967 Sakharov connected this asymmetry with the matter-antimatter asymmetry in the Universe [8] basing his theory on the CP violation observed in kaons decays.

Several explanations to account for the CP violation have been attempted.

It was however evident that the  $K_1$  and  $K_2$ , states with definite CP eigenvalue, could not be longer interpreted as *short-lived* and *long-lived* particles. To represent these latter states one needs to introduce  $K_S$  and  $K_L$ . In a world where CP was conserved  $K_S = K_1$  and  $K_L = K_2$ . In this non-conserving CP world the above equation do not hold, and are modified into:

$$|K_{S} \ge \frac{|K_{1} > +\varepsilon |K_{2} >}{(1+|\varepsilon|^{2})^{1/2}}$$

and  $|K_{L} \ge \frac{|K_{2} > +\varepsilon |K_{1} >}{(1+|\varepsilon|^{2})^{1/2}}$

where  $\varepsilon$ , which represents the amount of K<sub>2</sub> (K<sub>1</sub>) states in the K<sub>S</sub> (K<sub>L</sub>), ought to be small (~10<sup>-3</sup>). Even if the CP was conserved in the decay, we would observe a CP-noninvariant component  $\varepsilon$ .

Without entering in more details, this picture would have required:

$$\varepsilon = \eta_{+-} = \eta_{00} \qquad \text{where} \quad \eta_{+-} = \frac{amplitudeK_L \to \pi^+ \pi^-}{amplitudeK_S \to \pi^+ \pi^-}$$

and

$$\eta_{00} = \frac{amplitudeK_L \to \pi^0 \pi^0}{amplitudeK_S \to \pi^0 \pi^0}.$$

It was thus clear that only by establishing a deviation between  $\eta_{00}$  and  $\eta_{+}$  one could prove the CP-nonconservation of the decay (or direct CP violation). Observables are usually parameterized as follows.

$$\eta_{+-} = \varepsilon + \varepsilon'$$

and  $\eta_{00} = \varepsilon - 2\varepsilon$

In the recent years several measurements have been performed on the CP-violating ratio  $Re(\Box'/\Box)$ : a deviation from zero would have indicated a direct CP violation. Furthermore, this parameter is strictly related to the elements of the Cabibbo-Kobayashi-Maskawa V<sup>CKM</sup> matrix [9] and can put a constraint on it.

In the middle of 1980's the NA31 experiment at CERN and E731 at Fermilab performed the first measurement on the  $Re(\Box'/\Box)$  parameter, measuring simultaneously K<sub>L</sub> and K<sub>S</sub> decays:

$$R = \frac{\Gamma(K_L \to \pi^0 \pi^0) / \Gamma(K_S \to \pi^0 \pi^0)}{\Gamma(K_L \to \pi^+ \pi^-) / \Gamma(K_S \to \pi^+ \pi^-)} \cong 1 - 6 \operatorname{Re}(\mathcal{E}' / \mathcal{E})$$

NA31 measured  $(23 \pm 6.5) \Box 10^{-4}$  [10], showing the evidence of direct CP violation, while E731 measured  $(7.4 \pm 5.9) \Box 10^{-4}$ .

After that, new experiments have been constructed in 1990's at CERN (NA48) and Fermilab (KTeV) to measure  $Re(\Box'/\Box)$  with a precision of  $(1 \sim 2)\Box 10^{-4}$ , collecting the following results:

- NA48  $(14.7 \pm 2.2) \Box 10^{-4}$  [11]

- KTeV  $(19.2 \pm 2.1) \Box 10^{-4}$  [12]

In the following years the NA48 experiment also studied other rare decays of  $K_S$  (in 2002 under the name of NA48/1) and  $K^+ K^-$  (in 2003-2008 under the name of NA48/2) and the KTeV experiment completed this research program on the rare decays of kaons with the study of  $K_L$  (2008).

Other important studies performed on the K<sup>+</sup> decays have been done at Brookhaven AGS by the experiments E787 and E949. They collected in total seven events of the rare decay  $K^+ \rightarrow \pi^+ v \overline{v}$  measuring a branching ratio of  $(1.73^{+1.15}_{-1.05}) \times 10^{-10}$  [13], in accordance with the Standard Model (SM) prediction of  $(0.85 \pm 0.07) \times 10^{-10}$  [14]. These rare kaons modes offer a big opportunity to study the Standard Model and allow a clean determination of the important parameter V<sub>td</sub> of the CKM matrix. For this a new experiment (called NA62) is under construction at CERN Super Proton Synchrotron (SPS) with the goal of collecting at least 80  $K^+ \rightarrow \pi^+ v \overline{v}$  events.

## **Chapter 2**

## **Physical motivations**

The research program of the NA62 experiment at CERN SPS is to measure the Branching Ratio by accumulating a statistics of 80  $K^+ \rightarrow \pi^+ v \bar{v}$  events or more, with a signal to background ratio of (*S/B*) 10:1, in two years of data taking [15].

#### **2.1** The $K^+ \rightarrow \pi^+ v \overline{v}$ decay and the Standard Model

The study of the rare decays  $K^+ \to \pi^+ v \overline{v}$  and  $K_L \to \pi^0 v \overline{v}$  can give important information on the Standard Model and the Cabibbo-Kobayashi-Maskawa matrix (CKM) [9], completing the results coming out from the B physics. This process is extremely attractive because their rates (small but not negligible) can be calculated in terms of Cabibbo-Kobayashi-Maskawa CKM angles.

The CKM matrix, which connects the weak eigenstates (d', s', b') and the corresponding strong eigenstates, describes the probability of transition between quarks and is defined as follows:

$$\begin{pmatrix} d'\\s'\\b' \end{pmatrix} = \begin{pmatrix} V_{ud} & V_{us} & V_{ub}\\V_{cd} & V_{cs} & V_{cb}\\V_{td} & V_{ts} & V_{tb} \end{pmatrix} \begin{pmatrix} d\\s\\b \end{pmatrix} \equiv \hat{V}_{CKM} \begin{pmatrix} d\\s\\b \end{pmatrix}$$

There are several parameterizations of the CKM matrix in literature, but for present discussion it's convenient to use the Wolfenstein parameterization [16], where the basic parameters are:

$$\lambda, \qquad A = \frac{|V_{cb}|}{\lambda^2}, \qquad \overline{\rho} = \rho(1 - \frac{\lambda^2}{2}), \qquad \overline{\eta} = \eta(1 - \frac{\lambda^2}{2})$$

In this parameterization each element of the CKM matrix is expanded as a power series in the small parameter  $\lambda = |V_{us}| \approx 0.22$ .

$$\hat{V}_{CKM} = \begin{pmatrix} 1 - \frac{\lambda^2}{2} & \lambda & A\lambda^3(\rho - i\eta) \\ -\lambda & 1 - \frac{\lambda^2}{2} & A\lambda^2 \\ A\lambda^3(1 - \rho - i\eta) & -A\lambda^2 & 1 \end{pmatrix} + O(\lambda^4)$$

Because of the smallness of  $\lambda$  and the fact the expansion parameter is  $\lambda^2$ , it's normally sufficient to consider only the first few terms in the expansion. The diagonal elements are close to unity,  $|V_{cd}|$  and  $|V_{us}|$  of the order 0.2, the elements  $|V_{cb}|$  and  $|V_{ts}|$  of the order 4 10<sup>-2</sup>,  $|V_{ub}|$  and  $|V_{td}|$  of the order 5 10<sup>-3</sup>. The constraints of unitarity for the CKM matrix can be written as follows:

$$\sum_{k} |V_{ik}|^{2} = 1$$

for the diagonal elements

$$\sum_{k} V_{ik} V_{jk}^{*} = 0$$

for the other elements

This implies a set of equations, but for the present purpose we can use:

$$V_{us}^* V_{ud} + V_{cs}^* V_{cd} + V_{ts}^* V_{td} = 0$$

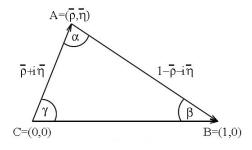

which identifies a unitarity triangle on the complex plane  $(\rho,\eta)$ .

Fig.2.1 Unitarity triangle

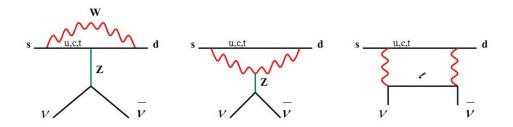

At the quark level, in the Standard Model, the two decays  $K^+ \to \pi^+ v \overline{v}$  and  $K_L \to \pi^0 v \overline{v}$  come from the  $s \to dv \overline{v}$  process and they are described by the  $Z_0$  penguin and the box diagram with a double W exchange.

Fig.2.2 Rare K decays in the Standard Model.

The active GIM mechanism implies on the decay amplitude the approximation  $A_q \approx \frac{m_q^2}{M_W^2} V_{qs}^* V_{qd}$  (where q are the *up*, *charm* or *top* quarks, u, c, t). For the mass values and the CKM elements involved, it's clear that the up-quark contribution is always negligible, while the top-quark dominates the process (the charm-quark has a smaller contribution in the decay  $K^+ \rightarrow \pi^+ v \bar{v}$ ). Since this is a short-distance process it can be described by a Fermi-like coupling with the following effective Hamiltonian:

$$\mathbf{H}_{eff} = \sum_{l=e,\mu,\tau} \frac{G_l}{\sqrt{2}} (\bar{s}d)_{V-A} (\overline{v_l}v_l)_{V-A}$$

where  $G_l$ , the effective coupling constant, is the sum of two elements, arising from the top-quark and the charm-quark:

$$G_{l} = \frac{\alpha G_{F}}{2 \pi \sin^{2} \Theta_{W}} [V_{ls}^{*} V_{ld} X(x_{l}) + V_{cs}^{*} V_{cd} X_{NL}^{l}]$$

where  $x_t = \frac{m_t^2}{M_W^2}$ . The coefficients  $X(x_t)$  and  $X_{NL}^l$ , which encode the top

and the charm-quark contributions, are calculated at NLO level [17, 18, 19]. The top-quark part is precisely computed, with a small error arising from the uncertainty of the top-quark mass. The smaller part of the charm-quark has the largest theoretical uncertainty, which cause an error of ~5-7% on the determination of V<sub>td</sub>. With the given definitions the branching fraction of  $K^+ \rightarrow \pi^+ v \bar{v}$  and  $K_L \rightarrow \pi^0 v \bar{v}$  can be written as:

$$BR(K^{+} \to \pi^{+} \upsilon \overline{\upsilon}) = 6r_{k^{+}} BR(K^{+} \to \pi^{0} e^{+} \upsilon) \frac{|G_{l}|^{2}}{G_{F}^{2} |V_{us}|^{2}}$$

$$BR(K^{0} \to \pi^{0} \upsilon \overline{\upsilon}) = 6\frac{\tau_{K_{L}}}{\tau_{K^{+}}} r_{K_{L}} BR(K^{+} \to \pi^{0} e^{+} \upsilon) \frac{(\mathrm{Im} G_{l})^{2}}{G_{F}^{2} |V_{us}|^{2}}$$

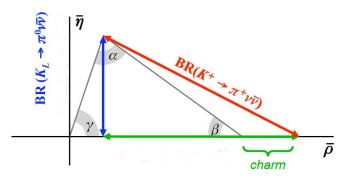

The measurement of both branching ratios would provide two independent elements on the unitarity triangle.  $BR(K^+ \rightarrow \pi^+ v \bar{v})$  defines an ellipse in the  $\bar{\rho} - \bar{\eta}$  plane (the charm-quark contribution to  $G_l$ , which depends on V<sub>cs</sub> and V<sub>cd</sub>, is a real number) and  $BR(K_L \rightarrow \pi^0 v \bar{v})$  a vertical line (the height of the unitarity triangle).

Fig.2.3 Unitarity triangle and rare K decays.

Since in the described approximations  $V_{ts} = -V_{cb}$  (and the latter is well extracted from *B* decays [20]), the measurement of the two branching ratios for the two kaon decays, will provide a direct measurement of the  $G_l$  coupling constant and thus the determination of the V<sub>td</sub> parameter. In addition combing these measurements with the existing data on the  $\beta$  angle and the  $B^0 \overline{B}^0$  oscillations, it will perform an exhaustive test on the Standard Model (for a detailed review of the CKM matrix and the rare kaon decays, please refer to [21] and [22]).

At the present the theoretical predictions for the two branching ratios within the Standard Model are:

$$K^+ \to \pi^+ \upsilon \upsilon = (0.85 \pm 0.07) \times 10^{-10} [14]$$

$$K_L \to \pi^0 v \overline{v} = (3.0 \pm 0.6) \times 10^{-11} [22]$$

Preliminary experimental results for the K<sup>+</sup> decay are given by the E787 and E949 collaborations at Brookhaven National Laboratory:

$$BR(K^+ \to \pi^+ \nu \overline{\nu}) = (1.73^{+1.15}_{-1.05}) \times 10^{-10}$$

(which are based on seven events in the entire E787+E949 data sample [13]).

For the  $K_L$  decay un upper limit has been set by the experiment E391a at KEK 12-GeV proton synchrotron [23]:

$$K_L \to \pi^0 v \bar{v} < 6.7 \times 10^{-8} (90\% \text{ C.L.})$$

In this general framework the NA62 experiment will play an important role in the following years, completing these results.

#### 2.1 Other physics opportunities

The new experimental setup for the NA62 experiment will provide an excellent resolution on the photon energy that will allow the study of radiative kaon decays with a precision never reached before. In addition the experimental apparatus can be used for many measurements on others rare kaon decays.

Moreover the study of rare kaon decays can give important inputs for physics beyond the Standard Model. The  $BR(K^+ \rightarrow \pi^+ v \bar{v})$  measured at Brookhaven seems to be larger than the predicted value within the Standard Model. A possible interpretation of this result can be found in the supersymmetric models, replacing the W boson with new particles like *charged Higgs, charginos* and *stops*. Possible scenarios of new physics contributions in the  $s \rightarrow d\bar{v}v$  amplitude and in  $B\bar{B}^0$  mixing are described in [24].

#### 2.2 Principle of the experiment

The goal of the experiment is to collect at least 80  $K^+ \rightarrow \pi^+ v \bar{v}$  events in two years with a signal to background ratio S/B=10:1. Considering the impossibility to measure the two neutrinos in the final state, the experiment requires an adequate strategy to optimize the kinematic measurements and the veto system. The main source of background, arising from the two body decays, mainly  $K^+ \rightarrow \pi^+ \pi^0$  and  $K^+ \rightarrow \mu^+ v$ , which have branching ratios  $10^{10}$  times larger than the expected signal, must be suppressed. Also, the reconstruction of the two-body kinematics, can be done only with a precise photon detection in conjunction with a good Particle Identification (PID). In addition also the three-body decays give a contribution to the background and they must be taken in account. The following table shows the  $K^+$  decay modes that can contribute to the background and the rejection handles.

| Decay mode                  | Branching ratio               | Background rejection              |  |

|-----------------------------|-------------------------------|-----------------------------------|--|

| $K^+ \to \mu^+ \nu$         | 63% (called K <sub>µ2</sub> ) | μ PID, two-body kinematics        |  |

| $K^+ 	o \pi^+ \pi^0$        | 21%                           | Photon veto, two-body kinematics  |  |

| $K^+ \to \pi^+ \pi^+ \pi^-$ | 6%                            | Charged particle veto, kinematics |  |

| $K^+ \to \pi^+ \pi^0 \pi^0$ | 2%                            | Photon veto, kinematics           |  |

| $K^+ \to \pi^0 \mu^+ \nu$   | 3% (called $K^{+}_{\mu3}$ )   | Photon veto, µ PID                |  |

| $K^+ \to \pi^0 e^+ \nu$     | 5% (called $K_{e3}^+$ )       | Photon veto, E/p                  |  |

Table 2.1  $K^+$  decay modes and rejection criteria.

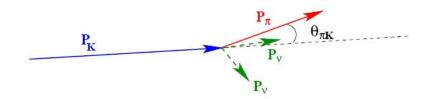

The kinematic of the decay under study can be represented as follows.

Fig. 2.4 Kinematics of  $K^+ \rightarrow \pi^+ \upsilon \overline{\upsilon}$ .

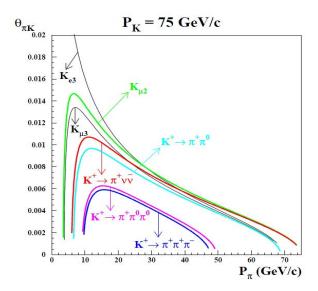

Fig. 2.5 Angle-momentum relation for  $K^+$  decays.

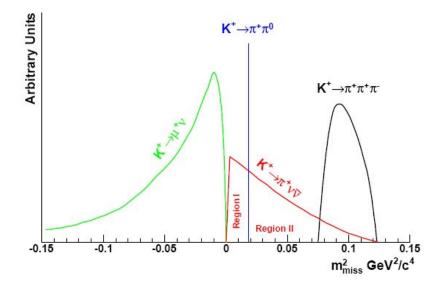

The measurable quantities are: the momentum of the incoming  $K^+$  (P<sub>K</sub>), the momentum of the outgoing  $\pi^+$  (P<sub> $\pi$ </sub>), and the angle between them ( $\theta_{\pi K}$ ). In order to separate the signal from the background, two acceptance regions can be defined. Under the hypothesis that the charged final state is a pion and the angle  $\theta_{\pi K}$  is small one can define the squared missing mass,  $m^2_{miss}$ , as:

$$m_{miss}^{2} \cong m_{K}^{2} \left(1 - \frac{|P_{\pi}|}{|P_{K}|}\right) + m_{\pi}^{2} \left(1 - \frac{|P_{K}|}{|P_{\pi}|}\right) - |P_{K}||P_{\pi}|\theta_{\pi K}^{2}$$

Assuming  $P_K = 75 \ GeV/c$ , corresponding of the central value of the beam momentum at the CERN SPS,  $m_{miss}^2$  distributions for the signal and for the other most probable  $K^+$  decays are somewhat in overlapping regions. In particular the squared missing mass of  $K^+ \rightarrow \pi^+ \pi^0$  has a fixed value of  $m_{miss}^2 = m_{\pi^0}^2$  (represented by a line) which is in the signal region. To cut out the 2-pion decays, the acceptance area must be divided in two regions (where  $\Delta m$  depends on the  $m_{miss}^2$  resolution):

• Region I:  $0 < m_{miss}^2 < m_{\pi^0}^2 - (\Delta m)^2$

• Region II:  $m_{\pi^0}^2 + (\Delta m)^2 < m_{miss}^2 < \min[m_{miss}^2(\pi^+\pi^+\pi^-)]$

The definition of Region II also rejects the three body decay  $K^+ \rightarrow \pi^+ \pi^- \pi^-$  (see Fig. 2.6).

Fig. 2.6 Squared missing mass distributions.

Simulations show that to reach  $S/B \ge 10$  it is necessary to fix the squared missing mass resolution at  $(\Delta m)^2 \approx 8 \times 10^{-3} GeV^2/c^4$  [15]. This value puts the constraints on the required performance of the two spectrometers which take part of the NA62 detector (refer to Chapter 3 for details). Also, to suppress the background arising from most probable  $K^+$  decays, the detector should provide an efficient  $\gamma$  detection to reject  $\pi^0$  decays. Finally  $\pi^-$  and  $\mu^+$ can be suppressed respectively with the wrong-charge deflection and particle identification, as explained in detail in the next chapter.

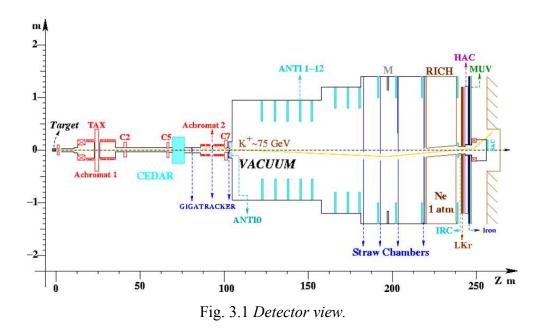

## Chapter 3 Experimental apparatus

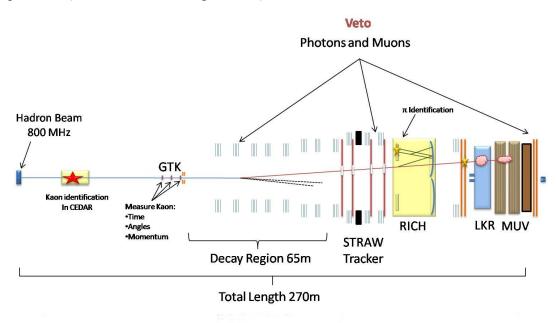

NA62 is a fixed target experiment making use of the proton beam of the CERN SPS to produce the  $K^+$  flux. The following picture is the section view of the entire detector, where the proton beam comes from the left. In this chapter it will be given a description of each sub-detector, focusing more on the Gigatracker system which is the object of the present work.

To better understand Fig. 3.1 refer to the acronyms list below:

- CEDAR: Cherenkov Differential counter with Achromatic Ring focus

- GIGATRACKER: silicon pixel detectors for momentum and time measurements

- ANTI: Anti-counters (Large Angle photon Veto)

- RICH: Ring Imaging Cherenkov detector

- LKr: Liquid Krypton calorimeter

- IRC: Intermediate Ring Calorimeter (photon veto)

- SAC: Small Angle Calorimeter (photon veto)

- HAC: the NA48 Hadronic Calorimeter (muon veto)

- MUV: MUon Veto system

#### 3.1 The beam for the experiment

The charged kaon beam for the experiment is derived from the primary proton beam at 400 GeV/c of the SPS colliding a beryllium target. The high energy of the primary beam gives some advantages. With the use of an empirical formula [25] can be calculated that the maximum  $K^+$  production, per primary proton of fixed momentum  $p_0$ , occurs for  $p_K \approx 0.35 p_0 (0.23$ for  $K^-$ ). In addition  $K^+$  ( $K^-$ ) production increases as  $p_K^2$  (and so as  $p_0^2$ ). It can be calculated that the maximum number of  $K^+$  decays, in the defined length range constrained by the detector geometry, is maximum when  $p_K \approx 0.23 p_0$  (0.15 for  $K^-$ ) and it increases as  $p_K$  (and therefore as  $p_0$ ). Moreover, at high energy, detectors like calorimeters, photon veto counters and muon detectors, have better performances in terms of acceptance, resolution, and efficiency. The choice of a positive kaon beam is motivated by the ratio of the production rates:  $K^+/K^- \approx 2.1$  (per 400 GeV/c proton beam).

A kaon momentum of 75 GeV/c has been chosen as central value. This is a compromise of the parameters listed in table 3.1. The number of produced  $K^+$  and the percentage in the beam increases with the momentum, but there are other aspects to take into consideration: the distance of the decay region (102 m from the target), the length of decay region itself, 50 m, and the detector acceptance: particles near the beam pipe can not be detected. The kaon fluxes listed in table 3.1 are the results of the combinations between

| $p_{K}$ [GeV/c]                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 75                                                                                                                                                                                                                                                                                                    | 120                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| p x 10 <sup>6</sup>                                                                        | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 171                                                                                                                                                                                                                                                                                                   | 550                                                                                                                                                                                                                                                                                                                                            |

| $K^{+} \ge 10^{6}$                                                                         | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 53                                                                                                                                                                                                                                                                                                    | 71                                                                                                                                                                                                                                                                                                                                             |

| $\pi^+ \ge 10^6$                                                                           | 353                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 532                                                                                                                                                                                                                                                                                                   | 825                                                                                                                                                                                                                                                                                                                                            |

| Total x 10 <sup>6</sup>                                                                    | 482                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 756                                                                                                                                                                                                                                                                                                   | 1446                                                                                                                                                                                                                                                                                                                                           |

| $K^+$                                                                                      | 0,797                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0,834                                                                                                                                                                                                                                                                                                 | 0,893                                                                                                                                                                                                                                                                                                                                          |

| $\pi^+$                                                                                    | 0,970                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0,976                                                                                                                                                                                                                                                                                                 | 0,985                                                                                                                                                                                                                                                                                                                                          |

| p x 10 <sup>6</sup>                                                                        | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 173                                                                                                                                                                                                                                                                                                   | 550                                                                                                                                                                                                                                                                                                                                            |

| $K^{+} \ge 10^{6}$                                                                         | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 45                                                                                                                                                                                                                                                                                                    | 63                                                                                                                                                                                                                                                                                                                                             |

| $\pi^{+} \ge 10^{6}$                                                                       | 343                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 525                                                                                                                                                                                                                                                                                                   | 813                                                                                                                                                                                                                                                                                                                                            |

| Total x $10^6$                                                                             | 464                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 743                                                                                                                                                                                                                                                                                                   | 1426                                                                                                                                                                                                                                                                                                                                           |

| $K^{+} \ge 10^{6}$                                                                         | 3,9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4,5                                                                                                                                                                                                                                                                                                   | 4,1                                                                                                                                                                                                                                                                                                                                            |

| $\pi^{+} \ge 10^{6}$                                                                       | 6,1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7,4                                                                                                                                                                                                                                                                                                   | 7,2                                                                                                                                                                                                                                                                                                                                            |

|                                                                                            | 0,64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0,61                                                                                                                                                                                                                                                                                                  | 0,57                                                                                                                                                                                                                                                                                                                                           |

| $K^+$ decays in 60 m / total hadron flux x 10 <sup>-3</sup>                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6,1                                                                                                                                                                                                                                                                                                   | 2,9                                                                                                                                                                                                                                                                                                                                            |

| $K^+ \rightarrow \pi^+ v \overline{v}$ acceptance (Region I, no $p_{\pi}$ cut)             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0,11                                                                                                                                                                                                                                                                                                  | 0,11                                                                                                                                                                                                                                                                                                                                           |

| Accepted $K^+ \rightarrow \pi^+ v \bar{v} / 10^{12}$ proton per s x10 <sup>6</sup> xB.R.   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0,50                                                                                                                                                                                                                                                                                                  | 0,45                                                                                                                                                                                                                                                                                                                                           |

| Accepted $K^+ \rightarrow \pi^+ v \bar{v} / \pi^+$ decays in 60 m x B.R.                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0,067                                                                                                                                                                                                                                                                                                 | 0,062                                                                                                                                                                                                                                                                                                                                          |

| Accepted $K^+ \rightarrow \pi^+ v \overline{v}$ /total hadron flux x10 <sup>-3</sup> xB.R. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0,67                                                                                                                                                                                                                                                                                                  | 0,31                                                                                                                                                                                                                                                                                                                                           |

|                                                                                            | $K^{+} \times 10^{6}$ $\pi^{+} \times 10^{6}$ Total x 10 <sup>6</sup> $K^{+}$ $\pi^{+}$ $p \times 10^{6}$ $K^{+} \times 10^{6}$ $\pi^{+} \times 10^{6}$ Total x 10 <sup>6</sup> $K^{+} \times 10^{6}$ $\pi^{+} \times 10^{6}$ Total x 10 <sup>6</sup> $x^{+} \times 10^{6}$ $\pi^{+} \times 10^{6}$ | $K^+ x 10^6$ 40 $\pi^+ x 10^6$ 353Total x 10^6482 $K^+$ 0,797 $\pi^+$ 0,970 $p x 10^6$ 89 $K^+ x 10^6$ 32 $\pi^+ x 10^6$ 343Total x 10^6464 $K^+ x 10^6$ 3,9 $\pi^+ x 10^6$ 6,1 $0,64$ 0,64 $10^{-3}$ 8,4 $o_{\pi}$ cut)0,08 $c s x 10^6 x B. R.$ 0,31 $0 m x B. R.$ 0,052 $x x 10^{-3} x B. R.$ 0,67 | p x 10689171 $K^+ x 106$ 4053 $\pi^+ x 106$ 353532Total x 106482756 $K^+$ 0,7970,834 $\pi^+$ 0,9700,976p x 10689173 $K^+ x 106$ 3245 $\pi^+ x 106$ 343525Total x 106464743 $K^+ x 106$ 3,94,5 $\pi^+ x 106$ 3,94,5 $\pi^+ x 106$ 6,17,4 $0,64$ 0,61 $10^{-3}$ 8,46,1 $o_{\pi}$ cut)0,080,11 $c x x 10^6 x B.R.$ 0,310,50 $m x B.R.$ 0,0520,067 |

measured particle rates and the estimation made with the use of an empirical formula [25].

Table 3.1  $K^+$  production and decay parameters for different  $p_k$  values.

The primary proton beam used to produce the  $K^+$  beam, previously has served the experiments NA48 [26] and NA48/2 [27] to produce the  $K^0_L$  and the  $K^+ K^-$  beams. The extracted 400 GeV/c proton beam from the SPS North Area is split into three branches hitting targets T2, T4 and T6. At the target station T4 a system of magnets provides the transport of protons that have not interacted, up to the experimental cavern ECN3. For a detailed overview of the beam layout refer to [28]. For the extraction of the secondary hadron beam it is planned to reuse the existing target station T10 and to install the new beam along the existing K12 beam line. At T10 the primary protons are focused with zero angle over the beryllium target, which is suspended between aluminium foils and cooled by forced convection. The  $K^+$  momentum selection and positron suppression are performed by a system of quadrupoles and motorized beam collimators (TAX). A listing of the layout and geometry of the new  $K^+$  beam for the NA62 experiment can be found in the *BEATCH* file attached in [28].

#### **3.1.1** K<sup>+</sup> tagging

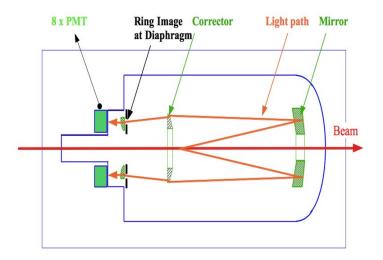

The secondary beam it is not a pure  $K^+$  beam but many other particle types cause the increment of the flux in the upstream detectors up to 17 times larger than the useful one. For this reason the  $K^+$  particles in the secondary beam must be identified with respect to pions and protons components by the differential Cerenkov counter (CEDAR). The detector is housed in a steel pressure vessel of 558 mm diameter, filled with hydrogen gas [28] at a pressure of about 4 bar.

Fig. 3.2 CEDAR detector.

The Cerenkov angle of the light produced by the particles traversing the vessel is function of their masses. The light is reflected by a spherical mirror

and detected by eight photomultipliers. The coincidence of at least six of them detects the passage of a particle. Trimming the pressure of the gas it is possible to transmit through the diaphragm only the light produced by a  $K^+$  particle at a given angle, whilst light associated to protons and pions will be stopped. The rate in the detector is limited to 50 MHz, which corresponds to the kaon rate in the beam.

Finally, to increase the efficiency of the light collection, a system of corrector lenses redirect the light rays to the diaphragm with the same radius independently on the wavelength and point of emission.

NA62 will use un update version of the *West CEDAR* built for the SPS secondary beams [29]. The main requirements are listed in table 3.2.

| Time resolution            | < 100 ps |

|----------------------------|----------|

| Number of photons per Kaon | 100      |

| Kaon rate                  | 50 MHz   |

| Rate per photomultiplier   | 3 MHz    |

| Efficiency                 | > 95%    |

Table 3.2 CEDAR main parameters.

The existing CEDAR must be adapted in order to meet the NA62 specifications. In particular new photodetectors and readout electronics are needed to manage the high kaon rate. As consequence also the light transport system must be re-designed [28]. At the moment the choice of the photodetector is based on a conventional vacuum photomultiplier tube with quartz window (Hamamatsu R7400P).

#### 3.1.2 Beam tracking and momentum measurement

The beam tracking system consists of three stations of silicon pixels detectors, installed in vacuum over the beam line, named Gigatracker. It will be described in detail in section 3.3. Of relevance for the beam is the deflecting system. A pair of quadrupoles match the beam through the three

stations of the Gigatracker and limits the beam size at the downstream detectors. Between the GTK1 and the GTK3 is placed an "achromat" composed of four dipole magnets, vertically deflecting the beam. The yokes of the first three magnets are installed below the beam (down) whereas the fourth is placed above (Up).

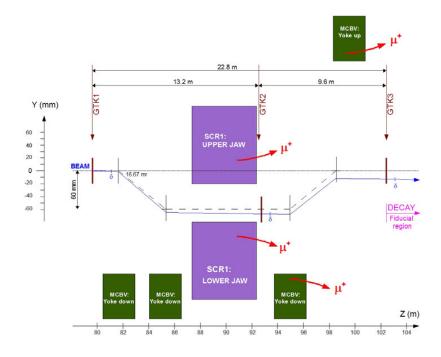

Fig. 3.3 Schematic layout of the beam tracking and momentum measurement system.

The effect of the resulting magnetic field is the defocusing action on the  $\mu^+$ , produced by the iron collimator SCRAPED 1 (SCR1). The lower jaw, placed 20 mm below the beam, deflects away the  $\mu^+$  of momenta < 55 GeV/c, which are travelling along the K<sup>+</sup> and  $\pi^+$  beam at 75 GeV/c. Moreover the upper jaw stops the undeviated particles assuring that no neutrals (K<sup>0</sup><sub>L</sub> and neutrons) or negative charged ( $\pi^-$  and K<sup>-</sup>) can be transmitted through the downstream detectors. The amount of displacement along the vertical axis of the GTK2 station respect the other two stations

(following the 75 GeV/c beam path) provides the momentum measurement with a resolution of  $\sim 0.2$  %.

#### 3.1.3 Decay region

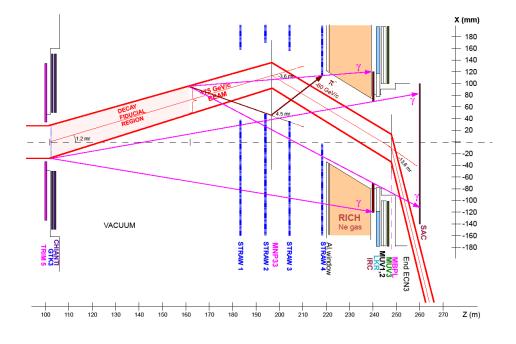

The decay fiducial region is contained in the first 60 m of the evacuated tank located immediately after the Gigatracker station 3. Then the beam is transported to the downstream detectors through a thin aluminium window traversed by the beam tube (of diameter  $\sim$ 155 mm).

Fig. 3.4 Vacuum tank and decay fiducial region.

The detectors installed in the vacuum tank are described in the next sections. But concerning the beam it is important to spend a few words about the single magnetic spectrometer, which is composed by four straw-tubes chambers covering the whole acceptance area except  $\pm 60$  mm around the beam path. Between the four chamber is installed the dipole magnet MNP33 which deflect the 75 GeV/c beam by -3.6 mrad in order to focus the beam to the undeviated axis at the beginning of the LKr calorimeter. Besides tagging the  $\pi^+$  candidates from the K<sup>+</sup> decays, the spectrometer detects the  $\pi^-$  originating from the  $K^+_{e4}$  decays ( $K^+ \to \pi^+ \pi^- e^+ \nu$ ), with momentum up to 60 GeV/c, deflected by the magnet by +4.5 mrad.

At the exit of the LKr calorimeter a pair of filament scintillators provides a further position measurement. The beam is finally deviated by -13.6 mrad to avoid the interaction with the Small Angle Calorimeter (SAC) and then dumped in concrete blocks placed at the end of the cavern ECN3.

#### **3.2 Detector overview**

As described in section 2.2 the rate of decay  $K^+ \rightarrow \pi^+ v \bar{v}$  is  $10^{10}$  times lower than the background sources (table 2.1). Therefore an accurate particle identification, a robust photon vetoes system in conjunction with the muon rejection are mandatory for the NA62 detector. Besides that the detector requires a high resolution timing to support the high rate of particles (~800 MHz at the Gigatracker).

Fig. 3.5 Detector elements and their function.

The squared missing mass defined in 2.2 is related to the K<sup>+</sup> and  $\pi^+$  momenta and defines the acceptance regions for the signal, Region I:  $0 < m_{miss}^2 < 0.01 \, GeV^2 / c^4$  and Region II:  $0.026 < m_{miss}^2 < 0.068 \, GeV^2 / c^4$ . The 92% of background sources are suppressed by this kinematics selection. The remaining 8% must be rejected by the vetoes systems and the particle identification.

First of all the kaon identification is performed in the CEDAR (section 3.1.1). Then, to reconstruct the squared missing mass, the Gigatracker system provides the measurement of  $P_K^+$  in conjunction with time and coordinates measurements of all the beam particles before the decay region. In the vacuum tank, the Straw Tracker (Magnetic Spectrometer) performs the measurement, momentum and position, of the charged particles from the K<sup>+</sup> decay. In addition, in the vacuum tank,  $\pi^-$  are suppressed for wrong-charge deflection (Fig. 3.4).

One of the main sources of background (BR: 63.4%) is the decay  $K^+ \rightarrow \mu^+ \nu$  (K<sub>µ2</sub>). The required rejection factor of 10<sup>-12</sup> is reached by the kinematics selection, the muon veto system (MUV) and particle identification performed by the RICH detector. The latter performs the separation between µ and  $\pi$  candidates.

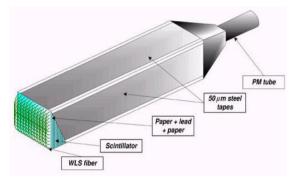

Another important source of background (BR: 20.9%) is the decay  $K^+ \rightarrow \pi^+ \pi^0$  (K<sub> $\pi^2$ </sub>). The required rejection factor of 10<sup>-12</sup> is achieved by the photon veto system which is composed of three different calorimeters covering different acceptance angles:

- Large Angle (LAV): 10 mrad < acceptance <5 0 mrad

- Medium Angle (Liquid Krypton): 1 mrad < acceptance < 10 mrad

- Small Angle (IRC, SAC): acceptance < 1 mrad.

A further background source can arise from the inelastic interactions in the beam collimators or in the GTK3 station, where the beam particles can generate pions and other particles at a small angle and reaching the Straw Tracker. If no other particles are detected a false  $K^+$  decay can be assumed; in fact it would mimic a  $K^+$  particle decaying into a pion with no other particles. The Charged ANTI (CHANTI) detector tags the inelastic interaction vetoing the charged particles produced at a large angle. This

system of scintillators is placed immediately after the GTK3 station. In addition it provides a further beam halo monitoring and muon halo tagging. In the following sections is given a detailed description of each subdetector.

#### 3.3 The Gigatracker

#### 3.3.1 System architecture and requirements

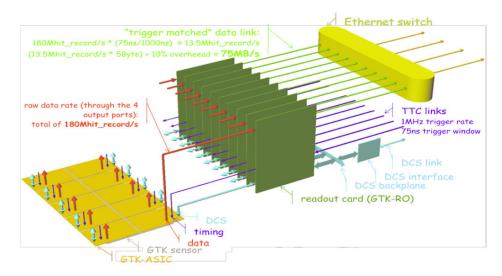

The Gigatracker (GTK) is one of the key elements for the NA62 experiment. It has to provide a precise time, angle, and momentum measurement of all the incoming particles in the 75 GeV/c beam.

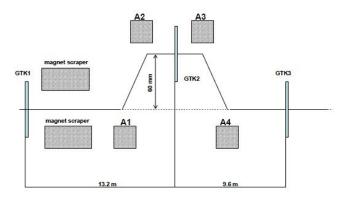

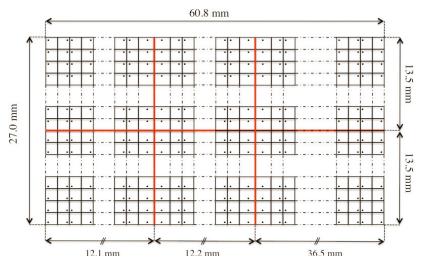

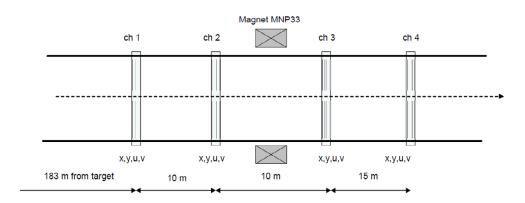

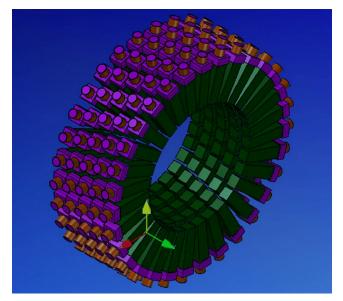

The GTK is composed of three stations of hybrid silicon pixels sensors mounted around four dipole magnets.

Fig. 3.6 Schematic layout of the Gigatracker.

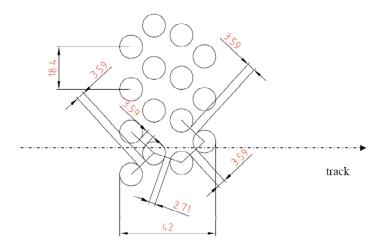

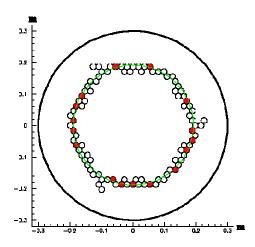

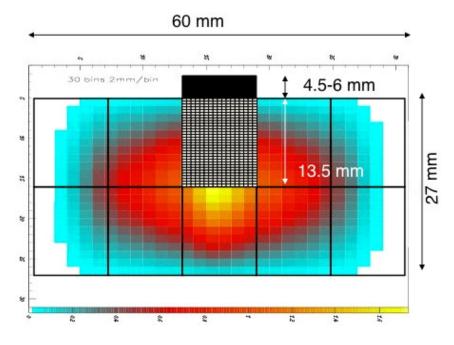

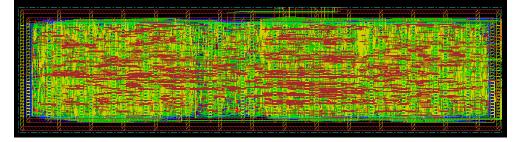

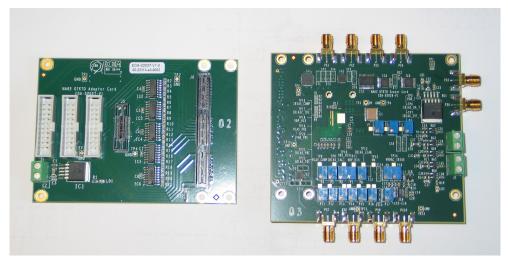

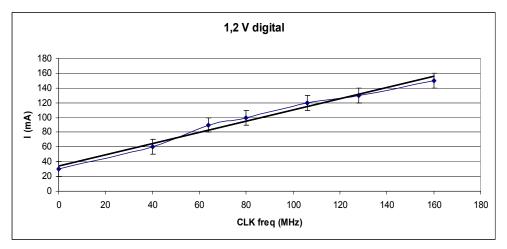

The distance between GTK1 and GTK2 is 13,2 m, between GTK2 and GTK3 is 9,6 m. To cope with the vertical bending of the beam at the achromat the GTK2 is displaced vertically by 60 mm. Each station covers an area of 60 x 27 mm, matching the expected beam dimension, and each pixel is 300 x 300  $\mu$ m. The readout is accomplished with a set of ten Application Specific Integrated Circuit (ASIC) chips (see Chapter 4 for details), which are bump bonded to the sensor and organized into two rows of five chip each. Being placed to match the beam, the Gigatracker (GTK) is exposed to a very high and not uniform beam rate, which ranges between

$\sim$ 0.8 and 1 GHz, with a peak of intensity around the centre of 1.5 MHz/mm<sup>2</sup>. Thus the GTK has to operate in a strong radiation environment. In order to minimize the hadronic interactions and the beam defocusing it has to operate in vacuum and the amount of crossed material must be minimum.

GTK information in conjunction with the Straw Tracker measurements will provide the momenta and angle of the incoming and outgoing particles in order to reconstruct the squared missing mass. Several simulations were performed to fix the required the GTK resolution [28]. Taking into account the expected Straw resolution it has been found that the GTK must be able to measure the momentum with a resolution  $\sigma(P_K)/P_K$  equal to 0,2 % and the direction with a resolution of 16 µrad [30].

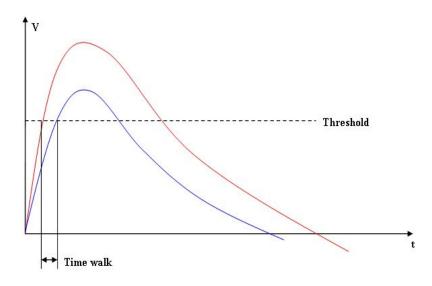

Due to the high rate, to match the tracks between the GTK and the downstream spectrometer (Straw Tracker) the time resolution must be < 200 ps (rms) per station on the single hit corresponding to  $\sim 150$  ps for a track.

Even with the required time resolution (150 ps) it is expected that a large number of events will suffer of multiple-tracks overlapping.

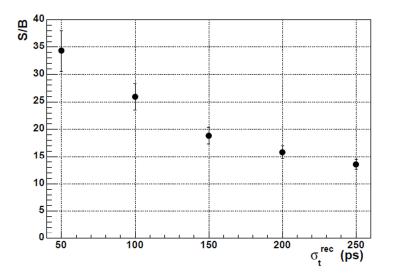

Fig. 3.7 S/B ratio and Gigatracker reconstructed time resolution.

However, when considering the overall event reconstruction more constraints can be applied to reject the fake overlapping tracks.

To study the track selection procedure, full events were simulated with GEANT4. The Monte Carlo showed that in case of a single track in the Gigatracker, the ratio of signal (S) with respect to background events (B) due to  $K^+ \rightarrow \pi^+ \pi^0$ , S/B, is ~100, when assuming an event signal acceptance of 10% and a  $\pi^0$  rejection efficiency of 2 x 10<sup>-8</sup>. In case of events with two tracks, the fake track can be rejected using the Closest Distance of Approach (CDA) algorithm. The computation determines the consistency of the two tracks, incoming and outgoing, as converging to a single point. Considering 800 MHz of particles rate, if the time resolution of the GTK is  $\sigma_t$ = 150 ps rms, within ± 2  $\sigma_t$  the number of events with more than one track in the GTK is around the 36% and in the  $\sim$  3% of them the matching between the incoming K and the outgoing  $\pi^+$  is incorrect. The wrong track can be rejected if the CDA is greater than a certain limit, which basically depends on the angular resolution. Because of the multiple tracks in the GTK and the beam divergence, the S/B ratio decreases rapidly and this requires a very good time resolution in the GTK. In fig. 3.7 it is shown the impact of the time resolution on the S/B ratio<sup>1</sup>. The required spatial resolution is less critical and it is set to 100 µm (rms). This value is obtained with a pixel size of 300 x 300 µm.

The time resolution of 150 ps is quite an ambitious value and at the moment no other pixels systems has such a capability. Just for comparison, pixels systems of the experiments at CERN LHC have a spatial resolution between 12 and 18  $\mu$ m, while the time resolution is more relaxed due to the bunch crossing time of 25 ns [31],[32],[33]. Another important R&D project on

<sup>&</sup>lt;sup>1</sup> The ratio quoted in fig. 3.7 was obtained by assuming that the time resolution of the beam tracker was improved by 40% with an extra detector following the GigaTracKer.

pixel detectors at CERN is the Timepix ASIC [34], which is an evolution of the Medipix chip [35]. In this case the time resolution is in the order of 10 ns [36].

Another challenging parameter is the high particles rate. The maximum beam intensity in the central area of the detector is expected to be 1,5  $MHz/cm^2$ . The fluence in the central area of the detector for the expected 100 days run time per year is  $2x10^{14}$  1MeV neutron equivalent per cm<sup>2</sup>. This value is very high and comparable with the working conditions of the inner layers of the LHC trackers in 10 years of operation. This requires the sensor and the readout electronics to have a robust radiation tolerance and to replace the Gigatracker stations every 60 days of data taking, which is the typical annual period expected to be granted to NA62. Moreover, to reduce the leakage in the silicon sensor, the Gigatracker must be cooled at 5° C or below. This request limits the power dissipated by the ASIC chips to be lower than  $2W/cm^2$ .

Another important issue is the material budget. The upper limit, which has been set to 0,5%  $X_0$ , imposes the thickness of the sensor and the readout ASIC to be respectively 200  $\mu$ m and 100  $\mu$ m. The table below summarizes the main parameters of the Gigatracker system.

| Number of stations                   | 3                      |

|--------------------------------------|------------------------|

| Number of pixels per station         | 18000                  |

| Number of readout chips per station  | 5 columns x 2 rows     |

| Number of pixels per chip            | 1800                   |

| Size of pixels                       | 300 μm x 300 μm        |

| Thickness of sensor                  | 200 μm                 |

| Thickness of readout chip            | 100 μm                 |

| Time resolution of GTK (rms)         | 150 ps                 |

| Time resolution of one station (rms) | 200 ps                 |

| Input dynamic range                  | 5000 – 60000 electrons |

| Particle rate per station               | 800 MHz                  |

|-----------------------------------------|--------------------------|

| Average particle intensity per station  | 0,5 MHz/mm <sup>2</sup>  |

| Design particle rate per chip           | 130 MHz                  |

| Dead time due to readout                | 1% (2% in beam centre)   |

| Time stamp resolution per station (rms) | < 200 ps                 |

| Total dose in 1 year                    | 10 <sup>5</sup> Gy       |

| Material budget                         | $0,5 \% X_0$ per station |

| Power dissipation per station           | $< 2W/cm^{2}$ , 32W      |

| Operating temperature vacuum            | < 0° C                   |

Table 3.3 Gigatracker parameters.

#### 3.3.2 The sensor

The silicon sensor is based on the p-in-n planar technology. Comparing the existing technologies for silicon hybrid pixels sensors the choice had to be made between planar and 3D detectors. While the latter one is very promising for the future, the starting time of NA62, foreseen for 2012, imposes the use of a mature technology as the planar one is. Finally the p-in-n technology has been choosen due to the simpler processing procedure and the relatively low cost compared to other possible solution such as underdepleated n-in-n).

The sensor must satisfy two main requirements: to have a very low material budget (< 0.5%  $X_0$  per station) and a sufficient large signal to provide the required time resolution. The 200 µm thickness is a good compromise between the material budget and the charge yield (~15000 e<sup>-</sup>). Moreover the sensor should operates at high over-depletion with the bias voltage of 500 V. To ensure a stable operation a multi-guard ring (12) structure has been developed

The overall time resolution is strongly dependent on the charge collection efficiency, speed, and on the capacitance of the sensor. These values degrade under radiation. Also the leakage current increases and the depletion voltage changes. In order to study these effects different p-in-n

diodes were irradiated to fluences between  $10^{12}$  and  $2 \times 10^{14}$  1 MeV n eq cm<sup>-2</sup> [37]. Some of the results are reported in table 3.4 and set the limit of 60 working days per station before their substitution. During the NA62 data taking a sufficient precise measurement (better than 100 nA of precision) of the leakage current will indicate the overall status of the detector.

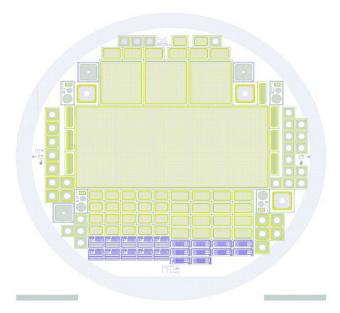

A first prototype of the p-in-n sensor has been realized at the end of 2009 on a 4" wafer. The substrate is n-type (phosphorous doped) with a resistivity of about 4-8 k $\Omega$ cm the thickness of (200±10) µm and the pixel size 300x300µm. The wafer contains different sensor geometries: one full-size sensor (18000 pixels), 3 single chip sensors (1800 pixels) and sensors for readout chips prototypes (see Chapter 4)

| Irradiation level                        | initial              | $5x10^{14}$         | 9x10 <sup>14</sup>  |

|------------------------------------------|----------------------|---------------------|---------------------|

| Coupling type amplifier                  |                      | DC                  |                     |

| Readout pixel implant                    | n                    |                     |                     |

| Pixel pitch                              | 300 µm               |                     |                     |

| Sensor thickness                         | 200 µm               |                     |                     |

| Capacitance of pixel to all neighbor     | 50 fF                |                     |                     |

| pixels                                   |                      |                     |                     |

| Capacitance of pixels to backplane       | 30 fF                | 40 fF               | 48 fF               |

| Extra bump capacitance                   | 20 fF                |                     |                     |

| Max leakage current per pixel for shot   | 0,5 nA               | 50 nA               | 200 nA              |

| noise                                    |                      |                     |                     |

| Charge collection efficiency ( at 500 V) | 1                    | 0,6                 | 0,45                |

| Collected charge (at 500 V)              | 16000 e <sup>-</sup> | 9600 e <sup>-</sup> | 7000 e <sup>-</sup> |

| Charge collection time                   |                      | < 5 ns              |                     |

Table 3.4 Irradiation results.

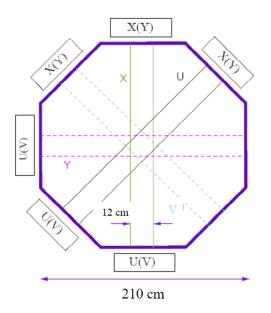

Fig. 3.8 4" wafer layout.

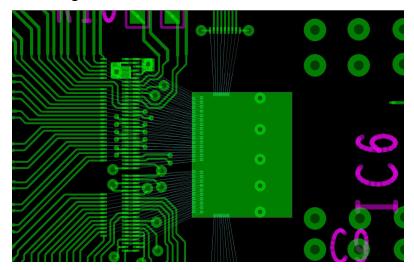

Two rows of five readout chips are connected to the sensor through bump bonding: each pixel cell is bump bonded to the corresponding read-out channel. The bump pads have an octagonal shape and the size is 26  $\mu$ m. Within the pixel, the pad is located 50  $\mu$ m from the pixel edge. The bump pads have a mirroring position with their neighboring columns. The pixel size in the interchip region is enlarged (300x400  $\mu$ m) in order to maintain the full sensitive area. Also the guard rings must be connected to the frontend chips by bump bonding.

Fig. 3.9 Schematic layout of the bump bonding position.

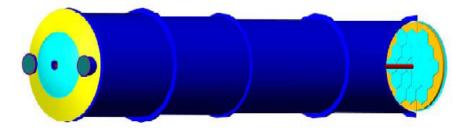

#### 3.3.3 Cooling and mechanics

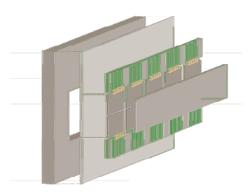

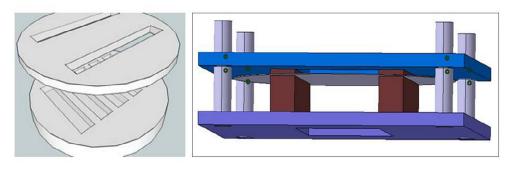

The detector module is supported by a carbon fiber structure as showed in the picture above.

Fig. 3.10 The Gigatracker supporting system.

In order to minimize the material budget in the beam area, all the mechanical connections must be done at least 10 mm outside the beam.

The cooling system must provide a uniform working temperature of  $5^{\circ}$  C or less. The total power dissipated should be less than 32 W corresponding to 2 W/cm<sup>2</sup>. In addition the system is operated in vacuum. At the moment, to reach these requirements, there are two possible solutions under development: a micro-channel structure and a vessel with mylar walls.

The micro-channel cooling option consists of two silicon plates. The upper one (cover) contains holes for inlet and outlet and it is glued to the second wafer which contains the micro-channels for the coolant passage. The sensor and the readout chips are clamped between the two silicon plates, through the two red metal blocks, as showed above.

Fig. 3.11 The micro-channel clamp concept.

The two metal blocks contains grooves to feed the micro-channels located in lower silicon plate. One should remark that the clamp solution is still under scrutiny and other possibilities are under consideration.

Choosing a channel dimension of  $50x50 \ \mu\text{m}$  and etching the silicon plates in the beam area it is possible to maintain a total material budget of 0,45%  $X_0$ .

A base solution for the coolant gas is  $C_6F_{14}$ , which is radiation hard, thermally and chemically stable as confirmed in the CMS and ATLAS trackers.

The expected pressure of the fluid in the micro-channels is 12 bar while the operation temperature between  $-20^{\circ}$  C and  $-30^{\circ}$  C. The advantage of using this technique is the lower thermal stress (smaller  $\Delta$ T between readout chips and coolant) and a better temperature uniformity.

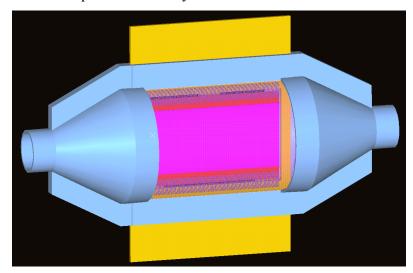

The second option under study for the Gigatracker cooling system is based on the use of a vessel with mylar walls, inserted in the vacuum beam, housing the sensor and the readout chips. A flux of nitrogen at  $100^{\circ}$  K and  $25 \text{ m}^3/\text{h}$  is expected to be sufficient to keep the temperature of the module at  $< 5^{\circ}$  C with the required uniformity.

Fig. 3.12 The GTK cooling vessel. The beam is orthogonal to the picture.

In this configuration the sensor is connected to a printed circuit board (PCB) (yellow in Fig. 3.12), which provides all the electrical connections to the external system. The detector is thermally decoupled form the PCB and the support must compensate the different thermal expansion coefficients of the materials. Simulations and thermal analysis showed a good uniformity with a maximum temperature of  $4^{\circ}$  C.

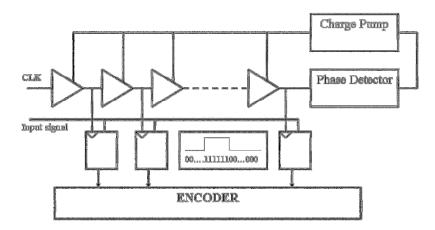

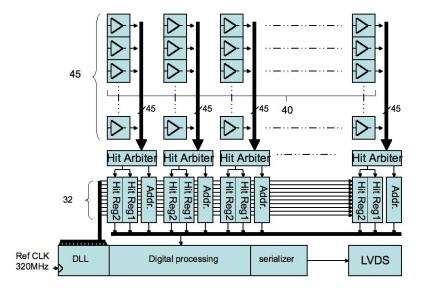

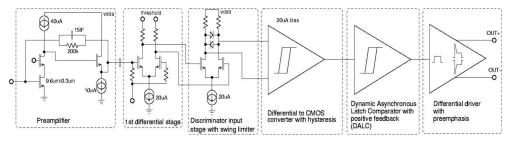

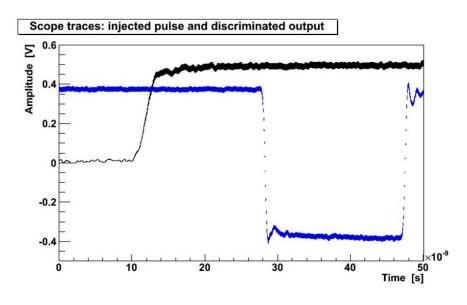

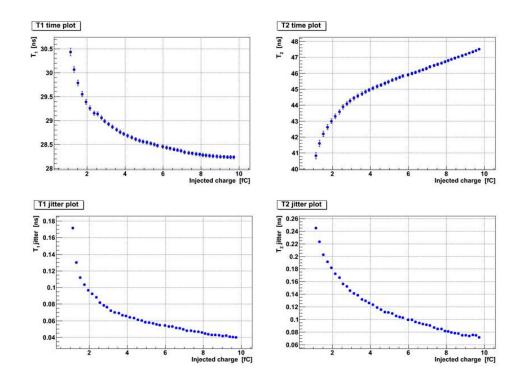

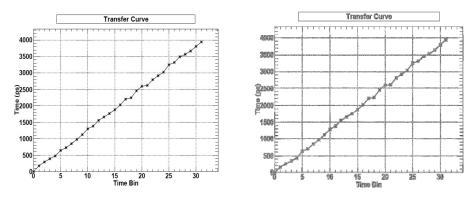

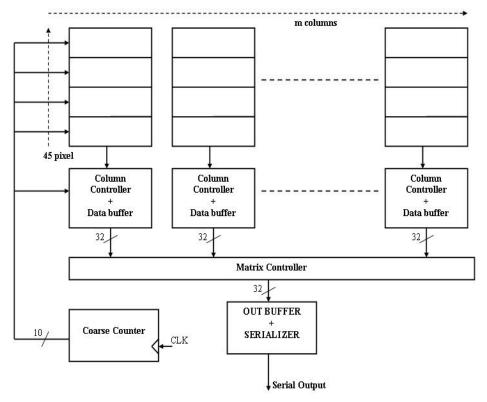

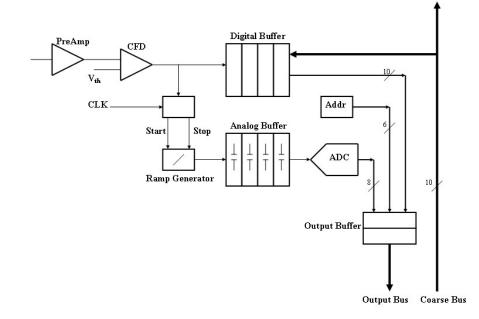

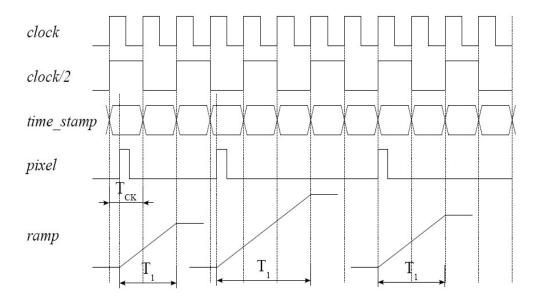

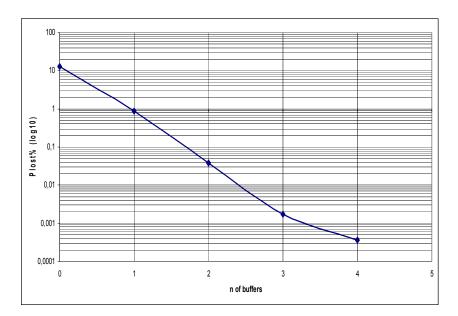

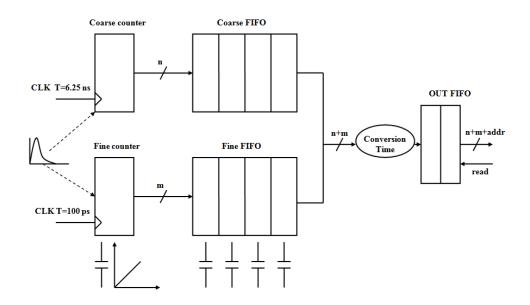

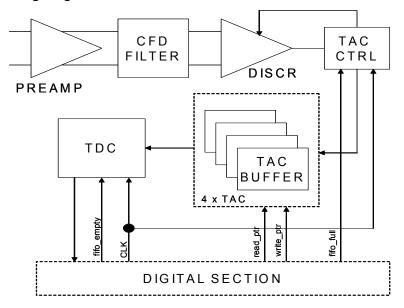

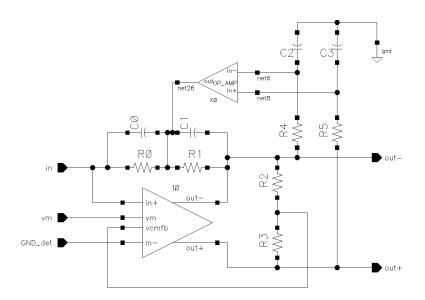

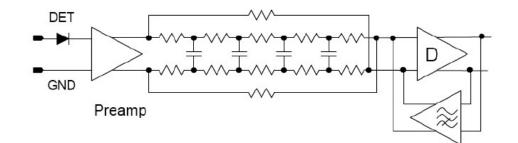

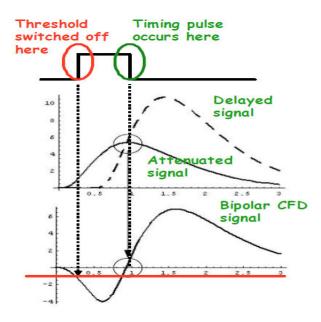

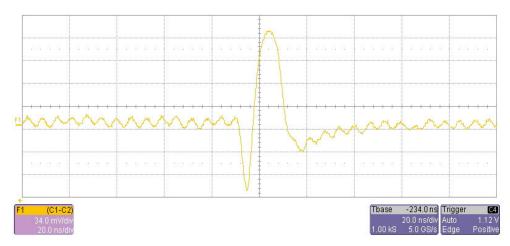

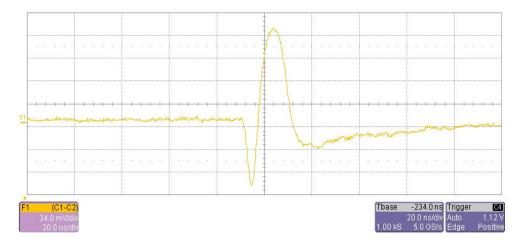

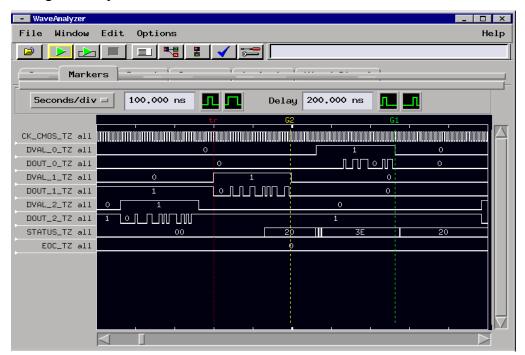

#### 3.4 Magnetic spectrometer