University of Turin

Faculty of Mathematical, Physics and Natural Sciences

Physics Degree Thesis

# Development of Integrated Electronics for Monolithic Detectors in Q-Well CMOS Technology

Candidate: Alessandra Lattuca

Supervisor: Dr. Angelo Rivetti

Co-Supervisor: Dr. Giovanni Mazza

Academic year 2011 / 2012

"In questo consiste la forza dell'acqua: non potrà mai essere spezzata da un martello, o ferita da un coltello.

La più potente spada al mondo non potr mai lasciare nessuna cicatrice sulla sua superficie.

L'acqua di un fiume si adatta al cammino possibile, senza dimenticare il proprio obiettivo: il mare.

Fragile alla sorgente, a poco a poco acquista la forza degli altri fiumi che incontra.

E, a partire da un certo momento, il suo potere È totale." P. C.

# Contents

## Introduction

| 1        | Pa  | rticle Detection and Tracking in High Energy Physics         | <b>5</b> |

|----------|-----|--------------------------------------------------------------|----------|

|          | 1.1 | Basic Concepts                                               | 6        |

|          |     | 1.1.1 Impact parameter resolution                            | 6        |

|          |     | 1.1.2 Deflection in magnetic field                           | 9        |

|          |     | 1.1.3 Occupancy, dead time and pile-up                       | 10       |

|          | 1.2 | Energy Loss of Heavy Charged Particles                       | 12       |

|          |     |                                                              | 13       |

|          |     | 1.2.2 Multiple Scattering                                    | 16       |

|          | 1.3 | Silicon Sensors                                              | 17       |

|          |     | 1.3.1 Hybrid Pixel Detectors and MAPS                        | 20       |

|          |     | 1.3.2 Silicon Strip Detectors                                | 21       |

|          |     | 1.3.3 Silicon Drift Detector                                 | 23       |

|          | 1.4 | An example: the ALICE experiment at CERN                     | 24       |

|          | 1.5 | Inner Tracking System (ITS)                                  | 26       |

|          | 1.6 | Limitations of current ITS and Motivations for the Upgrade . | 28       |

|          | 1.7 | Options for Upgrade                                          | 30       |

| <b>2</b> | Mo  | nolithic Active Pixel Sensors                                | 35       |

|          | 2.1 | P-n junction                                                 | 36       |

|          | 2.2 | -                                                            | 40       |

|          | 2.3 |                                                              | 43       |

|          | 2.4 | •                                                            | 46       |

|          | 2.5 |                                                              | 48       |

|          | 2.6 |                                                              | 50       |

|          | 2.7 |                                                              | 53       |

|          | 2.8 | •                                                            | 57       |

|          | 2.9 |                                                              | 62       |

|          |     |                                                              |          |

1

| 3        | The  | e LVDS Transmission System                                                            | <b>65</b> |

|----------|------|---------------------------------------------------------------------------------------|-----------|

|          | 3.1  | LVDS Specifications                                                                   | 66        |

|          |      | 3.1.1 LVDS Driver                                                                     | 68        |

|          |      | 3.1.2 LVDS Receiver                                                                   | 69        |

|          | 3.2  | Performance Qualification                                                             | 69        |

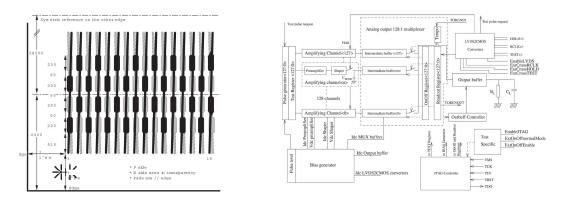

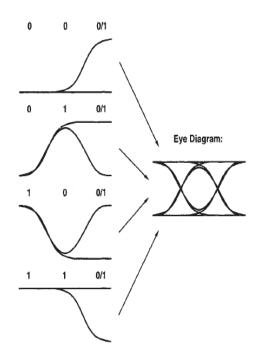

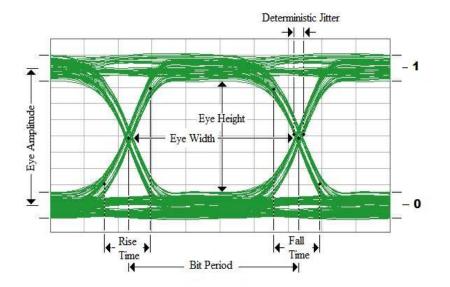

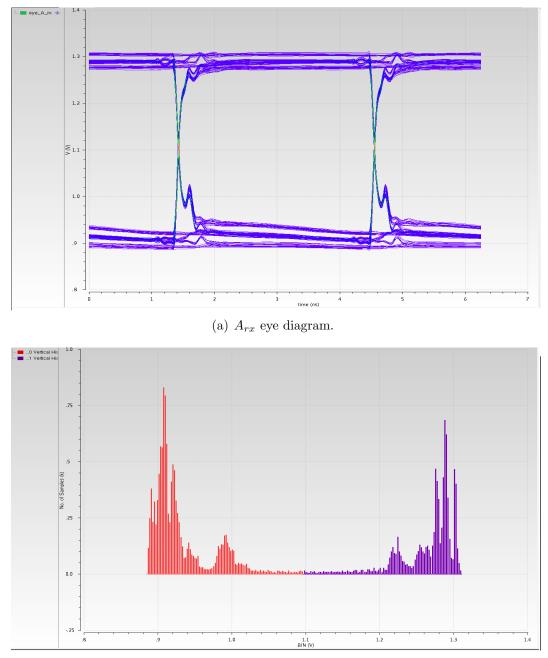

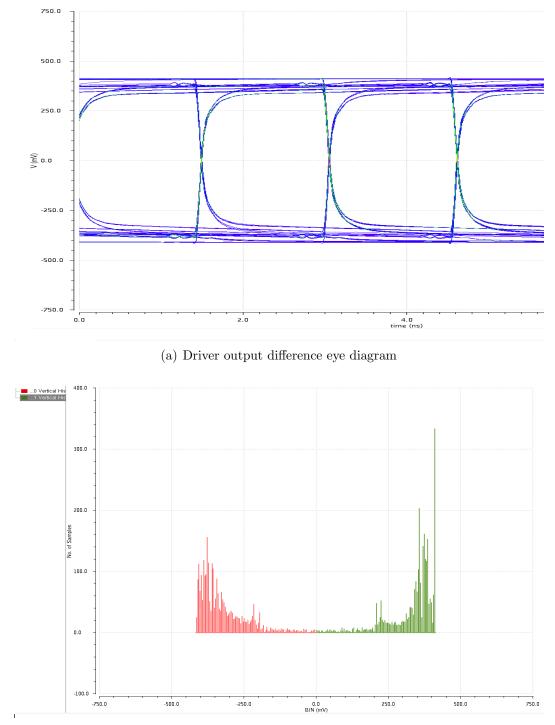

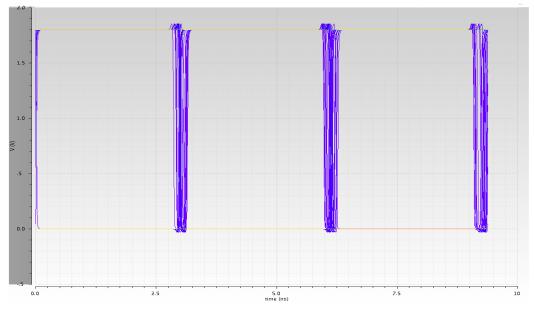

|          |      | 3.2.1 Eye Diagram                                                                     | 70        |

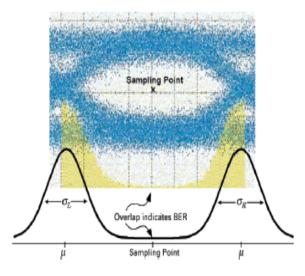

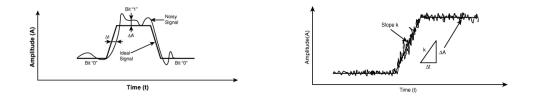

|          |      | 3.2.2 Timing Jitter                                                                   | 71        |

| <b>4</b> | Des  | ign of a Custom LVDS Interface in 0.18 $\mu m$ CMOS                                   | 75        |

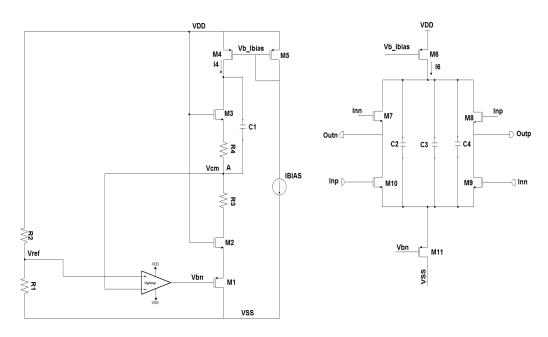

|          | 4.1  |                                                                                       | 75        |

|          | 4.2  | Transmitter 2                                                                         |           |

|          | 4.3  | Receiver                                                                              | 84        |

| 5        | Linl | k Optimization                                                                        | 87        |

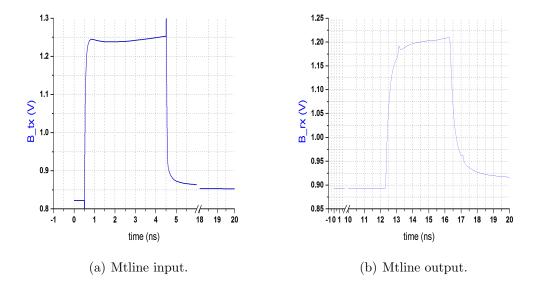

|          | 5.1  | Transmission line                                                                     | 88        |

|          | 5.2  | Simulation Test Bench                                                                 | 90        |

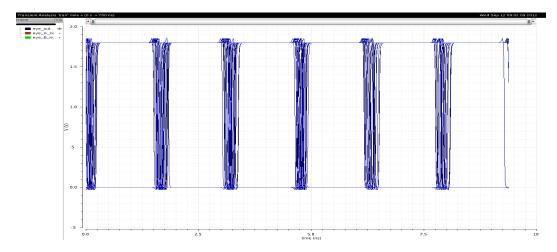

|          | 5.3  | Results of Transmitter 1                                                              | 93        |

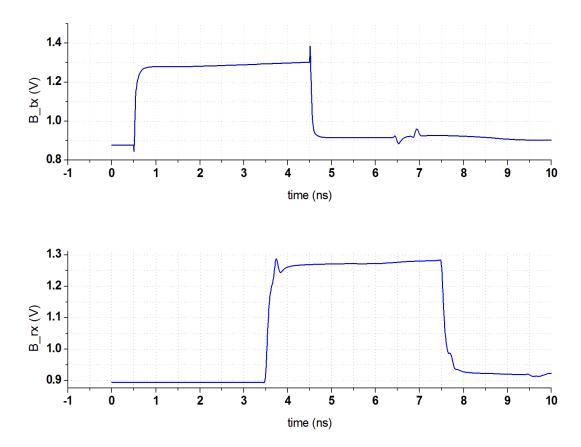

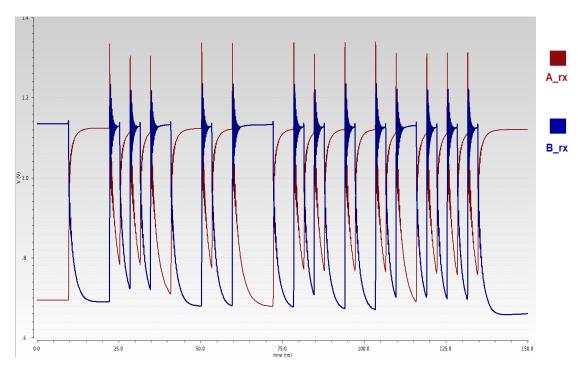

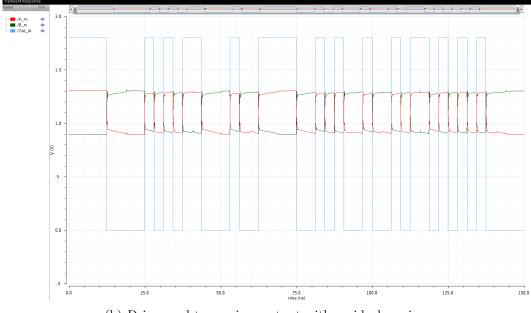

|          | 5.4  | Results for Transmitter 2 and receiver                                                | 94        |

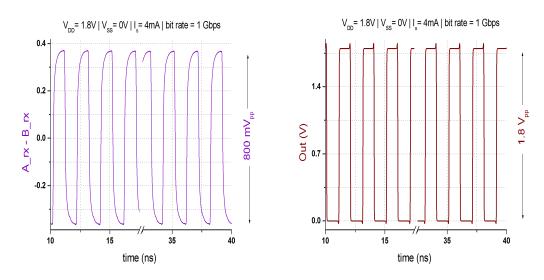

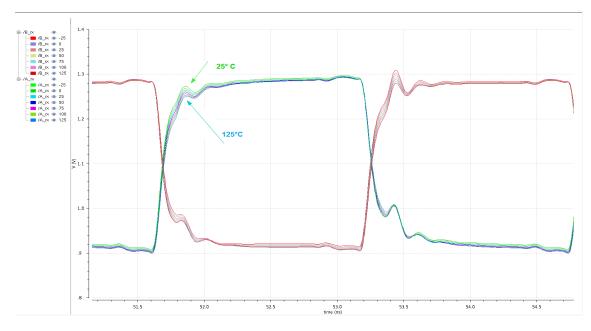

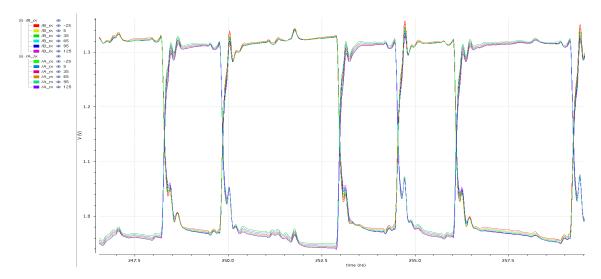

|          |      | 5.4.1 Corner Analysis                                                                 | 95        |

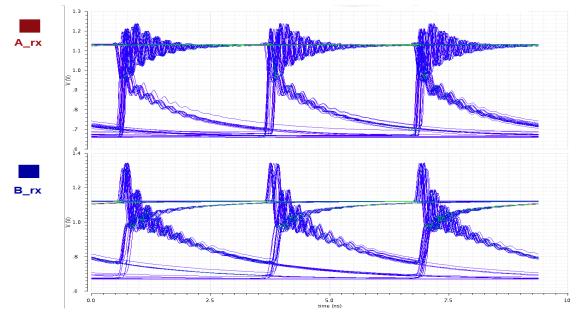

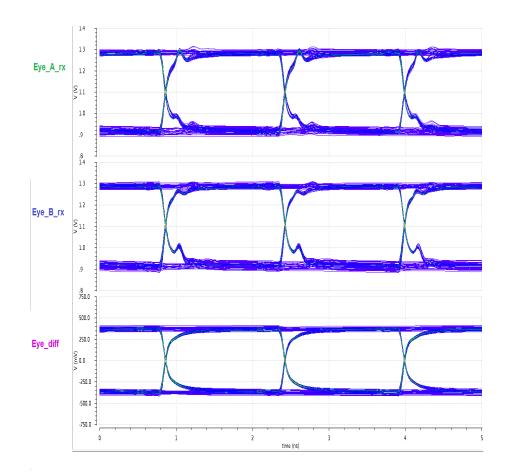

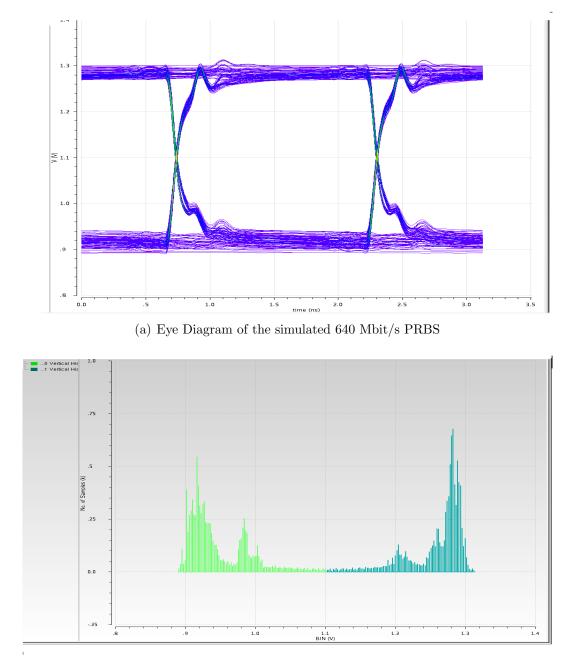

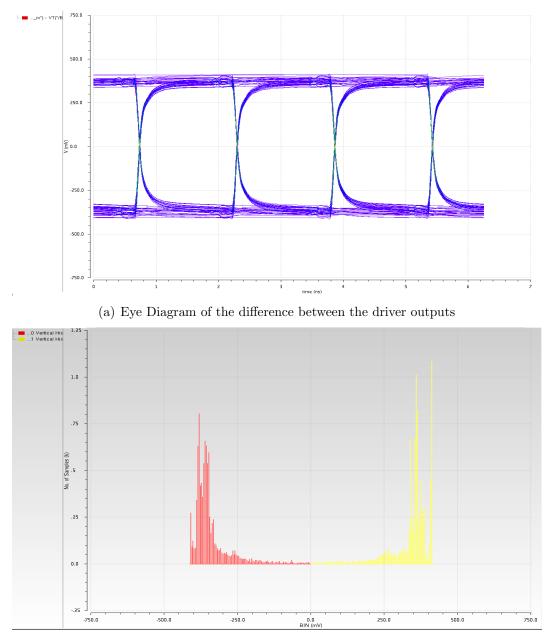

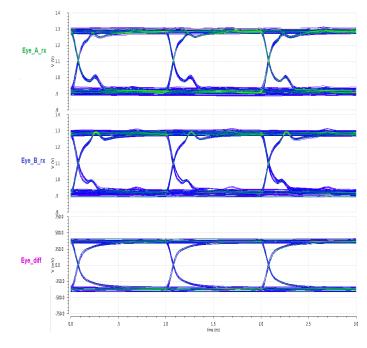

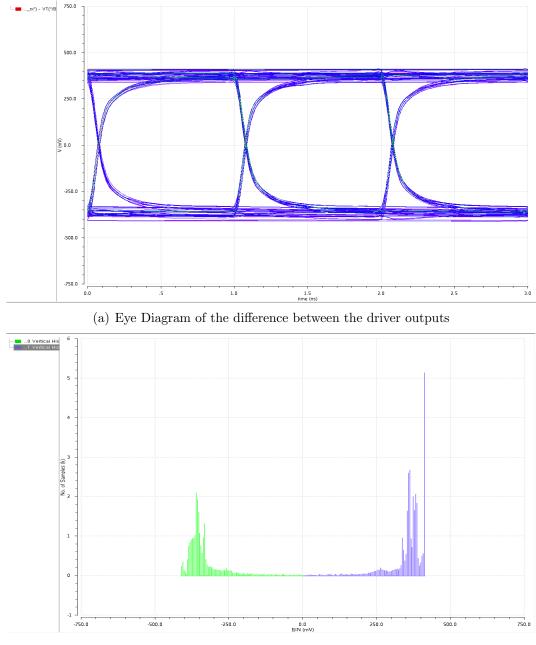

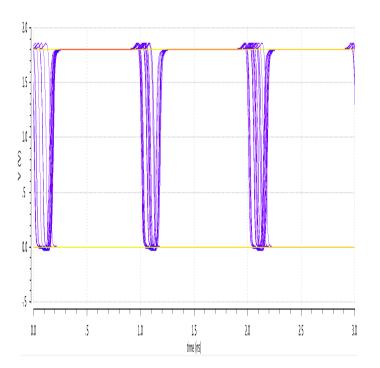

|          | 5.5  | Transmitter 2 Eye Diagrams                                                            | 100       |

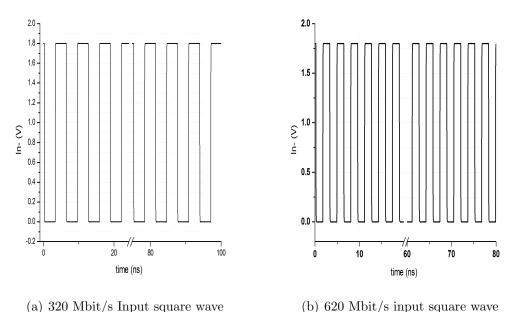

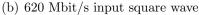

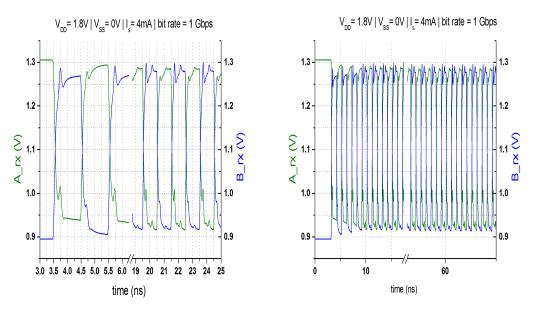

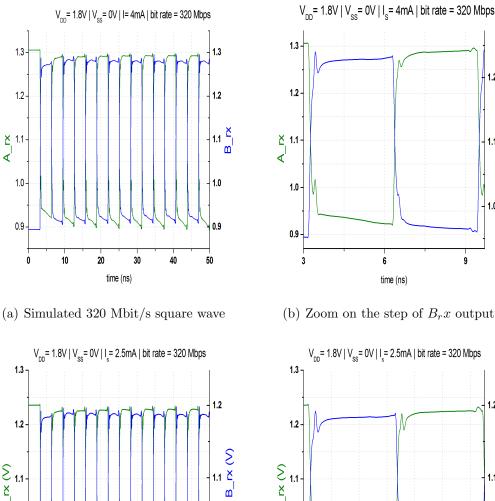

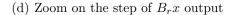

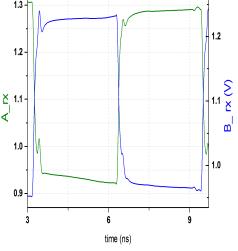

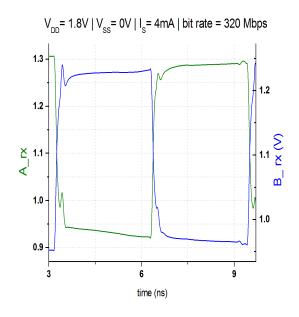

|          |      | 5.5.1 320 Mbit/s input data stream $\ldots \ldots \ldots \ldots \ldots \ldots $       | 101       |

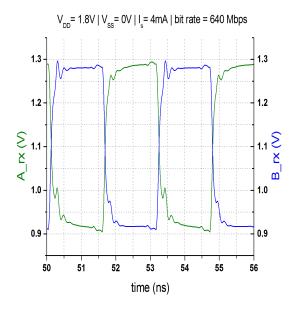

|          |      | 5.5.2 640 Mbit/s input data stream $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 105       |

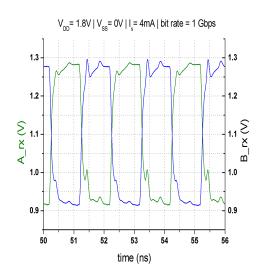

|          |      | 5.5.3 1 Gbps input data stream $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$     | 112       |

| a        | ,    |                                                                                       |           |

#### Conclusion

115

# Acknowledgments

Sono tante le persone che ho incontrato durante il mio percorso di studi e con le quali ho condiviso esperienze pi o meno divertenti e piacevoli e che mi hanno supporta e sopportata (!!) nei momenti critici.

Il momento dei ringraziamenti sempre quello più difficile perché si rischia o di non ringraziare abbastanza o di tralasciare qualcuno; proverò lo stesso a fare del mio meglio.

Prima di tutti ringrazio Giovanni, per l'amore e la pazienza con cui mi sta accanto e per avermi alleggerito la vita quando ce n'era di bisogno.

I miei genitori, per il sostegno costante e per l'affetto con cui mi circondano, e mia sorella perché lei c'è sempre stata. Le mie compagne di studi, di risate, di notti insonni, di folli inseguimenti in autostrada, di caffé in riva al mare e di situazioni imbarazzanti, Laura e Paola.

Giusy e Paolo per avermi accolto al mio arrivo a Torino e per l'affetto che mi hanno sempre dimostrato.

Alberto e Valentino per gli attestati di stima alle edizioni Lattuchelli.

Dons, Sara, Chiara, Giovanni, Fede e tutto il gruppo Johnny.

Agnese, Margherita, Alessio, Sofia<sup>1</sup>(questo te lo devo) e gli altri amici che a nominarli tutti non si finirebbe più.

Il Dott. Agnello, che mi ha guidata nel percorso del triennio e che non ho mai avuto l'occasione di ringraziare.

Un grazie particolare lo riservo poi a chi mi ha guidata durante lo svolgimento della tesi e di questo percorso di studi. Al Dott. Rivetti per avermi supportata pazientemente e per aver creduto in me.

Al Dott. Mazza per la supervisione attenta. A Sara e Manuel: ancora mi chiedo come avrei fatto senza di voi?!

Alla mia famiglia e a tutti voi, GRAZIE!

<sup>&</sup>lt;sup>1</sup>Cascio

## Abstract

This thesis is part of the ongoing studies for the upgrades of the Inner Tracking System of the Alice experiment at CERN.

ALICE is the LHC experiment devoted to the study of ultra-relativistic heavy-ion collisions. The experiment is now in the data taking phase. In 2017-2018 the LHC will be shut down for a major maintenance and it is foreseen to use this opportunity to introduce also important improvements in the ALICE experimental apparatus. One of this system considered for the upgrade is the Inner Tracking System or ITS, which is the closest detector to the interaction point. The use of a smaller beam-pipe will allow to introduce high granularity detectors closer to the interaction point, improving the vertex reconstruction and giving access to new physics channels that cannot be explored with the present set-up. The data rate capability of the system will also be increased from today's rate of 1 kHz to 50 kHz in order to improve the statistics on rare events.

Monolithic silicon detectors are considered in order to reduce the material budget. Since they do not need a conductive bond like hybrid pixel detectors, it is possible to get thinner sensors thus improving the impact parameter resolution. Several approaches exist in order to design a monolithic CMOS sensors. The Quadruple well technology provided by TowerJazz is regarded as a very promising candidate. This technology allows in fact to built complex pixels embedding both digital and analog circuits within the sensitive area. Furthermore, the feature size of 0.18  $\mu m$  already allows for dense digital design.

The development of the new ITS will be a large international collaboration and it involves teams from several institutions including IN2P3, CERN and INFN. The purpose is to develop new generation of CMOS sensors suited to the ALICE requirements. Such devices will need many high performance blocks performing different functions: amplification, data compression, power regulation, data transmission. One of the key components of the CMOS sensors is the data transmission link. Here, it is necessary to combine a high data throughput with a small power consumption.

In this work the design of such a link has been addressed. The link is based on the LVDS protocol, which is a widely used industrial standard. The link should work at a transmission rate of up to 1Gbit/s. This thesis is organized as follows:

- In Chapter 1 some basic concepts about the detectors principle of operation are reported together with a brief description of some types of silicon sensors: the hybrid pixel sensors, the silicon strip and the silicon drift detectors. Furthermore, a description of the general purpose detector ALICE and of its components is given, paying special attention on the features of the actual ITS and on its limitations which motivate the upgrade.

- In Chapter 2 the state of the art in the Monolithic Active Pixel Sensors is reported. We present the standards MAPS and its principle of operation together with two alternative layout of the sensor: Deep N-well MAPS and INMAPS. Monolithic sensors based on charge collection by drift.

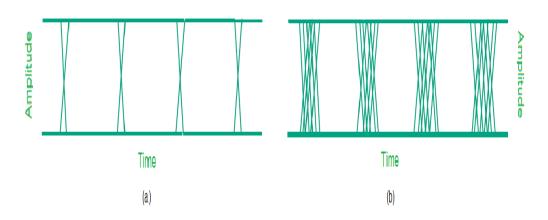

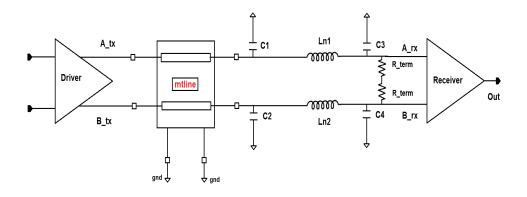

- Chapter 3 reports a description of the LVDS interface and of its specifications as well as the method used in order to analyze the quality of the transmitted signal, as the eye diagram.

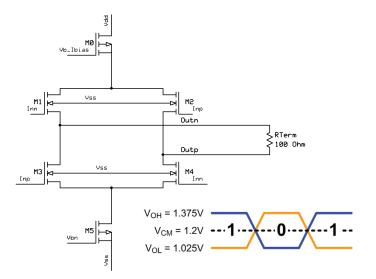

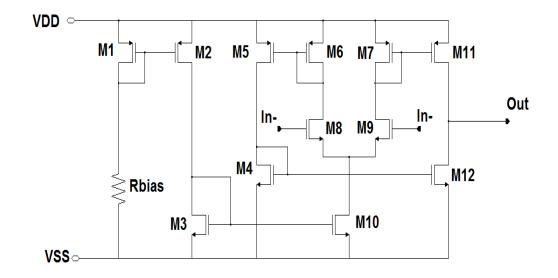

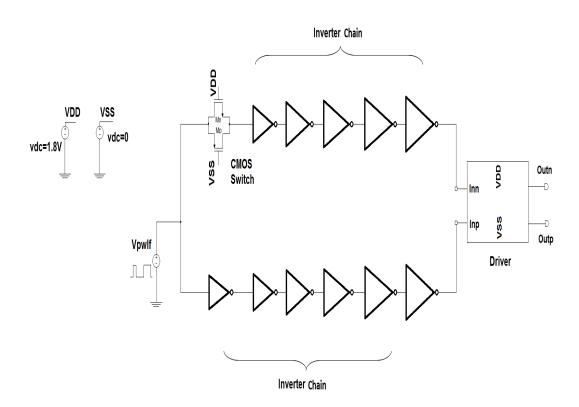

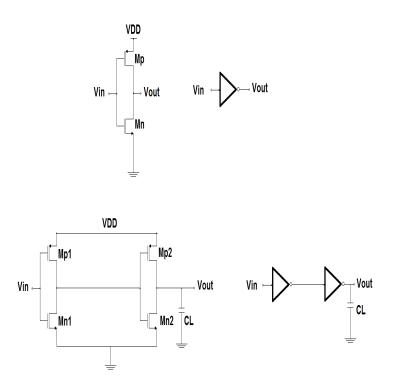

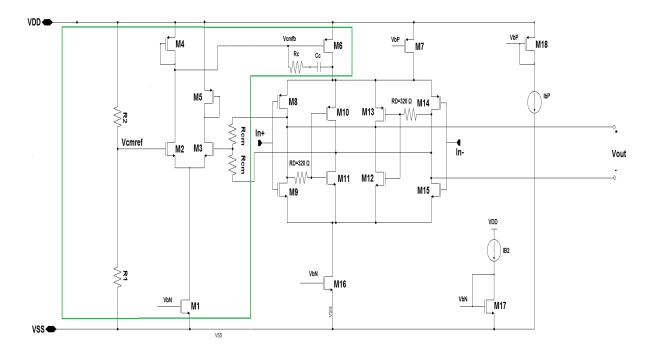

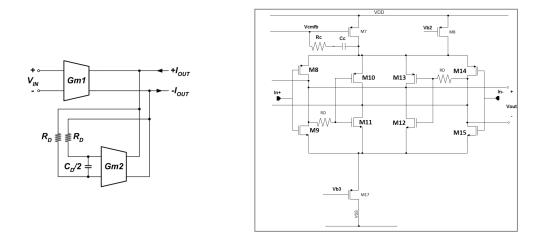

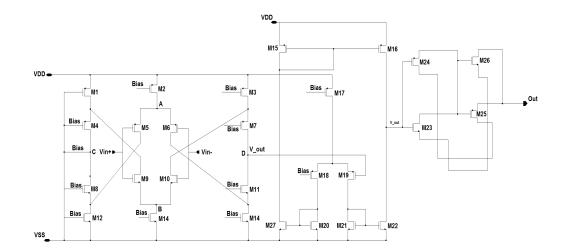

- In Chapter 4 we describe the LVDS transceivers the we have designed. The circuit are implemented in the 0.18  $\mu m$  Q-well CMOS technology. Two transmitter designs have been considered. Transmitter 1 is based on a scheme widely used in many applications at CERN. This scheme was scaled to adapt it to the technology of our interest. Some limitations were found by operating this device at power supply 1.8 V. This motivated the design of the alternative scheme Transmitter 2 that shows good performance. A receiver circuit based on a self biased amplifier was also developed.

- In Chapter 5, finally, we report the simulation results obtained with our LVDS link. Simulations were performed using both deterministic

and pseudo-random sequences to study the stability of the system and its dynamic response. The simulation were done under different conditions including the noise, mismatch effects, temperature and process variations.

## Chapter 1

# Particle Detection and Tracking in High Energy Physics

ALICE, acronym of A Large Ion Collider Experiment, is a heavy-ion experiment at the CERN Large Hadron Collider, near Geneva. The ALICE detector is designed to analyze the collisions between heavy-ions at the centerof-mass energy  $\sim 5.5$  TeV. The purpose of the experiment is to study the physics of strong interactions, in an attempt to answer fundamental questions about the mechanism of the mass generation of handrons and to understand why single quarks and gluons have never been observed[1].

The long term projects foresees the characterization of a new state of matter, created by the disintegration of hadrons in free quarks and gluons, the *Quark-Gluon Plasma* (QPG), which is likely the have existed just after the Big Bang. Therefore, the aim of the ALICE is to create the physic conditions for the QPG formation and to provide a comprehensive characterization of its properties like initial temperature, degrees of freedom, transport coefficients, etc.

The first part of this chapter introduces basic concepts that will be used throughout the thesis; the second part is devoted to the ALICE detector and to the Inner Tracking System (ITS) in particular.

The chapter starts with an overview of the tracking detectors employed to study the physics properties of subatomic particles. When one inserts the detector in a magnetic field, it is possible to determine the magnitude of the particles' momentum by measuring the radius of curvature of the trajectory. In addition, in order to correctly detect an event, the detector read out must be fast enough to avoid the *pile-up* of two successive events.

The second section of the chapter describes the principles on which particles detection is based, i.e. the energy loss in the sensor due to the interaction between the impinging particle and the atoms encountered in the sensor active volume. Multiple scattering, that often reduces the capability of a detector to locate the interaction vertex, is also discussed.

In the third section a review of the most important silicon sensors used in particle physics experiments is presented.

ALICE and its sub-detectors are described in the fourth section. The last section focuses on the *Inner Tracking System* (ITS). Here, a description the current ITS (Section 1.5) is followed by a discussion of the limitations of the current set-up and of the motivations for the upgrade. (Section 1.6). Finally, the technical options for the implementation of the new ITS are examined (Section 1.7).

## **1.1 Basic Concepts**

A detector is a device through which one detects a charged or electrically neutral particle and measures its properties. Although there are many different types of detectors (semiconductor detectors, scintillators, ionization chambers etc...), it should be noted that the principle of operation is always the same: the conversion of the energy released by the particles in the sensitive volume of the sensor into an electrical signal that is possible to handle by means of electronic circuits.

Complex systems combining different detectors are necessary to identify a particle and to measure its physical properties like energy, momentum, electrical charge and mass.

A tracking detector is used to determine the trajectories of charged particles that are deflected in a magnetic field  $\vec{B}$  and to measure their momenta. In addition, it allows to reconstruct the primary vertex of interaction and to localize the secondary vertex due to the decays of the particles produced in the interaction. By means of a tracking detector it is also possible to identify a particle studying its energy loss per unit path length (*stopping power*)  $\langle dE/dx \rangle$  and to select specific events.

#### **1.1.1** Impact parameter resolution

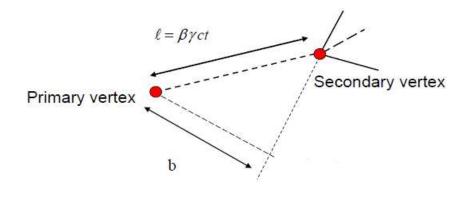

For optimal performance, a tracking detector should be as close as possible to the interaction point. In fact, many particles of interest live for a very short time  $\tau$  before disintegrating into the daughter particles. For example, the Pb-Pb collisions at LHC produce  $D^0$  mesons that have lifetime  $\tau \approx 10^{-12}s$ , during which they cover a distance of  $c\tau \approx 300 \mu m$ . Then, they decay generating  $K^-$  and  $\pi^+$ . In this case, given that the  $D^0$  meson is a neutral particle, the only way to reveal it by using a tracking detector is to trace the trajectories of secondary particles and to localize the decay point. This is a simple example of a general method used for all particles that have short lifetimes. Here, the relevant quantity is the minimum distance between the primary vertex where the collisions take place and the secondary vertex, where the particle has decayed, i.e. the *impact parameter b*. This must be determined with the best possible resolution, e.g.  $\leq 0.03 \ mm$  for particles which have lifetimes of ~ ps [2].

Figure 1.1: Interaction Point: primary vertex and secondary displaced vertex, [3]

The impact parameter b depends on the energy of the particle, its lifetime  $\tau$  and the angle between its direction of flight and the particles produced in the decay:

$$b = \gamma \beta c \tau \sin \theta \tag{1.1}$$

For high momentum particles  $\sin \theta \approx 1/(\gamma \beta)$  and therefore  $b \approx c\tau$  is equivalent to the distance traveled by the particles before they decay spontaneously. In this case the resolution  $\sigma_b$  doesn't depend on the magnitude of the particles momentum. On the contrary,  $\sigma_b$  only depends on detector's properties, like resolution and geometry, and the closer the detector is to the interaction point, the better the spatial resolution will be.

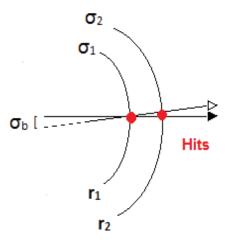

To give a quantitative idea, let's consider a cylindric tracker disposed around the interaction point that is formed only by two layers 1 and 2. The two layers are separated from the interaction point by  $r_1$  and  $r_2$ , with  $r_1 < r_2$ and their resolutions are respectively  $\sigma_1$  and  $\sigma_2$ . This is a crude simplification of a realistic tracker, which is usually composed of many layers. We suppose here to neglect also the magnetic field  $\vec{B}$ .

Figure 1.2: Impact parameter resolution

Now, let's approximate the trajectory with a straight line like t(r) = b + Ar, where the impact parameter b and the constant A represent respectively the offset and the slope of the track. We apply a weighted least square on the track point because each layers has its own resolution  $\sigma_i$ . Therefore, the impact parameter resolution is obtained through the offset's error:

$$\sigma_b^2 = \frac{\sum_i w_i r_i^2}{\Delta} = \left(\frac{r_1^2}{\sigma_1^2} + \frac{r_2^2}{\sigma_2^2}\right) \frac{1}{\Delta}$$

(1.2)

where  $w = 1/\sigma_i^2$  represents the weight of each layer and  $\Delta$  is defined as:

$$\begin{split} \Delta &= \sum_{i} w_{i} \sum_{i} w_{i} r_{i}^{2} - \left(\sum_{i} w_{i} r_{i}\right)^{2} = \\ &\frac{1}{\sigma_{1}^{2}} \left(\frac{r_{1}^{2}}{\sigma_{1}^{2}} + \frac{r_{2}^{2}}{\sigma_{2}^{2}}\right) + \frac{1}{\sigma_{2}^{2}} \left(\frac{r_{1}^{2}}{\sigma_{1}^{2}} + \frac{r_{2}^{2}}{\sigma_{2}^{2}}\right) - \left(\frac{r_{1}}{\sigma_{1}^{2}} + \frac{r_{2}}{\sigma_{2}^{2}}\right)^{2} = \\ &\left(\frac{1}{\sigma_{1}^{2}} + \frac{1}{\sigma_{2}^{2}}\right) \left(\frac{r_{1}^{2}\sigma_{2}^{2} + r_{2}^{2}\sigma_{1}^{2}}{\sigma_{1}^{2}\sigma_{2}^{2}}\right) - \left(\frac{r_{1}\sigma_{2}^{2} + r_{2}\sigma_{1}^{2}}{\sigma_{1}^{2}\sigma_{2}^{2}}\right)^{2} = \\ &\frac{(\sigma_{1}^{2} + \sigma_{2}^{2})(r_{1}^{2}\sigma_{2}^{2} + r_{2}^{2}\sigma_{1}^{2}) - (r_{1}^{2}\sigma_{2}^{4} + r_{2}^{2}\sigma_{1}^{4} + 2r_{1}r_{2}\sigma_{1}^{2}\sigma_{2}^{2})}{(\sigma_{1}^{2}\sigma_{2}^{2})^{2}} = \\ &\frac{r_{1}^{2}\sigma_{1}^{2}\sigma_{2}^{2} + r_{2}^{2}\sigma_{1}^{2}\sigma_{2}^{2} - 2r_{1}r_{2}\sigma_{1}^{2}\sigma_{2}^{2}}{(\sigma_{1}^{2}\sigma_{2}^{2})^{2}} = \frac{(r_{2} - r_{1})^{2}\sigma_{1}^{2}\sigma_{2}^{2}}{(\sigma_{1}^{2}\sigma_{2}^{2})^{2}} = \\ &\frac{(r_{2} - r_{1})^{2}}{(\sigma_{1}^{2}\sigma_{2}^{2})}. \end{split}$$

From (1.2) and (1.3) and with the previously mentioned approximation, one gets:

$$\sigma_b^2 \approx \left(\frac{r_1^2 \sigma_2^2 + r_2^2 \sigma_1^2}{\sigma_1^2 \sigma_2^2}\right) \left(\frac{1}{\Delta}\right) = \left(\frac{r_1^2 \sigma_2^2 + r_2^2 \sigma_1^2}{\sigma_1^2 \sigma_2^2}\right) \frac{\sigma_1^2 \sigma_2^2}{(r_2 - r_1)^2} = \left(\frac{\sigma_1 r_2}{r_2 - r_1}\right)^2 + \left(\frac{\sigma_2 r_1}{r_2 - r_1}\right)^2 = \frac{1}{(r_2 - r_1)^2} [(\sigma_1 r_2)^2 + (\sigma_2 r_1)^2]$$

(1.4)

This shows that the precision on the inner layer provides the main contribution because  $\sigma_1$  is highlighted by the greater radius.

If one supposes  $\sigma_1 = \sigma_2 = \sigma$ , 1.4 is rewritten as:

$$\left(\frac{\sigma_b}{\sigma}\right)^2 \approx \left(\frac{1}{1 - r_1/r_2}\right)^2 + \left(\frac{1}{r_2/r_1 - 1}\right)^2 \tag{1.5}$$

from which it is clear that the impact parameter resolution can be improved by properly setting the ratio between the distances of the layers from the interaction point [3].

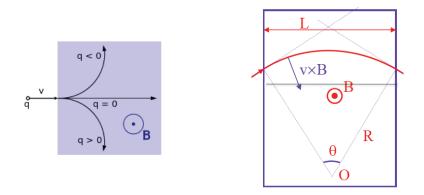

### 1.1.2 Deflection in magnetic field

It is well known that when a charged particle is moving in a magnetic field  $\vec{B}$  its trajectory is deflected due to the Lorentz force. The magnitude and

the direction of the particle deflections are functions of the rest mass  $m_0$  and the charge q of the particle: two particles having opposite charge moving in the same direction at velocity  $\vec{v}$  will have opposite deflections; two particles having the same charge but different masses, will have different curvature radii R.

In the relativistic case one has:

$$\vec{F} = q(\vec{v} \times \vec{B})$$

$R = \frac{p}{qB} = \frac{\gamma m_0 v}{qB}$  (1.6)

By knowing the magnitude of the magnetic field and the curvature radius,

Figure 1.3: (Left) Charge dependence of deflection in magnetic field; (Right) Radius of curvature

that is the deflection angle  $\theta$ , it is possible to go back to the momentum of the charged particle  $p = \gamma m_0 v$  or, if the detector is put into a solenoidal magnetic field, one measures the transverse momentum  $p_T$  on the deflection plane  $r\phi$  of the particle.

#### 1.1.3 Occupancy, dead time and pile-up

A notion that will be used later is the *occupancy* of the detector. As it may be inferred, the occupancy has to do with the number of busy channels in a detector, that is those channels that are active since they have been hit by a particle.

The occupancy value is expressed as a percentage and it is important because it determines the hit rate of a channel and its ability to reconstruct correctly two different events.

Let's assume that we have a collision rate 50kHz and that in each collision

Figure 1.4: Illustration of the concept of pile-up, which occurs when the time between two events is comparable with the readout time. [3].

100 different particles per  $cm^2$  are produced. If we have a detector with  $10^4$  pixels per  $cm^2$  the occupancy is 2%, that is 200 pixels only are experiencing simultaneously a signal. The rate per pixel will then be:

$$r_p = 50kHz \times (2\% \ 10000) = 1kHz \tag{1.7}$$

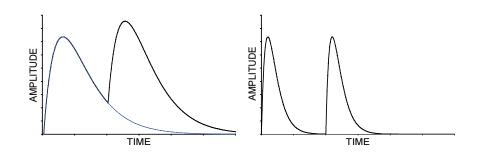

The time  $\Delta t$  required by the detector to process an event is defined as *dead* time and, in general, mainly depends on the dead time of the front-end. The latter should not be too long so that the ability of the detector to correctly detect the next event is quickly restored. In fact, when the detector is hit, it may remain sensitive or not to subsequent events: in the case in which the detector is no longer sensitive, each signal that arrives during  $\Delta t$  is missed; instead, if the detector is still sensitive the pile-up of the events occurs. In the latter case, a distortion of the signal with loss of information affect both on the first hit and the following ones. We have also a dilation of the dead time [4]. It is therefore important to estimate the pile-up probability for a given detector.

If one assumes that the time instants in which two different hits occur are statistically uncorrelated, the Poisson distribution can be used to calculate the probability to have a number of events n in the time  $\Delta t$ :

$$P(n) = \frac{(r_p \Delta t)^n e^{-r_p \Delta t}}{n!} \tag{1.8}$$

Suppose now to consider the case in which the dead time is equal to the average event rate, i.e:

$$\Delta t = \frac{1}{r_p} \tag{1.9}$$

which implies:

$$\Delta t \frac{1}{r_p} = 1 \tag{1.10}$$

With a rate of events of  $1/\Delta t$  the probability that no signal arrives while the system is in dead time is obtained with n = 0. Then (1.8) becomes:

$$P(0) = e^{-r_p \Delta t} \approx \frac{1}{e}$$

setting  $r_p \Delta t = 1$  (1.11)

that is the probability that two event are not superimposed is  $\approx 30\%$  and the pile-up probability is  $1 - P(0) \approx 70\%$ . Therefore the smaller is  $r_p\Delta t$ , that is for  $\Delta t \ll 1/r_p$ , the more the pile-up will be negligible [3].

## **1.2** Energy Loss of Heavy Charged Particles

When a particle goes through a detector it interacts with the atoms of the active material of the sensor loosing energy. The energy loss has a strong dependence ont the total energy, the mass and charge of the particle. For heavy charged particles two processes occur: the inelastic Coulomb scattering with the atomic electrons and the elastic scattering with the nuclei. However, only the former is fundamental in the interaction with a material because it is the mechanism by which the heavy charged particles release energy in the medium.

Since for each interaction with an electron the amount of energy lost by a charged particle is very small, about 1/500 of the particle energy per nucleon, and since the particle interacts with many electrons before stopping, a energy loss will result that can be represented with a continuous function. Due to the amount of energy transferred in the interaction, the atomic electrons can jump to excited states or they can be expelled from the atom, which becomes ionized. In a detector, an electric field is in general applied to sweep the electrons far from the ions and prevent recombination[6]. Finally, the number of the produced ion pairs is determined by calculating the ratio between the energy released by the particle and the average ionization energy  $E_i$ . In the case of silicon, which is of particular interest for this thesis,  $E_i = 3.6eV$ .

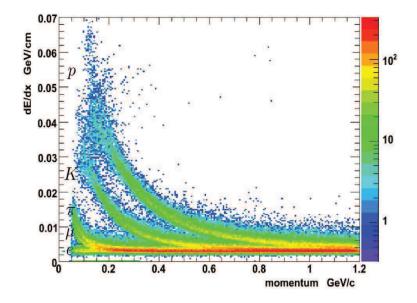

Figure 1.5: Energy Loss vs momentum for Hadrons and Leptons [5]

### 1.2.1 The Bethe-Bloch formula

The energy loss of a particle in the interaction with a material is characterized by the *linear stopping power* S that is the average energy loss per unit path length:

$$S = -\frac{dE}{dx} \tag{1.12}$$

If one takes into account the quantum-mechanical nature of the scattering between the particles that pass through the medium and the atomic electrons, one obtains the Bethe-Bloch formula for the energy loss:

$$-\langle \frac{dE}{dx} \rangle = K z^2 \frac{Z}{A\beta^2} \left[ \frac{1}{2} ln \left( \frac{2m_e c^2 \beta^2 \gamma^2 T_{max}}{I^2} \right) - \beta^2 \right]$$

(1.13)

with:

- $\langle \frac{dE}{dx} \rangle$  energy loss expressed in  $\frac{eV}{g/cm^2}$ ;

- K  $4\pi N_{av}r_e^2m_ec^2 = 0.307075MeVcm^2$  e  $r_e$  classical electron radius;

- z charge of incident particle in units of the electron charge;

Z atomic number of absorption medium (14 for silicon);

A atomic mass of absorption medium (28 for silicon);

$m_e c^2 = 0.511 MeV$  rest energy of the electron;

$\beta$  velocity of the particle in units of the speed of light;

$\gamma$  Lorentz factor defined as  $(1 - \beta^2)^{-\frac{1}{2}}$ ;

$T_{max}$  maximum kinetic energy transferred to the particle;

I mean excitation energy (137 eV for silicon).

It must be noted that  $\langle dE/dx \rangle$  depends on the characteristic of the absorber and especially on the properties of the incident particle like its charge and its mass M. The mass is contained in the expression of  $T_{max}$  and necessarily determines the behaviour of the function (1.12). Then, by measuring how particles of different masses lose energy one can identify them. figure 1.5 shows how hadrons and different leptons release energy as function of their momenta.

A particle whose energy is in the minimum of the Bethe-Bloch curve is defined as a *Minimum Ionizing Particle* or MIP.

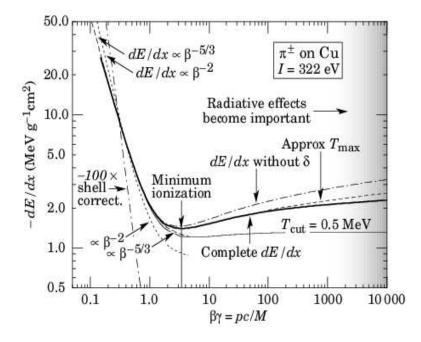

figure 1.6 shows that after the minimum  $\langle dE/dx \rangle$  slowly grows and has a plateau for high values of energy; conversely, in the low energy range ( $\beta \gamma < 1$ ) the energy loss is like  $1/\beta^2$ .

In practice, the Bethe-Bloch formula should be modified consider the effects that occur both at high and low energies, so that:

$$-\langle \frac{dE}{dx} \rangle = Kz^2 \frac{Z}{A\beta^2} \left[ \frac{1}{2} ln \left( \frac{2m_e c^2 \beta^2 \gamma^2 T_{max}}{I^2} \right) - \beta^2 - \frac{\delta}{2} - \frac{C(I, \beta\gamma)}{Z} \right]$$

(1.14)

Here two corrections are included: the density effect correction  $\delta$  and the shell correction C. The former manifests to high energies: it is due to relativistic effects that modify the electric field of the incident particle and result in a slowdown of the logarithmic slope of the function. The second one occurs at low energies, when the velocity of the traversing particle is almost similar to the speed of the electrons in the atomic shells. At such energies the assumption of stationarity of the electron with respect to the incident particle

Figure 1.6: Energy Loss in medium

breaks down [4].

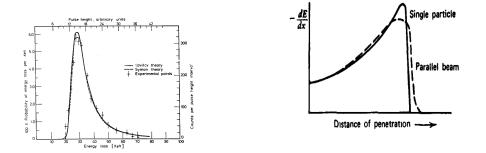

The corrected form of the Bethe Bloch formula (1.14) shows the mean value of the Landau distribution that describes the energy loss of the particle per unit path length. If a particle is not stopped in the sensor, the response varies around the peak of the distribution and there is a significant probability of high signals. This leads to the displacement of the mean value of the distribution toward energies higher than the one corresponding to the most probable value. The fluctuations of Landau distribution are due to the production of  $\delta$ -electrons, i.e. those electrons released by the atoms that have so much energy to produce further ionizations. The main consequence is a worse spatial resolution of the charge cloud because the  $\delta$ -electrons have a direction perpendicular to that of the traversing charged particle. The thinner is the sensor the more evident is the effect [2].

The number of ionizations that a particle produces changes with its kinetic energy. In the case in which the particle is completely stopped, the number of the produced electron-ion pairs increases at the end of the trajectory (fig 1.7) because the energy loss per unit path length is greater at the end of the

Figure 1.7: (Left) Landau Distribution: probability of energy loss; (Right) Bragg's curve: number of ionizations for single particle and parallel beam. [4]

path rather than at the beginning.

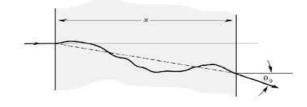

## 1.2.2 Multiple Scattering

A traversing particle is scattered by the atomic electron but also by the atomic nuclei. In the realistic hypothesis that the latter are heavier than the incident particles, the energy loss during the Coulomb scattering is negligible (elastic scattering) and the particles are just deflected. While a particle crosses the detector, multiple collisions occur and the particle trajectory can be significantly perturbed (multiple scattering). Multiple scattering worsens the space resolution on the particle track, thereby reducing also the impact parameter resolution  $\sigma_b$ .

The distribution of the scattering angles is mostly Gaussian with a rms given

Figure 1.8: Multiple scattering

$$\vartheta_{plane}^{rms} = \frac{13.6MeV}{\beta pc} z \sqrt{\frac{x}{X_0}} \Big[ 1 + 0.038 ln \Big(\frac{x}{X_0}\Big) \Big] \tag{1.15}$$

where  $\vartheta$  is expressed in rad,  $\beta$  is a velocity of the particle in unit of speed of light, p is the momentum of the particles expressed in MeV/c and z is a charge of the particle.  $X_0$  is defined as *radiation length* and it is a specific property of each material. For example, the radiation length of silicon, the most common material used for sensors, is 9.36 cm.  $X_0$  indicates how long one electron can travel in a material before its energy is reduced to 1/e of the the initial value  $E_0$  because of Bremsstrahlung:

$$E = E_0^{-\frac{x}{X_0}}$$

(1.16)

I must be point out that the appearance of  $X_0$  in the multiple scattering formula is fortuitous.

## **1.3** Silicon Sensors

Three key requirements of particle detectors are:

- Speed, in order to allow to study as many events as possible.

- Spatial resolution, to allow precise tracking and momentum measurement

- Radiation hardness, since in many experiments the sensors are exposed to significant amounts of both ionizing and not inionizing radiation.

Semiconductor detectors are widely used as they satisfy all the above requirements. In particular, silicon detectors provides the best spatial resolution and also a good energy resolution. In addition, it is possible to design very thin silicon detectors to minimize multiple scattering. Due to their radiation hardness, the can be located close to the interaction point with the main consequences of improving the impact parameter resolution and the separation of multiple tracks.

Silicon is a semiconductor material with an energy gap of 1.12 eV. The average energy required to generate an electron-ion pair is only 3.6 eV. It has an atomic number Z = 14 and a high atomic density, about 2330  $kg/m^3$ .

by:

These are fundamental properties to measure  $\langle dE/dx \rangle$  and for track reconstruction (see eq. 1.13). In addition, the high mobility<sup>1</sup> of the charge carriers in the semiconductor, even if at room temperature, is such that the charge collection time is very fast.

Four technologies of silicon sensors are examined in the following: the Hybrid Pixel and Monolithic Active Pixel Detectors, the Silicon Drift Detector, the Silicon Strip Detector. These devices have a different electrode segmentation but are all formed by a p-n junction that is reversely biased to deplete as much as possible the sensitive volume (depletion zone) of the sensor.

In doing so, the charge signal produced by a traversing particle is maximized. The average number of electron-hole pairs generated by a particle in the active volume can be calculated by dividing the energy lose E by the average energy necessary to produce the charge carriers  $E_i$ :

$$Q_s = \frac{E}{E_i};\tag{1.17}$$

for example, a MIP traversing a silicon detector gives on average about 80 electron-hole pairs per  $\mu m$  path length [3].

Because of the reversed bias, in the depletion zone an electric field  $\vec{E}$  is established that accelerates the carriers of opposite sign in opposite directions. The drift velocity of carriers depends on the magnitude and the direction of  $\vec{E}$ :  $\vec{v}(z) = \mu \vec{E}(z)$  where  $\mu$  is the mobility of the carriers in a medium and z is a depth of the sensor.

The field lines remain parallel to the electrodes into the volume of the sensor but they bend on the surfaces. Then, the geometry of the electrodes and their pitch segmentation affect the resolution of the particles position.

In this context, the read out mode (analog or binary read out), the algorithm of the track reconstruction, the magnitude of the shared charge between two elements of the detector, are also very important [2].

In the case of binary read out, the response function is box-like and the resolution of a single detector is equal to the pitch of the segmentation [3]. It should be noted that the particles hit a detector randomly. Then, the average difference between the true impact position and the measured one with a uniform distribution of the particle is given by [2]:

$$\sigma_p^2 = \int_{-\frac{p}{2}}^{\frac{p}{2}} \frac{x^2}{p} dx = \frac{p^2}{12}.$$

(1.18)

<sup>&</sup>lt;sup>1</sup>Mobility of charge carriers is determined by the material considered, the temperature, the charge of the carrier and its effective mass. In the case of silicon, elctron and hole mobilities are respectively  $\mu_n = 1350 cm^2/(Vs)$  e  $\mu_p = 450 cm^2/(Vs)$ .

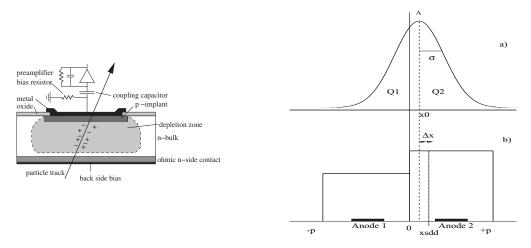

Figure 1.9: (Left) Cross section of general silicon sensor [2]; (Right) Position Resolution: a) Gaussian distribution; b) Centroid method [3].

This expression corresponds to the spatial resolution  $\sigma_p \approx 0.28p$ , i.e. setting  $p = 100 \mu m \sigma_p$  is about  $28 \mu m$ .

In addition to the drift, the thermal diffusion of the particles must be considered because it spreads the charge cloud in any direction. The thermal diffusion, too, is random with a rms width given by:

$$\sigma_y = \sqrt{2Dt} \tag{1.19}$$

where  $D^2$  is the diffusion constant of the carriers in silicon and t is the collection time.

If the charge cloud spreads out, two or more neighboring elements of the sensor share the signal charge and form a group which is called *cluster*.

While at a first glance this charge sharing degrades the performance of the sensor to exactly localize the impact point, on the other hand it improves the resolution of the position since the shared fractional charge is determined by superimposed Gaussian distribution[3]. The integral of the superimposition tend quickly to zero for deviations beyond several standard deviations: the technique to calculate the exact position of the particles is the *centroid method*.

The simplest case is with only two collection anodes that have a pitch p and measure respectively the fractional charges  $Q_1 \in Q_2$ : then, the impact point

<sup>&</sup>lt;sup>2</sup>The diffusion constant is related to the mobility of the carriers by the Einstein relation  $D = \frac{kT}{q}.$

is given by:

$$x_{cm} = \frac{-(p/2)Q_1 + (p/2)Q_2}{Q_1 + Q_2}.$$

(1.20)

If the width of the charge sharing is (s < p) and a cluster is formed by two elements only the expected  $\sigma_p$  is  $s/\sqrt{12}$ , i.e. we have an improvement of the spatial resolution. In fact, for a cluster formed by one element only the expected  $\sigma_p$  is  $(p-s)/\sqrt{12}$ . The best average spatial resolution is obtained when the number of the cluster formed by one element only is equal to those formed by two elements, i.e. if s = p/2.

An analog read out delivers a voltage proportional to the collected charge. To obtain a better spatial resolution, the rule of thumb requires that the electrodes pitch must be divided by the signal-to-noise ratio of the analog pulse. However, the spatial resolution is always limited to the value  $(p - s)/\sqrt{12}$  when a single anode is active.

In the following sections, the four technologies for the silicon sensors mentioned above are discussed.

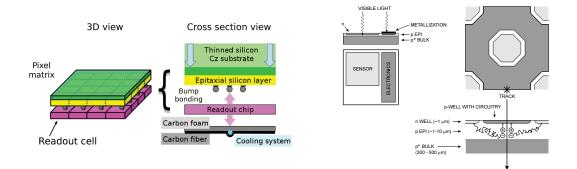

#### **1.3.1** Hybrid Pixel Detectors and MAPS

For the hybrid technology the sensor and the front-end electronics are fabricated in two distinct silicon wafers that have their own thickness <sup>3</sup> as it is shown in figure 1.15. The electrodes are segmented in two dimensions on the sensor surface to create a pixels matrix; each electrode is bump bonded with the corresponding read out cell. The connectivity between the two wafers is vertical and there is a correspondence between the matrix of the pixels and those of the read out cells, i.e. between the pixel area and those of the read out cells, i.e. between the pixel area and those of the read out cells, i.e. between the pixel area and those of the read out cells. At present, in the hybrid architecture the minimum dimensions of the pixels are  $50\mu m \times 50\mu m$  and are limited by the presence of the conductive bumps.

The pixel detectors today in use in the ALICE ITS have a cell size of  $50\mu m \times 425\mu m$ . The ALICE sensors are of the *p-in-n* type and the layer underneath the bulk is  $n^+$  type.

Two techniques are widely used to degrade the bias voltage towards the sensor edge and have a more stable electrical current in the device: multiple guardrings and edge implantation. Nowadays edges sensors are studied since the guardrings are dead zone that have an extension which ranges from a few  $\mu m$  to a few mm[8].

$<sup>^3\</sup>mathrm{A}$  detector has a total thickness about 350  $\mu m$  : 200  $\mu m$  for the pixel and 150  $\mu m$  for the front-end.

Figure 1.10: (L) Hybrid Pixel Sensors, [5]; (R) Standard MAPS, [3]

The monolithic technology is treated in detail the next section whereas here we have only a brief description.

Monolithic detectors are peculiar because they embed into the same CMOS ASIC both the sensor and the front-end electronics.

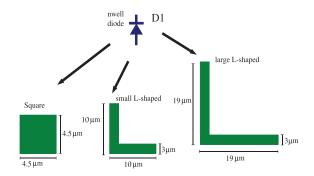

For this technology, we have different flavours of devices. For a standard monolithic active pixel sensor (standard MAPS) the sensitive volume is an p-type epitaxial layer (referred to as the "epi-layer") grown on the  $p^+$  silicon substrate. The thickness of the epi-layer ranges between 10-18  $\mu m$ , then the depletion zone is not as wide as that of hybrids.

When the impinging particle traverse the sensor, the charge generated by ionization is collected by the n-well deposited into the bulk. Since the sensor and the front-end electronics are in the same wafer the bump bonding is not needed and the size of the pixel can be reduced well belowe  $20 \ \mu m \times 20 \mu m$ . Several architectures for the monolithic sensors exist and they will be describe later: standard MAPS, quadruple well, deep n-well, CMOS sensors on high resistivity wafers.

#### **1.3.2** Silicon Strip Detectors

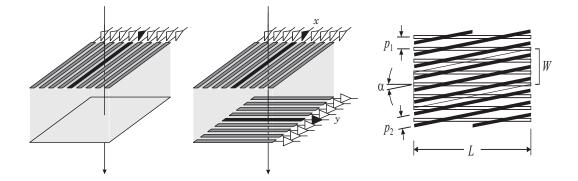

Silicon Strip Detectors (SSD) are divided into single sided and double sided. In a single sided detector, the electrodes are segmented only on one face of the wafer and the position information is unidimensional. Instead, double sided micro strips sensors give a two-dimensional information since both wafer surfaces are patterned. In this manner both the x and y coordinates can be determined. By using the SSDs it is possible to limit the number of channels with respect to that of the pixels maintaining the spatial resolution. In general, strip sensors allow also for a smaller material budget. However, the ghost hit effect is the main drawback of double sided strip sensors. This

Figure 1.11: (Left) Double-sided micro-Strip Detector: orthogonal strips; (Right)Double-sided micro-Strip Detector: stereo- angle  $\alpha$ . [3]

phenomenon occurs when two particles hit simultaneously the detector[5]. Indeed, with the layout depicted above, it is very difficult to identify the different positions of the two particles because each horizontal strip crosses more than one vertical strips. Doing so, the number of points that have to be inspected grows because each strip forms a combination with all of the strip traversing it on the othe side. A compromise solution is to form between the strips on the two opposite side a small angle  $\alpha$  named stereo angle. The number of ghost hits is minimized because the combinations between the strips are reduced.

To give a qualitative idea of the probability of the ghost hits for each of the two layouts shown in figure 1.11, let's suppose that the length of the sensing elements of each surface is respectively  $L_1$  and  $L_2$  and consider the pitches  $p_1$  and  $p_2$ . By setting  $\alpha = 90^\circ$ , the strips subtend the area  $A = L_1 \times L_2$  and the probability of ghost hit is maximized. Instead, let's suppose now  $L_1 = L_2 = L$ . In case of small *alpha* the probability of "ghosting" is reduced with the magnitude of the stereo angle as the area subtended by the strips is  $A \approx L^2(p_2/p_1) \tan \alpha + Lp_2$  [3].

Finally, it must be noted that, unlike pixels, the power of the SSD and the space occupied by its front-end electronics are not limited by the layout of the sensor.

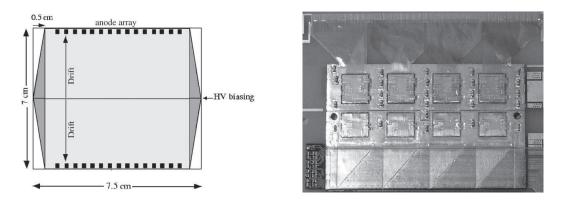

Figure 1.12: Layout of the Silicon Drift Detectors, [4]

#### 1.3.3 Silicon Drift Detector

The layout of a Silicon Drift Detector (SDD) is made depositing  $p^+$  contacts on both surfaces of a n-type silicon wafer. By doing so, two depleted zones are created that are symmetrical with respect to the central zone of the wafer. The formed  $p^+ - n$  junctions are then reverse biased to completely deplete the sensitive volume. This is necessary to allow the collection of the electronhole pairs generated when a particle traverses the sensor. The carriers so generated experience a parabolic potential. The holes are collected by the nearest  $p^+$  strips. The electrons, on the other hand, are pushed to the middle of the n-bulk and then drift to one extreme of the device. Here they are swept towards the surface where they are collected by an array of  $n^+$  contacts. Each collection electrode is connected to its own front-end electronics.

The information about the x coordinate of the impact point of the particle is obtained identifying the electrode that has given the signal. The y coordinate is deduced measuring the time t employed to the charge cloud to arrive in the collection zone and multiplying t by the drift velocity of the electrons.

By using SDD the advantage is to minimize the number of the channels necessary for the read out of a surface. In a typical SDD the pitch between the collection anodes is between 200 and 300 microns. An analog readout is then employed to measure the amplitude of the signals on the anode and the x coordinate is reconstructed by calculating the centroid of the charge distribution.

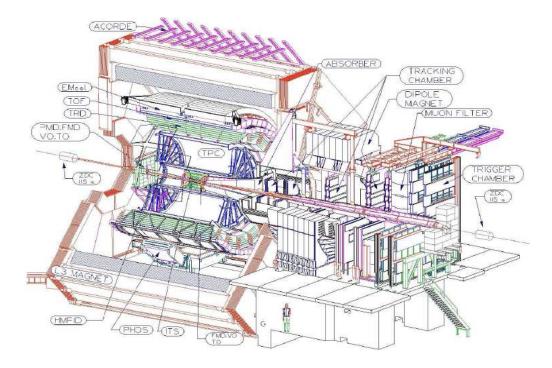

Figure 1.13: ALICE Detector [7]

## 1.4 An example: the ALICE experiment at CERN

The purpose of the ALICE experiment is to characterize the quark-gluon plasma, that should formed in the collision of ultra-relativistic heavy ions. To achieve this goal, several detectors are used. Starting from the closest layers to the beam pipe and going towards the external part, we have:

- tracking detectors:

- Inner Tracking System (ITS): it is the nearest detector to the interaction point and it is necessary to localize the primary vertex of interaction and to reconstruct the secondary vertex of hyperons and mesons D and B decay.

The ITS is also employed to identify particles with momentum below 200 MeV/c. The *Inner Tracking System* is described in the following section.

- Time-Projection Chamber (TPC): it is the main tracking detector

of the central barrel and it is employed to measure the chargedparticle momentum with a good two track separation. It is also used for particle identification.

- Particle IDentification (PID):

- Transition Radiation Detector (TRD): this device identifies electrons with momentum above 1 GeV/c whilst, below this value, particle identification is obtained through the TPC. TRD, ITS and TPC identify the particles but in different ranges of momentum. Therefore it is possible to combine their measurements to study the production of light and heavy vector-meson resonances and the dilepton continuum both in p-p and in Pb-Pb collisions.

- Time-of-Flight Detector (TOF): it is a detector used to recognize pions, kaons and protons for particles momenta ranging from 1 GeV/c to 4 GeV/c. This range of momentum overlaps with those covered by the ITS and the TPC. In fact, the TOF is employed together with these detectors to measure the energy loss of the partcles and to track and reconstruct the vertex of interaction. Doing so, the TOF provides the identification event by event of big samples of pions, kaons and protons.

- High-Momentum Particle Identification Detector (HMPID): this device is based on the ring imaging Cherenkov. Unlike the previous detectors, HMPID is devoted to the recognition of hadrons with a high transverse momentum improving the overall identification capabilities of ALICE.

- electromagnetic calorimeter:

- PHOS: it is located at 4.6 cm from the vertex of interaction and made of dense scintillating crystals. This calorimeter detects both neutral mesons and photons produced by several mechanisms as thermal production or *hard* QCD processes;

- EMCal: with Pb-scintillators, this calorimeter has the aim of measuring the *jet* production and the fragmentation function together with the others detectors of ALICE.

- Muon spectrometer: it is a device designed to detect the whole spectrum of heavy-quark resonances with a mass resolution sufficient to separate all states in the channel of decay  $\mu^+\mu^-$ .

• systems of small detectors dedicated to analyze the characteristics of some global events as the time of interaction (T0, V0, etc...) or for the triggering (FMD and PMD are multiplicity and photon detectors respectively, the ZDC calorimeter, etc..).

In ALICE the sub-detectors covers an angular range from  $45^{\circ}$ to  $135^{\circ}$ . Since to perform the measurements the magnetic fields are necessary, as in the case of the determination of the particle momentum, the smallest detectors are located into the dipolar magnetic field unlike the other ALICE detectors that are surrounded by a big solenoid producing a uniform weak magnetic field about 0.5 T [7].

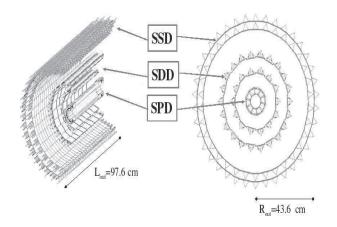

## 1.5 Inner Tracking System (ITS)

The Inner Tracking System is the nearest detector to the vertex of interaction and consists of six silicon cylindrical layers. They are coaxial and have radii from 3.9 cm to 43 cm. The front-end electronics is located on a very light weight carbon fiber frame. The inner radius measures 3.9 cm since this is the minimum length because ITS surrounds the beam pipe, i.e a 800  $\mu m$ thick beryllium tube with an outer diameter of 6 cm [7]. Instead, the outer radius of ITS is determined by the requirements to match the tracks of the ITS with those of the TPC.

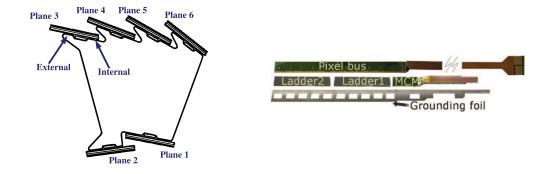

Given the required accuracy to localize the vertices of interactions ( $\approx 10 \mu m$ ), the layers of the current ITS consist of semiconductor detectors, in particular, silicon wafers properly segmented: *Silicon Pixel Detector* (SPD) on the first two layers, *Silicon Drift Detectors* (SDD) on the intermediate layers and *double-sided Silicon micro-Strip Detectors* (SSD) on the last two. The characteristics of detectors that covers ITS layers are shown in figure 1.18.

The SPDs are used for the inner layers of ITS because in this part of the central barrel there is a high density of particles (up to 100 particles per  $cm^2$ ) and highly segmented detectors are needed to achieve a good distance of closest approach (or dca) resolution. The radius of the first layer is 3.9 cm while the one of the second one is 7.6 cm. With the Silicon Pixel Detectors it is possible to determine the primary vertex position and the impact parameter of the secondary tracks due to the decay of strange, charm and beauty particles also.

The SPDs have been optimized to reduce both the material budget and the mean thickness traversed by a particle perpendicular to the detector surface. They consist of  $50\mu m \times 425\mu m$  silicon hybrid pixels that have a binary read

Figure 1.14: Current Detectors of Inner Tracking System, [7]

out[7].

The Silicon Drift Detectors equip the intermediate layers of the ITS that have a radius of 15.0 cm and 23.9 cm respectively. The sensors are 300  $\mu m$  thick. The density of the tracks for the SDD is less than for SPDs (about 7 particles per  $cm^2$ ). These detectors allow to identify the particles by measuring the energy loss dE/dx. For each track, the dE/dx is calculated using a truncated mean: if four points are measured, the three lowest points are averaged. If only three points are measured a weighted sum of the lowest and the second lowest point is executed. In addition, the SDDs allow to detect the impact parameter position.

The two outer layers of ITS are equipped with SSDs that face a small track density, about one particle per  $cm^2$  [8]. The read out of the SSDs is analog. The measurements of the position tracks detected are revealed by means of SSDs. These measurements are to be compared both with those obtained by the TPC and the data about dE/dx necessary to identify low momentum particles.

The ITS was designed for a maximum density of 8000 tracks per unit of rapidity. In this case up to 15000 tracks will have to be detected simultaneously. Furthermore, to get an occupancy of a few per cent each layer of the ITS requires several million of active cells. The spatial resolution is about a

Figure 1.15: (L) Structure of the two inner ITS layers, [7]; (R) Component of the SPDs, [10].

Figure 1.16: (L) Silicon Drift Detector in current ITS, [11]; (R) First prototype of the SPDs, [11].

few tens of  $\mu m$  but goes down up to 12  $\mu m$  for the two layers near to the primary vertex improving the impact parameter resolution. The latter have to be better than 100  $\mu m$  in the  $r\phi$  for charmed particles [9]. The properties of the current ITS are resumed in figure 1.19.

## 1.6 Limitations of current ITS and Motivations for the Upgrade

To fully accomplish the physics goals of ALICE an upgrade of the central detectors is needed.

The limitations of the current ITS concern several aspects. Besides the difficulties to access the apparatus for maintenance and repair, the drawbacks that limit the performance of the system are:

Figure 1.17: (L) Double sided micro Strip Detector in current ITS, [12]; (R) Block diagram of the front-end chip, [12].

- The limited rate that allows to use only a small fraction of the effectively produced Pb-Pb or p-p collisions in LHC. It is planned that the upgraded ITS will work with a readout rate of 50 kHz, to be compared with the 1 kHz of the present detector. This is of primary importance, expecially in case of rare probes.

- An insufficient precision in the determination of the distance of closest approach for transverse momenta below 2 GeV/c for charmed mesons.

- An unsatisfactory resolution for the tracks reconstruction for all baryons formed by more than one heavy quark (beauty e charm).

The new physics program is defined by studying the following benchmark channels [9]:

- charm meson production via  $D^0 \to K^- \pi^+$ ;

- charm baryon production via  $\Lambda_c \to p K^- \pi^+$ ;

- beauty production via

- $B \to D^{0}(\to K^{-}\pi^{+});$  $- B \to J/\psi(\to e^{+}e^{-});$  $- B \to e^{+};$

In the new ITS, the increase of the collision will increase also the amount of radiation received by the detectors with the need to have a higher radiation hardness. Furthermore, a reduction of the material budget of the detectors is

| Parameter                                      | Silicon Pixel | Silicon Drift   | Silicon Strip    |                |

|------------------------------------------------|---------------|-----------------|------------------|----------------|

| Spatial precision $r\phi$                      |               | 12              | 35               | 20             |

| Spatial precision z                            |               | 100             | 25               | 830            |

| Two track resolution $r\phi$                   |               | 100             | 200              | 300            |

| Two track resolution z                         |               | 850             | 600              | 2400           |

| Cell size                                      | $(\mu m^2)$   | $50 \times 425$ | $202 \times 294$ | 95 	imes 40000 |

| Active area per module                         | $(mm^2)$      | 12.8 × 69.6     | 72.5 × 75.3      | $73 \times 40$ |

| Readout channels per module                    |               | 40960           | $2 \times 256$   | $2 \times 768$ |

| Total number of modules                        |               | 240             | 260              | 1698           |

| Total number of readout channels               | (k)           | 9835            | 133              | 2608           |

| Total number of cells                          | (M)           | 9.84            | 23               | 2.6            |

| Max. occupancy for central Pb-Pb (inner layer) | (%)           | 2.1             | 2.5              | 4              |

| Max. occupancy for central Pb-Pb (outer layer) | (%)           | 0.6             | 1.0              | 3.3            |

| Power dissipation in barrel                    | (W)           | 1350            | 1060             | 850            |

| Power dissipation end-cap                      | (W)           | 30              | 1750             | 1150           |

Figure 1.18: Characteristics of the varius detector types, [7]

essential to limit the multiple scattering and improve the resolution. <sup>4</sup> The current impact parameter resolution does not allow to detect particles that have a decay length below  $100\mu m$ . By means of the new detector it should be possible to achieve exclusive measurement of the beauty production and obtain data with sufficient accuracy also for low momenta.

## 1.7 Options for Upgrade

At the time of this writing, two options are considered for the ITS upgrade. The first option foresees to use pixellated detector in the first three layers and double sided silicon microstrips in the four outermost layers. In this case, the pixel sensors could be either of the hybrid type or monolithics. In

<sup>&</sup>lt;sup>4</sup>The thick of the current silicon detetectors is  $\approx 350 \mu m$

|              |                   |                       | Number  | Active area              | Intrinsic            | Material    |

|--------------|-------------------|-----------------------|---------|--------------------------|----------------------|-------------|

| Layer / Type | $r [\mathrm{cm}]$ | $\pm z [\mathrm{cm}]$ | of      | per module               | resolution $[\mu m]$ | budget      |

|              |                   |                       | modules | $r\phi 	imes z \ [mm^2]$ | $r\phi$ $z$          | $X/X_0$ [%] |

| Beam pipe    | 2.94              | -                     | -       | -                        | -                    | 0.22        |

| 1 / pixel    | 3.9               | 14.1                  | 80      | $12.8 \times 70.7$       | 12 100               | 1.14        |

| 2 / pixel    | 7.6               | 14.1                  | 160     | $12.8 \times 70.7$       | 12 100               | 1.14        |

| Th. shield   | 11.5              | -                     | -       | -                        | -                    | 0.65        |

| 3 / drift    | 15.0              | 22.2                  | 84      | $70.2 \times 75.3$       | 35 25                | 1.13        |

| 4 / drift    | 23.9              | 29.7                  | 176     | $70.2 \times 75.3$       | 35 25                | 1.26        |

| Th. shield   | 31.0              | -                     | -       | -                        | -                    | 0.65        |

| 5 / strip    | 38.0              | 43.1                  | 748     | $73 \times 40$           | 20 830               | 0.83        |

| 6 / strip    | 43.0              | 48.9                  | 950     | $73 \times 40$           | 20 830               | 0.83        |

Figure 1.19: Characteristics of current ITS detectors, [7]

the second option, the ITS will consist only of pixel detectors. The cost of hybrid pixel sensors prevent them from beign used to cover large surfaces. Therefore, the second scenario implies the use of monolithic CMOS sensors for the whole apparatus. CMOS sensors offer the obvious advantages of allowing for smaller pixels and reduced cost. However, their capability of whistanding the radiation doses required in the inner part of ALICE is not yet fully demonstrated. For this reason, a dedicated R&D is in progress within the ALICE collaboration. The results obtained on first prototypes are however very encouraging and this weight the balance more in favor of the monolithic option. At larger radii, the use of monolithics poses challenges for what concern the integration and the power dissipation. In fact, the size of monolithic sensors is limited by the reticle size used in the production of CMOS chips, which can be in the order of 2 cm×3 cm. The use of such small sensors to cover large area may result in additional inneficiency. A particular procedure, called stiching, allows to produce CMOS sensors which are larger then the reticle size. In this way, sensors with a surface comparable with the one of a standard microstrip detectors could be fabricated. However, the yield of such large structures must be assessed. Another concern in using of CMOS sensors at larger radii is their power consumption, which is still higher than the one found in a typical strip sensors. Finally, it must be mentioned that the use of four layers of strips will allow to maintain in the future tracker a particle identification capability comparable with the one of the present ITS. Simulations have also suggested that a sufficient, although not optimal, PID performance could be provided by equipping seven layers of monolithic sensors with analog readout. The final layout will be chosen by the end of 2013. Several technologies are considered to design of the frontend electronics. In particular, 0.13  $\mu m$  CMOS technology could replace the  $0.25 \ \mu m$  CMOS technology currently used for the LHC detectors. The 0.13  $\mu m$  CMOS is to be preferred because of its radiation tolerance: indeed, the reduced dimensions of this technology causes the smaller capacitance of the digital gates and the lower power supply voltage reduces the digital power consumption. Finally, the 0.13  $\mu m$  CMOS technology is very versatile then permits to avoid interferences between digital and analog blocks [8].

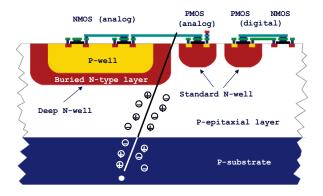

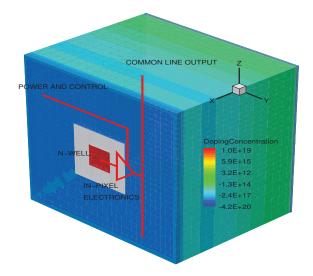

The last technology considered for the upgrade of ALICE, that will be likely used, is offered by TOWER/JAZZ: this is a 0.18  $\mu m$  quadruple well CMOS standard process widely used for image sensors. This technology has been identified as the most promising candidate for dedicated R&D in ALICE since it has some interesting features:

- 1. A high resistivity epitaxial layer up to 18  $\mu m$  thick and a gate oxide thickness below 4nm which make the sensor more robust to the dose radiation;

- 2. The resistivity of the epitaxial layer ranges from 1 k $\Omega$ cm to 5 k $\Omega$ cm, thus the 18  $\mu m$  thick epitaxial layer can be depleted by applying a revers bias between 1-2 V, in order to increase both the signal-to-noise ratio and the radiation hardness;

- 3. The possibility to fabricate in same pixel area both PMOS and NMOS to make more complex in-pixel signal processing [8].

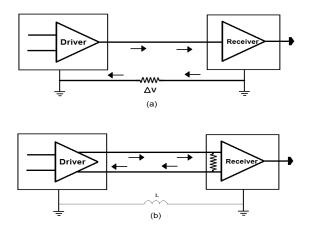

In any case, the signals which are registered in the sensor chip will be sent out by using a LVDS transmission in order to minimize the ground loop effect and the switching noise. By means of the LVDS transmission the current direction can be varied in order to transmit two different logic level.

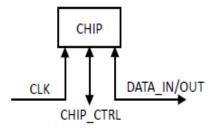

Figure 1.20: I/O of a single chip, [?]

In figure 1.20 a schematic view of the data transmission in showed. The CLK is a master clock which controls the on chip synchronous logic levels and it is unidirectional (input of the chip); the CHIP\_CTRL and the DAT\_IN/OUT are bidirectional: the first one controls the write/red chip configuration an provides trigger information and global asynchronous reset whereas the second one sends out the stored signals.

# Chapter 2

# Monolithic Active Pixel Sensors

Monolithic Active Pixels (MAPS) are of central interest for the ITS upgrade. Actually, MAPS can be thinned down to 50  $\mu$ m or less. Furthermore, the may allow a significant cost reduction due to the use of standard CMOS technologies for their production and because no hybridization processes is needed. In fact, unlike hybrid pixels, in the monolithics both the sensor and read out electronics are in the same wafer. With MAPS, very small pixels can be achieved (pixel smaller than 2  $\mu$ m × 2  $\mu$ m are already in production) even though the size of a pixel used in high energy physics is in general bigger than 10  $\mu$ m × 10  $\mu$ m. In fact, a pixel as large as 100  $\mu$ m is often already adequate.

A silicon wafer used for standard CMOS technologies for the electronics (*electronic grade*) needs to have low resistivity and is grown by the Czochralski method. Unfortunately, this technique leave in the silicon bulk both crystalline defects and atoms of impurities, like oxygen. In addition, also the formation of structural defects may occur. Instead, a *detector grade* silicon must have a high resistivity that allows to deplete easily the sensitive volume. A low density of defects is also necessary to reduce both the generation and the recombination of the carriers by the mechanism of trapping that modify the leakage current flowing in the device. Because of monolithic integration it has been necessary to match both the requirement of high resistivity for the sensor and low resistivity for the electronics. This is made by growing a silicon epitaxial layer on the Czochralski substrate, with the advantage to have a very ordered epitaxial layer with a poor probability to incorporate impurities, i.e. an epy-layer with a low density defects. The overall thickness occupied by sensor and electronics can be reduced to less than 50  $\mu m$ .

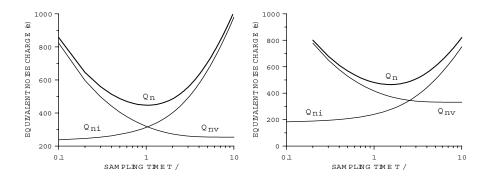

The operating principle of a MAPS is based on the creation of p-n junction that works for the collection of the charge produced by a ionizing particle traversing a detector. The carriers so generated into the device move because of thermal diffusion, so the time necessary to collect the charge is comparatively long,  $\approx 100 \ ns$ . Due to the long collection time, the probability of charge recombination is increased. This may become a probelm when the devices are exposed to non-ionizing radiation that damages the silicon bulk. An alternative solution to the active pixel sensors (APS), still using the monolithic integration of both sensor and read out electronics, requires the application of reverse bias to the collection diode: in this manner the depletion of the sensible volume is driven and the transport of the charge is mainly due to the drift, so the charge collection is very fast.

This chapter starts with a review of the working principle of a p-n junction, i.e the sensor key structure.

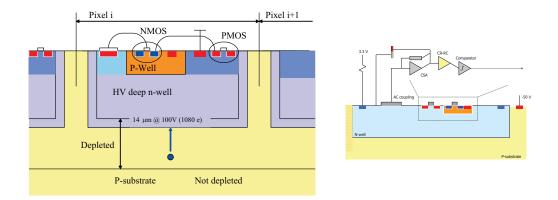

In the section 2.2 the principle of operation of standard MAPS is shown: these sensors, even if they have many interesting features for a tracking detector, exhibit some limitations about the components that it is possible to use for the read out. Two modified designs allow to overcome limits imposed by the layout of standard MAPS and they are discussed in sections 2.3 (DNW MAPS) and 2.4 (INMAPS).

In the sensors mentioned up to now, charge is collected by diffusion; instead, in both LePix (section 2.5) and pixel detectors in high voltage CMOS technology (section 2.6) an electrical field is applied to speed up the collection process.

In conclusion general aspects about the singal readout in monolithic sensors are discussed. In section 2.7 the amplifiers used for a MAPS are analyzed while in section 2.8 the Correlated Double Sampling technique is described since it is employed to remove both offset and low frequency noise that affect the signal charge measured by each pixel.

# 2.1 P-n junction

Silicon is a semiconductor widely employed in electronics since its resistivity can be modified by means of the doping with donors (n-type) or acceptors (p-type).

The resistivity of silicon doped with a  $n_p$  density of acceptors and  $n_n$  of donors is given by:

$$\rho = \frac{1}{q(\mu_n n_n + \mu_p n_p)} \tag{2.1}$$

$\rho$  can be varied adjusting the density of the dopants. For example, setting  $n_p >> n_n$  the majority charge carriers in the material are the holes so the

silicon resistivity is  $\rho \approx 1/(q\mu_p n_p)$ . The doping levels are typically  $10^{14} - 10^{19}$  atoms/cm<sup>3</sup>.

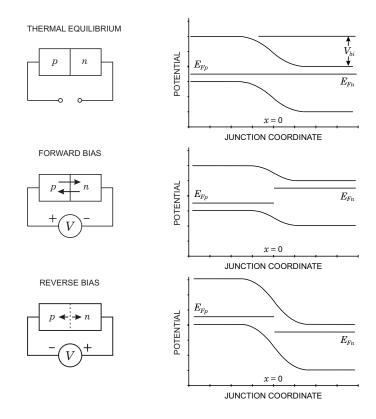

When two regions of a semiconductor are doped with complementary impurities, such as p-type and n-type regions, a p-n junction is formed. Because of the gradient of concentrations of holes as well as electrons between the two regions in the material, the thermal diffusion will drive the majority charge carriers across the junction, leaving in the p-type region an excess of negative ions and in the n-type an excess of positive ions. Therefore, a region of non-mobile space charge is formed. The potential barrier  $V_{bi}$  is generated between the two space charge densities. This potential prevents electrons and holes from diffusing further. In other words, between the space charge densities the electrical field  $\vec{\mathcal{E}}$  is established and it accelerates particles of opposite charges in opposite direction.

No mobile charge carrier is in the central zone of the junction that, for this reason, is named depletion zone: its spatial extent W depends on the doping levels with donors  $N_D$  for the *n* region or acceptors  $N_A$  for the *p* region:

$$W = \sqrt{\frac{2\epsilon_s V_{bi}}{q} \left(\frac{1}{N_A} + \frac{1}{N_D}\right)} \tag{2.2}$$

where  $\epsilon_s$  is the silicon dielectric constant and q is the electrical charge. Since the density of the dopants are not symmetrical, W is wider in the part in which the doping level is lower. For example, if we consider  $N_D >> N_A$ , where the junction is asymmetrical with a very strong doping level of the n region  $(p - n^+)$ , the depletion zone is more extended in the p region than in the n region.

When a ionizing particle hits the diode and traverses the depletion zone, it loses energy according to the formula (1.13). The energy lost causes the generation of the free charge carriers that are efficiently separated by the electrical field of the junction.

Having a large depletion zone implies to increase the size of the sensitive volume of the diode and, consequently, the magnitude of the registered signal. The depletion zone can be widened by reverse biasing the junction, i.e. connecting the p region to a lower voltage then the n region:

$$W = \sqrt{\frac{2\epsilon_s(V_{bi} + V)}{q} \left(\frac{1}{N_A} + \frac{1}{N_D}\right)}$$

(2.3)

This fact rises the height of the potential barriers for majority charge carriers in each part of the diode, so stopping their diffusion. However, the

Figure 2.1: p-n junction: the height of the potential barriers changes depending on the bias, [3].

reverse bias that can be applied to the junction is limited because too high values can lead to junction breakdown.

The negative potential difference at the junction limits the thermal diffusion of the carriers, but the minority charge carriers<sup>1</sup> can move across the junction. Thermally generated carriers in the depletion region are swept by the electric field, generating a leakage current. The leakage current depends on the intrinsic carrier concentration  $n_i$  of the silicon  $(n_i = 1.45 \cdot 10^{10} cm^{-3})$ , the diffusion constant  $D_{p,n}$  of both holes and electrons, the diffusion length  $L_{p,n}$ of the charge carriers <sup>2</sup> and on the diode section A:

$$I_s = -q \left[ \frac{D_n}{L_n N_A} + \frac{D_p}{L_p N_D} \right] n_i^2 A \tag{2.4}$$

Since the concentration of minority carriers is lower than that of the majority carriers, the current  $I_s$  is very low, about nA in silicon.

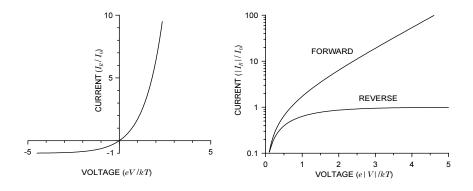

In the junction diode the electrical current flows in one direction only: this is a feature of this device. In fact, when the diode is forward biased the magnitude of the potential barrier between the junction is lowered, in favor of the minority carriers current. The ideal I-V characteristics of the diode is then:

$$I = I_s (e^{\frac{qV}{k_B T}} - 1)$$

(2.5)

where V is the tension applied (forward or reverse bias); this characteristics is shown in figure 2.2.

Because of the opposite ions in the two regions of the p-n junction, a diode resembles a capacitor which has a capacitance given by  $C_j = (\epsilon_s A)/W$ . The capacitance hence depends on the section of the diode as well as on the length of the depletion zone, i.e.  $C_j = (\epsilon_s A)/W$  depends on the doping levels of the n and p regions [2]. The value of  $C_j$  is important for the charge conversion efficiency (from current signal to voltage signal) as well as for its influence on the thermal noise of the front-end electronics. However,  $C_j$  does not affect the shot noise  $i_n$  that is given by  $i_n = \sqrt{2qI_g\Delta f}$ , where  $I_g$  is the electrical current generated by a particles that traverses the device and  $\Delta f$  is the bandwidth.

<sup>&</sup>lt;sup>1</sup>Minority carriers are electrons in a p-region or holes in n-region

<sup>&</sup>lt;sup>2</sup>The diffusion length is the mean specific distance that a free charge covers in the material because of the thermal diffusion, before recombining it with a carriers of opposite charge.  $L_{p,n}$  is given by:  $L_{p,n} = \sqrt{D_{p,n}\tau_{p,n}}$ , where  $\tau \approx \mu s$  is the time needed for a decrease of 1/e of the minority carriers.

Figure 2.2: I-V characteristics[3]

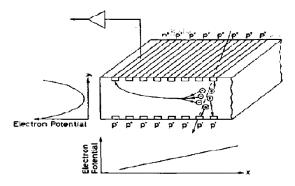

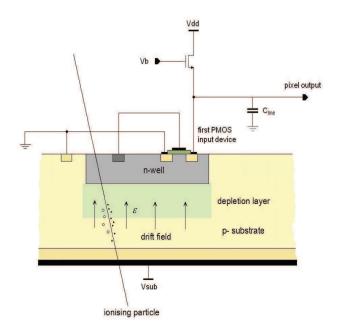

## 2.2 Standard MAPS

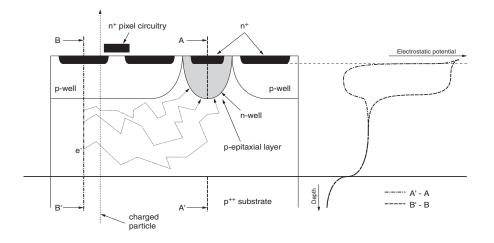

A standard MAPS is made of a silicon substrate at low resistivity heavily doped with p-impurities. On the substrate, a p-doped epitaxial layer (p epilayer) is grown. The p epi-layer can be up to 20  $\mu m$  thick. Moving towards the surface there is a n-well<sup>3</sup>, forming with the p epi-layer the collection charge diode. Under the n-well, a thin depletion region is formed in which the electrons generated in the sensitive volume, that is in the epi-layer, are collected.

The doping level  $p^-$  of the epi-layer is much smaller from that of the  $p^{++}$  substrate as well as of that of  $p^+$  p-wells: this is the reason why a depletion region is formed. The charge generated in the undepleted epi-layer move because of thermal diffusion. When they reach the depletion region associated to a nwell-p-epi junction they are collected by the electric field present in the depletion zone.

Actually, the charge carriers are also generated in the substrate but here the probability of charge recombination is very high. In fact, the carriers move in the bulk driven by the thermal diffusion, so they are fairly slow. In addition, the substrate is very thick and has a very high doping level. All this implies that the generated particles recombine each others before bing collected so they do not contribute to the signal current in the detector.

<sup>&</sup>lt;sup>3</sup>The doping level of the n-well is typically about 10<sup>18</sup> atomi/cm<sup>3</sup>.

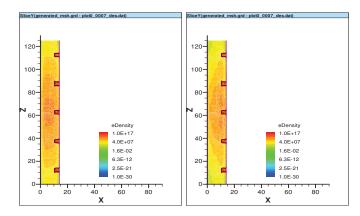

Figure 2.3: Standard MAPS operating principle: (L) Charge Diffusion in the p epi-layer; (R) Potential distribution in the device. [2]

Since the sensitive volume is very thin, the charge signal collected is weaker ( $\approx 1000e^{-}$ ) compared to that produced in the hybrid pixels, so the noise in the read out electronics circuitry must be minimized [13].

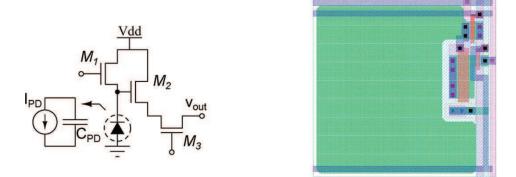

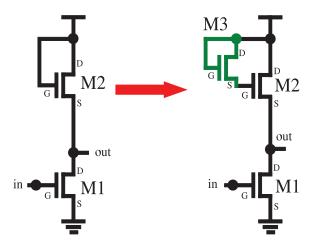

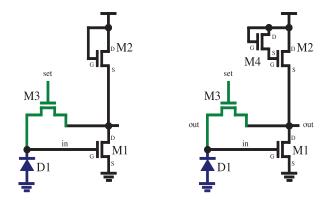

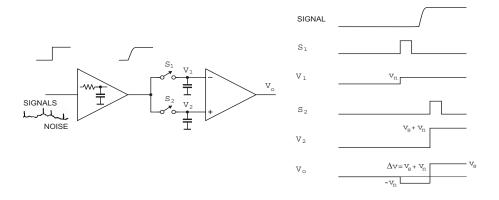

The simpler and most compact structure of a MAPS pixel is shown in figure 2.4: the collection diode is modeled by a current source with a capacitance  $C_{PD}$  in parallel, while the read out circuit is formed by three NMOS transistors (3T architecture).

$M_1$  is the reset transistor necessary to restore the dc bias point of the diode after each readout and to charge the diode capacitance at the power supply  $V_{dd}$ ;  $M_2$  is a source follower;  $M_3$  is a pass transistor connected to the read out electronics, through which the output is accessed [14].

The circuit shown in figure 2.4 converts the current generated in the diode into the voltage output  $v_{out}$  of the pixel.  $v_{out}$  depends on the capacitance  $C_{PD}$  as well as on the gain<sup>4</sup>  $A_{SF}$  is the gain of the source follower which it is

<sup>&</sup>lt;sup>4</sup>With a small signal model the gain of the source follower is  $\frac{v_{out}}{v_{in}} = \frac{g_m}{g_m + g_{mb}} \approx \frac{1}{1 + 1/3} < 1$ . Here:  $g_m$  is the transconductance of the transistor that generally depends on the size of the device;  $g_{mb}$  is the bulk transconductance that represents the effect of on the current of the voltage variation between source and bulk when the source is not grounded.

Figure 2.4: (L) The 3T Pixel Circuit with NMOS transistors ; (R) Layout of the 3T pixel circuit . [14]

below one:

$$v_{out} = A_{SF} \frac{1}{C_{PD}} \int I_{PD} dt \tag{2.6}$$

The formula 2.6 shows that to obtain an high voltage output the value of the capacitance  $C_{PD}$  must be minimized, which implies a small collection electrode. The further advantage in using the 3T architecture is the reduction of power consumption since the amplifier circuit can be turned on only when the pixel is read.

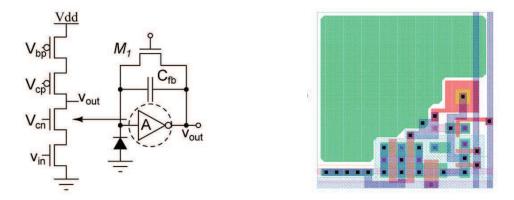

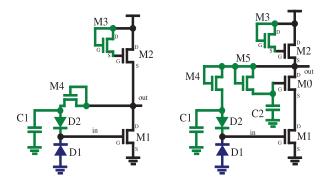

A more complex circuit used for the pixels is the CTIA, i.e. *Capacitive Transimpedance Amplifier*, shown in figure 2.5. Here A is a single stage cascode amplifier designed with both NMOS and PMOS transistors and it is AC coupled to the sensing diode.

Transistor  $M_1$  is a reset switch: it will be on to discharge the capacitor  $C_{fb}$ and off at the beginning the integration time. In the CTIA architecture  $v_{out}$  depends on the feedback capacitance <sup>5</sup>: this is an advantage over 3T architecture in which  $v_{out}$  is determined by the diode capacitance that it is difficult to control since it depends of several quantities, e.g. the width of the depletion region.

With  $C_{fb} \ll C_{PD}$  and for high gain of the amplifier (in this context the cascode configuration is fundamental), the circuit effectively pins the diode output and drives the current  $I_{PD}$  to charge the feedback capacitance. Then,

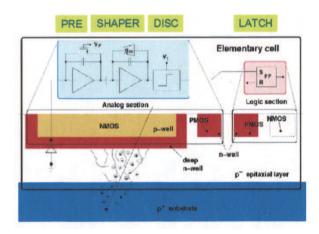

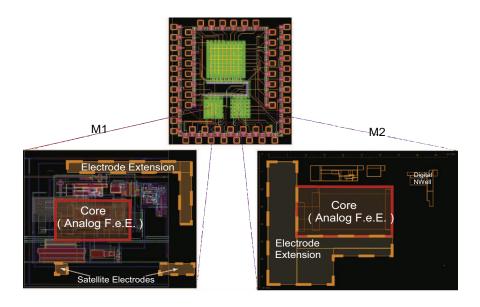

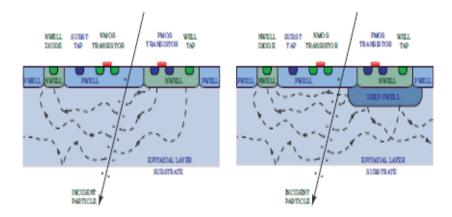

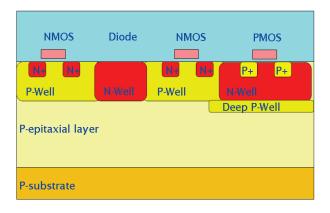

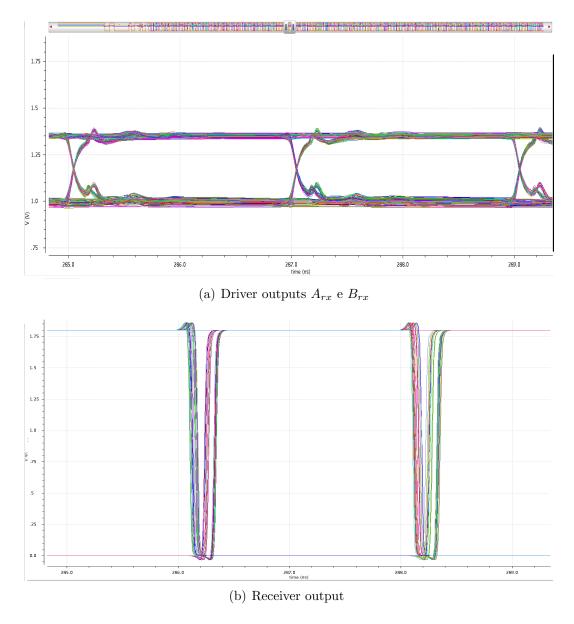

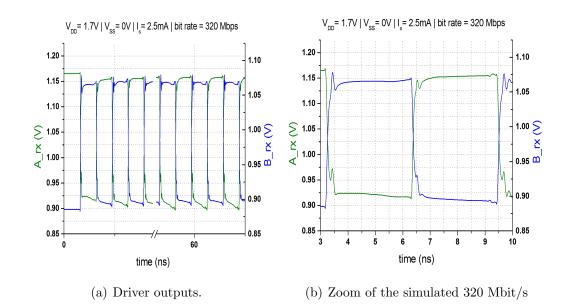

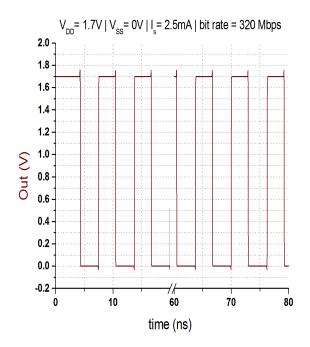

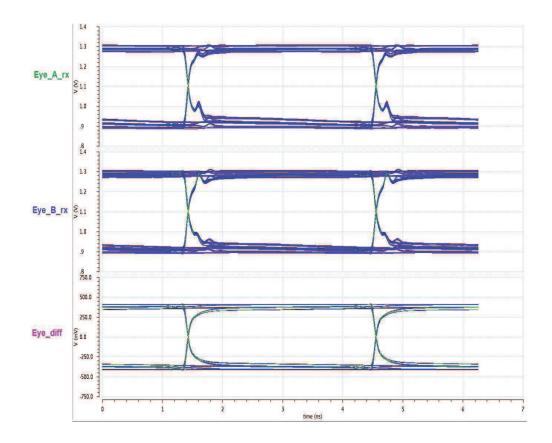

<sup>&</sup>lt;sup>5</sup>The equation of the circuit is given by:  $I_{PD(s)} + \frac{v_{out(s)}}{A}sC_{PD} + \left(\frac{v_{out(s)}}{A} - v_{out(s)}\right)sC_{fb} = 0$