## Università degli Studi di Torino Scuola di Dottorato in Scienza ed Alta Tecnologia

Indirizzo di Fisica ed Astrofisica

# LePix: Monolithic Sensor for Particle Tracking in a 90 nm CMOS technology

Author: Potenza Alberto

Supervisor: Prof. M. Costa Co-Supervisor: Dott. A. Rivetti External Reviewer: Prof. G. Dalla Betta

# Contents

| 1        | Hybrid Pixel Sensors8                                                                                 |                                                                                                                                                                                                                                 |                                                                                                |  |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|--|--|

|          | 1.1                                                                                                   | HEP Experiments                                                                                                                                                                                                                 | 8                                                                                              |  |  |  |  |

|          | 1.2                                                                                                   | Hybrid Pixel Detectors                                                                                                                                                                                                          | 11                                                                                             |  |  |  |  |

|          |                                                                                                       | 1.2.1 Sensor $\ldots$                                                                                                                                                                                                           | 11                                                                                             |  |  |  |  |

|          |                                                                                                       | 1.2.2 Front-end Electronics                                                                                                                                                                                                     | 17                                                                                             |  |  |  |  |

|          |                                                                                                       | 1.2.3 Noise Analysis                                                                                                                                                                                                            | 20                                                                                             |  |  |  |  |

| <b>2</b> | Mo                                                                                                    | nolithic Sensors                                                                                                                                                                                                                | 26                                                                                             |  |  |  |  |

|          | 2.1                                                                                                   | Monolithic Active Pixel Sensors                                                                                                                                                                                                 | 26                                                                                             |  |  |  |  |

|          | 2.2                                                                                                   | Deep N-well MAPS                                                                                                                                                                                                                | 33                                                                                             |  |  |  |  |

|          | 2.3                                                                                                   | INMAPS                                                                                                                                                                                                                          | 35                                                                                             |  |  |  |  |

|          | 2.4                                                                                                   | High Voltage MAPS                                                                                                                                                                                                               | 37                                                                                             |  |  |  |  |

|          | 2.5                                                                                                   | Silicon on Insulator                                                                                                                                                                                                            | 41                                                                                             |  |  |  |  |

|          |                                                                                                       |                                                                                                                                                                                                                                 |                                                                                                |  |  |  |  |

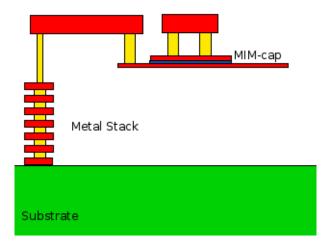

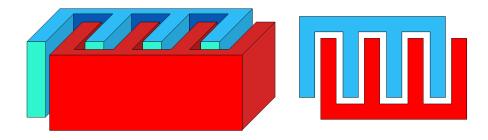

| 3        | LeP                                                                                                   | Pix                                                                                                                                                                                                                             | 44                                                                                             |  |  |  |  |

| 3        | <b>LeF</b><br>3.1                                                                                     |                                                                                                                                                                                                                                 | <b>44</b><br>44                                                                                |  |  |  |  |

| 3        |                                                                                                       | Technology Choice                                                                                                                                                                                                               |                                                                                                |  |  |  |  |

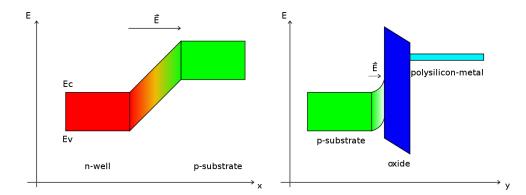

| 3        | 3.1                                                                                                   | Technology Choice       Sensor Principle                                                                                                                                                                                        | 44                                                                                             |  |  |  |  |

| 3        | $3.1 \\ 3.2$                                                                                          | Technology Choice                                                                                                                                                                                                               | 44<br>46                                                                                       |  |  |  |  |

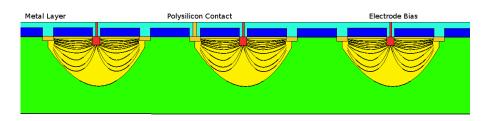

| 3        | 3.1<br>3.2<br>3.3<br>3.4                                                                              | Technology Choice                                                                                                                                                                                                               | 44<br>46<br>47                                                                                 |  |  |  |  |

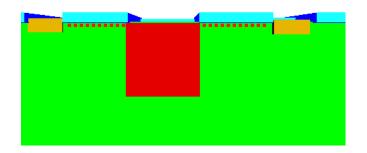

|          | 3.1<br>3.2<br>3.3<br>3.4                                                                              | Technology Choice       Sensor Principle         Sensor Principle       Device Design         Device Design       Practical Device Implementation         Practical Device Implementation       Practical Device Implementation | 44<br>46<br>47<br>52                                                                           |  |  |  |  |

|          | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>Dio</li> </ul>                           | Technology Choice                                                                                                                                                                                                               | <ul> <li>44</li> <li>46</li> <li>47</li> <li>52</li> <li>56</li> </ul>                         |  |  |  |  |

|          | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>Dio</li> <li>4.1</li> </ul>              | Technology Choice                                                                                                                                                                                                               | <ul> <li>44</li> <li>46</li> <li>47</li> <li>52</li> <li>56</li> </ul>                         |  |  |  |  |

|          | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>Dio</li> <li>4.1</li> <li>4.2</li> </ul> | Technology Choice                                                                                                                                                                                                               | 44<br>46<br>47<br>52<br><b>56</b><br>56<br>58                                                  |  |  |  |  |

|          | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>Dio</li> <li>4.1</li> <li>4.2</li> </ul> | Technology Choice                                                                                                                                                                                                               | <ul> <li>44</li> <li>46</li> <li>47</li> <li>52</li> <li>56</li> <li>58</li> <li>61</li> </ul> |  |  |  |  |

| <b>5</b> | Bre                                | akdown Structure 71              |  |  |  |  |  |  |  |

|----------|------------------------------------|----------------------------------|--|--|--|--|--|--|--|

|          | 5.1                                | Breakdown Structure Strategy     |  |  |  |  |  |  |  |

|          | 5.2                                | Experimental Set-Up              |  |  |  |  |  |  |  |

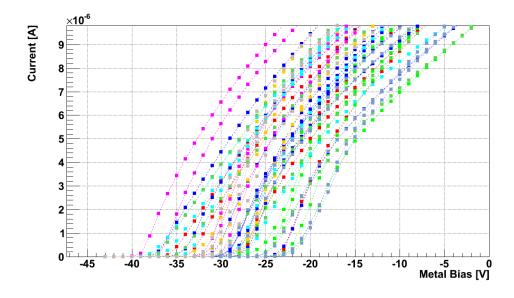

|          | 5.3                                | Measurement Results              |  |  |  |  |  |  |  |

|          |                                    | 5.3.1 Polysilicon Gate           |  |  |  |  |  |  |  |

|          |                                    | 5.3.2 Metal Gate                 |  |  |  |  |  |  |  |

|          | 5.4                                | Conclusions                      |  |  |  |  |  |  |  |

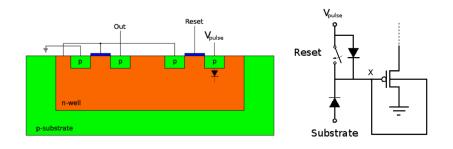

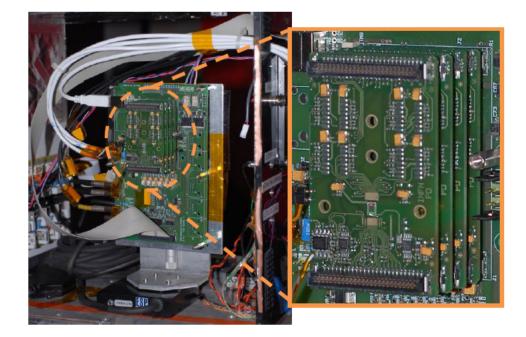

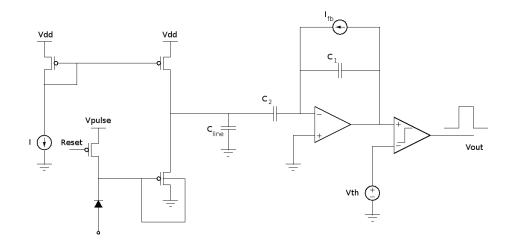

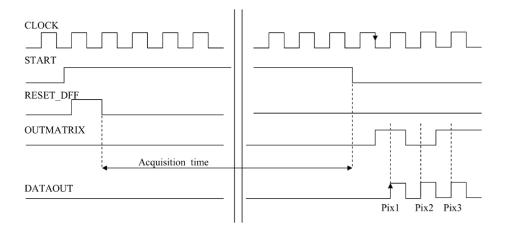

| 6        | Analog Front-end Matrix 87         |                                  |  |  |  |  |  |  |  |

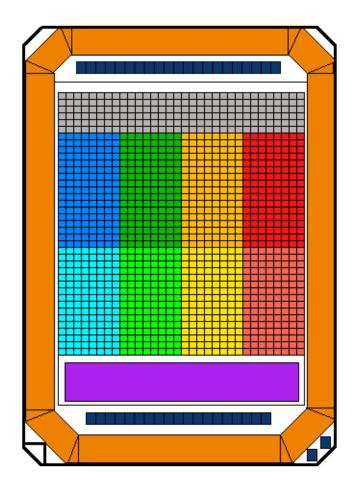

|          | 6.1                                | Matrix Strategy                  |  |  |  |  |  |  |  |

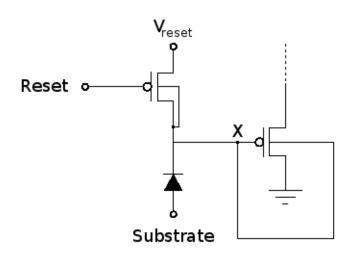

|          | 6.2                                | Pixel Cell                       |  |  |  |  |  |  |  |

|          | 6.3                                | Correlated Double Sampling       |  |  |  |  |  |  |  |

|          | 6.4                                | Experimental Equipment           |  |  |  |  |  |  |  |

| 7        | Ana                                | alog Matrix Characterization 104 |  |  |  |  |  |  |  |

|          | 7.1                                | Equipment and Bias               |  |  |  |  |  |  |  |

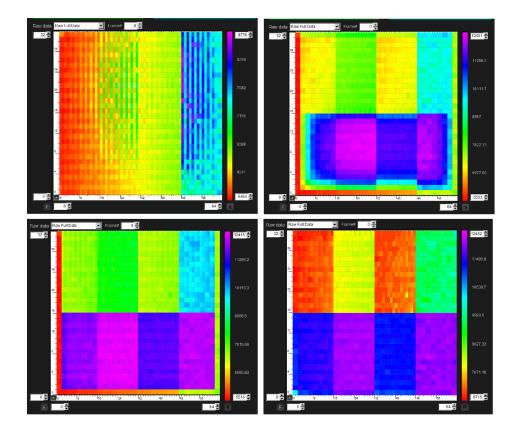

|          |                                    | Characterization                 |  |  |  |  |  |  |  |

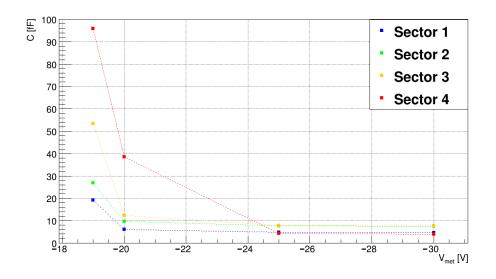

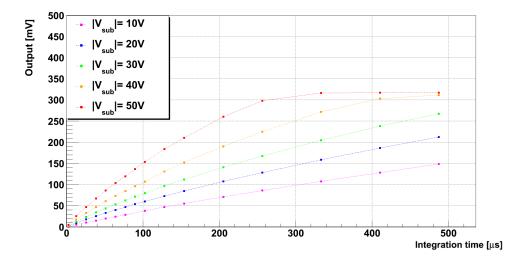

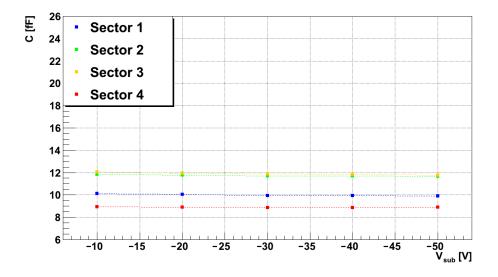

|          | 7.2                                | Sensor Capacitance               |  |  |  |  |  |  |  |

|          |                                    | Evaluation                       |  |  |  |  |  |  |  |

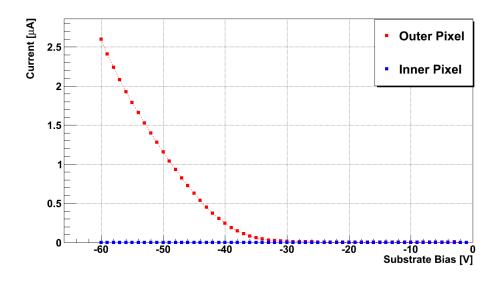

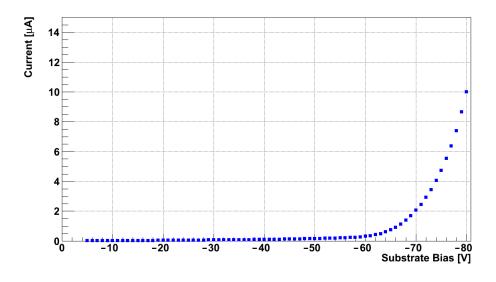

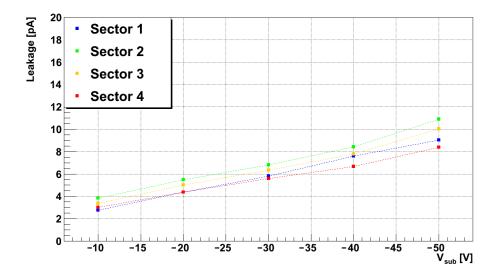

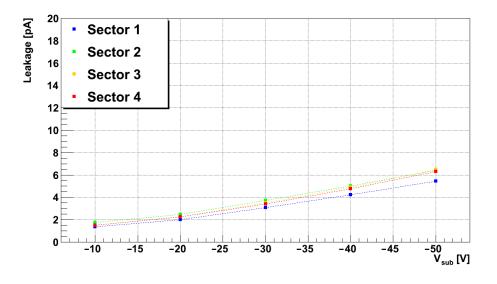

|          | 7.3                                | Leakage Current                  |  |  |  |  |  |  |  |

|          |                                    | Evaluation                       |  |  |  |  |  |  |  |

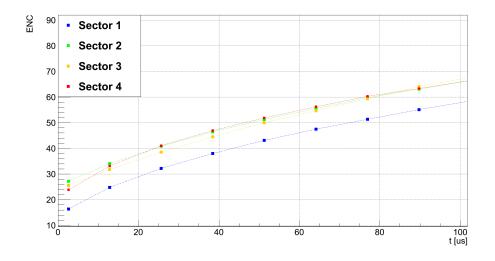

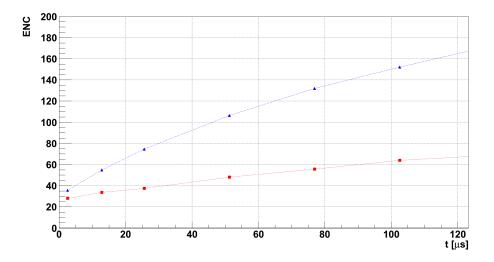

|          | 7.4                                | Matrix Noise                     |  |  |  |  |  |  |  |

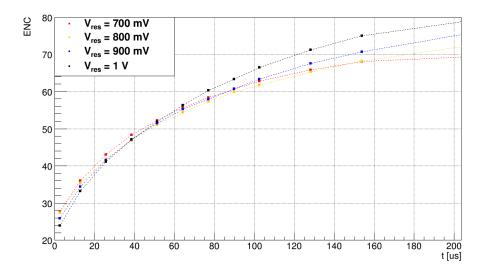

|          | 7.5                                | Larger Electrode Matrix          |  |  |  |  |  |  |  |

|          | 7.6                                | Conclusions                      |  |  |  |  |  |  |  |

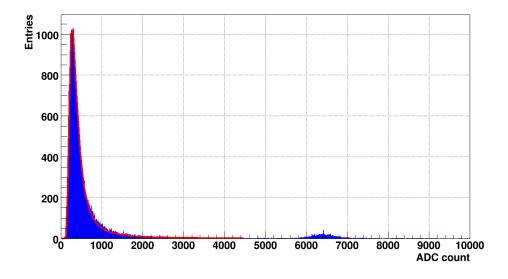

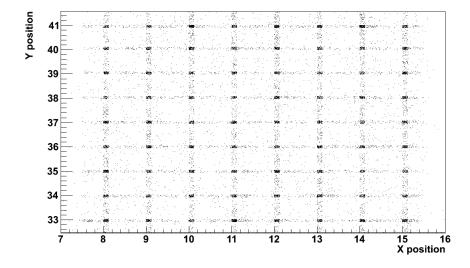

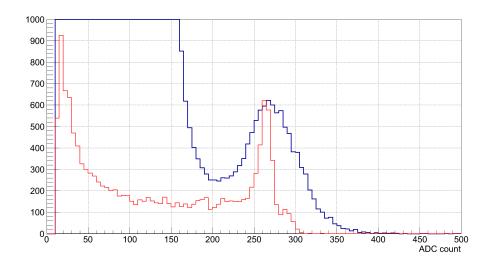

| 8        | Charge Collection Measurements 126 |                                  |  |  |  |  |  |  |  |

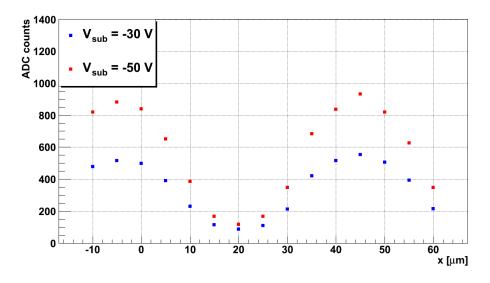

|          | 8.1                                | Laser Test                       |  |  |  |  |  |  |  |

|          | 8.2                                | X-Ray Source                     |  |  |  |  |  |  |  |

|          | 8.3                                | Beam Test                        |  |  |  |  |  |  |  |

|          | 8.4                                | Conclusions                      |  |  |  |  |  |  |  |

| 9        | Radiation Hardness 151             |                                  |  |  |  |  |  |  |  |

|          | 9.1                                | Radiation Damage                 |  |  |  |  |  |  |  |

|          | 9.2                                | Diode Radiation Hardness         |  |  |  |  |  |  |  |

|          | 9.3                                | Matrix Radiation Hardness        |  |  |  |  |  |  |  |

|          | 9.4                                | Conclusions                      |  |  |  |  |  |  |  |

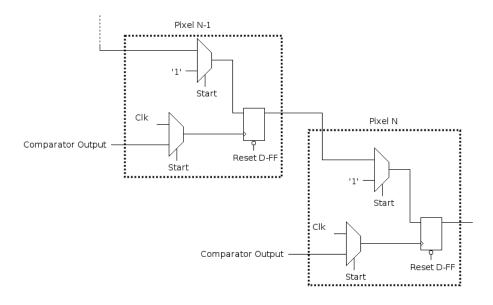

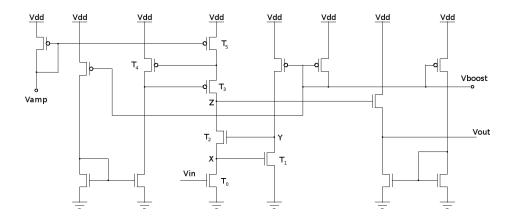

| 10 Binary Front-end Matrix1                                                                                      | .71 |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------|-----|--|--|--|--|--|--|--|

| 10.1 Binary Front-end                                                                                            | 171 |  |  |  |  |  |  |  |

| 10.2 Front-end Amplifier $\ldots \ldots 1$ | 174 |  |  |  |  |  |  |  |

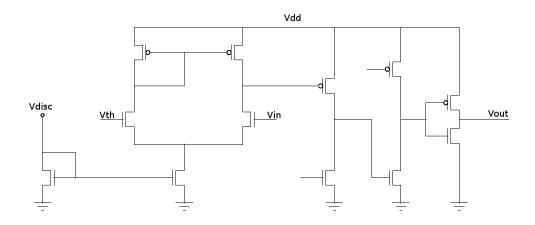

| 10.3 Discriminator $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $1$                            | 177 |  |  |  |  |  |  |  |

| 11 Digital Matrix Characterization 1                                                                             |     |  |  |  |  |  |  |  |

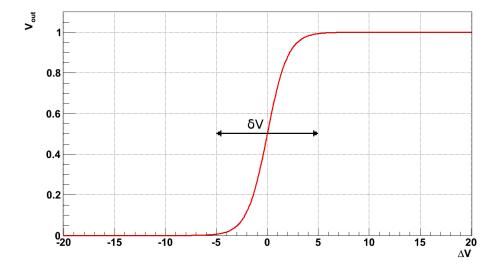

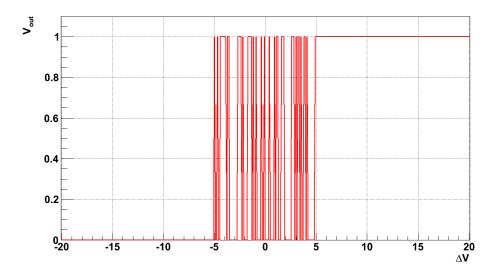

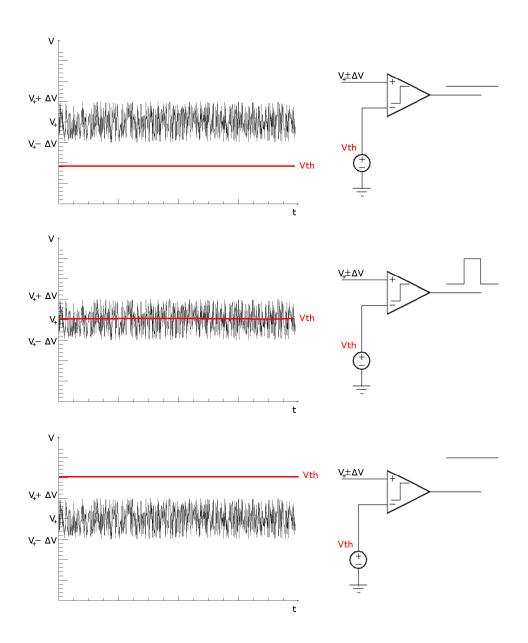

| 11.1 Discriminator                                                                                               |     |  |  |  |  |  |  |  |

| Characterization                                                                                                 | 180 |  |  |  |  |  |  |  |

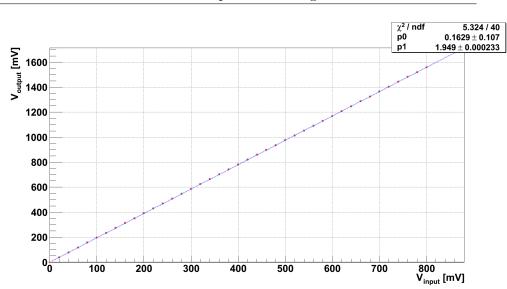

| 11.2 Pre-Amplifier                                                                                               |     |  |  |  |  |  |  |  |

| Gain                                                                                                             | 186 |  |  |  |  |  |  |  |

| 11.3 Laser Test                                                                                                  | 191 |  |  |  |  |  |  |  |

| 11.4 X-Ray Source                                                                                                | 192 |  |  |  |  |  |  |  |

| 11.5 Conclusions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ 1                                | 195 |  |  |  |  |  |  |  |

| Bibliography 1                                                                                                   | .99 |  |  |  |  |  |  |  |

# Introduction

High energy particle physics experiments investigate the elementary constituents of the matter and how they interact with each other. In particular, they are interested in strong interactions (range  $\approx 10^{-18} m$ ). The energy required to probe that range is in the TeV range, which is the energy scale typically used in hadrons collider experiments. In these experiments, massive particles are accelerated to reach a speed close to the light speed and they collide with themselves creating quark-antiquark pairs which recombine forming new hadrons. Most hadrons decay in new particles which can be stable or unstable. The latter will decay until a stable configuration is reached. By measuring the characteristics (momentum and energy) of the particles produced after collisions, it is possible to obtain informations about the particles created immediatly after the collisions. To do that, detector systems are built. The first layers of a detector system have several constraints in terms of space resolution, time resolution and granularity to have the possibility to detect and distinguish as many tracks as possible in the rate imposed by the machine. Moreover, a low mass, low power and low noise system is usually required in the inner layers of a detector system. Nowadays, the hybrid pixel sensors are the best solution for inner tracking systems that have to operate with very high particle fluxes. They consist of a detector and a readout chip assembled by bump bonding. The detector is based on a semiconductor p-n junction fully depleted while the read-out chip is based on a electronics system made in a planar CMOS technology. Both the sensor and the electronics are a well-known and mature technology to be used in the main detectors to detect high energy particles. They have excellent performance in terms of space resolution (a few  $\mu m$ ), time resolution (a feew tens of ns), power consumption (typycally 50  $\mu W$  per channel) and radiation hardness (about  $10^{15} n(1MeV)/cm^2$  in terms of non-ionizing radiation and about 10 *Mrad* in terms of ionizing radiation). The main drawback of the hybrid pixel sensors approach is represented by the high mass production costs due to the bump bonding process.

In the last twenty years, an intense R&D effort has been invested in monolithic detectors. Monolithic devices integrate on the same substrate the sensor and the front-end electronics: in a p-type substrate a n-well, containing the front-end electronics, is used as collection electrode. The integration between the sensor and its front-end electronics is automatically realised at the factory, avoiding expensive interconnection technologies such as the fine pitch bump bonding required by high resolution hybrid pixel detectors. The devices can be thinned down to 50  $\mu m$  or less, making the contribution of the sensor to the overall material budget very small. Last, but not least, one can take profit of the scale economy offered by state of the art CMOS technologies, which allow to pattern 8 or 12 inch wafers with costs of a few thousand dollars per sample. The main drawbacks of the monolithic approach are represented by the charge collection mechanism and the limited possible options in terms of read-out electronics. Since no-external electric field is applied, the main collection mechanism is based on charge diffusion, which usually means a few hundreds of ns in terms of collection time. Moreover, the limited options in terms of front-end electronics usable in the collection electrodes force the read-out time to be several tens of microseconds. The charge collection time and the read-out time are not suitable for fast applications, where a time resolution in the order of tens of nanoseconds or less is demanded. Furthermore, the charge collection occuring mainly by diffusion weaks the sensors resistance against bulk damage induced by non-ionizing radiation. It is clear that a sensor produced in a standard CMOS technology collecting the charge by drift represents an interesting perspective in terms of time resolution and radiation hardness. These were the main motivations driving the development of the LePix sensors. This thesis work is organized as follows:

• Chapter 1 shows a brief introduction on High Energy Particle Experiments and discusses the Hybrid Pixel Sensors approach;

• Chapter 2 describes the monolithic sensor approach describing the state of art of the *R*&*D* activity, focusing on the performance of some prototypes produced;

- Chapter 3 shows the LePix approach, focusing on the technology choice, the sensor principle, the device design and the pratical device implementation;

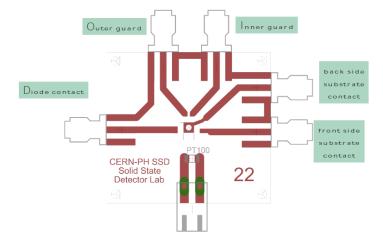

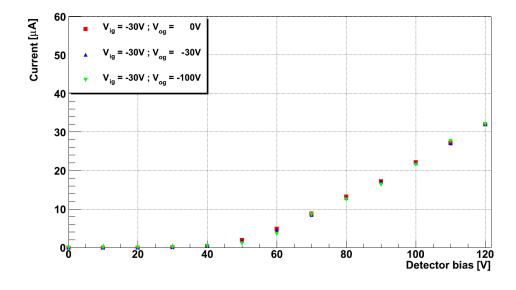

- Chapter 4 describes the diode-prototype produced to evaluate the performance of the CMOS technology chosen in the LePix project whit a back-bias applied;

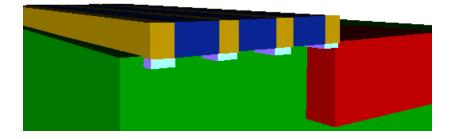

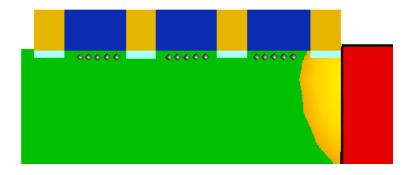

- Chapter 5 describes the breakdown-prototype produced to deeply evaluate the geometry on which the LePix detector is based on;

- Chapter 6 shows the matrix-prototype used to detect particles, containing both the electrodes and the front-end electronics ;

- Chapter 7 describes the performance of the matrix-prototype in terms of collection capacitance, leakage current and noise;

- Chapter 8 shows the performance of the matrix-prototype in terms of charge collection efficiency;

- Chapter 9 shows the diode-prototype and the matrix-prototype performance in terms of radiation hardness;

- Chapter 10 describes an alternative read-out approach based on a binary output for the matrix-prototype;

- Chapter 11 shows the performance of the matrix-prototype with the read-out electronics based on a binary output.

## Chapter 1

# Hybrid Pixel Sensors

In this chapter, a description of hybrid pixel sensors will be given. The chapter starts with a brief introduction on High Energy Particle (HEP) experiments (that is not the main subject of this thesis) focused on the constrains for the inner tracker silicon detector. Then the hybrid pixels approach will be discussed. In particular, the sensor characteristics, taking into account the main parameters to optimize in the device, and a classical approach for the front-end electronics will be reviewed. The aim of this chapter is to introduce some concepts that will be continuously used in the thesis.

### **1.1 HEP Experiments**

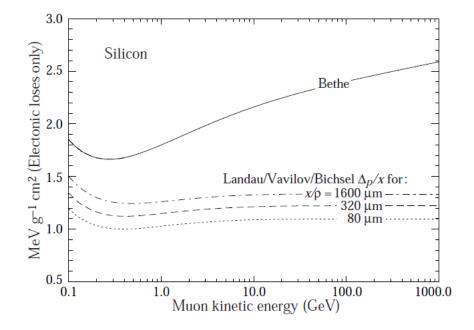

The goal of high energy particle physics experiments is to investigate the elementary constituents of matter and how they interact with each other. To do so, high energy particle accelerators have been built. High energy is necessary both to have a wavelength as short as possible and to produce massive particles. These particles interact by electroweak and strong interactions. High energy particle physics experiments are mainly interested in strong interactions (range  $\approx 10^{-18} m$ ). By following the *de Broglie* law, the energy necessary to probe particles in that range is given by:

$$E = \frac{hc}{\lambda} \approx 1.2 \ TeV \tag{1.1}$$

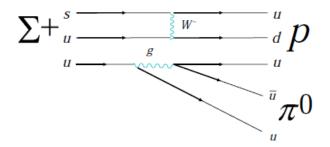

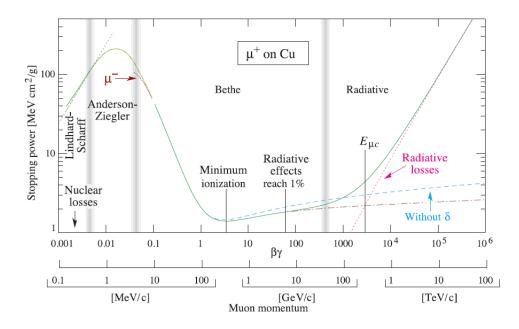

The TeV is the typical energy scale used in high energy hadrons collider experiment (LHC, TEVATRON). In these experiments, massive particles are accelerated to reach a speed close to the light speed. After their collision, quark-antiquark pairs are produced, which recombine forming new hadrons, in a few fermi range from the interaction point. In same cases, they can also recombine forming a spray of hadrons, called jets. Most hadrons decay a few hundred of micrometers far from their production point (called primary vertex). By measuring the characteristics (momentum and energy) of the particles produced at that distance (called secondary vertex), it is possible to obtain information about the primary vertex and, consequently, about the quarks' parameter. The goal of a detector system is to detect and track the particles produced after the collisions. For example, the sigma barion  $\Sigma^+$  lifetime is  $\tau = (8.018 \pm 0.025) \cdot 10^{-11} s$ : the distance covered by this barion is  $d \approx 24 \text{ mm}$ . It decays (see Fig. 1.1) in a proton (stable) and a pion  $(\pi^0)$ . The pion decays immediately in two photons. The first layer of detector, usually placed a few centimeters far from the interaction point, will detect only the protons: only by offline analysis it will be possible to go back to the primary vertex. The accuracy commonly required to the first layers is  $\approx 10\% c\tau$ : it means less than 30  $\mu m$  for a particle having a lifetime in the order of a picosecond. In addition, many other particles could pass close to the decay point. To distinguish multiple tracks, not only high space and time resolution are required, but also a high granularity, that means an appropriate number of independent sensing elements. In

Figure 1.1: The  $\Sigma^+$  barion decay process.

fact, the first layers of a detector system have to deal with a huge number of primary and secondary vertexes. An interesting example is given by the LHC ([1]) working in an ideal regime. In this machine, two proton beams are accelerated (one rotating clockwise, the other one counterclockwise) at ticles rate:

7 GeV; each beam contains many bunches of  $10^{11}$  particles. They cross each other every 25 ns but only a few particles per crossing collide (about 20). For a detector layer placed 5 cm far from the collision point, it means a rate of  $\approx 50 \frac{MHz}{cm^2}$ . Of course, not all the hits represent an interesting event and multistep selection criteria will reduce considerably the amount of data but the sensors and their electronics front-end have to deal with that order of magnitude in rate. Finally, the detector has to be robust enough to tolerate the high irradiation flux coming from the impinging particles: the detector performance tends to decrease because of the radiation damage. In short, the main characteristics of an inner detector system are:

• high time and space resolution, to be able to deal with the high par-

- high accuracy, to be able to distinguish close tracks;

- high radiation hardness, to be able to have good performance in a high flux of particles environment.

Furthermore, the detectors must have low mass (to reduce the multiscattering effect) and, together with their electronics, low noise and low power consumption. Obviously, it is not possible to satisfy all these requirements simultaneously. For example a thin semiconductor detector offers excellent performance in terms of radiation tolerance and multiple scattering, but only yields a relatively small signal, making the design of the front-end circuit more challenging and typically requiring more power consumption and, consequently, more mass in cabling to cool down the system. Even if it is not possible to optimize all the requirements at the same time, it is possible to obtain interesting performance through reasonable compromises. Nowadays, the hybrid pixel sensors are the best solution for inner tracking systems that have to operate with very high particle fluxes. In the following sections, both the detector and the frontend electronics will be described.

### **1.2** Hybrid Pixel Detectors

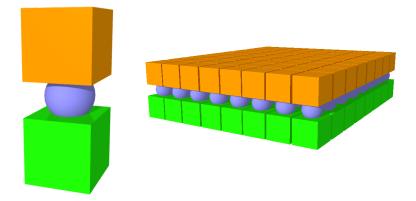

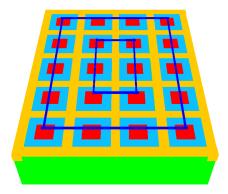

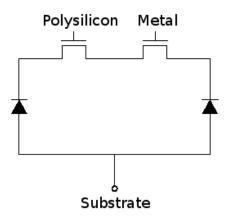

Hybrid pixel detectors consist of a detector and a readout chip assembled by bump bonding (see Fig. 1.2). They can cover several square cm in one unit. The front-end chip is made in a planar CMOS technology. Both the sensor and the electronics are a well-known and mature technology to be used in the main detectors to detect high energy particles.

Figure 1.2: Schematic view of a hybrid pixel (left) with the sensor in the bottom part (green) and the front-end electronics connected through a bump bonding and a matrix of sensors (right).

#### 1.2.1 Sensor

The sensor is a two dimensional matrix of *pin* diodes. The detection principle of a semiconductor is the same of a gas ionization chamber: the energy released by an impinging particle produces electron-hole pairs and, by applying an electric field, it is possible to collect the charges produced and measure the energy lost by the impinging particle. However, in the diode case, a semiconductor junction is used to separate electrons and holes for charge collection. The main advantage compared to the gas chamber is the energy resolution given by:

$$N = \frac{E}{E_i}$$

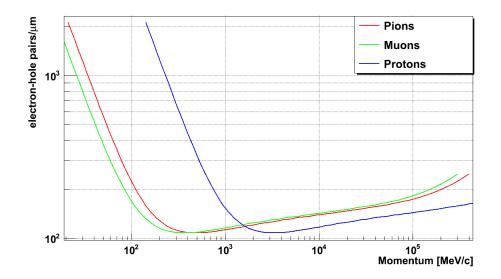

where N is the number of charged pairs due to the energy lost by the particles and  $E_i$  is the energy required to have an electron-hole pair (a few eVfor a semiconductor, 20 eV for a gas chamber). The p-n junction is the basic building block of silicon sensor. In fact, only one doped semiconductor is not sufficient to detect particles: the energy lost by a minimum ionizing particle (MIP) in silicon generates about 80 electron-hole pairs per micrometer. Assuming a detector with the typical size of a pixel detector (thickness  $d \approx 300 \ \mu m$  and area  $A = 10^4 \ \mu m^2$ ), the number of electron-hole pairs is given by:

$$N_{e-h} = 80 \cdot 300 = 2.4 \cdot 10^4$$

The number of electron-hole pairs excited by thermal effect at  $T = 300 \ K$  for an intrinsic semiconductor having the same volume is given by:

$$N_{e-h} = n_i \cdot d \cdot A \approx 4.4 \cdot 10^4$$

with  $n_i$  intrinsic charge carrier density at  $T = 300 \ K \ (n_i = 1.45 \cdot 10^{10} \ cm^{-3})$ . The number of thermal created electron-hole pairs has the same order of magnitude of the pairs due to a MIP. In a p-n junction, the space charge region (that is the depleted region) is almost completely depleted of mobile charge carriers and consequently the number of electron-hole pairs generated via thermal effect is negligible compared to the number due to a MIP. The main parameters to be study in a semiconductor sensor are the depletion region, the charge collection time and the leakage current.

#### 1.2.1.1 Depletion region

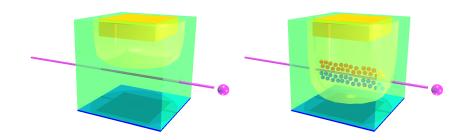

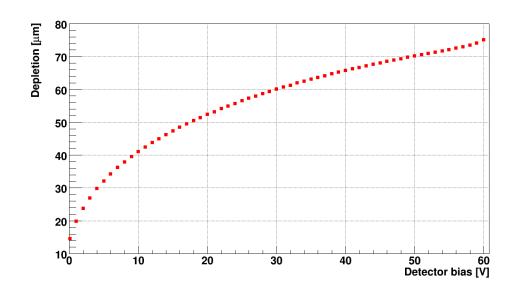

Most modern p-n junctions are fabricated using a planar technology: in a low doped substrate bulk, a high doped well having the opposite doping is introduced. Usually the thickness of the bulk is a few hundred of micrometers. By applying a reverse bias to the junction, it is possible to increase the depletion region depth up to the thickness of the detector. Having a fully depleted sensor is important both to maximize the efficiency of the detector, which is useful to detect particles penetrating the device with a shallow angle (Fig. 1.3), and to maximize the output signal due to the impinging particle. In fact, if the detector is fully depleted, all the electron-hole pairs created by the impinging particle will be collected (provided there are not trapping effects present). The depletion region width for a planar and abrupt junction is given by:

$$d = \sqrt{\frac{2 \cdot \epsilon}{q \cdot N_{eff}} \cdot (V_{appl} + V_{bi})}$$

(1.2)

with  $\epsilon$  silicon permittivity, q electron charge,  $N_{eff}$  effective doping level (also accounting for radiation damage effects, if present),  $V_{appl}$  potential applied at the junction and  $V_{bi}$  built-in potential. Full depletion voltage can be

Figure 1.3: Efficiency of the pn junction not depleted (left) and depleted (right): maximizing the depletion region allows to collect charge over the full volume of the detector.

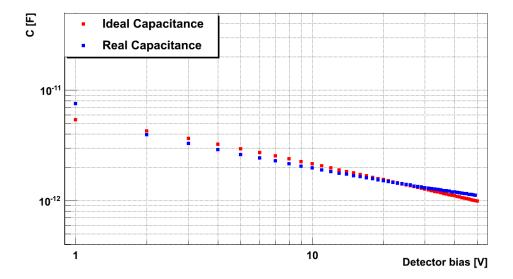

determined by capacitance measurements. A reversed biased detector acts as a capacitor having the value:

$$C = \epsilon \cdot \frac{A}{d} \tag{1.3}$$

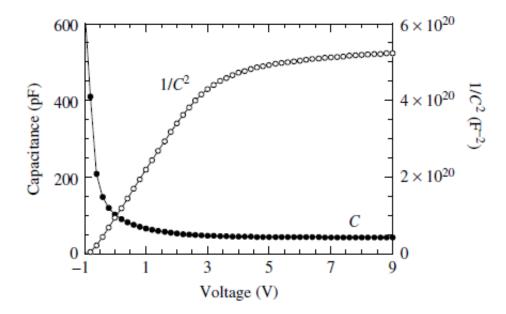

where A is the detector area and d is the depletion region depth. As soon as the detector is fully depleted, the capacitance reaches its minimum constant value (Fig. 1.4). However, the capacitance to the back-plane is only one

Figure 1.4: C - V curve and  $1/C^2 - V$  curve of a Si  $n^+p$  diode ([7]).

of the capacitive contributions at the input of the front-end electronics; in fact, the other contributions are due to:

- the sum of the capacitances to the neighboring pixels;

- the front-end electronics input capacitance;

- the capacitance due to the bump and parasitic capacitance of the bump bonding pad.

The largest contribution to the total capacitance in hybrid pixel sensors is normally given by the interpixel capacitance which is due to the parasitic capacitances between one pixel and its neighboring pixels. This interpixel capacitance is proportional to the perimeter of the pixel and to the gap size between the pixel implants. For pixels typically used in high energy particle experiments, the contribute due to the interpixel capacitance is a few tens of fF; in particular, it has been estimated to be about 60 fF for a  $125 \times 125 \ \mu m^2$  pixel having a 20  $\mu m$  gap (close to the choice of the CMS) experiment) and, for a pixel having sizes of  $50 \times 400 \ \mu m^2$  (choice of ATLAS experiment), between 30 and 100 fF ([8]). The main effect of the interpixel capacitance is the parasitic signals induced by a charge deposited on a single pixel on the neighboring pixels: this effect is usually called *cross-talk* and can be minimized by a correct electronics front-end design. A realistic value of the total capacitance of a detector is a few hundreds of fF. A MIP in a 300  $\mu m$  thickness fully depleted device generates 24000 electronhole pairs (80 pairs/ $\mu m$ ), that is a charge  $Q = 3.84 \ fC$ . By considering a typical capacitance value seen at the input of the front-end electronics of 200 fF, it is possible to estimate the signal at the output of the sensor:  $V_{sign} = \frac{3.84}{200} \frac{fC}{fF} = 19 \ mV$  that is the order of magnitude of the signal that has to be processed by the front-end chip.

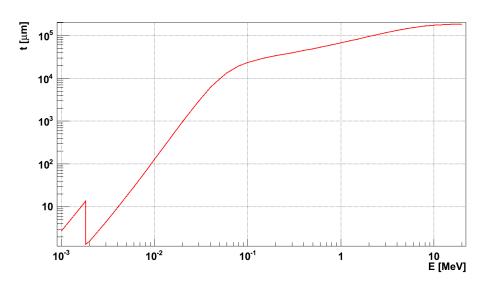

#### 1.2.1.2 Charge Collection Time

The charge generated in a semiconductor detector does not appear at the input of the amplifier instantaneously after the impact of an ionizing particle: it takes some time for the generated charge to reach the collection electrode. There are two possible charge collection mechanisms in the p-n junction: diffusion and drift. The former happens when no external voltage bias is applied to the junction and, consequently, there is not an electric field moving the charges generated outside the depleted region but their movement is due to a carrier concentration gradient; the latter is dominant when an external bias is applied in the same direction as the built-in voltage (there is also a diffusion component but it is negligible compared to the drift component). The charge movement is due to the electric field applied at the junction. The time spent by the device to collect a charge generated in the substrate depends on the  $\Delta V$  applied to the p-n junction. In fact, the speed of a charge in a semiconductor is given by:

$$v = \mu E$$

where  $\mu$  is the mobility of the charge in the medium and E is the electric field applied. If we suppose to apply a reverse bias  $\Delta V = 100 V$  to have a fully depleted 300  $\mu m$  junction, we can estimate the charge collection time. In fact, for a device collecting electrons, this is given by:

$$t = \frac{d}{v} = \frac{d}{\mu \cdot \frac{dV}{dx}} = \frac{300 \ \mu m}{0.14 \ \frac{m^2}{V \cdot s} \cdot \frac{100 \ V}{300 \ \mu m}} \approx 6 \ ns$$

The formula to calculate the collection time assumes a constant field across the detector. Even if this is an approximation which is only true in case the detector has significant over depletion voltage, it is useful to have an idea about the order of magnitude of the collection time. For a device collecting holes, the mobility is lower and, consequently, the collection time is approximately three times higher.

#### 1.2.1.3 Leakage Current

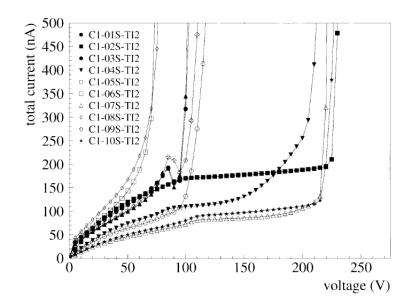

The leakage current (or dark current) is the current flowing in the sensor in absence of external effects like particles or light if a reverse bias is applied ([8]). It can be due to free carriers which diffuse from the undepleted volume into the space charge region or, more important, charges generated by thermal excitation in the depletion region. A typical current to voltage curve for a reversed biased sensor is shown in Fig. 1.5 ([8]). For voltages lower than the full depletion voltage, the current is proportional to the square root of voltage; when the full depletion is reached, it remains constant up to the electrical breakdown. In first approximation, its behavior can be obtained

Figure 1.5: I-V curves for different pixel sensors of about 8.8  $cm^2$ .

from the following equation:

$$J_{vol} \approx -e \cdot \frac{n_i}{\tau_g} \cdot d \tag{1.4}$$

where  $J_{vol}$  is the current density,  $\tau_g$  is the carrier generation lifetime, d is the depletion region depth and  $n_i$  is the intrinsic carrier concentration. The current depends on the temperature and this dependency is hidden in the term  $n_i$ ; the dependency can be obtained from the following equation:

$$J_{vol} \propto T^2 e^{-\frac{E_g(T)}{2kT}}$$

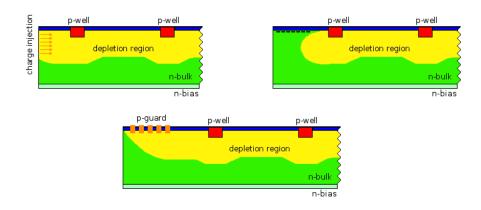

Usually a rough estimation is to assume that the current doubles every 8K. One of the most crucial regions for the sensor stability in terms of leakage current and breakdown voltage is represented by the edge termination. The sensor behavior at the edge is determinated by the potential surface in that region. An a priori prediction of the surface voltage in the edge region is complex due to the several parameters influencing it (local variations of surface conductivity, surface humidity, dust contamination and so on). The two worst-case scenarios for the edge are represented in the top part of Fig. 1.6. In the first case, the depletion region reaches the sensor edge which is full of generation-recombination centers because of its imperfect lattice

structure due to the mechanical damage caused by the dicing procedure: the free charges are driven by the electric field causing an unwanted current flowing in the device. Usually this is avoided by design allowing enough space for the extension of the depletion layer.

In the second extreme case the surface potential drop to the bulk voltage through the device scribe-line causing an electrons accumulation layer. Due to the conductive nature of the electrons layer, the potential in that region will be close to the back-bias voltage, causing a local breakdown due to the high voltage drop in a small region. Floating rings are typically used to increase the breakdown voltage of the detector since they allow to drop the voltage over several junctions.

Figure 1.6: Worst scenario in terms of edge leakage current (top-left), breakdown voltage (top-right) and solution used to have a smooth voltage drop towards the cutting edge (bottom).

#### 1.2.2 Front-end Electronics

The front-end electronics has to convert an analog signal coming from the output of the sensor into a signal manageable by the digital interface: usually, the raw detector signal has to be processed to perform amplitude or time measurements. Several constraints are imposed to the front-end electronics chips; for example, the size of the chip is limited by the size of the pixel matrix, the power consumption has to be limited to avoid a too aggressive cooling system, the circuit noise has to be as small as possible to have a high detection efficiency, the circuit has to work at a sufficient speed to deal with

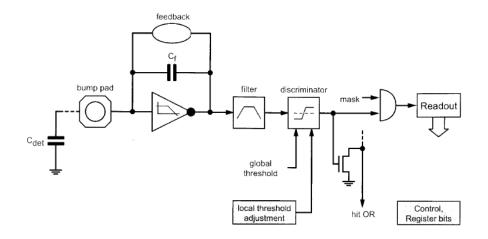

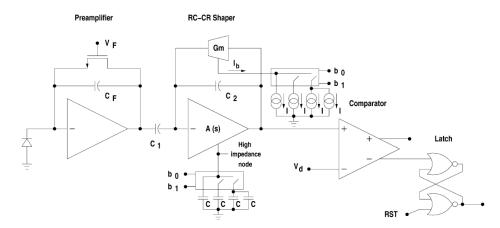

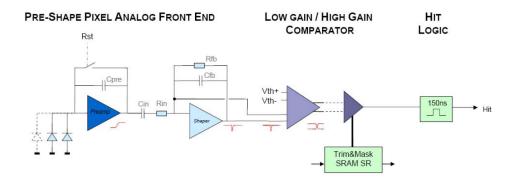

all signals coming from the detector avoiding to overlap them and avoiding to miss some signals, a high radiation-hardness has to be guaranteed. Nowadays, these features can be satisfied using modern CMOS technology which allows to design fully custom made Integrated Circuit (IC): their complexity depends on the measure they have to perform. Even if a huge number of different ICs having different purposes have been designed and produced, it is possible to spot several common building blocks. In particular, the chips can be divided in an active area and a periphery. The active area is made of a repetitive Pixel Unit Cell (PUC) having approximately the same area of the corresponding pixel; in the PUC, the signal coming from the sensor is amplified and a noise filtering is usually done. A typical scheme employs a Charge Sensitive Amplifier (CSA) and a shaper filter (see Fig. 1.7). The

Figure 1.7: Schematic view of a possible readout for pixel particle detectors.

CSA, which amplifies the signal, is one of the most crucial stages of the front-end electronics. In fact, it has to be designed having a high gain with a sufficient bandwidth, with a low power consumption (typically 50  $\mu W$  in high energy physics) and low noise, with a good immunity to the fluctuation in the supply voltage and a good uniformity between different channels. The shaper filter is also an important stage because it allows to fix the desired rise and decay times, through RC high-pass and low-pass filters, and, more importantly, it allows to improve the signal to noise ratio. If an information about the energy of the impinging particle is required, the signal at the output is usually digitalized by an ADC which converts the signal in discrete

steps corresponding to the digital bits. Since the power consumption of an ADC is usually high, it is placed in the periphery of the chip and it does not process all signals but it works only when it is activated by a trigger system. When no information about the energy lost by the particles is required, the stage at the output of the shaper is made by a discriminator which compares the input signal to a threshold value, usually set as low as possible to maximize the detection efficiency without suffering from noise: the logic output value is then sent to the chip periphery. The resolution of a segmented detector is strongly dependent on the readout. In fact, for a binary readout, the maximum reachable spatial resolution is  $p/\sqrt{12}$ , where p is the pixel pitch. It means a spatial resolution of a few ten microns for a pixel pitch  $p \approx 100 \ \mu m$ . With an analog readout, a higher resolution (up to a few microns) is possible by using a *charge center of gravity* reconstruction based on the amplitude of the signal coming from a group of pixels.

#### 1.2.3 Noise Analysis

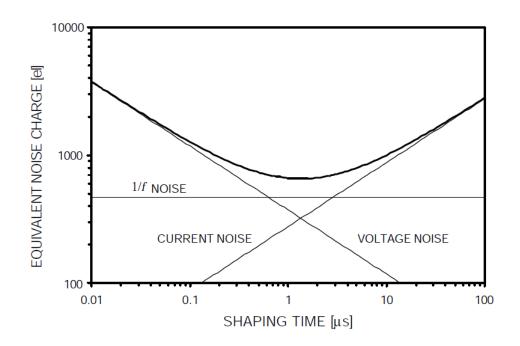

The noise optimization represents a crucial point in the IC design. In fact, the detector charge collection efficiency is tightly correlated to the noise level: the magnitude of the noise must be sufficiently low that, at the minimum signal level, it is still possible to have the required efficiency. Since the first amplifying stage gives the dominant contribution to the noise figure, it is possible to optimize the noise performance by minimizing the noise of the input stage. In fact, the noise in terms of equivalent noise charge can be written as follows ([9]):

$$Q_n^2 = i_n^2 F_i T_s + e_n^2 F_\nu \frac{C^2}{T_s} + F_{\nu f} A_f C^2$$

(1.5)

where  $i_n$  is the input noise current spectral density,  $e_n$  is the input noise voltage spectral density, C is the sum of all capacitances shunting the input,  $A_f$  is the 1/f noise coefficient,  $T_s$  is the shaping time and  $F_i$ ,  $F_{\nu}$  and  $F_{\nu f}$  are shape factors. Fig. 1.8 illustrates that voltage noise becomes dominant for smaller shaping times and current noise for larger shaping times; moreover it can be demonstrated that the minimum noise can be obtained with a

Figure 1.8: Equivalent noise charge versus shaping time ([9]).

shaping time of:

$$T_s = \frac{e_n}{i_n} C \sqrt{\frac{F_\nu}{F_i}}$$

The influence of the input capacitances and of the input transistor can be better understood by studying the signal to noise ratio at the input node:

$$\left(\frac{S}{N}\right)^2 = \frac{\left(\frac{Q}{C}\right)^2}{e_n^2} = \frac{Q^2}{(C_d + C_{in})^2} \cdot \frac{g_m}{4\gamma kT}$$

where  $C_d$  is the capacitance due to the detector (pixel capacitance and interpixel capacitances),  $C_{in}$  is the MOS input capacitance,  $g_m$  is the transconductance and  $\gamma$  is a constant factor. In this case, both the current noise of the transistor and the detector noise are considered to be negligible. It is possible to maximize the signal to noise ratio by optimizing the device geometry. In fact, for  $C_d \gg C_{in}$ , the signal to noise ratio can be written as:

$$\left(\frac{S}{N}\right) \propto \frac{\sqrt{g_m}}{C_d}$$

For a transistor working in strong inversion, the transconductance increases as the device width is increased and, consequently, also the signal to noise ratio increases; however, the increase will stop as soon as the transistor capacitance will be the dominant contribution. For  $C_d \ll C_{in}$  the signal to noise ratio can be written as:

$$\left(\frac{S}{N}\right) \propto \frac{\sqrt{g_m}}{C_{in}}$$

For a transistor working in strong inversion, both the transconductance and the input capacitance are directly proportional to the device width. Consequently, the signal to noise ratio is in inverse proportion to the square root of the transistor width:

$$\left(\frac{S}{N}\right) \propto \frac{1}{\sqrt{W}}$$

and it can be optimized by reducing the transistor width. As already mentioned, the voltage noise spectral density is given by:

$$e_n^2 = 4\gamma \frac{kT}{g_m}$$

It is strongly dependent on the working condition of the input transistor. For a transistor working in saturation, the transconductance is given by:

$$g_m = \sqrt{2I_d \mu \frac{\epsilon_{ox}}{d_{ox}} \frac{W}{L}}$$

In principle, by fixing the drain current and the MOS sizes, it is possible to see the intrinsic advantage of MOS scaling in terms of noise reduction  $(e_n^2 \propto \sqrt{d_{ox}})$ ; however, by scaling the technology maintaining the same biases and sizes, it may be possible that the input transistor changes from strong to weak inversion, in which case the transconductance is no more given by the previous relationship. For a MOS transistor working in weak inversion, the transconductance is given by:

$$g_m \propto I_d \frac{q}{kT}$$

Consequently the relations between the noise voltage spectral density for a transistor working in strong inversion

$$e_{ns}^2 \propto \frac{1}{\sqrt{I_d}}$$

and in weak inversion

$$e_{nw}^2 \propto \frac{1}{I_d}$$

show the input noise scaling with the inverse of the square root of the current in the former case and with the inverse of the current in the latter case. In Fig. 1.9 it is possible to compare the transconductance in both cases: weak inversion for small drain current (linear relationship) and strong inversion for high drain current (square root relationship). The strong inversion regime is

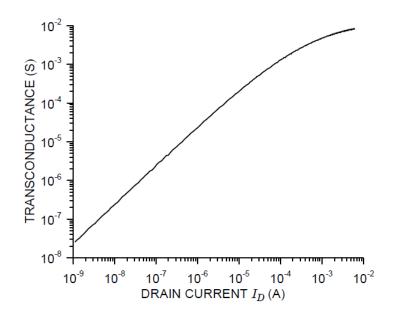

Figure 1.9: Transconductance vs Drain Current in a MOS transistor ([9])

commonly used when minimum noise is required because it allows to reach the highest transconductance value. Moreover, it allows to have the highest gain bandwidth product, given by:

$$f = \frac{g_m}{2\pi C_0}$$

However, using the transistor in strong inversion often yields prohibitive power consumption for low power applications like HEP, where usually weak inversion is preferred as it offers the maximum  $g_m/I$  ratio. Assuming the transistor to be in weak inversion, the square of the noise charge is proportional to the square of the input capacitance divided by the drain current:

$$Q_n^2 \propto \frac{C_{in}^2}{I_d}$$

For a constant noise charge  $Q_n$ , the power is therefore proportional to the current and, consequently, to the square of the input capacitance:

$$P \propto I_d \propto C_{in}^2$$

For hybrid pixel detectors the parasitic capacitance is often proportional to the perimeter and therefore segmenting further will be advantageous. In fact, supposing to be dominated by the perimeter parasitic capacitances, the input capacitance is proportional to the sensor perimeter:

$$C_{in} \propto 2l + 2p$$

where l is the cell length and p is the pitch. Consequently, the noise will be given by:

$$Q_n^2 \propto (2l+2p)^2$$

In the strip case, the perimeter is dominated by the length:

$$Q_{ns}^2 \propto 4l^2$$

In the pixel case, the area covered by n strips is covered by  $n \times n$  pixels having a pitch p and a length  $l^1 = l/n$ , where l is the length of the strips considered in the previous case. Consequently it is possible to write:

$$Q_{np}^2 \propto \left(2\frac{l}{n} + 2p\right)^2$$

In case of a square shaped pixel (p = l/n), the noise will be written as follow:

$$Q_{np}^2 \propto 16 \frac{l^2}{n^2}$$

It is possible to study the noise improvement given by the pixel shaped detector compared to the strip shaped detector:

$$Q_{np}^2 \propto \frac{16\frac{l^2}{n^2}}{4l^2} Q_{ns}^2 = \frac{4}{n^2} Q_{ns}^2$$

The power consumption for a strip will be given by:

$$P_s \propto 4l^2$$

and for a pixel having a length l/n it will be:

$$P_p \propto 16 \frac{l^2}{n^2}$$

By comparing the two power consumptions, it can be written:

$$P_p = \frac{4}{n^2} P_s$$

Since the power consumption for one pixel can be written as the power consumption of all pixels divided the number of pixels  $(P_p = P_{p-tot}/(n \times n))$  and also the power consumption of one strip can be written following the same idea  $(P_s = P_{s-tot}/n)$ , it can be written:

$$P_{p-tot} = \frac{4}{n} P_{s-tot}$$

The above illustrates the advantage of segmentation for analog power consumption. Of course beyond a certain segmentation, the reduction of the input capacitance will saturate and will no longer yield a further power reduction for the same noise level. Another important advantage of a pixel detector is its capability to deal with high trace density without generating ghost hits or ambiguity as in strip detectors for multiple hits. The main drawback of a hybrid pixel detector is its cost usually dominated by the bump bonding cost, which is normally larger than the cost for silicon sensors and the readout chips. For this reason only the central part of the detectors are typically implemented as hybrid pixel detectors, while the outer part are strip detectors to contain the cost. Hybrid pixel detectors now yield almost noise-free and unambiguous tracking information in the inner detectors of the LHC. Monolithic pixel detectors were not sufficiently mature at the time of the construction of the present LHC detectors, but they do not suffer from the same cost penalty and even offer the perspective of improved performance. They are the topic of the next chapter.

# Chapter 2

# **Monolithic Sensors**

In this chapter, monolithic sensors will be discussed with their benefits (low capacitance, low material budget, low power consumption, low noise, low cost) and drawbacks (in particular the radiation hardness). The main approaches for monolithic integration will be presented with their device and circuitry solutions and their performance.

## 2.1 Monolithic Active Pixel Sensors

Monolithic devices integrate on the same substrate the sensor and the frontend electronics. Several developments have yielded functional pixel detectors. One of the most used approach is based on the so called Monolithic Active Pixel Sensors (MAPS), which traditionally collect charge by diffusion and hence offer reduced radiation tolerance, and which often have readout of the rolling shutter type usually not compatible with HEP requirements. The very significant advantage of MAPS is their compatibility with standard CMOS processing which allows a low price production. Some other developments also yielded functional devices and radiation tolerance, but required exotic process steps like double sided processing not compatible with standard CMOS manufacturing. For example, in the early '90 a successful prototype of monolithic detector in a non-standard CMOS process on high resistivity and fully depleted p-bulk was produced ([14]). It was based on a monolithic pixel array of  $10 \times 30$  pixels measuring each  $125 \times 34 \ \mu m^2$ . A schematic view of the device is shown in Fig. 2.1. It is based on a p-n junction made by a n-diffusion and a low doped p-substrate. The pixel is made

Figure 2.1: Schematic view of one of the first monolithic detectors built.

of a n-well containing the PMOS circuitry and a highly doped p-diffusion used as collection electrode. Both the n-well and the p-diffusion are placed in the p-substrate. The different doping level between the p-substrate and the p-diffusion allows the electron-hole pairs due to the impinging particle to flow towards the p-diffusion; the signal is sent to the adjacent n-well containing a first circuitry stage which produces a signal which is sent to the periphery where both types of transistors are used in p-wells and n-wells for the read-out electronics. This detector reached an effective capacitance of  $\approx 25 \ fF$  and it was used in a muon beam test obtaining excellent results: a 100% efficiency, a spatial resolution of 2.2  $\mu m$  and a signal to noise ratio of 55; however no further development followed due to the complicated double side processes required for the backside diffusion.

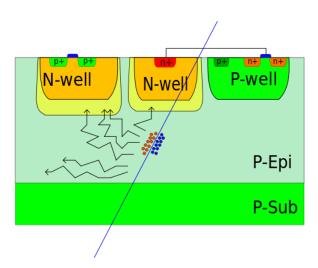

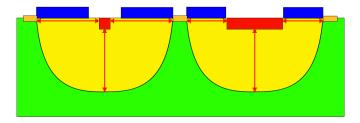

As already mentioned, MAPS offer the opportunity to integrate analog and digital electronics together with the sensor in the same substrate. A schematic view of the typical pixel cell of a MAPS made in a CMOS technology is shown in Fig. 2.2. Most commercial CMOS technologies use only low resistivity silicon which is not suited for charge collection. However, some of them offer the possibility to grow a lightly doped epitaxial layer, having a thickness from a few  $\mu m$  to 20  $\mu m$ , useful as active layer. In the epitaxial layer, a n-well used as collection electrode is built; another p-well highly doped is used to place the NMOS transistors used as amplifier. The signal at the output of the input NMOS transistor is usually sent to the periphery where double and triple well structures allow to use an appropriate readout electronics.

In MAPS there is usually no significant reverse substrate bias and therefore

Figure 2.2: Schematic view of a MAPS (the yellow region represents the depleted volume).

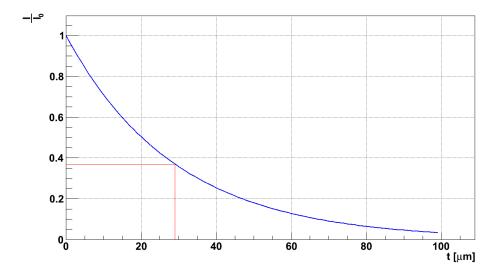

most of the epitaxial layer remains undepleted, yielding charge collection dominated by diffusion in the absence of a significant electric field. As a result, the generated charges tend to spread over several pixels (see Fig. 2.3). It is possible to estimate the width of the charge carrier distribution. In fact, it is defined as:

$$\sigma = \sqrt{2Dt}$$

where D is the diffusion coefficient defined as:

$$D = \frac{kT}{q} \cdot \mu$$

and t is the collection time. For electrons spending 100 ns to reach the electrode (which is the typical collection time in a MAPS) at T = 300 K, the width of the distribution is  $\approx 20 \ \mu m$ : the diffusing charge is generally shared between neighboring pixels. Even with a charge carrier distribution width much higher than hybrid pixels, several prototypes of MAPS detectors have been reached an excellent spatial resolution ( $\approx 1.5 \ \mu m$  for the so called MIMOSA detectors, as explained in [15]). For MAPS devices the substrate represents a material which does not yield useful signal and, for HEP, it is therefore desiderable to use wafer thinning techniques to reduce this excess material and minimize scattering of particles in the detector.

The low leakage current is surely a key point in monolithic devices as it

Figure 2.3: Schematic view of the widening effect due to diffusion: the charge cloud sizes increase with time ([8]).

contributes to the noise. Because in MAPS depletion is not complete, leakage current is typically collected only from a small fraction of the sensitive volume and, consequently, also the noise related to the leakage current is less than for fully depleted sensors.

A very important advantage of monolithic detectors is the possibility to reach a very low input capacitance, down to a few fF, because there is no need for bump bonding and the collection electrode is very small; moreover, since most of the capacitance is not to the neighboring pixel but to a fixed potential, the cross-talk between pixels is also reduced. This low capacitance value allows to reach very good signal to noise ratios for a low analog power consumption: even if the collected charge is less than for hybrid pixel detectors due to the smaller charge collection volume, the reduction in capacitance by a few orders of magnitude sometimes still yields better charge over input capacitance ratios and hence better signal to noise-power performance.

Another advantage of MAPS is the low cost compared with hybrid pixel detectors (potentially  $\approx 25 \in /cm^2$ ).

With their high granularity, high signal to noise ratio, low power consumption and low cost, MAPS seem to be an interesting alternative to hybrid pixel sensors in vertex detectors of high energy experiments but their low radiation hardness, in particular for non ionizing radiation, does not allow to use them in a harsh radiation environment. In fact, the duration of the collection process increases the trapping probability making them more sensitive to the bulk radiation damage. Furthermore, the charges trapped in the undepleted volume are not subjected to any electric field: once a charge is trapped there is not the possibility to move it away from the trap. Consequently, it is possible to have groups of trapped charges causing undesired electric fields in the undepleted region. The radiation damage caused by ionizing particles is much less influent than bulk damage. In fact, MAPS detectors take advantage of the intrinsic radiation hardness of sub-micron technology which is increasing with scaling. Nowadays, MAPS detectors can work in a reasonable performance regime up to a  $10^{13} n_{eq}/(cm^2 \cdot year)$  non ionizing fluence and a few Mrad ionizing dose: this represents the main restriction to their use in the innermost layer of a vertex tracker in a hadron machine, in which the non ionizing fluence can reach values higher than  $10^{14} n_{eq}/(cm^2 \cdot year)$ , while it is not an issue for lepton machines, in which the non ionizing fluence reach values around  $10^{12} n_{eq}/(cm^2 \cdot year)$  (Table 2.1).

| Machine     | Luminosity               | Non Ionizing Fluence                   | Ionizing Dose          |

|-------------|--------------------------|----------------------------------------|------------------------|

|             | $[cm^{-2} \cdot s^{-1}]$ | $[n_{eq} \cdot cm^{-2} \cdot yr^{-1}]$ | $[kRad \cdot yr^{-1}]$ |

| LHC         | $10^{34}$                | $1.4 \times 10^{14}$                   | 11300                  |

| Super LHC   | $10^{35}$                | $1.4 \times 10^{15}$                   | 71400                  |

| ILC         | $10^{34}$                | $1.0 \times 10^{11}$                   | 50                     |

| CLIC        | $10^{34} - 10^{35}$      | $1.0 \times 10^{11}$                   | 70                     |

| Super Belle | $10^{35}$                | $6.0 \times 10^{11}$                   | 500                    |

| RHIC        | $8 \times 10^{27}$       | $3.0 	imes 10^{12}$                    | 80                     |

A second limitation of traditional MAPS is the impossibility to use full

Table 2.1: Main accelerator machines built or to be built in the future with their nominal luminosity, non ionizing fluence and ionizing dose.

CMOS in the pixel: an additional N-well necessary for the PMOS transistors would compete with the N-well collection electrode to collect the signal charge, and can result in charge loss and even loss of detection efficiency (Fig. 2.4). This NMOS only limitation in the pixel is actually quite a significant constraint for the design of the readout circuitry. Finally, the CMOS technology is optimized for general purpose electronics and not for detector devices: consequently, there is a low flexibility in the processes. Despite the availability of specific CMOS imagers technologies, these are often oriented towards the detection of visible light only and hence do not generally offer very thick epitaxial layers which would yield a more advantageous signal for HEP.

Nevertheless, despite some of these drawbacks, very promising results have been obtained by the MIMOSA (Minimum Ionizing MOnolithic Active pixel Sensor) collaboration. The first prototype has been produced in the late '90 in a 0.6  $\mu m$  AMS CMOS technology ([16]). The chip has been divided in

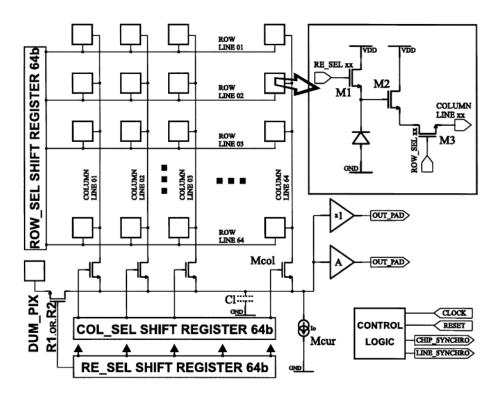

Figure 2.4: Schematic view of the competitive effect between the electrode and the N-well used for the circuitry.

four matrices having small design differences. Each matrix consists of  $64 \times 64$ pixels having a pitch of 20  $\mu m$ : each pixel is made of four diodes connected in parallel; in this way it is possible to reduce the charge dispersion and the collection time at the expense of a larger capacitance, hence a lower charge to voltage conversion gain and a higher noise. The signal at the output of the pixel is read by a three transistors structure (3T) implemented in the pixel itself. A schematic view of the readout system is shown in Fig. 2.5. The three transistors structure is based on a reset transistor, which resets the diode voltage, a source follower transistor and a row selector transistor, which allows to read the signal of the pixel: in this way the low power consumption is guaranteed by the activation of the pixel circuitry only during the read-out phase avoiding to have power dissipation due to digital clock signals driving large capacitances. Usually the sensor works in a so called rolling shutter mode: all pixels in one raw are read in parallel by using the row-selector transistor. During the test of the chip, the possibility to reach a capacitance in a few fF range and a charge collection time of  $\approx 150 \ ns$  were demonstrated. The measured noise was estimated to be a few  $e^- ENC$  and, after a beam test, the efficiency reached by the sensor was close to 100% with a spatial resolution of a few  $\mu m$ . The sensitivity to neutron irradiation has been investigated obtaining a charge-to-voltage conversion almost constant up to the highest fluence  $(10^{13} n/cm^2)$ . An increase of the leakage current

Figure 2.5: Schematic view of the readout chain of the MIMOSA 1 chip.

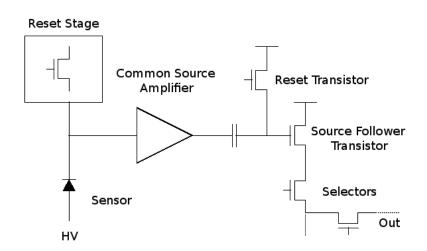

of an order of magnitude (from a few fA per diode to a few tens of fAper diode) has been observed without a significant noise penalty. However, charge losses have been observed for fluence exceeding  $\approx 10^{12} n/cm^2$  ([16]). Even more interesting is one of the last prototypes produced, MIMOSA -28, the second large scale sensor of the MIMOSA series ([18]). It has been produced in a 0.35  $\mu m$  AMS CMOS technology, with an epitaxial layer of 20  $\mu m$  and a pixel pitch of 20  $\mu m$ . A matrix of  $\approx 0.9$  million pixels divided in 960 columns of 928 pixels, for an active area of  $19.9 \times 19.2 \ mm^2$  has been designed. In each column, the pixels are read sequentially with a typical read-out time of  $\approx 200 \ ns$  by a rolling shutter based read-out; the columns are read in parallel. The readout circuit is based on a common source stage and a source follower stage (Fig. 2.6). The power consumption of the sensor has been measured to be  $\approx 150 \ mW/cm^2$ . The noise has been estimated to be  $\approx 15e^-$  ENC per pixel. After a beam test, the efficiency of the system has been calculated to be  $\approx 100\%$  with a resolution of  $\approx 3 \ \mu m$ . These same performance have been obtained also for irradiated sensors up to a 150 kRad

Figure 2.6: Schematic view of the readout chain of the MIMOSA-28 chip.

ionizing dose and a  $3\cdot 10^{12}~n/cm^2$  non ionizing fluence.

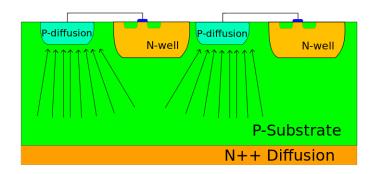

### 2.2 Deep N-well MAPS

Deep n-well (DNW) MAPS ([19]) devices represent an interesting evolution of classical MAPS in terms of read-out speed. They have the possibility to implement at pixel level the standard front-end electronics used for hybrid pixel sensors (see 1.2.2) by taking the advantage of modern submicron triple well CMOS commercial technology, where a n-well with a deep junction is available to have a better insulation of the NMOS transistors from the substrate and the neighboring digital devices. A schematic view of the sensor is shown in Fig. 2.7. The deep n-well is the collecting electrode; the triple well process allows to have a p-well placed in the n-well to have the possibility to use also NMOS transistors. A more complex circuitry than standard MAPS can be used to process the signal: a charge amplifier, a shaper and a discriminator. By using a charge preamplifier, the charge sensitivity is almost independent on the capacitance of the electrode allowing to have a large area sensor. There is also the possibility to have standard n-wells which contain PMOS devices for the analog and the digital part; their area has to be minimized to avoid to capture part of the signal from the deep n-well: the degradation of the charge collection efficiency depends on the ratio between

Figure 2.7: Schematic view of a DNW MAPS (the yellow region represents the depleted volume).

the deep n-well sensor and the n-well used to place the PMOS transistors. However, even by minimizing the area of the small n-wells, it is not possible to eliminate completely the charge loss.

By following the deep n-well approach, interesting results have been obtained with the APSEL prototypes series mostly produced in a 130 nm technology. In Fig. 2.8 it is possible to see a schematic view of the typical front-end of the APSEL series ([25]). The preamplifier is based on a cascode stage

Figure 2.8: Schematic view of the typical front-end electronics of the APSEL chip series.

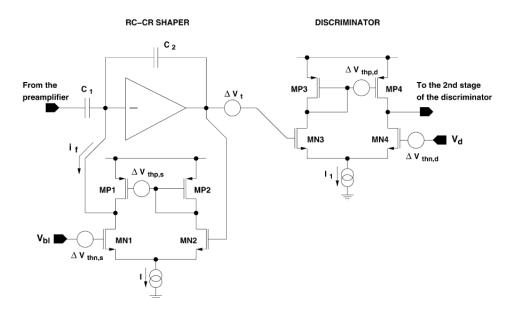

with a capacitive feedback: the capacitance of a few fF, implemented using a MOS capacitor, allows to achieve a large charge sensitivity. The charge sensitive amplifier is AC coupled with a RC-CR shaper; it is based on a high gain amplifier with a capacitive and transconductive feedback. The input capacitance, the feedback capacitance and the transconductive feedback allow to program the peaking time (see [25]) to deal with the charge collection time of the monolithic detector. The transconductive feedback (Fig. 2.9)

Figure 2.9: Schematic view of the RC-CR shaper and the discriminator of the APSEL chip series.

is based on a differential pair providing current at the input when a signal arrives at the input of the shaper amplifier. The signal at the shaper output is compared to an external voltage by a comparator and the binary information is then stored in a NOR latch.

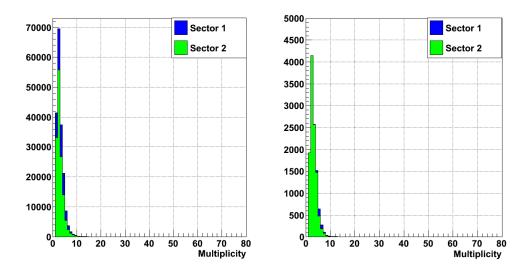

A chip of that series obtaining interesting results is the APSEL4D chip. It is based on a 4096 pixels matrix, 32 rows by 128 columns, with a pitch of 50  $\mu m$ for an estimated capacitance of 300 fF, an average gain of 890 mV/fC, a power consumption of  $\approx 35 \ \mu W$  per pixel and a noise of  $\approx 75e^-$ ; the efficiency has been measured to be higher than 90% and the resolution slightly lower than 15  $\mu m$ .

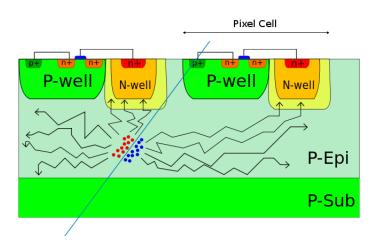

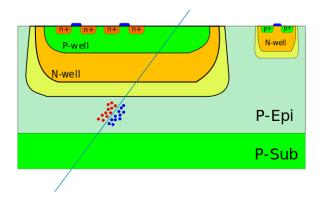

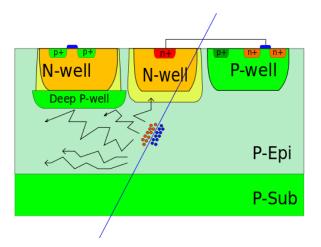

### 2.3 INMAPS

Another interesting solution to the competitive effect between n-wells is represented by the INMAPS devices ([26]); their approach allows to use both type of transistors in a monolithic device by using a p-implant forming a deep p-well which screens the n-well used to place the PMOS transistors (Fig. 2.10): the deep p-well prevents the charge collection of the N-well containing the PMOS transistors and the associated signal loss. It therefore allows the use of full CMOS circuitry in the pixel without penalty. By

Figure 2.10: Schematic view of a INMAPS (the yellow region represents the depleted volume).

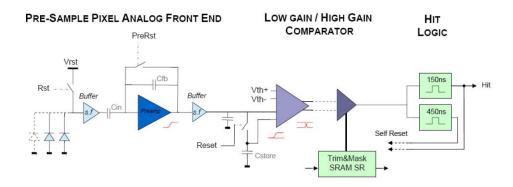

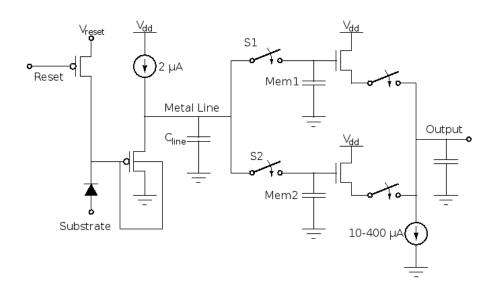

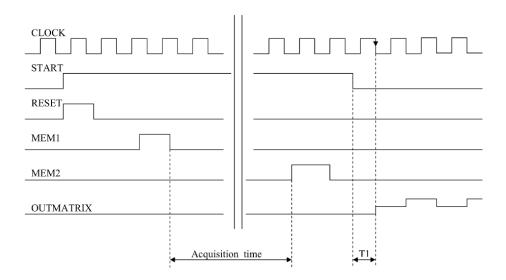

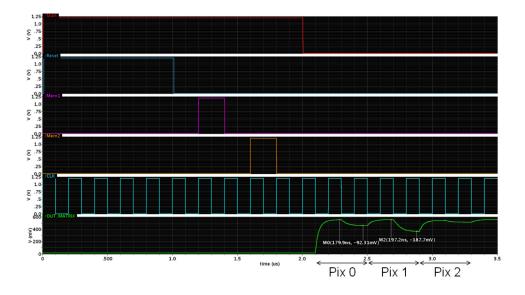

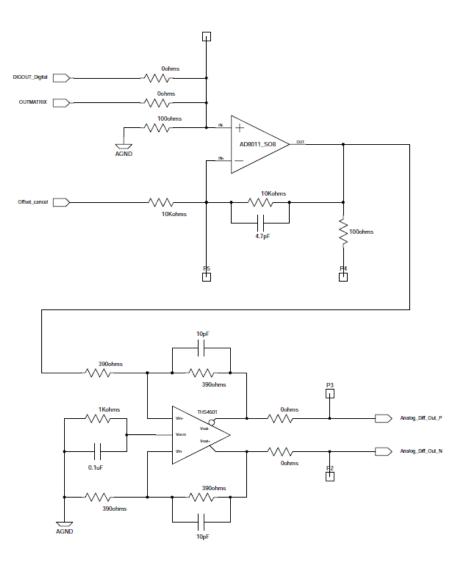

using both type of transistors, it is possible to develop a more complex read-out electronics, compared to standard MAPS read-out electronics. In Fig. 2.11 and Fig. 2.12, two possible read-out electronics used in [26] are shown. In the former, a double sampling approach, similar to a conventional MAPS device, is used: a so called *pre-sample stage* buffers the voltage drop on the diode node and a charge amplifier is used to generate a voltage step proportional to the input. A reference signal previously stored in a sampling capacitor is used to obtain a pseudo-differential signal which is then sent to the remaining part of the read-out electronics. In the second circuit, a preamplifier is used to amplify the collected charge. Moreover, a CR-RC shaper is used to generate a signal with peak and decay time proportional to the input. The input of the shaper stage is also used as reference to obtain a pseudo-differential signal.

Figure 2.11: INMAPS read-out electronics based on a pre-sample pixel analog front-end.

Figure 2.12: INMAPS read-out electronics based on a pre-shape pixel analog front-end.

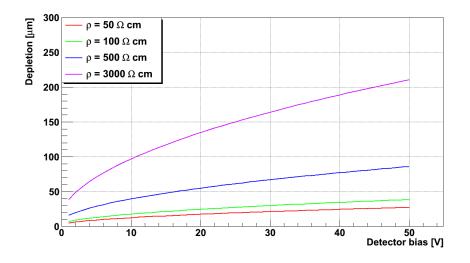

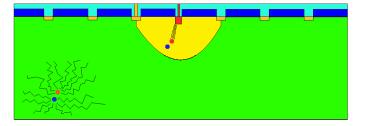

#### 2.4 High Voltage MAPS

An innovative approach to monolithic detectors is represented by the so called High-Voltage (HV) MAPS: they take the advantage of high voltage CMOS technology to develop a detector. In this context, the term *high voltage* means a voltage significantly higher than the standard low voltage applied to CMOS devices. By using this technology it is possible to apply a voltage bias to the substrate higher that 50 V offering two advantages compared to a standard MAPS: increased depletion thickness (and hence more signal), and charge collection by drift yielding faster signals and better radiation tolerance (as the charge has much less time to be trapped before being collected).

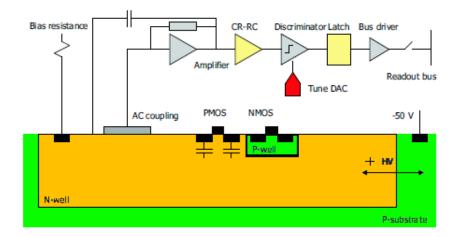

Interesting results in this field has been obtained by [28]. In that project,

a 0.35  $\mu m$  CMOS technology has been used to produce a small matrix of  $50 \times 50 \ \mu m^2$  pixels. A schematic view of the detector is shown in Fig. 2.13:

Figure 2.13: Schematic view of a HV MAPS detector ([28]).

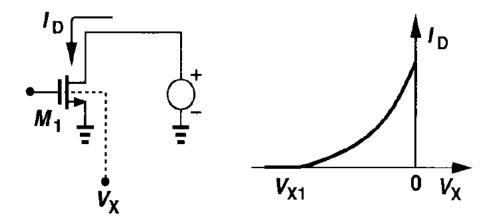

a deep n-well is placed in a p-substrate and it is used as main collecting electrode; the substrate is negatively biased down to 50V - 60 V. Inside the n-well electrode, both PMOS transistors and a p-well containing NMOS transistors are placed, allowing to take the advantage of the complementary MOS structures of the CMOS technology. The n-well is biased by  $V_{dd}$ through a high value resistor  $(R \approx G\Omega)$  to avoid to have the charge flowing to the positive power supply before the amplifier can react. The sensor is AC coupled to the front-end electronics based on a charge sensitive amplifier with a constant current feedback used to discharge the capacitive feedback, a shaper based on a CR - RC filter, a threshold discriminator and a latch. The charge sensitive amplifier is based on a folded cascode stage (Fig. 2.14). The p-diffusions (a,b,c and d in Fig. 2.14) are capacitively coupled with the n-well and can be source of cross-talk; however, the diffusions a, b and c are connected to voltage values almost constant and represent only a parasitic contribute to the detector capacitance; the diffusion d connects the output with the n-well and represents a capacitive feedback regulating the charge amplifier gain  $(V_{out} = Q_{in}/C_{fb})$ . Since the p-diffusion of the M1 transistor can be made narrow, the feedback capacitance is relatively low  $(C_{fb} \approx 1 fF)$ and it guarantees a high gain. The dominant parasitic capacitance is due to the P-well containing the NMOS transistors. The  $\Delta V$  between the p-well

Figure 2.14: Charge sensitive amplifier of the HV MAPS ([28]).

and the n-well is only a few volts and, consequently, the depletion region is small and the capacitance is high (see formula 1.2 and 1.3). The detector capacitance has been estimated to be  $\approx 38 \ fF$  and the parasitic capacitance is  $\approx 180 \ fF$ . In terms of performance, the detector has been able to be depleted up to  $\approx 9 \ \mu m$  for a reverse bias of  $\approx 60 \ V$ , with a detector noise  $85e^-$  and a threshold dispersion of  $75e^-$  for a minimum detectable signal of  $6\sigma_{noise} = 960e^-$  and a 100% fill factor.

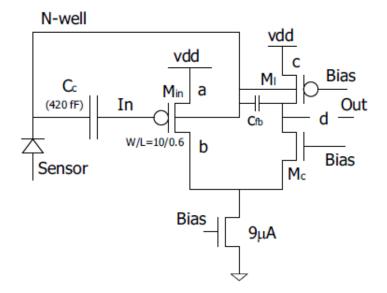

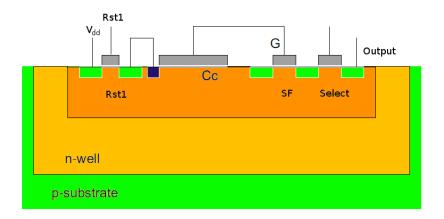

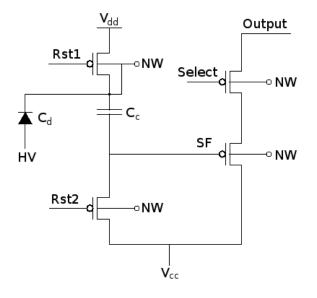

Interesting results have been obtained also from another prototype of the HV MAPS collaboration ([29]). The new prototype implemented in a 0.35  $\mu m$  CMOS technology is based on a matrix of  $128 \times 128$  pixels of  $21 \times 21 \ \mu m^2$ . In this prototype the P-well has been eliminated by implementing the frontend electronics only in PMOS (see Fig. 2.15). This significantly reduced the parasitic capacitance compared to the previous prototype. Moreover, using only PMOS transistors offers also the advantage of lower radiation induced transistor leakage. The front-end electronics is shown in Fig. 2.16: the sensor is AC coupled with the source follower through the capacitance  $C_c$ ; a reset transistor ( $Rst_1$ ) is used to bias the n-well before the acquisition time: in this way it is possible both to have the bulk of the PMOS at the highest voltage and the n-well floating during the acquisition. A second reset transistor ( $Rst_2$ ) is used to bias the gate of the source follower. The voltage

Figure 2.15: New prototype of HV MAPS.

Figure 2.16: Front-end electronics of the new HV MAPS prototype based only on PMOS transistors.

signal at the source follower input is  $V = Q_{in}/C_d$ ; the signal is then stored at the output where it will be treated by a voltage amplifier and digitalized by an ADC. The output readout is based on the rolling-shutter method. The main results obtained by testing this prototype are a spatial resolution of  $\approx 7 \ \mu m$ , a detection efficiency higher 85%, a noise of  $90e^-$  and a power consumption of the pixel matrix of 8 mW.

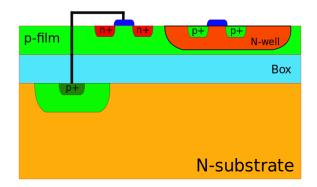

#### 2.5 Silicon on Insulator

Silicon on Insulator (SOI) technology represents an interesting alternative to CMOS technology which is reaching its performance limits with ultra deep submicron nodes, such as 45 nm and 32 nm, in terms of power consumption and speed. The possibility to use high-resistivity bulk material maintaining CMOS processing of electronics circuits makes them interesting also for particles detector applications. A schematic view of a SOI detector is shown in Fig. 2.17 ([32]). An oxide layer (of a 10 nm to 5  $\mu m$  thickness) is grown on a

Figure 2.17: Schematic view of a SOI detector (the clear green part represents the depletion region due to the pn junction).

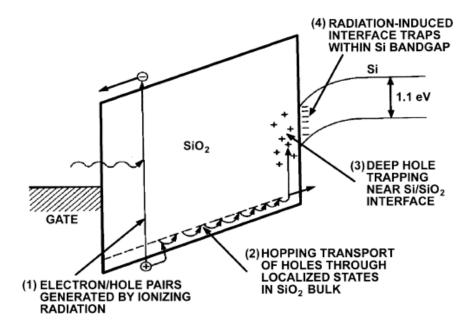

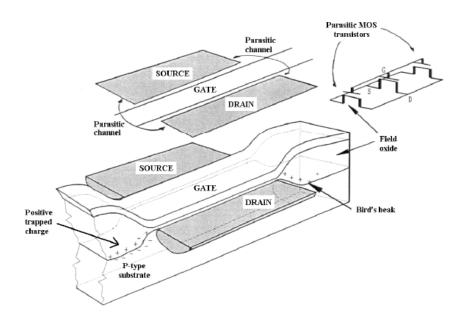

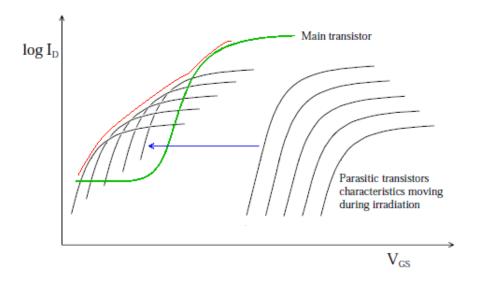

n-type substrate. The circuitry is built on a silicon film layer, usually floating, resting on the silicon dioxide layer. A p-well in the n-substrate is used as collecting electrode; the sensor is DC coupled with the front-end electronics by a connection (typically tungsten) passing through the oxide and the silicon film. The buried oxide (Box) acts as excellent isolation between the sensor and the circuitry allowing to place an n-well in the front-end electronics and, consequently, to use both types of transistors (NMOS and PMOS) having more flexibility in the electronics design. Furthermore, it acts as dielectric barrier reducing considerably the substrate noise (in particular the digital noise affecting the analog circuit), the junction capacitance (in fact, the junctions and the bulk are now separated by the oxide), the cross-talk between neighbor circuits via substrate (which is now totally isolated) and the latch-up problem. The decreasing of the parasitic capacitances and the parasitic current allows to have better performance in terms of speed and power consumption. However, the main drawback is represented by the low radiation hardness due to the Box which is highly sensitive to ionizing radiation damage. Consequently, they can find more applications as soft radiation detector (such as X-ray and near visible), for which radiation damage is not an issue.

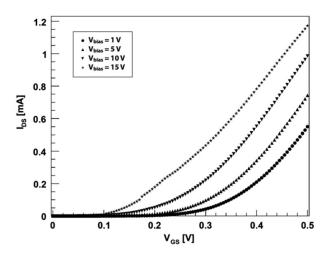

By applying a reverse bias it is also possible to obtain a fully depleted substrate. The main problem due to the back bias is the so called *back gate effect*: the transistors placed in the silicon film are close to the sensor where the high voltage bias applied influences the transistor threshold; in fact, the Box acts as a secondary parasitic gate causing the previous mentioned issue (see Fig. 2.18). It can be solved by placing a low-doped p-implant surround-

Figure 2.18: Shift of the threshold voltage for different substrate biases for a NMOS transistor (from [33]).

ing the p+ electrode which shields the transistors in the SOI. The SOI Pixel Collaboration is obtaining interesting results in SOI application, in particular with the SOImager-2 sensor ([35]), designed in a 0.2  $\mu m$ SOI technology. The sensitive area is made by a 256 × 256 pixels matrix having a pitch of 13.75  $\mu m$ . The front-end is based on a 3T configuration and the pixels are read-out by four parallel arrays of 64 columns each by the rolling shutter method. Measurements results show an efficiency close to 100%, a signal to noise ratio up to 50 and a point resolution down to 1.07  $\mu m$ .

## Chapter 3

# LePix

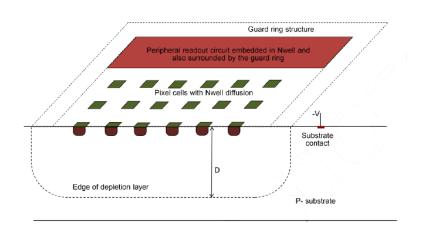

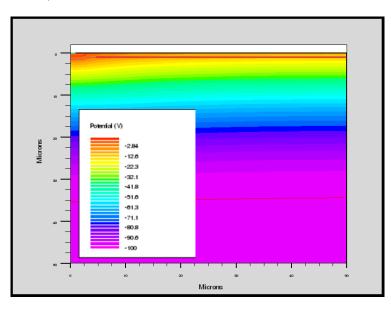

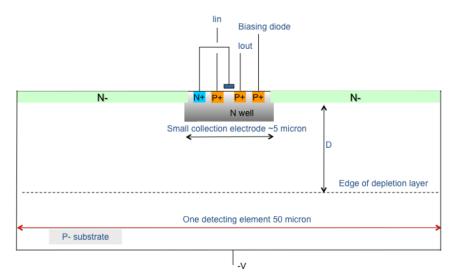

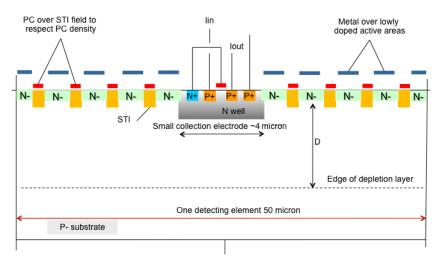

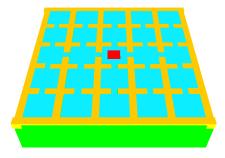

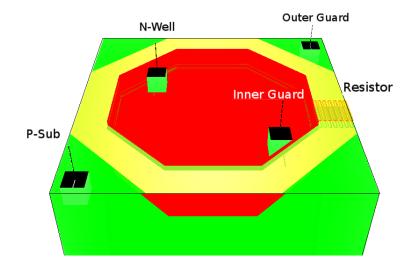

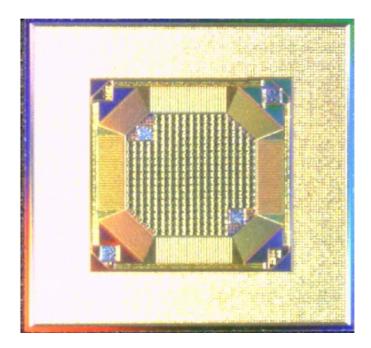

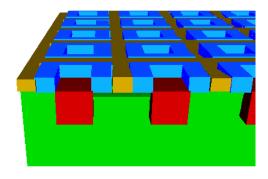

The LePix project explores monolithic pixel sensors fabricated in a 90 nm CMOS technology on a high resistivity substrate. The sensor has the advantage of a monolithic device and offers also the possibility to collect charge by drift applying a reverse bias to the substrate; consequently there is the possibility to reach interesting performance in terms of signal to noise ratio and radiation tolerance. In this chapter the technology and foundry choices, the sensor principle and some practical device implementations will be shown; in particular, the main solutions used to deal with the technology limitations will be discussed. Only the detecting device will be treated: the circuitry implementation to process the signal will be described in the following chapters.

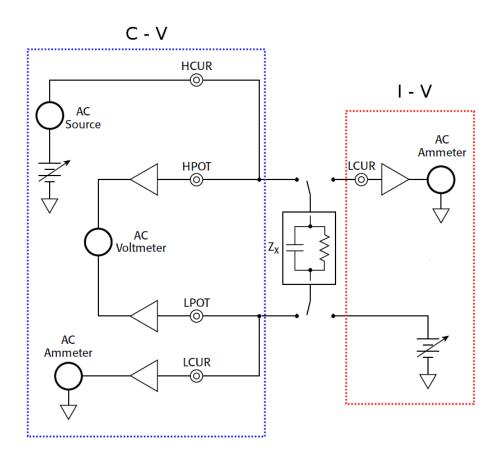

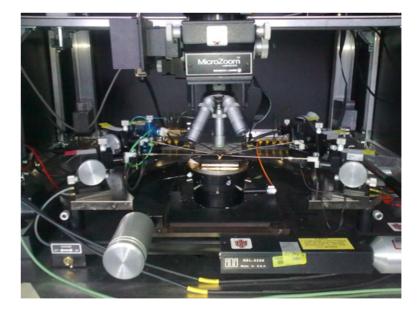

### 3.1 Technology Choice